Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512h-80i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

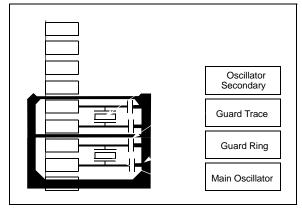

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## TABLE 4-1: SFR MEMORY MAP

|                        | Virtual A | Address         |

|------------------------|-----------|-----------------|

| Peripheral             | Base      | Offset<br>Start |

| Watchdog Timer         |           | 0x0000          |

| RTCC                   |           | 0x0200          |

| Timer1-Timer5          |           | 0x0600          |

| Input Capture 1-5      |           | 0x2000          |

| Output Compare 1-5     |           | 0x3000          |

| I2C1-I2C5              |           | 0x5000          |

| SPI1-SPI4              |           | 0x5800          |

| UART1-UART6            | 0xBF80    | 0x6000          |

| PMP                    | UXBFOU    | 0x7000          |

| ADC                    |           | 0x9000          |

| CVREF                  |           | 0x9800          |

| Comparator             |           | 0xA000          |

| Oscillator             |           | 0xF000          |

| Device and Revision ID |           | 0xF200          |

| Flash Controller       |           | 0xF400          |

| Reset                  |           | 0xF600          |

| Interrupts             |           | 0x1000          |

| Bus Matrix             |           | 0x2000          |

| DMA                    |           | 0x3000          |

| Prefetch               | 0xBF88    | 0x4000          |

| USB                    |           | 0x5040          |

| PORTA-PORTG            |           | 0x6000          |

| Ethernet               |           | 0x9000          |

| Configuration          | 0xBFC0    | 0x2FF0          |

# 4.2 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

## TABLE 4-2: BUS MATRIX REGISTER MAP

| ress                        | <b>_</b>                | e         |                      |       |       |       |       |           |      |      |       | Bits       |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|----------------------|-------|-------|-------|-------|-----------|------|------|-------|------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15                | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7  | 22/6       | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 0000                        |                         | 31:16     | —                    |       | —     | —     |       | BMXCHEDMA | —    | _    |       | —          | —    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | BINIXCON                | 15:0      | —                    | -     | _     | _     |       | _         | _    | _    | _     | BMXWSDRM   | _    | _         | _         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —                    | -     | -     | _     | _     | _         | —    | -    | _     | —          | —    | —         | _         | —         | _          | —        | 0000          |

| 2010                        | DIVINDINF DAV /         | 15:0      |                      |       |       |       |       |           |      | -    | BMXD  | (PBA<15:0> |      | -         |           | -         | -          |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | —                    | —     | —     | —     | —     |           | —    | —    | —     | _          | —    | -         | —         | —         | —          | —        | 0000          |

| 2020                        | DWIXDODDI               | 15:0      | BMXDUDBA<15:0>       |       |       |       |       |           | T    | 0000 |       |            |      |           |           |           |            |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _                    | —     | —     |       | _     | —         | _    | _    | _     | —          | _    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |                      |       |       |       |       |           |      |      | BMXDL | JPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |                      |       |       |       |       |           |      |      | BMXDF | RMSZ<31:0> |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |                      |       |       |       |       |           |      |      |       |            |      |           |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —                    | —     | -     |       | —     | —         | _    |      | —     | _          | _    | —         |           | BMXPUPB   | A<19:16>   |          | 0000          |

|                             |                         | 15:0      |                      |       |       |       |       |           |      |      | BMXPL | JPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     | BMXPFMSZ<31:0>       |       |       |       |       |           |      | xxxx |       |            |      |           |           |           |            |          |               |

|                             |                         | 15:0      |                      |       |       |       |       |           |      | xxxx |       |            |      |           |           |           |            |          |               |

| 2070                        | BMXBOOTSZ               | 31:16     | 1:16 BMXBOOTSZ<31:0> |       |       |       |       |           |      | 0000 |       |            |      |           |           |           |            |          |               |

|                             |                         |           |                      |       |       |       |       |           | 3000 |      |       |            |      |           |           |           |            |          |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX5XX/6XX/7XX devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site.

Note: For PIC32MX5XX/6XX/7XX devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

| TABLE 7-1: INTERRUPT IRQ                                                            | VECTOR | AND BIT | IT LOCATION (CONTINUED) |          |              |              |  |

|-------------------------------------------------------------------------------------|--------|---------|-------------------------|----------|--------------|--------------|--|

| Interrupt Source <sup>(1)</sup>                                                     | IRQ    | Vector  | Interrupt Bit Location  |          |              |              |  |

| interrupt Source ?                                                                  | Number | Number  | Flag                    | Enable   | Priority     | Sub-Priority |  |

| AD1 – ADC1 Convert Done                                                             | 33     | 27      | IFS1<1>                 | IEC1<1>  | IPC6<28:26>  | IPC6<25:24>  |  |

| PMP – Parallel Master Port                                                          | 34     | 28      | IFS1<2>                 | IEC1<2>  | IPC7<4:2>    | IPC7<1:0>    |  |

| CMP1 – Comparator Interrupt                                                         | 35     | 29      | IFS1<3>                 | IEC1<3>  | IPC7<12:10>  | IPC7<9:8>    |  |

| CMP2 – Comparator Interrupt                                                         | 36     | 30      | IFS1<4>                 | IEC1<4>  | IPC7<20:18>  | IPC7<17:16>  |  |

| U2E – UART2 Error<br>SPI2E – SPI2 Fault<br>I2C4B – I2C4 Bus Collision Event         | 37     | 31      | IFS1<5>                 | IEC1<5>  | IPC7<28:26>  | IPC7<25:24>  |  |

| U2RX – UART2 Receiver<br>SPI2RX – SPI2 Receive Done<br>I2C4S – I2C4 Slave Event     | 38     | 31      | IFS1<6>                 | IEC1<6>  | IPC7<28:26>  | IPC7<25:24>  |  |

| U2TX – UART2 Transmitter<br>SPI2TX – SPI2 Transfer Done<br>IC4M – I2C4 Master Event | 39     | 31      | IFS1<7>                 | IEC1<7>  | IPC7<28:26>  | IPC7<25:24>  |  |

| U3E – UART3 Error<br>SPI4E – SPI4 Fault<br>I2C5B – I2C5 Bus Collision Event         | 40     | 32      | IFS1<8>                 | IEC1<8>  | IPC8<4:2>    | IPC8<1:0>    |  |

| U3RX – UART3 Receiver<br>SPI4RX – SPI4 Receive Done<br>I2C5S – I2C5 Slave Event     | 41     | 32      | IFS1<9>                 | IEC1<9>  | IPC8<4:2>    | IPC8<1:0>    |  |

| U3TX – UART3 Transmitter<br>SPI4TX – SPI4 Transfer Done<br>IC5M – I2C5 Master Event | 42     | 32      | IFS1<10>                | IEC1<10> | IPC8<4:2>    | IPC8<1:0>    |  |

| I2C2B – I2C2 Bus Collision Event                                                    | 43     | 33      | IFS1<11>                | IEC1<11> | IPC8<12:10>  | IPC8<9:8>    |  |

| I2C2S – I2C2 Slave Event                                                            | 44     | 33      | IFS1<12>                | IEC1<12> | IPC8<12:10>  | IPC8<9:8>    |  |

| I2C2M – I2C2 Master Event                                                           | 45     | 33      | IFS1<13>                | IEC1<13> | IPC8<12:10>  | IPC8<9:8>    |  |

| FSCM – Fail-Safe Clock Monitor                                                      | 46     | 34      | IFS1<14>                | IEC1<14> | IPC8<20:18>  | IPC8<17:16>  |  |

| RTCC – Real-Time Clock and<br>Calendar                                              | 47     | 35      | IFS1<15>                | IEC1<15> | IPC8<28:26>  | IPC8<25:24>  |  |

| DMA0 – DMA Channel 0                                                                | 48     | 36      | IFS1<16>                | IEC1<16> | IPC9<4:2>    | IPC9<1:0>    |  |

| DMA1 – DMA Channel 1                                                                | 49     | 37      | IFS1<17>                | IEC1<17> | IPC9<12:10>  | IPC9<9:8>    |  |

| DMA2 – DMA Channel 2                                                                | 50     | 38      | IFS1<18>                | IEC1<18> | IPC9<20:18>  | IPC9<17:16>  |  |

| DMA3 – DMA Channel 3                                                                | 51     | 39      | IFS1<19>                | IEC1<19> | IPC9<28:26>  | IPC9<25:24>  |  |

| DMA4 – DMA Channel 4                                                                | 52     | 40      | IFS1<20>                | IEC1<20> | IPC10<4:2>   | IPC10<1:0>   |  |

| DMA5 – DMA Channel 5                                                                | 53     | 41      | IFS1<21>                | IEC1<21> | IPC10<12:10> | IPC10<9:8>   |  |

| DMA6 – DMA Channel 6                                                                | 54     | 42      | IFS1<22>                | IEC1<22> | IPC10<20:18> | IPC10<17:16> |  |

| DMA7 – DMA Channel 7                                                                | 55     | 43      | IFS1<23>                | IEC1<23> | IPC10<28:26> | IPC10<25:24> |  |

| FCE – Flash Control Event                                                           | 56     | 44      | IFS1<24>                | IEC1<24> | IPC11<4:2>   | IPC11<1:0>   |  |

| USB – USB Interrupt                                                                 | 57     | 45      | IFS1<25>                | IEC1<25> | IPC11<12:10> | IPC11<9:8>   |  |

| CAN1 – Control Area Network 1                                                       | 58     | 46      | IFS1<26>                | IEC1<26> | IPC11<20:18> | IPC11<17:16> |  |

| CAN2 – Control Area Network 2                                                       | 59     | 47      | IFS1<27>                | IEC1<27> | IPC11<28:26> | IPC11<25:24> |  |

| ETH – Ethernet Interrupt                                                            | 60     | 48      | IFS1<28>                | IEC1<28> | IPC12<4:2>   | IPC12<1:0>   |  |

| IC1E – Input Capture 1 Error                                                        | 61     | 5       | IFS1<29>                | IEC1<29> | IPC1<12:10>  | IPC1<9:8>    |  |

| IC2E – Input Capture 2 Error                                                        | 62     | 9       | IFS1<30>                | IEC1<30> | IPC2<12:10>  | IPC2<9:8>    |  |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                       | —                 | _                 | _                 | _                | —                |  |  |  |

| 22:46        | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                       | —                 | _                 | _                 | -                | —                |  |  |  |

| 45.0         | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | —                       | _                 | _                 | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | —                 | —                 | TUN<5:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| J. J.             |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

| bit 5-0 | <b>TUN&lt;5:0&gt;:</b> FRC Oscillator Tuning bits <sup>(1)</sup><br>100000 = Center frequency -12.5% for PIC32MX575/595/675/695/775/795 devices<br>100000 = Center frequency -1.5% for PIC32MX534/564/664/764 devices<br>100001 = |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 111111 =<br>000000 = Center frequency; Oscillator runs at nominal frequency (8 MHz)<br>000001 =                                                                                                                                   |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 011110 =<br>011111 = Center frequency +12.5% for PIC32MX575/595/675/695/775/795 devices<br>011111 = Center frequency +1.5% for PIC32MX534/564/664/764 devices                                                                     |

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the |

|-------|----------------------------------------------------------------------------------------------------------|

|       | "PIC32 Family Reference Manual" for details.                                                             |

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | _                 |                   |                   |                   |                   |                  | —                |  |  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   |                   |                   |                   |                   |                   |                  | —                |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | -                 | -                 | —                 | _                 | —                | —                |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | CNT<7:0>          |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits

- Typical values of the threshold are: 01001010 = 64-byte packet 00101010 = 32-byte packet 00011010 = 16-byte packet

00010010 = 8-byte packet

## REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   |                   |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   |                   |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | —                 | _                 | _                 | -                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          |                   |                   | В                 | DTPTRL<15:9       | )>                |                   |                  | —                |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-1 BDTPTRL<15:9>: BDT Base Address bits

This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | —                 | —                 | —                 | -                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

## REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

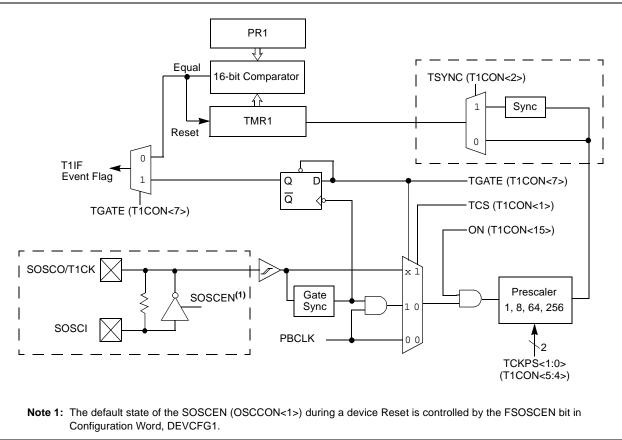

# 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## FIGURE 13-1: TIMER1 BLOCK DIAGRAM

## 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

# REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Legend:           | HC = Cleared by hardware |                                          |  |  |  |

|-------------------|--------------------------|------------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'       |  |  |  |

| -n = Value at POR | '1' = Bit is set         | 0' = Bit is cleared $x = Bit is unknown$ |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the I<sup>2</sup>C module; all I<sup>2</sup>C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (software can write '0' to initiate stretch and write '1' to release clock). Cleared by hardware at the beginning of a slave transmission and at the end of slave reception.

If STREN = 0:

Bit is R/S (software can only write '1' to release clock). Cleared by hardware at the beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C reserved address rule is not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

0 = Start condition is not in progress

#### I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED) REGISTER 19-1: **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave) bit 7 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception) 0 = General call address is disabled STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave) bit 6 Used in conjunction with SCLREL bit. 1 = Enable software or receive clock stretching 0 = Disable software or receive clock stretching bit 5 ACKDT: Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive) Value that is transmitted when the software initiates an acknowledge sequence. 1 = Send NACK during an acknowledge 0 = Send ACK during an acknowledge bit 4 ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive) 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence. 0 = Acknowledge sequence not in progress bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master) 1 = Enables Receive mode for $l^2C$ . Hardware clear at end of eighth bit of master receive data byte. 0 = Receive sequence is not in progress **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master) bit 2 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. 0 = Stop condition is not in progress **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master) bit 1 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence. 0 = Repeated Start condition is not in progress **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master) bit 0 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the

- SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | _                 | _                 | —                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | —                 | _                 | _                 |                  | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   |                   | OB3E              | OB2E              | OB1E             | OB0E             |

## REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (ONLY SLAVE MODES)

| Legend:           | d: HS = Set by Hardware |                           |                    |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

- 0 = An overflow has not occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = An underflow has not occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN19           | MSEL1             | 9<1:0>            |                   | FSEL19<4:0>       |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN17           | MSEL1             | 7<1:0>            |                   | F                 | SEL17<4:0>        | >                |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN16           | MSEL1             | 6<1:0>            |                   | F                 | SEL16<4:0>        | FSEL16<4:0>      |                  |  |

## REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | <b>FLTEN19:</b> Filter 19 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           |                                                                                                                                                                                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

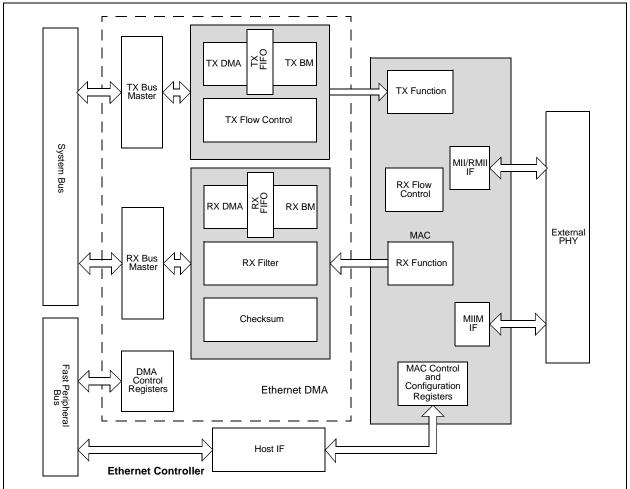

# 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

## FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

## REGISTER 25-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | _                 |                   |                   | B2                | BIPKTGP<6:(       | )>                |                  |                  |

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23:16        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |

## REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

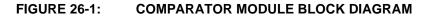

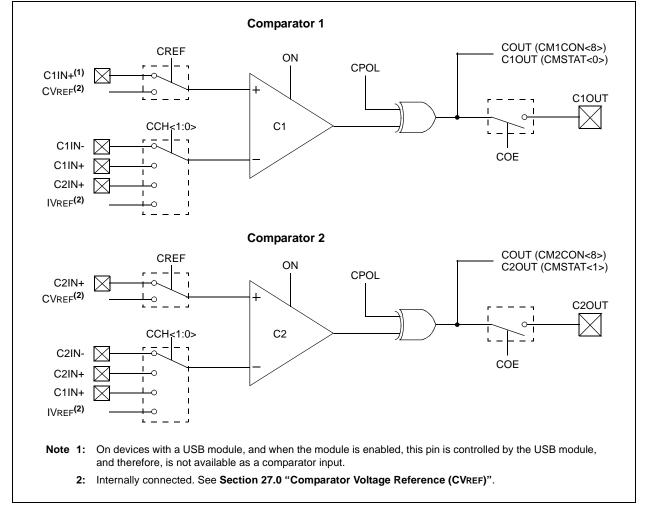

# 26.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 19.** "Comparator" (DS60001110) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Comparator module contains two comparators that can be configured in a variety of ways.

Key features of the Comparator module include:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be inverted

- Selectable interrupt generation

A block diagram of the Comparator module is illustrated in Figure 26-1.

| REGISTE | ER 29-4: D | DEVCFG3: DE | EVICE CON | FIGURATIO | N WORD 3 |  |

|---------|------------|-------------|-----------|-----------|----------|--|

|         |            |             |           |           |          |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|

| 04-04        | R/P               | R/P               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |

| 31:24        | FVBUSONIO         | FUSBIDIO          | _                 | _                 | —                 | FCANIO <sup>(1)</sup> | FETHIO <sup>(2)</sup> | FMIIEN <sup>(2)</sup> |

| 22.46        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |

| 23:16        | —                 | —                 | —                 | —                 | —                 | FSRSSEL<2:0>          |                       |                       |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                       |                       |                       |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                       |                       |                       |

| Legend:           | r = Reserved bit | P = Programmable bit        |                  |

|-------------------|------------------|-----------------------------|------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x      | = Bit is unknown |

1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

bit 30

FUSBIDIO: USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

bit 29-27

Reserved: Write '1'

bit 26

FCANIO: CAN I/O Pin Selection bit<sup>(1)</sup> 1 = Default CAN I/O Pins 0 = Alternate CAN I/O Pins

bit 25

FETHIO: Ethernet I/O Pins

1 = Default Ethernet I/O Pins

FVBUSONIO: USB VBUSON Selection bit

- 0 =Alternate Ethernet I/O Pins

- bit 24 FMIIEN: Ethernet MII Enable bit<sup>(2)</sup>

- 1 = MII is enabled

- 0 = RMII is enabled

- bit 23-19 Reserved: Write '1'

- bit 18-16 FSRSSEL<2:0>: SRS Select bits

- 111 = Assign Interrupt Priority 7 to a shadow register set

- 110 = Assign Interrupt Priority 6 to a shadow register set

- •

bit 31

- 001 = Assign Interrupt Priority 1 to a shadow register set

000 = All interrupt priorities are assigned to a shadow register set

- bit 15-0 **USERID<15:0>:** User ID bits This is a 16-bit value that is user-defined and is readable via ICSP<sup>™</sup> and JTAG.

- Note 1: This bit is Reserved and reads '1' on PIC32MX664/675/695 devices.

- 2: This bit is Reserved and reads '1' on PIC32MX534/564/575 devices.

## TABLE 32-37: 10-BIT ADC CONVERSION RATE PARAMETERS

| Standard Operating Conditions (see Note 3): 2.5V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                |                             |               |              |                            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|---------------|--------------|----------------------------|--|--|

| ADC Speed <sup>(2)</sup>                                                                                                                                                                                        | TAD<br>Minimum | Sampling<br>Time<br>Minimum | Rs<br>Maximum | Vdd          | ADC Channels Configuration |  |  |

| 1 Msps to<br>400 ksps <sup>(1)</sup>                                                                                                                                                                            | 65 ns          | 132 ns                      | 500Ω          | 3.0V to 3.6V | ANX CHX<br>S&H<br>ADC      |  |  |

| Up to 400 ksps                                                                                                                                                                                                  | 200 ns         | 200 ns                      | 5.0 kΩ        | 2.5V to 3.6V | ANX ADC<br>ANX or VREF-    |  |  |

Note 1: External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX5XX/6XX/7XX

NOTES: