Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512ht-80i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         |                      | Pin Nur         | nber <sup>(1)</sup> |                 | <b>D</b> !  | Buffer<br>Type | Description                       |  |  |

|---------|----------------------|-----------------|---------------------|-----------------|-------------|----------------|-----------------------------------|--|--|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type |                |                                   |  |  |

| RA0     | _                    | 17              | G3                  | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |  |  |

| RA1     | —                    | 38              | J6                  | A26             | I/O         | ST             |                                   |  |  |

| RA2     | —                    | 58              | H11                 | A39             | I/O         | ST             |                                   |  |  |

| RA3     | —                    | 59              | G10                 | B32             | I/O         | ST             |                                   |  |  |

| RA4     | —                    | 60              | G11                 | A40             | I/O         | ST             |                                   |  |  |

| RA5     | —                    | 61              | G9                  | B33             | I/O         | ST             |                                   |  |  |

| RA6     | —                    | 91              | C5                  | B51             | I/O         | ST             |                                   |  |  |

| RA7     | —                    | 92              | B5                  | A62             | I/O         | ST             |                                   |  |  |

| RA9     | —                    | 28              | L2                  | A21             | I/O         | ST             |                                   |  |  |

| RA10    |                      | 29              | K3                  | B17             | I/O         | ST             | ]                                 |  |  |

| RA14    |                      | 66              | E11                 | B36             | I/O         | ST             | ]                                 |  |  |

| RA15    | —                    | 67              | E8                  | A44             | I/O         | ST             |                                   |  |  |

| RB0     | 16                   | 25              | K2                  | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |  |  |

| RB1     | 15                   | 24              | K1                  | A15             | I/O         | ST             |                                   |  |  |

| RB2     | 14                   | 23              | J2                  | B13             | I/O         | ST             |                                   |  |  |

| RB3     | 13                   | 22              | J1                  | A13             | I/O         | ST             |                                   |  |  |

| RB4     | 12                   | 21              | H2                  | B11             | I/O         | ST             |                                   |  |  |

| RB5     | 11                   | 20              | H1                  | A12             | I/O         | ST             |                                   |  |  |

| RB6     | 17                   | 26              | L1                  | A20             | I/O         | ST             |                                   |  |  |

| RB7     | 18                   | 27              | J3                  | B16             | I/O         | ST             |                                   |  |  |

| RB8     | 21                   | 32              | K4                  | A23             | I/O         | ST             |                                   |  |  |

| RB9     | 22                   | 33              | L4                  | B19             | I/O         | ST             |                                   |  |  |

| RB10    | 23                   | 34              | L5                  | A24             | I/O         | ST             | 1                                 |  |  |

| RB11    | 24                   | 35              | J5                  | B20             | I/O         | ST             | ]                                 |  |  |

| RB12    | 27                   | 41              | J7                  | B23             | I/O         | ST             | ]                                 |  |  |

| RB13    | 28                   | 42              | L7                  | A28             | I/O         | ST             | ]                                 |  |  |

| RB14    | 29                   | 43              | K7                  | B24             | I/O         | ST             |                                   |  |  |

| RB15    | 30                   | 44              | L8                  | A29             | I/O         | ST             |                                   |  |  |

| RC1     | —                    | 6               | D1                  | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |  |  |

| RC2     | —                    | 7               | E4                  | B4              | I/O         | ST             |                                   |  |  |

| RC3     | —                    | 8               | E2                  | A6              | I/O         | ST             |                                   |  |  |

| RC4     |                      | 9               | E1                  | B5              | I/O         | ST             | ]                                 |  |  |

| RC12    | 39                   | 63              | F9                  | B34             | I/O         | ST             | ]                                 |  |  |

| RC13    | 47                   | 73              | C10                 | A47             | I/O         | ST             | ]                                 |  |  |

| RC14    | 48                   | 74              | B11                 | B40             | I/O         | ST             | ]                                 |  |  |

|         | -                    | 64              | F11                 | A42             | I/O         | ST             | 1                                 |  |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| TABLE 1-1 | : PINOU            | T I/O DES                 |                  | NS (CONT        | )           |                |                                                                                                                |  |  |

|-----------|--------------------|---------------------------|------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------|--|--|

|           |                    | Pin Number <sup>(1)</sup> |                  |                 |             |                |                                                                                                                |  |  |

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP           | 121-Pin<br>TFBGA | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                    |  |  |

| PMD0      | 60                 | 93                        | A4               | B52             | I/O         | TTL/ST         | Parallel Master Port data                                                                                      |  |  |

| PMD1      | 61                 | 94                        | B4               | A64             | I/O         | TTL/ST         | (Demultiplexed Master mode) or                                                                                 |  |  |

| PMD2      | 62                 | 98                        | B3               | A66             | I/O         | TTL/ST         | address/data (Multiplexed Master modes)                                                                        |  |  |

| PMD3      | 63                 | 99                        | A2               | B56             | I/O         | TTL/ST         | nodes)                                                                                                         |  |  |

| PMD4      | 64                 | 100                       | A1               | A67             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD5      | 1                  | 3                         | D3               | B2              | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD6      | 2                  | 4                         | C1               | A4              | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD7      | 3                  | 5                         | D2               | B3              | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD8      | —                  | 90                        | A5               | A61             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD9      | —                  | 89                        | E6               | B50             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD10     | —                  | 88                        | A6               | A60             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD11     | _                  | 87                        | B6               | B49             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD12     | _                  | 79                        | A9               | B43             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD13     | _                  | 80                        | D8               | A54             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD14     | _                  | 83                        | D7               | B45             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMD15     | _                  | 84                        | C7               | A56             | I/O         | TTL/ST         |                                                                                                                |  |  |

| PMALL     | 30                 | 44                        | L8               | A29             | ο           | _              | Parallel Master Port address latch<br>enable low byte (Multiplexed Master<br>modes)                            |  |  |

| PMALH     | 29                 | 43                        | К7               | B24             | 0           | _              | Parallel Master Port address latch<br>enable high byte (Multiplexed Master<br>modes)                           |  |  |

| PMRD      | 53                 | 82                        | B8               | A55             | 0           | _              | Parallel Master Port read strobe                                                                               |  |  |

| PMWR      | 52                 | 81                        | C8               | B44             | 0           | _              | Parallel Master Port write strobe                                                                              |  |  |

| VBUS      | 34                 | 54                        | H8               | A37             | I           | Analog         | USB bus power monitor                                                                                          |  |  |

| VUSB3V3   | 35                 | 55                        | H9               | B30             | Р           | _              | USB internal transceiver supply. If the<br>USB module is <i>not</i> used, this pin mus<br>be connected to VDD. |  |  |

| VBUSON    | 11                 | 20                        | H1               | A12             | 0           | _              | USB Host and OTG bus power contro<br>output                                                                    |  |  |

| D+        | 37                 | 57                        | H10              | B31             | I/O         | Analog         | USB D+                                                                                                         |  |  |

| D-        | 36                 | 56                        | J11              | A38             | I/O         | Analog         | USB D-                                                                                                         |  |  |

| USBID     | 33                 | 51                        | K10              | A35             | Ι           | ST             | USB OTG ID detect                                                                                              |  |  |

| C1RX      | 58                 | 87                        | B6               | B49             | I           | ST             | CAN1 bus receive pin                                                                                           |  |  |

| C1TX      | 59                 | 88                        | A6               | A60             | 0           |                | CAN1 bus transmit pin                                                                                          |  |  |

| AC1RX     | 32                 | 40                        | K6               | A27             | I           | ST             | Alternate CAN1 bus receive pin                                                                                 |  |  |

| AC1TX     | 31                 | 39                        | L6               | B22             | 0           | —              | Alternate CAN1 bus transmit pin                                                                                |  |  |

| C2RX      | 29                 | 90                        | A5               | A61             | I           | ST             | CAN2 bus receive pin                                                                                           |  |  |

|           | 21                 | 89                        | E6               | B50             | 0           | —              | CAN2 bus transmit pin                                                                                          |  |  |

| C2TX      |                    |                           | 1                | 1               | 1           |                | Alternate CAN2 bus receive pin                                                                                 |  |  |

#### PINOLIT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

### TABLE 3-3: PIC32MX5XX/6XX/7XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

### 3.3 Power Management

The MIPS32 M4K Processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 28.0 "Power-Saving Features".

#### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-5XX/6XX/7XX family core is in the clock tree and clocking registers. The PIC32 family uses extensive use of local gated clocks to reduce this dynamic power consumption.

### 3.4 EJTAG Debug Support

The MIPS32 M4K Processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the MIPS M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the MIPS32 M4K processor core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Interrupt Source <sup>(1)</sup>   | IRQ    | Vector        | Interrupt Bit Location |          |              |              |  |  |

|-----------------------------------|--------|---------------|------------------------|----------|--------------|--------------|--|--|

| Interrupt Source                  | Number | Number        | Flag                   | Enable   | Priority     | Sub-Priority |  |  |

| IC3E – Input Capture 3 Error      | 63     | 13            | IFS1<31>               | IEC1<31> | IPC3<12:10>  | IPC3<9:8>    |  |  |

| IC4E – Input Capture 4 Error      | 64     | 17            | IFS2<0>                | IEC2<0>  | IPC4<12:10>  | IPC4<9:8>    |  |  |

| IC5E – Input Capture 5 Error      | 65     | 21            | IFS2<1>                | IEC2<1>  | IPC5<12:10>  | IPC5<9:8>    |  |  |

| PMPE – Parallel Master Port Error | 66     | 28            | IFS2<2>                | IEC2<2>  | IPC7<4:2>    | IPC7<1:0>    |  |  |

| U4E – UART4 Error                 | 67     | 49            | IFS2<3>                | IEC2<3>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U4RX – UART4 Receiver             | 68     | 49            | IFS2<4>                | IEC2<4>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U4TX – UART4 Transmitter          | 69     | 49            | IFS2<5>                | IEC2<5>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U6E – UART6 Error                 | 70     | 50            | IFS2<6>                | IEC2<6>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U6RX – UART6 Receiver             | 71     | 50            | IFS2<7>                | IEC2<7>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U6TX – UART6 Transmitter          | 72     | 50            | IFS2<8>                | IEC2<8>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U5E – UART5 Error                 | 73     | 51            | IFS2<9>                | IEC2<9>  | IPC12<28:26> | IPC12<25:24> |  |  |

| U5RX – UART5 Receiver             | 74     | 51            | IFS2<10>               | IEC2<10> | IPC12<28:26> | IPC12<25:24> |  |  |

| U5TX – UART5 Transmitter          | 75     | 51            | IFS2<11>               | IEC2<11> | IPC12<28:26> | IPC12<25:24> |  |  |

| (Reserved)                        | —      | —             | —                      | —        | <u> </u>     |              |  |  |

|                                   | Lowe   | est Natural ( | Order Priority         | /        |              |              |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

'1' = Bit is set

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31.24        |                   |                   |                   | CHEPFAB           | Г<31:24>                           |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEPFABT<23:16>   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   |                   | CHEPFAB           | T<15:8>                            |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | CHEPFABT<7:0>     |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| ·            |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| R = Rea      | R = Readable bit  |                   |                   | bit               | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |  |

# bit 31-0 CHEPFABT<31:0>: Prefab Abort Count bits

-n = Value at POR

Incremented each time an automatic prefetch cache is aborted due to a non-sequential instruction fetch, load or store.

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | ΓA<7:0>           |                   |                  |                  |  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | DCRCXOR<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

#### 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Т | ABLE 12 | PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H | Н. |

|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |         | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                   | ,  |

|   | ssa     | Bits                                                                                                                                                                                            |    |

| ö                          |                                 | Φ         |       |        |       |       |           |                    |        | -               |        |        |      |      |        |        |      |      | <i>(</i> 0 |

|----------------------------|---------------------------------|-----------|-------|--------|-------|-------|-----------|--------------------|--------|-----------------|--------|--------|------|------|--------|--------|------|------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11     | 26/10              | 25/9   | 24/8            | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset  |

| 6180                       | TRISG                           | 31:16     | —     | —      | —     | _     | —         | —                  | _      | —               | —      | —      | _    | _    | -      | _      | _    | _    | 0000       |

| 6160                       | TRIBU                           | 15:0      | _     | _      | _     | _     | _         |                    | TRISG9 | TRISG8          | TRISG7 | TRISG6 | _    |      | TRISG3 | TRISG2 | -    |      | 03CC       |

| 6100                       | PORTG                           | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000       |

| 6190                       | PURIG                           | 15:0      | _     | _      | _     | _     | _         |                    | RG9    | RG8             | RG7    | RG6    | _    |      | RG3    | RG2    | -    |      | xxxx       |

| 61A0                       | LATG                            | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000       |

| OTAU                       | LAIG                            | 15:0      | _     | _      | _     | _     | _         |                    | LATG9  | LATG8           | LATG7  | LATG6  | _    |      | LATG3  | LATG2  | -    |      | xxxx       |

| 61B0                       | ODCG                            | 31:16     | -     | _      | _     | _     | -         | _                  | _      | _               | _      | -      | _    |      |        | -      | _    |      | 0000       |

| 0180                       | ODCG                            | 15:0      | -     | _      | _     | _     | -         | _                  | ODCG9  | ODCG8           | ODCG7  | ODCG6  | _    |      | ODCG3  | ODCG2  | _    |      | 0000       |

| Laware                     |                                 |           |       | Divisi |       |       | fal Deset | alter a successful |        | dia statistical |        |        |      |      |        |        |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 |           |         |         |         |         |       |       |        | Bi     | ts     |        |      |      |        |        |        |        | <i>(</i> 0 |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -      | -      | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —      | _      | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      |      | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —      | —      | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —      | —      | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

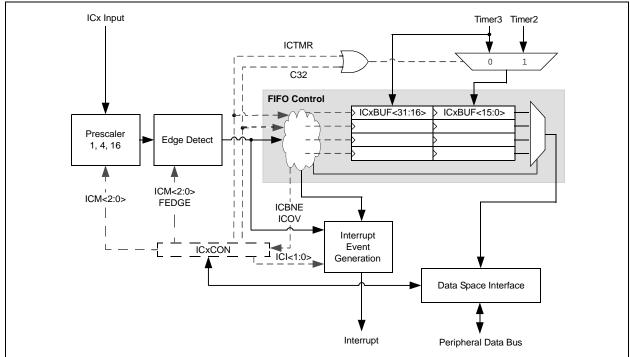

# 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input Capture module can also be used to provide additional sources of external interrupts

### FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

# **19.1 Control Registers**

#### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP

| ss                          |                                 |               |              |             |       |        |        |              |             | Bi         | ts    |             |              |              |               |          |          |          |            |

|-----------------------------|---------------------------------|---------------|--------------|-------------|-------|--------|--------|--------------|-------------|------------|-------|-------------|--------------|--------------|---------------|----------|----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14       | 29/13 | 28/12  | 27/11  | 26/10        | 25/9        | 24/8       | 23/7  | 22/6        | 21/5         | 20/4         | 19/3          | 18/2     | 17/1     | 16/0     | All Resets |

| 5000                        | I2C3CON                         | 31:16         | _            | _           | —     | _      |        |              | _           | _          |       |             | —            | _            | —             |          |          |          | 0000       |

|                             |                                 | 15:0          | ON           | —           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5010                        | I2C3STAT                        | 31:16<br>15:0 | —<br>ACKSTAT | —<br>TRSTAT |       |        | _      | BCL          | —<br>GCSTAT | —<br>ADD10 |       | –<br>I2COV  | —<br>D/A     | —<br>P       |               | —<br>R/W | —<br>RBF | —<br>TBF | 0000       |

|                             | 1000100                         | 31:16         | —            | -           | _     | _      | _      | -            |             | -          | —     | -           |              | -            | _             | -        | —        | —        | 0000       |

| 5020                        | I2C3ADD                         | 15:0          | _            | _           | _     | _      | _      | _            |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5000                        | IOCOMOK                         | 31:16         | _            | _           | —     | —      | —      | _            | —           | _          | —     | _           | —            | —            | —             | _        | —        | _        | 0000       |

| 5030                        | I2C3MSK                         | 15:0          | _            | _           | —     | _      | —      | — — MSK<9:0> |             |            |       |             |              |              |               |          | 0000     |          |            |

| 5040                        | I2C3BRG                         | 31:16         | _            | _           | —     | _      | _      | -            | _           | _          | -     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5040                        | IZCODKG                         | 15:0          | _            | _           | —     | —      |        |              |             |            | Ba    | ud Rate Ger | nerator Regi | ster         |               |          |          |          | 0000       |

| 5050                        | I2C3TRN                         | 31:16         | —            | —           |       |        | —      |              |             | _          |       | —           | _            | _            | _             | —        | —        | -        | 0000       |

| 5050                        | 120311(1)                       | 15:0          | —            | —           |       |        | —      |              |             | _          |       |             | -            | Transmit     | Register      |          |          |          | 0000       |

| 5060                        | I2C3RCV                         | 31:16         | —            | —           | —     | —      | —      | _            | —           | —          | _     | —           | —            | —            | —             | —        | —        | —        | 0000       |

| 0000                        | 12001101                        | 15:0          | _            | _           | —     | _      | —      | _            | _           | —          |       |             |              | Receive      | Register      | -        | -        |          | 0000       |

| 5100                        | I2C4CON                         | 31:16         | _            | _           | —     | _      | _      | _            | _           | —          | _     | —           | _            | _            | _             | —        | —        | —        | 0000       |

|                             |                                 | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5110                        | I2C4STAT                        | 31:16         | —            | —           | —     |        | _      | —            | —           | _          | —     | —           |              | —            |               | —        | —        | —        | 0000       |

| L                           |                                 | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL          | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5120                        | I2C4ADD                         | 31:16         | _            | _           | —     | _      | _      | _            | —           |            | —     | —           | —            | —            | —             | _        | _        | —        | 0000       |

| <b></b>                     |                                 | 15:0          | _            | _           | _     | _      | _      |              |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5130                        | I2C4MSK                         | 31:16         | _            | _           |       |        |        |              |             | _          | _     | _           |              |              |               |          | _        | _        | 0000       |

| ┢────┼                      |                                 | 15:0          |              | _           |       |        | _      |              |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5140                        | I2C4BRG                         | 31:16         |              | _           | _     |        |        | —            | —           |            | -     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0<br>31:16 | _            | _           | _     |        |        |              |             |            |       | ud Rate Ger | erator Regi  | ster         |               |          |          |          | 0000       |

| 5150                        | I2C4TRN                         | 15:0          |              |             |       |        |        |              |             |            | _     | _           | _            | <br>Transmit | —<br>Register | —        | —        | —        | 0000       |

| ł                           |                                 | 31:16         |              |             |       |        |        |              |             |            |       |             |              |              |               | _        | _        | _        | 0000       |

| 5160                        | I2C4RCV                         | 15:0          | _            | _           |       |        |        |              |             | _          | _     |             |              | Receive      | Register      |          |          |          | 0000       |

|                             |                                 | 31:16         | _            | _           | _     | _      | _      | _            | _           | _          | _     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5200                        | I2C5CON                         | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5040                        | 10050747                        | 31:16         | _            | _           | —     | —      | _      | _            | —           |            | _     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5210                        | I2C5STAT                        | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL          | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5000                        | 1005405                         | 31:16         | _            | _           | —     | —      | _      | —            | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5220                        | I2C5ADD                         | 15:0          | _            | _           | _     | _      | _      | _            |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This register is not available on 64-pin devices.

### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | FLTEN11           | MSEL1             | 1<1:0>            | FSEL11<4:0>       |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | FLTEN10           | MSEL1             | 0<1:0>            | FSEL10<4:0>       |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | FLTEN9            | MSEL              | 9<1:0>            | FSEL9<4:0>        |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | FLTEN8            | FLTEN8 MSEL8<1:0> |                   |                   | FSEL8<4:0>        |                   |                  |                  |  |  |  |

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

| bit 31    | FLTEN11: Filter 11 Enable bit                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                                                                                                                               |

|           | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                             |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                  |

| bit 23    | FLTEN10: Filter 10 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | ·<br>·                                                                                                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

|           | — · · · · · · · · · · · · · · · · · · ·                                                                                                                                        |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | FLTEN23           | MSEL2             | 3<1:0>            | FSEL23<4:0>       |                   |                   |                  |                  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | FLTEN22           | MSEL2             | 2<1:0>            | FSEL22<4:0>       |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | FLTEN21           | MSEL2             | 21<1:0>           | FSEL21<4:0>       |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | FLTEN20           | MSEL2             | 20<1:0>           | FSEL20<4:0>       |                   |                   |                  |                  |  |  |  |

#### REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

| bit ( | 31    | <b>FLTEN23:</b> Filter 23 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                    |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit ( | 30-29 | MSEL23<1:0>: Filter 23 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 2 | 28-24 | <pre>FSEL23&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1</pre>                                                       |

| bit 2 | 23    | 00000 = Message matching filter is stored in FIFO buffer 0<br><b>FLTEN22:</b> Filter 22 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                      |

| bit 2 | 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 2 | 20-16 | FSEL22<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

|       | otor  | The hite in this register can only be madified if the correspond                                                                                                                                                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 |                   |                   |                   |                   |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 15:8      | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 10.0      | _                 | TXBUSE            | RXBUSE            | _                 | _                 | _                 | EWMARK           | FWMARK           |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       | RXDONE            | PKTPEND           | RXACT             | _                 | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |

### **REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-15 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | TXBUSE: Transmit BVCI Bus Error Interrupt bit                                                                                                                                                                                                                   |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the TX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 13    | RXBUSE: Receive BVCI Bus Error Interrupt bit                                                                                                                                                                                                                    |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the RX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

| bit 9     | EWMARK: Empty Watermark Interrupt bit                                                                                                                                                                                                                           |

|           | <ul><li>1 = Empty Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                          |

|           | This bit is set when the RX Descriptor Buffer Count is less than or equal to the value in the RXEWM bit (ETHRXWM<0:7>) value. It is cleared by BUFCNT bit (ETHSTAT<16:23>) being incremented by hardware. Writing a '0' or a '1' has no effect.                 |

| bit 8     | FWMARK: Full Watermark Interrupt bit                                                                                                                                                                                                                            |

|           | <ul><li>1 = Full Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                           |

|           | This bit is set when the RX Descriptor Buffer Count is greater than or equal to the value in the RXFWM bit (ETHRXWM<16:23>) field. It is cleared by writing the BUFCDEC (ETHCON1<0>) bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect. |

| bit 7     | RXDONE: Receive Done Interrupt bit                                                                                                                                                                                                                              |

|           | <ul><li>1 = RX packet was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                      |

|           | This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                      |

|           |                                                                                                                                                                                                                                                                 |

| Note:     | It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.                                                                    |

# REGISTER 25-32: EMAC1MCMD: ETHERNET CONTROLLER MAC MII MANAGEMENT COMMAND REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | _                 | SCAN             | READ             |

#### Legend:

| 5                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-2 Unimplemented: Read as '0'