Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512ht-80i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 6: PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

64 1

QFN<sup>(3)</sup> 64 TQFP

| Pin# | Full Pin Name                                             |

|------|-----------------------------------------------------------|

| 1    | ETXEN/PMD5/RE5                                            |

| 2    | ETXD0/PMD6/RE6                                            |

| 3    | ETXD1/PMD7/RE7                                            |

| 4    | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              |

| 5    | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               |

| 6    | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              |

| 7    | MCLR                                                      |

| 8    | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              |

| 9    | Vss                                                       |

| 10   | VDD                                                       |

| 11   | AN5/C1IN+/VBUSON/CN7/RB5                                  |

| 12   | AN4/C1IN-/CN6/RB4                                         |

| 13   | AN3/C2IN+/CN5/RB3                                         |

| 14   | AN2/C2IN-/CN4/RB2                                         |

| 15   | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            |

| 16   | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       |

| 17   | PGEC2/AN6/OCFA/RB6                                        |

| 18   | PGED2/AN7/RB7                                             |

| 19   | AVDD                                                      |

| 20   | AVss                                                      |

| 21   | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         |

| 22   | AN9/C2OUT/PMA7/RB9                                        |

| 23   | TMS/AN10/CVrefout/PMA13/RB10                              |

| 24   | TDO/AN11/PMA12/RB11                                       |

| 25   | Vss                                                       |

| 26   | VDD                                                       |

| 27   | TCK/AN12/PMA11/RB12                                       |

| 28   | TDI/AN13/PMA10/RB13                                       |

| 29   | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 |

| 30   | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 |

| 31   | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        |

| 32   | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        |

| Note | 1: Shaded pins are 5V tolerant.                           |

| Pin # | Full Pin Name                                 |

|-------|-----------------------------------------------|

| 33    | USBID/RF3                                     |

| 34    | VBUS                                          |

| 35    | Vusb3v3                                       |

| 36    | D-/RG3                                        |

| 37    | D+/RG2                                        |

| 38    | VDD                                           |

| 39    | OSC1/CLKI/RC12                                |

| 40    | OSC2/CLKO/RC15                                |

| 41    | Vss                                           |

| 42    | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 43    | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 44    | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 45    | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 46    | OC1/INT0/RD0                                  |

| 47    | SOSCI/CN1/RC13                                |

| 48    | SOSCO/T1CK/CN0/RC14                           |

| 49    | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 50    | SDA3/SDI3/U1RX/OC3/RD2                        |

| 51    | SCL3/SDO3/U1TX/OC4/RD3                        |

| 52    | OC5/IC5/PMWR/CN13/RD4                         |

| 53    | PMRD/CN14/RD5                                 |

| 54    | AETXEN/ETXERR/CN15/RD6                        |

| 55    | ETXCLK/AERXERR/CN16/RD7                       |

| 56    | VCAP                                          |

| 57    | VDD                                           |

| 58    | C1RX/AETXD1/ERXD3/RF0                         |

| 59    | C1TX/AETXD0/ERXD2/RF1                         |

| 60    | ERXD1/PMD0/RE0                                |

| 61    | ERXD0/PMD1/RE1                                |

| 62    | ERXDV/ECRSDV/PMD2/RE2                         |

| 63    | ERXCLK/EREFCLKPMD3/RE3                        |

| 64    | ERXERR/PMD4/RE4                               |

- Note 1: Shaded pins are 5V tolerant

- 2: This pin is not available on PIC32MX765F128H devices.

- 3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

#### 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- · Dual Internal Bus interfaces

- · Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- · Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16 bit wide *rs*, 15 iterations are skipped and for a 24 bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

TABLE 3-1: MIPS32® M4K® CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

**NOTES:**

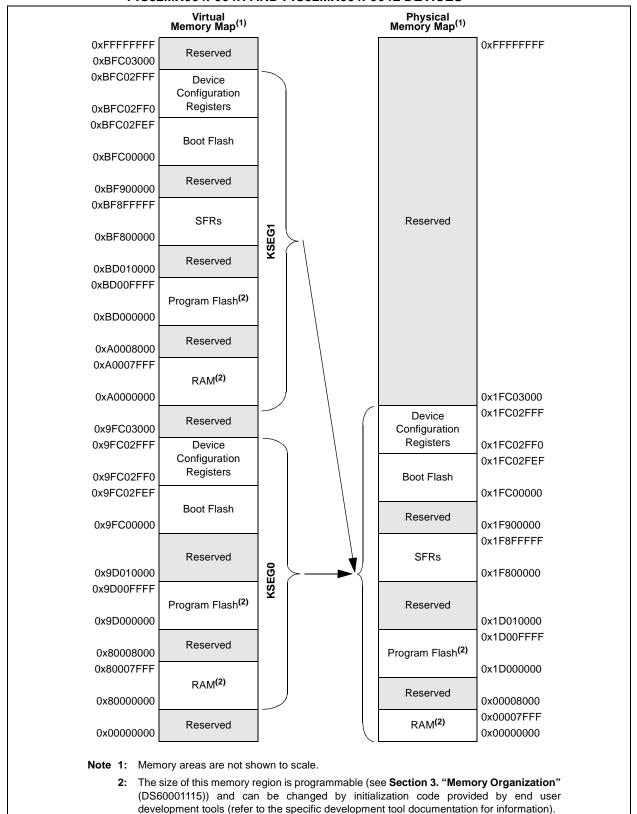

FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX564F064H, PIC32MX564F064L, PIC32MX664F064H AND PIC32MX664F064L DEVICES

### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | _                 |                   | 1                 | 1                 | 1                 |                   | 1                | _                    |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | _                 | _                 | 1                 | 1                 | 1                 |                   | 1                | _                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | 1                 | 1                 | -                 |                   | 1                | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |

Legend: HC = Cleared by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-1 Unimplemented: Read as '0'

bit 0 **SWRST:** Software Reset Trigger bit<sup>(1)</sup>

1 = Enable software Reset event

0 = No effect

Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to **Section** 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

|                             |                                 |           | 10321117 |       |       | 1.0-01                     |             | · /    |                      |                      |      |      |      |             |             |            |                      |                      |            |      |  |  |           |  |       |       |  |

|-----------------------------|---------------------------------|-----------|----------|-------|-------|----------------------------|-------------|--------|----------------------|----------------------|------|------|------|-------------|-------------|------------|----------------------|----------------------|------------|------|--|--|-----------|--|-------|-------|--|

| SSe                         |                                 |           |          |       |       |                            |             |        |                      | В                    | its  |      |      |             |             |            |                      |                      |            |      |  |  |           |  |       |       |  |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14 | 29/13 | 28/12                      | 27/11       | 26/10  | 25/9                 | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4        | 19/3        | 18/2       | 17/1                 | 16/0                 | All Resets |      |  |  |           |  |       |       |  |

| 10D0                        | IPC4                            | 31:16     | ı        | _     | _     | INT4IP<2:0>                |             | INT4IS | S<1:0>               | _                    | I    | I    |      | OC4IP<2:0>  |             | OC4IS<1:0> |                      | 0000                 |            |      |  |  |           |  |       |       |  |

| 1000                        | 11-04                           | 15:0      | I        | _     | _     |                            | IC4IP<2:0>  |        | IC4IS                | <1:0>                | _    | I    | ı    |             | T4IP<2:0>   |            | T4IS                 | :1:0>                | 0000       |      |  |  |           |  |       |       |  |

| 10E0                        | IPC5                            | 31:16     | -        | _     | _     |                            | SPI1IP<2:0> |        |                      | S<1:0>               | _    | -    |      |             | OC5IP<2:0>  | •          | OC5IS                | <1:0>                | 0000       |      |  |  |           |  |       |       |  |

| 1020                        | IPC5                            | 15:0      | I        | _     | _     |                            | IC5IP<2:0>  |        | IC5IS                | <1:0>                | _    | I    | ı    |             | T5IP<2:0>   |            | T5IS-                | :1:0>                | 0000       |      |  |  |           |  |       |       |  |

|                             |                                 | 31:16     | _        | _     | _     |                            | AD1IP<2:0>  | •      | AD1IS                | S<1:0>               | _    | _    | _    |             | CNIP<2:0>   |            | CNIS                 | <1:0>                | 0000       |      |  |  |           |  |       |       |  |

| 1050                        | IPC6                            |           |          |       |       |                            |             |        |                      |                      |      |      |      |             | U1IP<2:0>   |            | U1IS-                | <1:0>                |            |      |  |  |           |  |       |       |  |

| 10F0                        | IPC6                            | 15:0      | _        | _     | _     | I2C1IP<2:0>                |             |        | 12C1IS               | I2C1IS<1:0>          |      | _    | _    | SPI3IP<2:0> |             |            | SPI3IS<1:0>          |                      | 0000       |      |  |  |           |  |       |       |  |

|                             |                                 |           |          |       |       |                            |             |        |                      |                      |      |      |      |             | I2C3IP<2:0> | •          | I2C3IS<1:0>          |                      |            |      |  |  |           |  |       |       |  |

|                             |                                 |           |          |       |       |                            | U3IP<2:0>   |        | U3IS-                | <1:0>                |      |      |      |             |             |            |                      |                      |            |      |  |  |           |  |       |       |  |

| 1100                        | 00 IPC7                         | 31:16     | _        | _     | _     |                            | SPI2IP<2:0> | •      | SPI2IS               | S<1:0>               | _    | _    | _    | (           | CMP2IP<2:0  | >          | CMP2I                | S<1:0>               | 0000       |      |  |  |           |  |       |       |  |

| 1100                        | IPC/                            |           |          |       |       |                            | I2C4IP<2:0> | •      | 12C4IS               | S<1:0>               |      |      |      |             |             |            |                      |                      |            |      |  |  |           |  |       |       |  |

|                             |                                 | 15:0      | I        | _     | _     | (                          | CMP1IP<2:0> |        | CMP1I                | S<1:0>               | _    |      | -    | PMPIP<2:0>  |             | PMPIP<2:0> |                      | PMPIS                | i<1:0>     | 0000 |  |  |           |  |       |       |  |

|                             |                                 | 31:16     | I        | _     | _     | F                          | RTCCIP<2:0> |        | RTCCI                | S<1:0>               | _    | I    | ı    | FSCMIP<2:0> |             | FSCMI      | S<1:0>               | 0000                 |            |      |  |  |           |  |       |       |  |

| 1110                        | IPC8                            |           |          |       |       |                            |             |        |                      |                      |      | ·    |      |             |             |            |                      |                      |            |      |  |  | U2IP<2:0> |  | U2IS- | <1:0> |  |

| 1110                        | IPCo                            | 15:0      | _        | _     | _     |                            | I2C2IP<2:0> | •      | 12C2IS               | S<1:0>               | _    | _    | _    |             | SPI4IP<2:0> | •          | SPI4IS<1:0>          | 0000                 |            |      |  |  |           |  |       |       |  |

|                             |                                 |           |          |       |       |                            |             |        |                      |                      |      |      |      |             | I2C5IP<2:0> | •          | 12C51S               | <1:0>                | ]!         |      |  |  |           |  |       |       |  |

| 1120                        | IPC9                            | 31:16     | -        | _     | _     | [                          | DMA3IP<2:0  | >      | DMA3I                | S<1:0>               | _    | _    | -    | [           | DMA2IP<2:0  | >          | DMA2I                | S<1:0>               | 0000       |      |  |  |           |  |       |       |  |

| 1120                        | IPC9                            | 15:0      | I        | _     | _     | [                          | DMA1IP<2:0  | >      | DMA1I                | S<1:0>               | _    |      | -    | [           | OMA0IP<2:0  | >          | DMA0I                | S<1:0>               | 0000       |      |  |  |           |  |       |       |  |

| 1130                        | IPC10                           | 31:16     | I        | _     | _     |                            | MA7IP<2:0>  |        | DMA7IS               | <1:0> <sup>(2)</sup> | _    | I    | ı    |             | MA6IP<2:0>  |            | DMA6IS               | <1:0> <sup>(2)</sup> | 0000       |      |  |  |           |  |       |       |  |

| 1130                        | IFCIU                           | 15:0      | I        | _     | _     | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS | <1:0> <sup>(2)</sup> | _                    | I    | ı    | D    | MA4IP<2:0>  | (2)         | DMA4IS     | <1:0> <sup>(2)</sup> | 0000                 |            |      |  |  |           |  |       |       |  |

| 1140                        | IPC11                           | 31:16     | I        | _     | _     |                            |             | _      | _                    | -                    | _    | I    | -    | _           |             |            | _                    | _                    | 0000       |      |  |  |           |  |       |       |  |

| 1140                        | IFUII                           | 15:0      | _        | _     | _     |                            | USBIP<2:0>  | ·      | USBIS                | S<1:0>               | _    | -    | _    |             | FCEIP<2:0>  |            | FCEIS                | <1:0>                | 0000       |      |  |  |           |  |       |       |  |

| 1150                        | IPC12                           | 31:16     | ı        | _     | _     |                            | U5IP<2:0>   |        | U5IS-                | <1:0>                | _    | ı    | ı    | U6IP<2:0>   |             | U6IS-      | <1:0>                | 0000                 |            |      |  |  |           |  |       |       |  |

| 1130                        | IFC12                           | 15:0      | _        | _     | _     |                            | U4IP<2:0>   |        | U4IS-                | <1:0>                | _    | _    | _    |             | ETHIP<2:0>  |            | ETHIS                | <1:0>                | 0000       |      |  |  |           |  |       |       |  |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

- 2: These bits are not available on PIC32MX664 devices.

- 3: This register does note have associated CLR, SET, and INV registers.

| 0          |  |

|------------|--|

| 2009-2016  |  |

| Microchip  |  |

| Technology |  |

| y Inc.     |  |

| ess                         |                                 |                                   |        |       |       |       |       | -     | 1025) | Ві      | its     |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------------------------------|--------|-------|-------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                         | 31/15  | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8    | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16                             | _      | _     | _     | _     |       | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3100                        | DOITIDGIZ                       | 15:0                              |        |       |       |       |       |       |       | CHDSIZ  | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 0100                        | DOITION III                     | 15:0 CHSPTR<15:0>                 |        |       |       |       |       |       |       | ı       | ı       | 0000   |        |        |        |        |        |        |            |

| 31A0                        | DCH1DPTR                        | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 0 17 10                     | 5011151 111                     | 15:0                              |        | 1     | 1     |       |       | 1     | ı     | CHDPT   | R<15:0> |        | 1      | 1      | 1      | 1      | 1      | ı      | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16                             |        | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0                              |        | 1     | 1     |       |       | 1     | 1     | CHCSIZ  | Z<15:0> |        | 1      | 1      | 1      | 1      | 1      | 1      | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0                              |        |       |       |       |       |       |       | CHCPT   | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16                             |        | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      |        |        | _      | _      | _      | 0000       |

| -                           |                                 | 15:0                              | _      | _     | _     | _     |       | _     | _     | _       |         | 1      |        | CHPDA  |        |        |        |        | 0000       |

| 31E0                        | DCH2CON                         | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0                              | CHBUSY | _     | _     | _     | _     | _     | _     | CHCHNS  | CHEN    | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 31F0                        | DCH2ECON                        | 31:16 — — — — — — — — CHAIRQ<7:0> |        |       |       |       |       |       | I     | 00FF    |         |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0                              |        |       |       | CHSIR |       |       |       | 1       | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      |        |        | FF00       |

| 3200                        | )()   D(CH2INI   -              | 31:16                             |        | _     | _     | _     |       | _     | _     | _       | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0                              | _      | _     | _     | _     | _     | _     | _     | _       | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0                     |        |       |       |       |       |       |       | CHSSA   | N<31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16                             |        |       |       |       |       |       |       |         |         |        |        |        |        |        |        |        | 0000       |

| 3220                        | DCH2DSA                         | 15:0                              |        |       |       |       |       |       |       | CHDSA   | N<31:0> |        |        |        |        |        |        |        | 0000       |

| 0000                        | DOL100017                       | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0                              |        |       | •     |       |       |       | •     | CHSSIZ  | Z<15:0> | •      | •      |        | •      | •      |        | •      | 0000       |

| 2040                        | DOLLODOLZ                       | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0                              |        |       |       |       |       |       |       | CHDSIZ  | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 0050                        | DOLLOODED                       | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3250                        | DCH2SPTR                        | 15:0                              |        |       |       |       |       |       |       | CHSPTI  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 0000                        | DOLIODDED                       | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3260                        | DCH2DPTR                        | 15:0                              |        |       |       |       |       |       |       | CHDPT   | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 2270                        | DCHOCOLZ                        | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0                              |        |       |       |       |       |       |       | CHCSIZ  | Z<15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16                             | _      | _     | _     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3280                        | DCH2CPTR                        | 15:0                              |        |       |       |       |       |       |       | CHCPT   | R<15:0> |        |        |        |        |        |        |        | 0000       |

| Ь                           | i                               | 10.0                              |        |       |       |       |       |       |       | 0.101 1 | 10.02   |        |        |        |        |        |        |        | 3000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1:

<sup>2:</sup> DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

#### REGISTER 11-5: **U1PWRC: USB POWER CONTROL REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | 1                 | -                 | -                 |                   | -                 | -                 | _                | 1                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | _                 | _                 | _                 | _                | 1                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | 1                 | _                 | _                 | _                 | _                 | _                 | _                | 1                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | _                 | _                 | USLPGRD           | USBBUSY           | _                 | USUSPEND         | USBPWR           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **UACTPND:** USB Activity Pending bit

1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

bit 6-5 Unimplemented: Read as '0'

bit 4 **USLPGRD:** USB Sleep Entry Guard bit

1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

0 = USB module does not block Sleep entry

bit 3 **USBBUSY:** USB Module Busy bit

1 = USB module is active or disabled, but not ready to be enabled

0 = USB module is not active and is ready to be enabled

When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all

USB module registers produce undefined results.

bit 2 Unimplemented: Read as '0'

bit 1 **USUSPEND:** USB Suspend Mode bit

1 = USB module is placed in Suspend mode

(The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

0 = USB module operates normally

bit 0 **USBPWR:** USB Operation Enable bit

1 = USB module is turned on

0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power

consumption.)

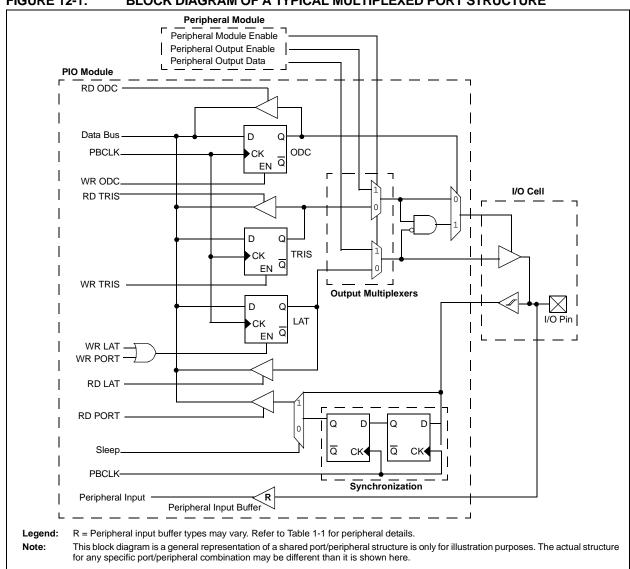

## 12.0 **I/O PORTS**

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 12.** "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC32 MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual output pin open-drain enable/disable

- Individual input pin weak pull-up enable/disable

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

FIGURE 12-1: BLOCK DIAGRAM OF A TYPICAL MULTIPLEXED PORT STRUCTURE

REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized 0 = External clock input is not synchronized

When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit

1 = External clock from TxCKI pin0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 24.24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31:24        | _                    | _                 | -                   | -                 | _                  | -                 | _                  | -                |

| 23:16        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23.10        | -                    | _                 | -                   | -                 | _                  | -                 | _                  | 1                |

| 15.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | _                  | _                 | _                  | -                |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

1 = Module is enabled 0 = Module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

1 = Discontinue operation when device enters Idle mode

0 = Continue operation when device is in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

111 = 1:256 prescale value

110 = 1:64 prescale value

101 = 1:32 prescale value

100 = 1:16 prescale value

011 = 1:8 prescale value

010 = 1:4 prescale value

001 = 1:2 prescale value

000 = 1:1 prescale value

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

REGISTER 16-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 22:40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 | _                 | -                 | _                |                  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             | ICM<2:0>          |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Input Capture Module Enable bit (1)

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = Halt in Idle mode

0 = Continue to operate in Idle mode

bit 12-10 **Unimplemented:** Read as '0'

bit 9 **FEDGE:** First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first0 = Capture falling edge first

bit 8 C32: 32-bit Capture Select bit

1 = 32-bit timer resource capture 0 = 16-bit timer resource capture

bit 7 ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')

1 = Timer2 is the counter source for capture 0 = Timer3 is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow is occurred0 = No input capture overflow is occurred

bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

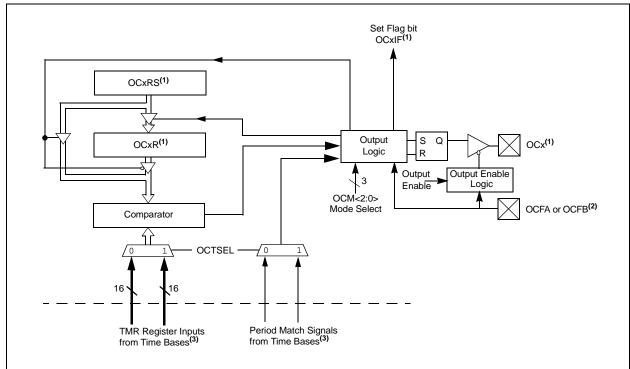

## 17.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Output Compare module is used to generate a single pulse or a series of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of the Output Compare module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Programmable selection of 16-bit or 32-bit time bases

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- **Note 1:** Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 5.

- **2:** The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

- 3: Each output compare channel can use one of two selectable 16-bit time bases or a single 32-bit timer base.

## 20.1 Control Registers

## TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP

| 0.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SS                          | LL 20-1.              |           |        |         | JII OAK |       |        |       |       | Bi     | ts     |         |       |          |          |      |        |       |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------|-----------|--------|---------|---------|-------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| 000   01500E    150   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015    | Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14   | 29/13   | 28/12 | 27/11  | 26/10 | 25/9  |        |        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6000                        | U1MODE <sup>(1)</sup> |           |        | _       |         |       |        | -     | -     | _      |        |         |       |          |          |      | _      | -     |            |

| 17   17   17   18   17   17   18   17   18   18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | 01111022              | _         | ON     | _       | SIDL    | IREN  | RTSMD  |       | UEN-  |        | WAKE   | LPBACK  | ABAUD |          |          | PDSE | L<1:0> | STSEL | 0000       |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6010                        | U1STA <sup>(1)</sup>  |           | _      |         |         | _     |        |       |       |        |        |         |       |          |          | 1    | 1      |       | -          |

| Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                       |           | UTXISE | L<1:0>  | UTXINV  | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA |            |

| 15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6020                        | U1TXREG               |           | _      | _       | _       |       |        |       |       |        |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                       |           | _      | _       | _       |       |        |       |       | TX8    |        | ı       |       | Transmit | Register | 1    |        |       | _          |

| March   Marc | 6030                        | 30 U1RXREG            |           | _      | _       | _       | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | _          |

| BRG   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |                       |           | _      | _       | _       | _     |        |       |       | RX8    |        | ı       |       | Receive  | Register | 1    |        |       |            |

| 0000   04MODE   03116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6040                        | U1BRG <sup>(1)</sup>  |           | _      | _       | _       | _     | _      | _     | _     | _      |        | _       | _     | _        | _        | _    | _      | _     | _          |

| MANOPETON   15.0   ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             | •                     | 15:0      |        | 1       | 1       |       |        |       |       | BRG<   | :15:0> | 1       |       | 1        | 1        | 1    |        |       |            |