Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512ht-80v-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

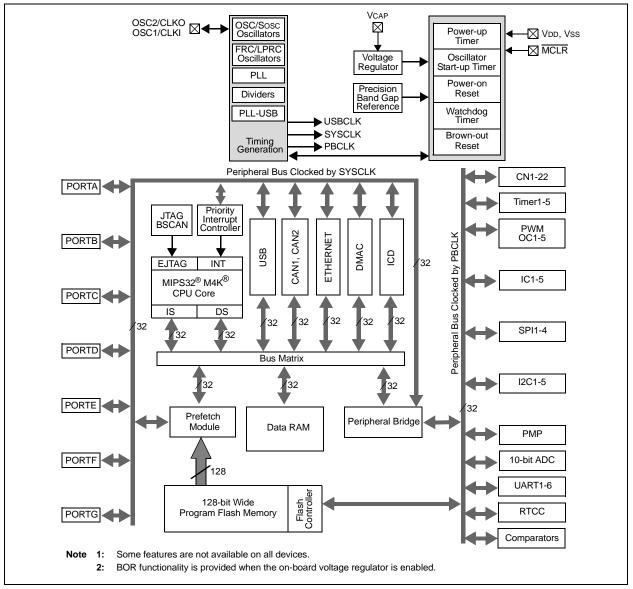

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| TABLE 7-1: INTERRUPT IRQ                                                            | VECTOR | AND BIT | BIT LOCATION (CONTINUED) |          |              |              |  |  |  |

|-------------------------------------------------------------------------------------|--------|---------|--------------------------|----------|--------------|--------------|--|--|--|

| Interrupt Source <sup>(1)</sup>                                                     | IRQ    | Vector  | Interrupt Bit Location   |          |              |              |  |  |  |

| interrupt Source ?                                                                  | Number | Number  | Flag                     | Enable   | Priority     | Sub-Priority |  |  |  |

| AD1 – ADC1 Convert Done                                                             | 33     | 27      | IFS1<1>                  | IEC1<1>  | IPC6<28:26>  | IPC6<25:24>  |  |  |  |

| PMP – Parallel Master Port                                                          | 34     | 28      | IFS1<2>                  | IEC1<2>  | IPC7<4:2>    | IPC7<1:0>    |  |  |  |

| CMP1 – Comparator Interrupt                                                         | 35     | 29      | IFS1<3>                  | IEC1<3>  | IPC7<12:10>  | IPC7<9:8>    |  |  |  |

| CMP2 – Comparator Interrupt                                                         | 36     | 30      | IFS1<4>                  | IEC1<4>  | IPC7<20:18>  | IPC7<17:16>  |  |  |  |

| U2E – UART2 Error<br>SPI2E – SPI2 Fault<br>I2C4B – I2C4 Bus Collision Event         | 37     | 31      | IFS1<5>                  | IEC1<5>  | IPC7<28:26>  | IPC7<25:24>  |  |  |  |

| U2RX – UART2 Receiver<br>SPI2RX – SPI2 Receive Done<br>I2C4S – I2C4 Slave Event     | 38     | 31      | IFS1<6>                  | IEC1<6>  | IPC7<28:26>  | IPC7<25:24>  |  |  |  |

| U2TX – UART2 Transmitter<br>SPI2TX – SPI2 Transfer Done<br>IC4M – I2C4 Master Event | 39     | 31      | IFS1<7>                  | IEC1<7>  | IPC7<28:26>  | IPC7<25:24>  |  |  |  |

| U3E – UART3 Error<br>SPI4E – SPI4 Fault<br>I2C5B – I2C5 Bus Collision Event         | 40     | 32      | IFS1<8>                  | IEC1<8>  | IPC8<4:2>    | IPC8<1:0>    |  |  |  |

| U3RX – UART3 Receiver<br>SPI4RX – SPI4 Receive Done<br>I2C5S – I2C5 Slave Event     | 41     | 32      | IFS1<9>                  | IEC1<9>  | IPC8<4:2>    | IPC8<1:0>    |  |  |  |

| U3TX – UART3 Transmitter<br>SPI4TX – SPI4 Transfer Done<br>IC5M – I2C5 Master Event | 42     | 32      | IFS1<10>                 | IEC1<10> | IPC8<4:2>    | IPC8<1:0>    |  |  |  |

| I2C2B – I2C2 Bus Collision Event                                                    | 43     | 33      | IFS1<11>                 | IEC1<11> | IPC8<12:10>  | IPC8<9:8>    |  |  |  |

| I2C2S – I2C2 Slave Event                                                            | 44     | 33      | IFS1<12>                 | IEC1<12> | IPC8<12:10>  | IPC8<9:8>    |  |  |  |

| I2C2M – I2C2 Master Event                                                           | 45     | 33      | IFS1<13>                 | IEC1<13> | IPC8<12:10>  | IPC8<9:8>    |  |  |  |

| FSCM – Fail-Safe Clock Monitor                                                      | 46     | 34      | IFS1<14>                 | IEC1<14> | IPC8<20:18>  | IPC8<17:16>  |  |  |  |

| RTCC – Real-Time Clock and<br>Calendar                                              | 47     | 35      | IFS1<15>                 | IEC1<15> | IPC8<28:26>  | IPC8<25:24>  |  |  |  |

| DMA0 – DMA Channel 0                                                                | 48     | 36      | IFS1<16>                 | IEC1<16> | IPC9<4:2>    | IPC9<1:0>    |  |  |  |

| DMA1 – DMA Channel 1                                                                | 49     | 37      | IFS1<17>                 | IEC1<17> | IPC9<12:10>  | IPC9<9:8>    |  |  |  |

| DMA2 – DMA Channel 2                                                                | 50     | 38      | IFS1<18>                 | IEC1<18> | IPC9<20:18>  | IPC9<17:16>  |  |  |  |

| DMA3 – DMA Channel 3                                                                | 51     | 39      | IFS1<19>                 | IEC1<19> | IPC9<28:26>  | IPC9<25:24>  |  |  |  |

| DMA4 – DMA Channel 4                                                                | 52     | 40      | IFS1<20>                 | IEC1<20> | IPC10<4:2>   | IPC10<1:0>   |  |  |  |

| DMA5 – DMA Channel 5                                                                | 53     | 41      | IFS1<21>                 | IEC1<21> | IPC10<12:10> | IPC10<9:8>   |  |  |  |

| DMA6 – DMA Channel 6                                                                | 54     | 42      | IFS1<22>                 | IEC1<22> | IPC10<20:18> | IPC10<17:16> |  |  |  |

| DMA7 – DMA Channel 7                                                                | 55     | 43      | IFS1<23>                 | IEC1<23> | IPC10<28:26> | IPC10<25:24> |  |  |  |

| FCE – Flash Control Event                                                           | 56     | 44      | IFS1<24>                 | IEC1<24> | IPC11<4:2>   | IPC11<1:0>   |  |  |  |

| USB – USB Interrupt                                                                 | 57     | 45      | IFS1<25>                 | IEC1<25> | IPC11<12:10> | IPC11<9:8>   |  |  |  |

| CAN1 – Control Area Network 1                                                       | 58     | 46      | IFS1<26>                 | IEC1<26> | IPC11<20:18> | IPC11<17:16> |  |  |  |

| CAN2 – Control Area Network 2                                                       | 59     | 47      | IFS1<27>                 | IEC1<27> | IPC11<28:26> | IPC11<25:24> |  |  |  |

| ETH – Ethernet Interrupt                                                            | 60     | 48      | IFS1<28>                 | IEC1<28> | IPC12<4:2>   | IPC12<1:0>   |  |  |  |

| IC1E – Input Capture 1 Error                                                        | 61     | 5       | IFS1<29>                 | IEC1<29> | IPC1<12:10>  | IPC1<9:8>    |  |  |  |

| IC2E – Input Capture 2 Error                                                        | 62     | 9       | IFS1<30>                 | IEC1<30> | IPC2<12:10>  | IPC2<9:8>    |  |  |  |

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

## TABLE 12-7: PORTE REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H,

#### PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES Virtual Address (BF88\_#) Bits Resets Bit Range Register Name<sup>(1)</sup> 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 ₹ 31:16 \_ 0000 \_ 6100 TRISE 15:0 TRISE7 TRISE6 TRISE5 TRISE4 TRISE3 TRISE2 TRISE1 TRISE0 00FF \_ \_ \_ \_ \_ \_ 31:16 0000 PORTE 6110 15:0 \_ \_ \_ \_ \_ \_ RE7 RE6 RE5 RE4 RE3 RE2 RE1 RE0 xxxx \_ \_ 0000 31:16 \_ \_ \_ \_ 6120 LATE 15:0 \_ \_ \_ \_ \_ \_ \_ \_ LATE7 LATE6 LATE5 LATE4 LATE3 LATE2 LATE1 LATE0 xxxx 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ 6130 ODCE 15:0 \_ \_ \_ ODCE7 0DCE6 ODCE5 ODCE4 ODCE3 ODCE2 ODCE1 ODCE0 0000 Leaend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 12-8: PORTE REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                        |                                 | e         |       |       |       |       |       |       |        | Bi     | its    |        |        |        |        |        |        |        | s          |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6100                       | TRISE                           | 31:16     | _     | _     | -     | _     | -     | _     | _      | —      | _      | _      | -      | —      | _      | —      | -      | _      | 0000       |

| 6100                       | IRISE                           | 15:0      | Ι     | _     | _     | -     | _     | _     | TRISE9 | TRISE8 | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 03FF       |

| 6110                       | PORTE                           | 31:16     | -     | —     | —     | _     | -     | —     | —      | —      | —      | —      | -      | —      | —      | —      |        | _      | 0000       |

| 6110                       | PORTE                           | 15:0      | -     | —     | _     | _     | _     | _     | RE9    | RE8    | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx       |

| C4 00                      | LATE                            | 31:16     | -     | _     | _     | -     | -     | _     | _      | _      | _      | _      | -      | _      | _      | _      | -      | _      | 0000       |

| 6120                       | LATE                            | 15:0      | —     | _     | _     | —     | _     | _     | LATE9  | LATE8  | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx       |

| 6130                       | ODCE                            | 31:16     | _     | -     |       | _     | _     |       |        |        |        |        | —      |        |        |        | —      | —      | 0000       |

| 0130                       | ODCE                            | 15:0      | _     | _     | _     | —     | _     | _     | ODCE9  | ODCE8  | ODCE7  | 0DCE6  | ODCE5  | ODCE4  | ODCE3  | ODCE2  | ODCE1  | ODCE0  | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

| Т | TABLE 12-11:         PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, |  |      |  |  |  |  |  |  |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------|--|--|--|--|--|--|--|--|

|   | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                        |  |      |  |  |  |  |  |  |  |  |

|   | ssa                                                                                                                                                                                                  |  | Bits |  |  |  |  |  |  |  |  |

| ö                          |                                 | Φ         |       | 2.13 v |       |       |           |                    |        |                 |        |        |      |      |        |        |      |      |           |

|----------------------------|---------------------------------|-----------|-------|--------|-------|-------|-----------|--------------------|--------|-----------------|--------|--------|------|------|--------|--------|------|------|-----------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11     | 26/10              | 25/9   | 24/8            | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset |

| 6180                       | TRISG                           | 31:16     | —     | —      | —     | _     | —         | —                  | _      | —               | —      | —      | _    | _    | -      | _      | _    | _    | 0000      |

| 6160                       | TRIBU                           | 15:0      | _     | _      | _     | _     | _         |                    | TRISG9 | TRISG8          | TRISG7 | TRISG6 | _    |      | TRISG3 | TRISG2 | -    |      | 03CC      |

| 6100                       | PORTG                           | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000      |

| 6190                       | PURIG                           | 15:0      | _     | _      | _     | _     | _         |                    | RG9    | RG8             | RG7    | RG6    | _    |      | RG3    | RG2    | -    |      | xxxx      |

| 61A0                       | LATG                            | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000      |

| OTAU                       | LAIG                            | 15:0      | _     | _      | _     | _     | _         |                    | LATG9  | LATG8           | LATG7  | LATG6  | _    |      | LATG3  | LATG2  | -    |      | xxxx      |

| 61B0                       | ODCG                            | 31:16     | -     | _      | _     | _     | -         | _                  | _      | _               | _      | -      | _    |      |        | -      | _    |      | 0000      |

| 0180                       | ODCG                            | 15:0      | -     | _      | _     | _     | -         | _                  | ODCG9  | ODCG8           | ODCG7  | ODCG6  | _    |      | ODCG3  | ODCG2  | _    |      | 0000      |

| Laware                     |                                 |           |       | Divisi |       |       | fal Deset | alter a successful |        | dia statistical |        |        |      |      |        |        |      |      |           |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 |           |         | Bits    |         |         |       |       |        |        |        |        |      |      |        | <i>(</i> 0 |        |        |            |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|------------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2       | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -          | -      | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2     | TRISG1 | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —          | _      | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      | -    | RG3    | RG2        | RG1    | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —          | —      | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2      | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —          | —      | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2      | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

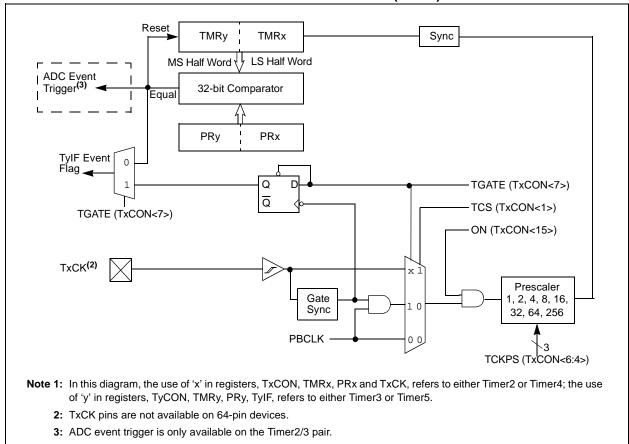

#### FIGURE 14-2: TIMER2/3 AND TIMER4/5 BLOCK DIAGRAM (32-BIT)

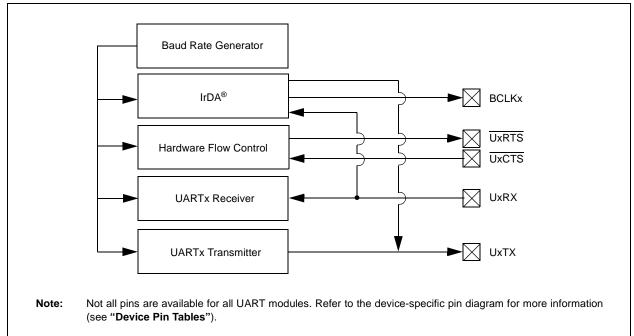

### 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in the PIC32MX5XX/6XX/7XX family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

The following are primary features of the UART module:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (ninth bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- LIN 2.1 Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 20-1 illustrates a simplified block diagram of the UART module.

#### FIGURE 20-1: UART SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range                                           | Bit<br>31/23/15/7  | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------------------------------------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24                                                  | U-0                | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24                                                  | —                  | _                  |                   |                   |                   | _                 | _                |                  |  |

| 23:16                                                  | U-0                | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16                                                  | —                  | —                  | _                 | _                 | _                 | —                 |                  | _                |  |

|                                                        | R/W-0              | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8                                                   | CS2 <sup>(1)</sup> | CS1 <sup>(3)</sup> |                   |                   |                   | .4.2.0            |                  |                  |  |

| ADDR15 <sup>(2)</sup> ADDR14 <sup>(4)</sup> ADDR<13:8> |                    |                    |                   |                   |                   |                   |                  |                  |  |

| 7:0                                                    | R/W-0              | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|                                                        | ADDR<7:0>          |                    |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

#### Legend:

| 5                 |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

- bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup>

11111111 = Alarm will trigger 256 times

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

<li

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is only reset on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2                  | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------------|------------------------------------|------------------|------------------|--|--|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x                              | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   | HR10-             | <3:0>             |                   |                                          | HR01                               | <3:0>            |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x                              | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                               |                                    |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x                              | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                   |                                          | SEC01                              | <3:0>            |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                      | U-0                                | U-0              | U-0              |  |  |  |

| 7:0          | —                 | —                 | _                 | _                 | —                                        | _                                  | —                | _                |  |  |  |

|              |                   |                   |                   |                   |                                          |                                    |                  |                  |  |  |  |

| Legend:      |                   |                   |                   |                   |                                          |                                    |                  |                  |  |  |  |

| R = Read     | able bit          |                   | W = Writable bit  |                   |                                          | U = Unimplemented bit, read as '0' |                  |                  |  |  |  |

| -n = Value   | e at POR          |                   | '1' = Bit is se   | t                 | 0' = Bit is cleared $x = Bit is unknown$ |                                    |                  |                  |  |  |  |

#### REGISTER 22-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

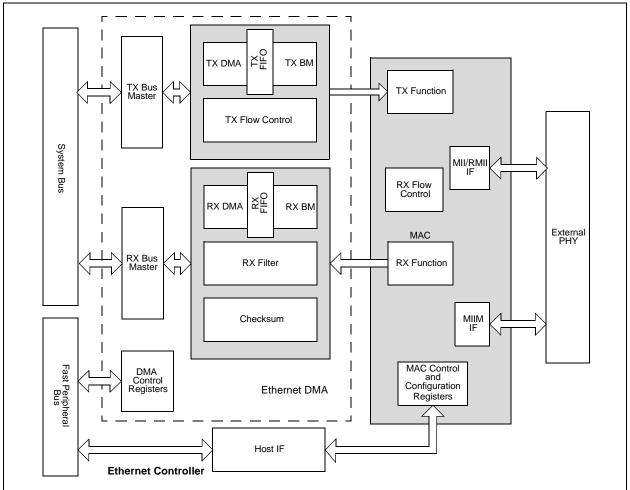

### 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

#### FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

### REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 | _                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   |                   |                   | —                |                  |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | HTEN              | MPEN              | _                 | NOTPM             |                   | PMMODE            | <3:0>            |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **HTEN:** Enable Hash Table Filtering bit

- 1 = Enable Hash Table Filtering

- 0 = Disable Hash Table Filtering

- bit 14 **MPEN:** Magic Packet<sup>™</sup> Enable bit 1 = Enable Magic Packet Filtering 0 = Disable Magic Packet Filtering

- bit 13 Unimplemented: Read as '0'

- bit 12 **NOTPM:** Pattern Match Inversion bit

- 1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

- 0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 PMMODE<3:0>: Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)<sup>(1,3)</sup>

- 1000 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Hash Table Filter match)<sup>(1,2)</sup>

- 0111 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0110 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0101 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0100 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0011 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0010 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches)<sup>(1)</sup>

- 0000 = Pattern Match is disabled; pattern match is always unsuccessful

#### **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|

| 31:24        | U-0                      | U-0                     |

| 31.24        | —                 | —                 | -                 | _                 | —                 | -                 | —                        | —                       |

| 23:16        | U-0                      | U-0                     |

| 23.10        | —                 | —                 | -                 | _                 | —                 | -                 | —                        | _                       |

| 15:8         | U-0                      | U-0                     |

| 15.0         | —                 | —                 | -                 | _                 | —                 | -                 | —                        | —                       |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   |

| 7.0          |                   | —                 |                   |                   | _                 | TESTBP            | TESTPAUSE <sup>(1)</sup> | SHRTQNTA <sup>(1)</sup> |

#### REGISTER 25-30: EMAC1TEST: ETHERNET CONTROLLER MAC TEST REGISTER

#### Legend:

| Logonan           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 TESTBP: Test Backpressure bit

- 1 = The MAC will assert backpressure on the link. Backpressure causes preamble to be transmitted, raising carrier sense. A transmit packet from the system will be sent during backpressure.

0 = Normal operation

#### bit 1 **TESTPAUSE:** Test PAUSE bit<sup>(1)</sup>

- 1 = The MAC Control sub-layer will inhibit transmissions, just as if a PAUSE Receive Control frame with a non-zero pause time parameter was received

- 0 = Normal operation

#### bit 0 SHRTQNTA: Shortcut PAUSE Quanta bit<sup>(1)</sup>

- 1 = The MAC reduces the effective PAUSE Quanta from 64 byte-times to 1 byte-time

- 0 = Normal operation

- **Note 1:** This bit is only for testing purposes.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

#### REGISTER 25-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 51.24        | —                 | —                 | _                 | _                 | _                     | _                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 15.0         | RESETMGMT         | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-1             | R/W-0             | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 |                   | CLKSEL            | _<3:0> <sup>(1)</sup> |                   | NOPRE            | SCANINC          |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 RESETMGMT: Test Reset MII Management bit

- 1 = Reset the MII Management module

- 0 = Normal Operation

#### bit 14-6 **Unimplemented:** Read as '0'

bit 5-2 CLKSEL<3:0>: MII Management Clock Select 1 bits<sup>(1)</sup>

These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

#### bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

#### bit 0 SCANINC: Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

- Note 1: Table 25-7 provides a description of the clock divider encoding.

| Note: | Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). |

|-------|------------------------------------------------------------------------------------------------------------|

|       | 8-bit accesses are not allowed and are ignored by the hardware.                                            |

#### TABLE 25-7: MIIM CLOCK SELECTION

| MIIM Clock Select    | EMAC1MCFG<5:2>        |

|----------------------|-----------------------|

| SYSCLK divided by 4  | 000x                  |

| SYSCLK divided by 6  | 0010                  |

| SYSCLK divided by 8  | 0011                  |

| SYSCLK divided by 10 | 0100                  |

| SYSCLK divided by 14 | 0101                  |

| SYSCLK divided by 20 | 0110                  |

| SYSCLK divided by 28 | 0111                  |

| SYSCLK divided by 40 | 1000                  |

| Undefined            | Any other combination |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 | _                 | -                 | _                 | _                 | _                | —                |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |

| 45.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 15:8         |                   | STNADDR2<7:0>     |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 7:0          |                   |                   |                   | STNADDR           | 1<7:0>            |                   |                  |                  |  |

#### REGISTER 25-39: EMAC1SA2: ETHERNET CONTROLLER MAC STATION ADDRESS 2 REGISTER

| Legend:           | P = Programmable bit |                                    |                    |

|-------------------|----------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-16 Reserved: Maintain as '0'; ignore read

- bit 15-8 **STNADDR2<7:0>:** Station Address Octet 2 bits These bits hold the second transmitted octet of the station address.

- bit 7-0 **STNADDR1<7:0>:** Station Address Octet 1 bits These bits hold the most significant (first transmitted) octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

#### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

#### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                      | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 23.10        |                   |                   | _                 |                   | —                 | _                      |                  |                  |

| 15.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | R/W-0                  | R/W-0            | R/W-1            |

| 15:8         | ON <sup>(1)</sup> | —                 | —                 | —                 | —                 | VREFSEL <sup>(2)</sup> | BGSEL            | <1:0> <b>(2)</b> |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0            | R/W-0            |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             |                   | CVR<                   | :3:0>            |                  |

#### REGISTER 27-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

ON: Comparator Voltage Reference On bit<sup>(1)</sup> bit 15 Setting or clearing this bit does not affect the other bits in this register. 1 = Module is enabled0 = Module is disabled and does not consume current bit 14-11 Unimplemented: Read as '0' VREFSEL: Voltage Reference Select bit<sup>(2)</sup> bit 10 1 = CVREF = VREF+0 = CVREF is generated by the resistor network BGSEL<1:0>: Band Gap Reference Source bits<sup>(2)</sup> bit 9-8 11 = IVRFF = VRFF+10 = Reserved 01 = IVREF = 0.6V (nominal, default)

- 00 = IVREF = 1.2V (nominal)

- bit 7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

#### bit 5 **CVRR:** CVREF Range Selection bit

- 1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.719 CVRSRC, with CVRSRC/32 step size

#### bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

- bit 3-0 When CVRR = 1:  $CVREF = (CVR < 3:0 > /24) \bullet (CVRSRC)$ When CVRR = 0:  $CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)$

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: These bits are not available on PIC32MX575/675/775/795 devices. On these devices, the reset value for CVRON is '0000'.

#### 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

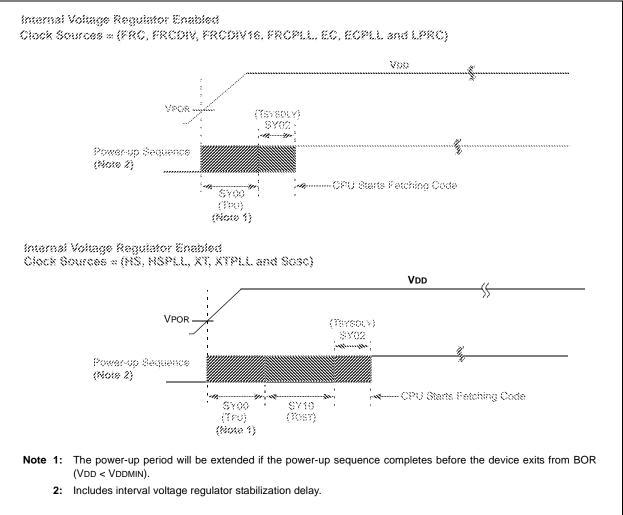

### FIGURE 32-4: POWER-ON RESET TIMING CHARACTERISTICS

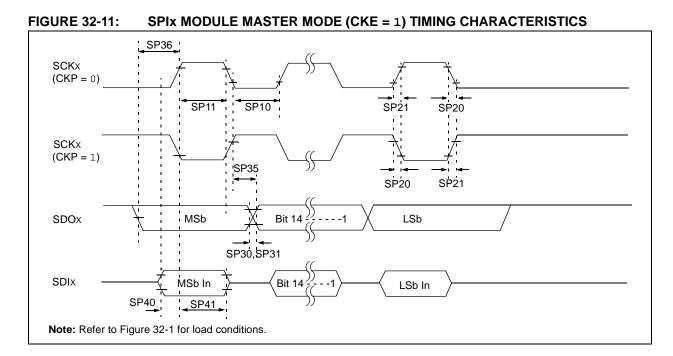

#### TABLE 32-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                     |      |       |                    |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                              | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>          | Tsck/2                                                                                                                                                                                                                                                                            | —                   | _    | ns    | —                  |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>         | Tsck/2                                                                                                                                                                                                                                                                            | —                   | _    | ns    | —                  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>         | —                                                                                                                                                                                                                                                                                 | —                   | —    | ns    | See parameter DO32 |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>         | _                                                                                                                                                                                                                                                                                 | —                   | _    | ns    | See parameter DO31 |

| SP30               | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>    | _                                                                                                                                                                                                                                                                                 | —                   |      | ns    | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>    | —                                                                                                                                                                                                                                                                                 | —                   | _    | ns    | See parameter DO31 |

| SP35               | TSCH2DOV,<br>TSCL2DOV | SDOx Data Output Valid after<br>SCKx Edge    |                                                                                                                                                                                                                                                                                   | —                   | 15   | ns    | VDD > 2.7V         |

|                    |                       |                                              |                                                                                                                                                                                                                                                                                   | —                   | 20   | ns    | Vdd < 2.7V         |

| SP36               | TDOV2SC,<br>TDOV2SCL  | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                                                                                                                                                                                                                                                | —                   |      | ns    | —                  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge   | 15                                                                                                                                                                                                                                                                                | —                   |      | ns    | VDD > 2.7V         |

|                    |                       |                                              | 20                                                                                                                                                                                                                                                                                | —                   |      | ns    | VDD < 2.7V         |

| SP41               | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input<br>to SCKx Edge | 15                                                                                                                                                                                                                                                                                | —                   |      | ns    | VDD > 2.7V         |

|                    |                       |                                              | 20                                                                                                                                                                                                                                                                                | _                   | _    | ns    | VDD < 2.7V         |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.