Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512l-80i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX5XX/6XX/7XX devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 Memory Layout

PIC32MX5XX/6XX/7XX microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX5XX/6XX/7XX devices are illustrated in Figure 4-1 through Figure 4-6. Table 4-1 provides memory map information for the Special Function Registers (SFRs).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 | -                | —                |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 **BMXDKPBA<9:0>:** DRM Kernel Program Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0                | U-0                |

| 31.24        |                   | _                 | -                 | —                 | _                 | —                 |                    | —                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | —                 | _                 | —                 |                    | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | _                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31-10 | Unimplemented: Read as '0 | n' |

|-----------|---------------------------|----|

|           | eninplemented. Read as    |    |

| bit 9 | CMR: Configuration Mismatch Reset Flag bit                                   |

|-------|------------------------------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred                                |

|       | 0 = Configuration mismatch Reset has not occurred                            |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit                                  |

|       | $\ensuremath{\mathtt{l}}$ = Regulator is enabled and is on during Sleep mode |

|       | 0 = Regulator is set to Stand-by Tracking mode                               |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit                                     |

|       | 1 = Master Clear (pin) Reset has occurred                                    |

|       | 0 = Master Clear (pin) Reset has not occurred                                |

| bit 6 | SWR: Software Reset Flag bit                                                 |

|       | 1 = Software Reset was executed                                              |

|       | 0 = Software Reset was not executed                                          |

| bit 5 | Unimplemented: Read as '0'                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                                       |

|       | 1 = WDT Time-out has occurred                                                |

|       | 0 = WDT Time-out has not occurred                                            |

| bit 3 | SLEEP: Wake From Sleep Flag bit                                              |

|       | 1 = Device was in Sleep mode                                                 |

|       | 0 = Device was not in Sleep mode                                             |

| bit 2 | IDLE: Wake From Idle Flag bit                                                |

|       | 1 = Device was in Idle mode                                                  |

|       | 0 = Device was not in Idle mode                                              |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                 |

|       | 1 = Brown-out Reset has occurred                                             |

|       | 0 = Brown-out Reset has not occurred                                         |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                           |

|       | 1 = Power-on Reset has occurred                                              |

|       | 0 = Power-on Reset has not occurred                                          |

|       |                                                                              |

Note 1: User software must clear this bit to view the next detection.

# 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

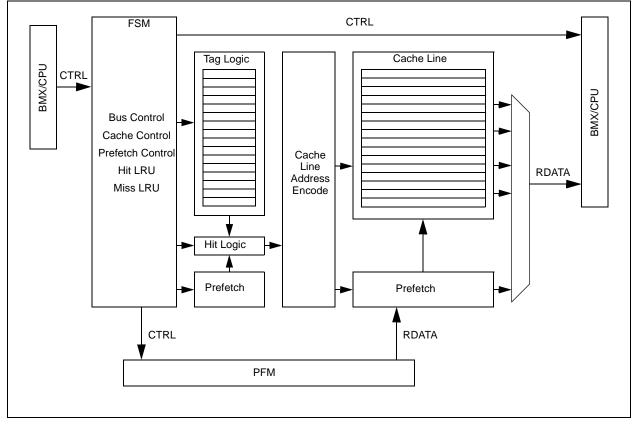

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

# 9.1 Features

- 16 fully-associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- Pseudo-LRU replacement policy

- All cache lines are software writable

- 16-byte parallel memory fetch

- Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

# FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

# PIC32MX5XX/6XX/7XX

### REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| R-x          |                   | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNE              | 320               | TOKBUSY <sup>(1,5)</sup> | 030631            | TIOSTEIN'             | KESUME"               | FFDKOI           | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-ended zero was detected on the USB

0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

PIC32MX5XX/6XX/7XX

#### TABLE 12-3: PORTC REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 | n         |         |          |            |             |             |             |            | Bi      | ts   |      |      |      |      |      |      |      | ő          |

|-----------------------------|---------------------------------|-----------|---------|----------|------------|-------------|-------------|-------------|------------|---------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14    | 29/13      | 28/12       | 27/11       | 26/10       | 25/9       | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6090                        | TRICC                           | 31:16     | —       | _        | -          | —           | _           | -           | —          | _       | -    | -    | -    | _    | —    | _    | _    | -    | 0000       |

| 6060                        | 6080 TRISC                      | 15:0      | TRISC15 | TRISC14  | TRISC13    | TRISC12     | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | F000       |

| 6000                        | PORTC                           | 31:16     | —       | -        |            | —           | —           |             | -          |         |      | _    |      | _    | _    | -    | _    |      | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14     | RC13       | RC12        | _           | -           | —          | -       | -    | -    | -    | -    |      | -    |      | -    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14   | LATC13     | LATC12      | _           | _           | -          | —       | _    | —    | _    | —    | _    | _    | _    | _    | xxxx       |

| CORO                        |                                 | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 00B0                        | OBO ODCC -                      | 15:0      | ODCC15  | ODCC14   | ODCC13     | ODCC12      | _           | _           | —          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| Logon                       | 4                               | - unkno   |         | Pocot: - | unimplomon | ted read as | '0' Poset v | luce are ch | we in hove | locimol |      |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-4: PORTC REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 | 0         |         |         |         |         |       |       |      | Bi   | ts   |      |      |        |        |        |        |      | ú          |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

|                             | TRICC                           | 31:16     |         | _       | —       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6060                        | 6080 TRISC                      | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | FOOF       |

| 6000                        | PORTC                           | 31:16     | _       | —       | —       | —       | —     | —     | —    | —    | _    | —    | —    | —      | —      | —      | —      | —    | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | —    | —    | _    | —    | —    | RC4    | RC3    | RC2    | RC1    | —    | xxxx       |

| 6040                        |                                 | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 60A0                        | 50A0   LATC                     | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | _     | —    | —    | _    | —    | —    | LATC4  | LATC3  | LATC2  | LATC1  | —    | xxxx       |

| CORO                        |                                 | 31:16     | —       | _       | _       | —       | _     | —     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 00B0                        | 60B0 ODCC                       | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

# TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |                                                                                                                                                                                         |         |        |       |        | •      |          | -             | Bi                           | ts       |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-------|--------|--------|----------|---------------|------------------------------|----------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                                                                                                                               | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10    | 25/9          | 24/8                         | 23/7     | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16                                                                                                                                                                                   | -       | —      | —     | _      |        | _        | —             | -                            | _        | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0                                                                                                                                                                                    | -       | —      | —     | -      |        | _        |               |                              |          |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16                                                                                                                                                                                   | _       | _      | _     | —      | _      | —        | _             | —                            | _        | —           | _           | —         | —        |        | -    | _        | 0000       |

| 5240                        |                                 | 15:0                                                                                                                                                                                    | —       | —      | —     | —      |        |          |               |                              | Ba       | ud Rate Ger | erator Regi | ster      |          |        | •    |          | 0000       |

| 5250                        | I2C5TRN                         | 31:16                                                                                                                                                                                   | —       | —      | —     | —      | _      | —        | _             | —                            | _        | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0                                                                                                                                                                                    | —       | _      | _     | —      | _      | —        | _             | _                            |          | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16                                                                                                                                                                                   | -       |        |       | —      | _      | _        |               | _                            | _        | —           | —           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0                                                                                                                                                                                    | -       |        | —     | —      |        | —        |               | _                            |          |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16                                                                                                                                                                                   | _       | —      | —     | —      | —      | —        | —             | —                            | _        | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0                                                                                                                                                                                    | ON      | _      | SIDL  | SCLREL | STRICT | A10M     | DISSLW        | SMEN                         | GCEN     | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16                                                                                                                                                                                   | —       | _      | _     | _      | _      | _        | —             | —                            | _        | —           | —           | _         | _        |        | —    | —        | 0000       |

|                             |                                 |                                                                                                                                                                                         | ACKSTAT | TRSTAT | —     | —      | —      | BCL      | GCSTAT        | ADD10                        | IWCOL    | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16                                                                                                                                                                                   | _       | _      | —     | —      | _      |          | —             |                              | _        | _           |             | _         | —        |        | —    | —        | 0000       |

|                             |                                 | 15:0                                                                                                                                                                                    | _       | _      | _     | _      | _      | -        |               |                              | ADD<9:0> |             |             |           |          |        |      |          | 0000       |

| 5330                        | I2C1MSK                         | 31:16                                                                                                                                                                                   | _       | _      | _     | _      | _      | -        | _             | -                            | _        | _           | —           | -         | _        | -      | —    | —        | 0000       |

| 15:0                        |                                 |                                                                                                                                                                                         |         |        |       | _      |        |          |               |                              | MSK      | <9:0>       |             |           |          |        | 0000 |          |            |

| 5340                        | I2C1BRG                         | 31:16                                                                                                                                                                                   | _       |        |       | _      | _      | —        |               | _                            | -        | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0                                                                                                                                                                                    | _       |        |       | _      |        |          |               |                              | Ва       | ud Rate Ger | Ū.          | ster      |          |        |      |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16                                                                                                                                                                                   | _       | —      | —     | _      | _      | _        | _             | _                            | _        | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0                                                                                                                                                                                    | _       | _      | _     | _      | _      | _        |               | _                            |          |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0                                                                                                                                                                           | _       | _      |       |        |        | —        |               |                              | —        | —           | —           | - Deseive |          | —      | —    | —        | 0000       |

|                             |                                 |                                                                                                                                                                                         |         |        |       |        |        | _        |               |                              |          |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0                                                                                                                                                                           | ON      |        | -     | -      |        | -        | —<br>DI001144 | -                            | -        | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |                                                                                                                                                                                         |         | _      | SIDL  | SCLREL | STRICT | A10M     | DISSLW        | SMEN                         | GCEN     |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16                                                                                                                                                                                   |         |        | _     | _      | _      | —<br>DCI | —<br>         | -                            | -        | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16                                                                                                                                                                           | ACKSTAT | TRSTAT |       | _      | _      | BCL      | GCSTAT        | ADD10                        | IWCOL    | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0                                                                                                                                                                                    |         |        |       | _      | _      |          | _             | -                            | —        | —           |             | <br><9:0> | —        |        | _    | —        | 0000       |

|                             |                                 | 31:16                                                                                                                                                                                   | _       |        |       | _      |        | _        | _             |                              | _        |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0                                                                                                                                                                                    |         |        |       |        |        |          | _             | _                            | _        | _           |             | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 | 31:16                                                                                                                                                                                   |         |        |       |        |        |          |               | MSK<9:0>                     |          |             |             |           |          | _      | 0000 |          |            |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0                                                                                                                                                                                    | _       |        |       | _      | _      | _        | _             |                              | Ra       | ud Rate Ger | erator Regi | ster      | _        |        |      |          | 0000       |

|                             |                                 | 31:16                                                                                                                                                                                   | _       | _      | _     | _      | _      | _        | _             | Baud Rate Generator Register |          |             |             |           | _        | _      | 0000 |          |            |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0                                                                                                                                                                                    | _       | _      | _     | _      | _      |          | _             | — Transmit Register          |          |             |             |           |          |        | 0000 |          |            |

|                             |                                 | 31:16                                                                                                                                                                                   | _       | _      | _     | _      |        | _        | _             |                              |          |             |             |           | _        | 0000   |      |          |            |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0                                                                                                                                                                                    | _       | _      | _     | _      | _      | _        | _             | _                            |          |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 | 15:0       -       -       -       -       Receive Register       0000         = unknown value on Reset:= unimplemented, read as '0'. Reset values are shown in hexadecimal.       0000 |         |        |       |        |        |          |               |                              |          |             |             |           |          |        |      |          |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |

|              |                   | —                 | _                 | _                 | —                 | —                 | —                | ADM_EN           |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R-0              | R-1              |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0, HS        | R-0              |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend:           | HS = Set by hardware | HC = Cleared by hardwar            | re                 |  |

|-------------------|----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

- bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

- bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion.

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------------|-------------------|------------------|------------------|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | HR10-             | <3:0>             |                   |                                          | HR01              | <3:0>            |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

|              |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                               |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                               |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                      | U-0               | U-0              | U-0              |

| 7:0          | —                 | —                 | _                 | _                 | —                                        | _                 | —                | _                |

|              |                   |                   |                   |                   |                                          |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                                          |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0'       |                   |                  |                  |

| -n = Value   | e at POR          |                   | '1' = Bit is se   | t                 | 0' = Bit is cleared $x = Bit is unknown$ |                   |                  |                  |

# REGISTER 22-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

# TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |                                    |                                    |       |       |       |       |      | Bi   | ts   |      |      |      |      |      |      |      |            |

|-----------------------------|------------------|---------------|------------------------------------|------------------------------------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15                              | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 | ADC Result Word B (ADC1BUFB<31:0>) |                                    |       |       |       |       |      |      |      | 0000 |      |      |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 | ADC Result Word C (ADC1BUFC<31:0>) |                                    |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 | ADC Result Word D (ADC1BUED<31:0>) |                                    |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 | ADC Result Word E (ADC1BUFE<31:0>) |                                    |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |                                    | ADC Result Word F (ADC1BUFF<31:0>) |       |       |       |       |      |      |      | 0000 |      |      |      |      |      |      |            |

= unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: x = unknown value on Reset

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

# PIC32MX5XX/6XX/7XX

| REGISTE      | REGISTER 23-3: AD1CON3: ADC CONTROL REGISTER 3 |                   |                   |                   |                   |                          |                  |                  |  |

|--------------|------------------------------------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              | U-0              |  |

|              | —                                              | —                 | —                 | —                 | —                 | —                        | —                | —                |  |

| 00.40        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              | U-0              |  |

| 23:16        | —                                              | —                 | —                 | —                 | —                 | —                        | —                | —                |  |

| 45.0         | R/W-0                                          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0                    | R/W-0            | R/W-0            |  |

| 15:8         | ADRC                                           | —                 | —                 |                   |                   | SAMC<4:0> <sup>(1)</sup> |                  |                  |  |

| 7:0          | R/W-0                                          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W              | R/W-0            |  |

|              |                                                |                   |                   | ADCS<             | 7:0> <b>(2)</b>   |                          |                  |                  |  |

## Legend:

| 0                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15    | ADRC: ADC Conversion Clock Source bit               |

|-----------|-----------------------------------------------------|

|           | 1 = Clock derived from FRC                          |

|           | 0 = Clock derived from Peripheral Bus Clock (PBCLK) |

| bit 14-13 | Unimplemented: Read as '0'                          |

```

bit 12-8 SAMC<4:0>: Auto-Sample Time bits<sup>(1)</sup>

11111 = 31 TAD

00001 = 1 TAD

00000 = 0 TAD (Not allowed)

ADCS<7:0>: ADC Conversion Clock Select bits<sup>(2)</sup>

bit 7-0

11111111 =TPB • 2 • (ADCS<7:0> + 1) = 512 • TPB = TAD

```

```

00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD

00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

```

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | FLTEN7            | MSEL              | 7<1:0>            | FSEL7<4:0>        |                   |                   |                  |                  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN6            | MSEL              | 6<1:0>            | FSEL6<4:0>        |                   |                   |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            | FSEL5<4:0>        |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN4            | MSEL4<1:0>        |                   | FSEL4<4:0>        |                   |                   |                  |                  |  |

### **REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31    | FLTEN7: Filter 7 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN6: Filter 6 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 - Massage matching filter is stored in EIEO buffer 30 |

uffer 31 11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |

### REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

#### REGISTER 25-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 51.24        | —                 | —                 | _                 | _                 | _                     | _                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 15.0         | RESETMGMT         | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 7:0          | U-0               | U-0               | R/W-1             | R/W-0             | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

|              |                   | —                 |                   | CLKSEL            | _<3:0> <sup>(1)</sup> |                   | NOPRE            | SCANINC          |

#### Legend:

| - 5               |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 RESETMGMT: Test Reset MII Management bit

- 1 = Reset the MII Management module

- 0 = Normal Operation

# bit 14-6 **Unimplemented:** Read as '0'

bit 5-2 CLKSEL<3:0>: MII Management Clock Select 1 bits<sup>(1)</sup>

These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

#### bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

#### bit 0 SCANINC: Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

- Note 1: Table 25-7 provides a description of the clock divider encoding.

| Note: | Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). |

|-------|------------------------------------------------------------------------------------------------------------|

|       | 8-bit accesses are not allowed and are ignored by the hardware.                                            |

#### TABLE 25-7: MIIM CLOCK SELECTION

| MIIM Clock Select    | EMAC1MCFG<5:2>        |

|----------------------|-----------------------|

| SYSCLK divided by 4  | 000x                  |

| SYSCLK divided by 6  | 0010                  |

| SYSCLK divided by 8  | 0011                  |

| SYSCLK divided by 10 | 0100                  |

| SYSCLK divided by 14 | 0101                  |

| SYSCLK divided by 20 | 0110                  |

| SYSCLK divided by 28 | 0111                  |

| SYSCLK divided by 40 | 1000                  |

| Undefined            | Any other combination |

# 26.1 Control Registers

# TABLE 26-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 6         | Bits  |       |       |       |       |       |      |      |      |        |      |      |      | 6    |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 4.000                       |                                 | 31:16     | _     | _     | -     | —     | -     | _     |      |      |      | —      | —    | —    |      | -    | —     | -     | 0000       |

| A000                        | CM1CON                          | 15:0      | ON    | COE   | CPOL  | —     | _     | _     | _    | COUT | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | 00C3       |

| A010                        | CM2CON                          | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | —      | —    | —    |      |      | —     | _     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | -     | -     | -     |      | COUT | EVPO | L<1:0> | —    | CREF |      |      | CCH   | <1:0> | 00C3       |

| A060                        | CMSTAT                          | 31:16     |       | -     | —     | —     | —     | —     | —    | —    | —    | —      | —    | —    | —    | —    | —     | —     | 0000       |

| A060                        | CIVISTAT                        | 15:0      |       | _     | SIDL  | -     |       | _     |      |      |      | _      | _    | _    |      |      | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

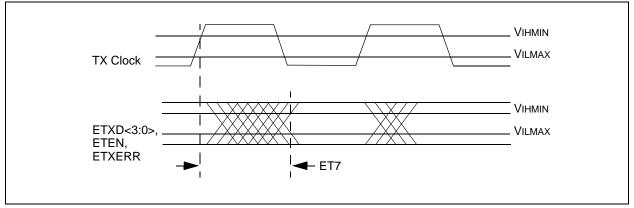

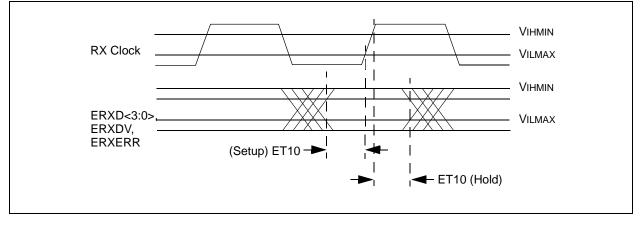

### FIGURE 32-21: TRANSMIT SIGNAL TIMING RELATIONSHIPS AT THE MII

# PIC32MX5XX/6XX/7XX

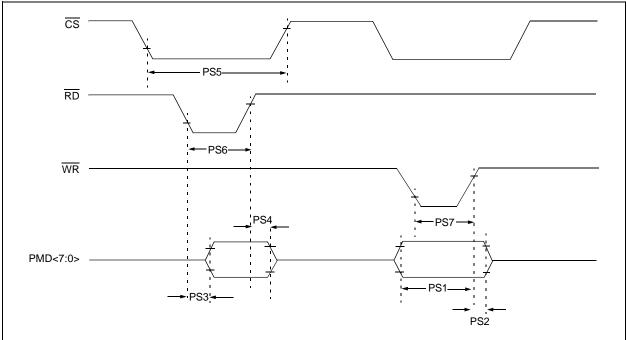

# FIGURE 32-25: PARALLEL SLAVE PORT TIMING

| AC CHA        | RACTERIS | TICS                                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |            |  |

|---------------|----------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No. | Symbol   | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                | Typical | Max. | Units | Conditions |  |

| PS1           | TdtV2wrH | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                  | _       |      | ns    | _          |  |

| PS2           | TwrH2dtl | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                  | —       | _    | ns    | —          |  |

| PS3           | TrdL2dtV | RD and CS Active to Data-Out<br>Valid                                            | —                                                                                                                                                                                                                                                                                   | —       | 60   | ns    | —          |  |

| PS4           | TrdH2dtl | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                   | —       | 10   | ns    | _          |  |

| PS5           | Tcs      | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                            | _       |      | ns    | _          |  |

| PS6           | Twr      | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | —       | _    | ns    | _          |  |

| PS7           | Trd      | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | _       | _    | ns    |            |  |

### TABLE 32-39: PARALLEL SLAVE PORT REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

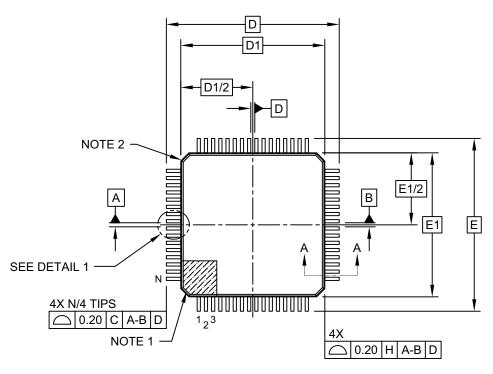

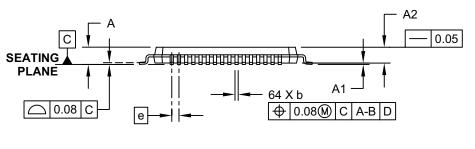

# 34.2 Package Details

The following sections give the technical details of the packages.

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PIC32       MX       5XX       F       512       H       T       80       I/PT - XXX         Microchip Brand |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|