Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

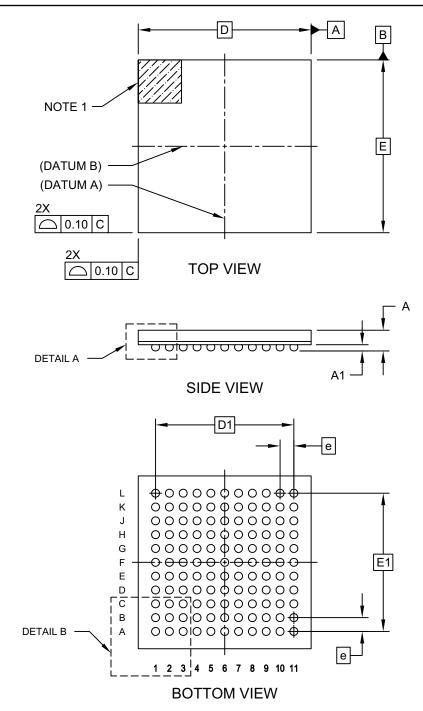

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512lt-80i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX5XX/6XX/7XX devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site.

Note: For PIC32MX5XX/6XX/7XX devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

| TABLE 7-1: INTERRUPT IRQ                                                            | VECTOR | AND BIT | LOCATIO  | N (CONTIN | UED)            |              |

|-------------------------------------------------------------------------------------|--------|---------|----------|-----------|-----------------|--------------|

| Interrupt Source <sup>(1)</sup>                                                     | IRQ    | Vector  |          | Interru   | pt Bit Location |              |

| interrupt Source ?                                                                  | Number | Number  | Flag     | Enable    | Priority        | Sub-Priority |

| AD1 – ADC1 Convert Done                                                             | 33     | 27      | IFS1<1>  | IEC1<1>   | IPC6<28:26>     | IPC6<25:24>  |

| PMP – Parallel Master Port                                                          | 34     | 28      | IFS1<2>  | IEC1<2>   | IPC7<4:2>       | IPC7<1:0>    |

| CMP1 – Comparator Interrupt                                                         | 35     | 29      | IFS1<3>  | IEC1<3>   | IPC7<12:10>     | IPC7<9:8>    |

| CMP2 – Comparator Interrupt                                                         | 36     | 30      | IFS1<4>  | IEC1<4>   | IPC7<20:18>     | IPC7<17:16>  |

| U2E – UART2 Error<br>SPI2E – SPI2 Fault<br>I2C4B – I2C4 Bus Collision Event         | 37     | 31      | IFS1<5>  | IEC1<5>   | IPC7<28:26>     | IPC7<25:24>  |

| U2RX – UART2 Receiver<br>SPI2RX – SPI2 Receive Done<br>I2C4S – I2C4 Slave Event     | 38     | 31      | IFS1<6>  | IEC1<6>   | IPC7<28:26>     | IPC7<25:24>  |

| U2TX – UART2 Transmitter<br>SPI2TX – SPI2 Transfer Done<br>IC4M – I2C4 Master Event | 39     | 31      | IFS1<7>  | IEC1<7>   | IPC7<28:26>     | IPC7<25:24>  |

| U3E – UART3 Error<br>SPI4E – SPI4 Fault<br>I2C5B – I2C5 Bus Collision Event         | 40     | 32      | IFS1<8>  | IEC1<8>   | IPC8<4:2>       | IPC8<1:0>    |

| U3RX – UART3 Receiver<br>SPI4RX – SPI4 Receive Done<br>I2C5S – I2C5 Slave Event     | 41     | 32      | IFS1<9>  | IEC1<9>   | IPC8<4:2>       | IPC8<1:0>    |

| U3TX – UART3 Transmitter<br>SPI4TX – SPI4 Transfer Done<br>IC5M – I2C5 Master Event | 42     | 32      | IFS1<10> | IEC1<10>  | IPC8<4:2>       | IPC8<1:0>    |

| I2C2B – I2C2 Bus Collision Event                                                    | 43     | 33      | IFS1<11> | IEC1<11>  | IPC8<12:10>     | IPC8<9:8>    |

| I2C2S – I2C2 Slave Event                                                            | 44     | 33      | IFS1<12> | IEC1<12>  | IPC8<12:10>     | IPC8<9:8>    |

| I2C2M – I2C2 Master Event                                                           | 45     | 33      | IFS1<13> | IEC1<13>  | IPC8<12:10>     | IPC8<9:8>    |

| FSCM – Fail-Safe Clock Monitor                                                      | 46     | 34      | IFS1<14> | IEC1<14>  | IPC8<20:18>     | IPC8<17:16>  |

| RTCC – Real-Time Clock and<br>Calendar                                              | 47     | 35      | IFS1<15> | IEC1<15>  | IPC8<28:26>     | IPC8<25:24>  |

| DMA0 – DMA Channel 0                                                                | 48     | 36      | IFS1<16> | IEC1<16>  | IPC9<4:2>       | IPC9<1:0>    |

| DMA1 – DMA Channel 1                                                                | 49     | 37      | IFS1<17> | IEC1<17>  | IPC9<12:10>     | IPC9<9:8>    |

| DMA2 – DMA Channel 2                                                                | 50     | 38      | IFS1<18> | IEC1<18>  | IPC9<20:18>     | IPC9<17:16>  |

| DMA3 – DMA Channel 3                                                                | 51     | 39      | IFS1<19> | IEC1<19>  | IPC9<28:26>     | IPC9<25:24>  |

| DMA4 – DMA Channel 4                                                                | 52     | 40      | IFS1<20> | IEC1<20>  | IPC10<4:2>      | IPC10<1:0>   |

| DMA5 – DMA Channel 5                                                                | 53     | 41      | IFS1<21> | IEC1<21>  | IPC10<12:10>    | IPC10<9:8>   |

| DMA6 – DMA Channel 6                                                                | 54     | 42      | IFS1<22> | IEC1<22>  | IPC10<20:18>    | IPC10<17:16> |

| DMA7 – DMA Channel 7                                                                | 55     | 43      | IFS1<23> | IEC1<23>  | IPC10<28:26>    | IPC10<25:24> |

| FCE – Flash Control Event                                                           | 56     | 44      | IFS1<24> | IEC1<24>  | IPC11<4:2>      | IPC11<1:0>   |

| USB – USB Interrupt                                                                 | 57     | 45      | IFS1<25> | IEC1<25>  | IPC11<12:10>    | IPC11<9:8>   |

| CAN1 – Control Area Network 1                                                       | 58     | 46      | IFS1<26> | IEC1<26>  | IPC11<20:18>    | IPC11<17:16> |

| CAN2 – Control Area Network 2                                                       | 59     | 47      | IFS1<27> | IEC1<27>  | IPC11<28:26>    | IPC11<25:24> |

| ETH – Ethernet Interrupt                                                            | 60     | 48      | IFS1<28> | IEC1<28>  | IPC12<4:2>      | IPC12<1:0>   |

| IC1E – Input Capture 1 Error                                                        | 61     | 5       | IFS1<29> | IEC1<29>  | IPC1<12:10>     | IPC1<9:8>    |

| IC2E – Input Capture 2 Error                                                        | 62     | 9       | IFS1<30> | IEC1<30>  | IPC2<12:10>     | IPC2<9:8>    |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

#### **TABLE 7-3**: INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND PIC32MX695F512H DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |                            |       |             | В                | its  |      |      |             |             |            |             |                      |            |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------------------|-------|-------------|------------------|------|------|------|-------------|-------------|------------|-------------|----------------------|------------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                      | 26/10 | 25/9        | 24/8             | 23/7 | 22/6 | 21/5 | 20/4        | 19/3        | 18/2       | 17/1        | 16/0                 | All Resets |      |

| 4000                        | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0>                |       | INT4IS      | S<1:0>           | —    | -    | —    |             | OC4IP<2:0>  | •          | OC4IS       | 5<1:0>               | 0000       |      |

| 10D0                        | IPC4                            | 15:0      | _     | -     | _     |       | IC4IP<2:0>                 |       | IC4IS       | <1:0>            | _    | _    | _    |             | T4IP<2:0>   |            | T4IS        | <1:0>                | 0000       |      |

| 10E0                        | IPC5                            | 31:16     | _     | -     | _     | _     |                            |       | _           | _                | _    | _    | _    |             | OC5IP<2:0>  | •          | OC5IS       | 5<1:0>               | 0000       |      |

| IUEU                        | IPC5                            | 15:0      | —     | _     |       |       |                            |       | IC5IS       | <1:0>            | —    |      |      |             | T5IP<2:0>   |            | T5IS<       | <1:0>                | 0000       |      |

|                             |                                 | 31:16     | _     | -     | _     |       | AD1IP<2:0> A               |       | AD1IS       | S<1:0>           | _    | _    | _    |             | CNIP<2:0>   |            | CNIS        | <1:0>                | 0000       |      |

| 10F0                        | IPC6                            |           |       |       |       |       |                            |       |             |                  |      |      |      |             | U1IP<2:0>   |            | U1IS-       | <1:0>                |            |      |

| IOFU                        | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0>                |       | I2C1IS<1:0> |                  | —    | —    | —    |             | SPI3IP<2:0> | >          | SPI3IS      | S<1:0>               | 0000       |      |

|                             |                                 |           |       |       |       |       |                            |       |             |                  |      |      |      |             | I2C3IP<2:0> |            | I2C3IS<1:0> |                      |            |      |

|                             |                                 |           |       |       |       |       | U3IP<2:0>                  |       | U3IS-       | <1:0>            |      |      |      |             |             |            |             |                      |            |      |

| 1100                        | IPC7                            | 31:16     | —     | -     | —     |       | SPI2IP<2:0>                |       | SPI2IS      | S<1:0>           | —    | —    | —    |             | CMP2IP<2:0  | >          | CMP2I       | S<1:0>               | 0000       |      |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0>                |       | 12C415      | S<1:0>           |      |      |      |             |             |            |             |                      |            |      |

|                             |                                 | 15:0      | _     | —     |       | (     | CMP1IP<2:0:                | >     | CMP1        | S<1:0>           | —    |      |      | PMPIP<2:0>  |             | PMPIS<1:0> |             | 0000                 |            |      |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0>                |       | RTCCI       | S<1:0>           | —    | _    |      | FSCMIP<2:0> |             |            |             | FSCM                 | S<1:0>     | 0000 |

| 1110                        | IPC8                            |           |       |       |       |       |                            |       |             |                  |      |      |      |             | U2IP<2:0>   |            | U2IS-       | <1:0>                |            |      |

|                             | 11 00                           | 15:0      | —     | -     | —     | —     | —                          | —     | —           | —                | —    | —    | —    |             | SPI4IP<2:0> | >          | SPI4IS      | S<1:0>               | 0000       |      |

|                             |                                 |           |       |       |       |       |                            |       |             |                  |      |      |      |             | I2C5IP<2:0> | >          | 12C515      | S<1:0>               |            |      |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     |       | DMA3IP<2:0:                |       | DMA3        |                  | —    | _    |      |             | DMA2IP<2:0  |            | DMA2        |                      | 0000       |      |

| 1120                        | 11 00                           | 15:0      | _     | —     |       |       | DMA1IP<2:0:                |       | DMA1        |                  | —    | _    |      |             | DMA0IP<2:0  |            | DMA0I       |                      | 0000       |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | MA7IP<2:0>                 |       |             | <1:0> <b>(2)</b> | —    | _    |      |             | MA6IP<2:0>  |            | DMA6IS      |                      | 0000       |      |

| 1130                        | 11 010                          | 15:0      | _     | —     |       | D     | DMA5IP<2:0> <sup>(2)</sup> |       | DMA5IS      | <1:0> <b>(2)</b> | —    | _    |      | D           | MA4IP<2:0>  | (2)        | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |      |

| 1140                        | IPC11                           | 31:16     | —     | —     | _     | _     |                            |       | —           | —                | —    | _    | _    | —           | _           | —          | —           | —                    | 0000       |      |

|                             |                                 | 15:0      | —     | —     | —     |       | USBIP<2:0>                 |       | USBIS       |                  | —    | —    | —    | FCEIP<2:0>  |             | FCEIS      |             | 0000                 |            |      |

| 1150                        | IPC12                           | 31:16     | —     | —     | _     |       | U5IP<2:0>                  |       | U5IS-       | <1:0>            | —    | _    | _    | U6IP<2:0>   |             | U6IS-      | <1:0>       | 0000                 |            |      |

| 1100                        | 11 012                          | 15:0      | _     | —     | —     |       | U4IP<2:0>                  |       | U4IS-       | <1:0>            | —    | _    | —    |             | ETHIP<2:0>  |            | ETHIS<1:0>  |                      | 0000       |      |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. These bits are not available on PIC32MX664 devices. This register does not have associated CLR, SET, and INV registers.

2:

3:

### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                                                  |                                 |               |              |              |             |                |                |              |              | В       | its     |        |        |        |                  |         |        |         |              |

|------------------------------------------------------|---------------------------------|---------------|--------------|--------------|-------------|----------------|----------------|--------------|--------------|---------|---------|--------|--------|--------|------------------|---------|--------|---------|--------------|

| Virtual Address<br>(BF88_#)                          | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14        | 29/13       | 28/12          | 27/11          | 26/10        | 25/9         | 24/8    | 23/7    | 22/6   | 21/5   | 20/4   | 19/3             | 18/2    | 17/1   | 16/0    | All Resets   |

|                                                      |                                 | 31:16         | _            |              | _           | _              | _              | _            | _            | _       | —       | _      | _      | _      | _                | _       | _      | _       | 0000         |

| 3290                                                 | DCH2DAT                         | 15:0          | _            |              | _           | _              | _              | _            | _            | _       |         |        |        | CHPDA  | AT<7:0>          |         |        |         | 0000         |

| 32A0                                                 | DCH3CON                         | 31:16         | _            |              | _           | _              | _              | _            |              | _       | _       |        | _      | _      | —                | —       | _      | _       | 0000         |

| 32A0                                                 | Denseon                         | 15:0          | CHBUSY       | -            | —           | —              | —              | —            | —            | CHCHNS  | CHEN    | CHAED  | CHCHN  | CHAEN  | —                | CHEDET  | CHPR   | l<1:0>  | 0000         |

| 32B0                                                 | DCH3ECON                        | 31:16         |              | _            | —           | —              | —              | —            |              | —       |         | 1      | ł      |        | Q<7:0>           |         |        |         | 00FF         |

| 15:0 CHSIRQ<7:0> CFORCE CABORT PATEN SIRQEN AIRQEN - |                                 |               |              |              |             |                |                |              | _            | —       | —       | FF00   |        |        |                  |         |        |         |              |

| 32C0                                                 | <b>DCH3INT</b>                  | 31:16         | —            | _            | —           | —              | _              | _            | _            | —       | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

|                                                      |                                 |               |              |              |             |                |                |              |              |         |         |        |        | 0000   |                  |         |        |         |              |

| 32D0                                                 | DCH3SSA                         | 31:16         |              | CHSSA<31:0>  |             |                |                |              |              |         |         |        |        |        |                  |         |        |         |              |

|                                                      |                                 | 15:0          | 000          |              |             |                |                |              |              |         |         |        |        | 0000   |                  |         |        |         |              |

| 32E0                                                 | DCH3DSA                         | CHDSA<310>    |              |              |             |                |                |              |              |         |         |        | 0000   |        |                  |         |        |         |              |

| 31.16                                                |                                 |               |              |              |             |                |                |              | _            | 0000    |         |        |        |        |                  |         |        |         |              |

| 32F0                                                 | DCH3SSIZ 15:0 CHSSIZ<15:0>      |               |              |              |             |                |                |              |              |         |         | 0000   |        |        |                  |         |        |         |              |

|                                                      |                                 | 31:16         | _            | _            | _           | _              | _              | _            |              | _       | _       |        | _      | _      | _                | _       | _      |         | 0000         |

| 3300                                                 | DCH3DSIZ                        | 15:0          |              |              |             |                |                |              |              | CHDSI   | Z<15:0> |        |        |        |                  |         |        |         | 0000         |

|                                                      | DOLIGODITO                      | 31:16         | _            | _            | _           | _              | _              | —            | _            | _       | _       | _      | _      | _      | _                | _       | _      | _       | 0000         |

| 3310                                                 | DCH3SPTR                        | 15:0          |              |              |             | •              | •              |              |              | CHSPT   | R<15:0> |        | •      |        | •                |         |        |         | 0000         |

| 2220                                                 | DCH3DPTR                        | 31:16         | _            |              | _           | —              | _              | _            | _            | —       | _       | _      | _      | _      | —                | —       | _      | _       | 0000         |

| 3320                                                 | DCH3DFTK                        | 15:0          |              |              |             |                |                |              |              | CHDPT   | R<15:0> |        |        |        |                  |         |        |         | 0000         |

| 3330                                                 | DCH3CSIZ                        | 31:16         | —            | —            | —           | —              | —              | —            | —            | —       | —       | —      | —      | —      | —                | —       | —      | —       | 0000         |

| 0000                                                 | DOI 130012                      | 15:0          |              |              |             |                |                |              |              | CHCSI   | Z<15:0> |        | -      |        | -                |         |        |         | 0000         |

| 3340                                                 | DCH3CPTR                        | 31:16         | —            | —            | —           | —              | —              | —            | —            | —       | —       | —      | -      | —      | —                | —       | —      | —       | 0000         |

|                                                      |                                 | 15:0          |              |              |             | -              | -              |              |              | CHCPT   | R<15:0> |        | -      |        | -                |         |        |         | 0000         |

| 3350                                                 | DCH3DAT                         | 31:16         | _            | _            | —           |                |                | _            | _            |         | _       |        | —      | —      | —                | _       | _      |         | 0000         |

|                                                      |                                 | 15:0          | _            |              | _           |                |                | _            | -            |         |         |        |        |        | AT<7:0>          | 1       |        |         | 0000         |

| 3360                                                 | DCH4CON                         | 31:16         | -            |              | _           | _              | _              | _            | _            | -       | -       | -      | -      | -      | -                |         | -      | —       | 0000         |

|                                                      |                                 | 15:0          | CHBUSY       |              | -           |                | _              |              | _            | CHCHNS  | CHEN    | CHAED  | CHCHN  | CHAEN  | -                | CHEDET  | CHPR   | (1<1:0> | 0000         |

| 3370                                                 | DCH4ECON                        | 31:16<br>15:0 | _            |              |             |                | <br>Q<7:0>     |              |              | —       | CFORCE  | CABORT | PATEN  | SIRQEN | Q<7:0><br>AIRQEN |         | _      | _       | 00FF<br>FF00 |

|                                                      |                                 | 31:16         | _            | _            |             |                |                |              |              | _       | CHSDIE  | CABORT | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

| 3380                                                 | DCH4INT                         | 15:0          |              | _            | _           | _              | _              | _            |              | _       | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

|                                                      |                                 | 31:16         |              |              |             |                |                | 1            |              |         |         | Shorm  | 51000  |        | 0110011          | 0110011 | JIIAI  | SHER    | 0000         |

| 3390                                                 | DCH4SSA                         | 15:0          | CHSSA<31:0>  |              |             |                |                |              |              |         |         |        |        |        | 0000             |         |        |         |              |

|                                                      |                                 | 31:16         | 6            |              |             |                |                |              |              |         |         |        |        | 0000   |                  |         |        |         |              |

| 33A0                                                 | DCH4DSA                         | 15:0          | CHD\$A>31:05 |              |             |                |                |              |              |         |         |        |        | 0000   |                  |         |        |         |              |

| Legen                                                | <b>d:</b> x = u                 | nknown        | value on Re  | eset; — = ur | nimplemente | ed, read as '0 | )'. Reset valu | ues are show | vn in hexade | ecimal. |         |        |        |        |                  |         |        |         | <u>ا</u> ا   |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | —                          |                   | _                 |                   | _                    | _                 | _                | —                |  |  |  |  |  |

| 22.16        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 15:8         |                            |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | —                |  |  |  |  |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

# 13.2 Control Registers

# TABLE 13-1: TIMER1 REGISTER MAP

| ess                       |                                 | â         |       |                 |       |       |       |       |      | В    | its   |      |      |        |      |       |      |      | 6          |

|---------------------------|---------------------------------|-----------|-------|-----------------|-------|-------|-------|-------|------|------|-------|------|------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0000                      | TACON                           | 31:16     | -     | _               | -     | _     | _     | —     | _    | —    | _     | —    | _    | —      | —    | _     | —    | _    | 0000       |

| 0600                      | T1CON                           | 15:0      | ON    | _               | SIDL  | TWDIS | TWIP  | —     | _    | _    | TGATE | _    | TCKP | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | _     | Ι               | _     | _     | _     | _     | -    | _    | _     | _    | -    | _      | —    | -     | _    | _    | 0000       |

| 0610                      | I IVIR I                        | 15:0      |       | TMR1<15:0> 0000 |       |       |       |       |      |      |       |      |      |        | 0000 |       |      |      |            |

| 0620                      | PR1                             | 31:16     | —     | -               |       |       |       | _     | _    | _    | _     |      | _    | _      | —    | _     | _    | _    | 0000       |

| 0020                      | FRI                             | 15:0      |       | PR1<15:0> FFFF  |       |       |       |       |      |      |       |      |      |        | FFFF |       |      |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14 |        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|--------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                         | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |

| 31:24        |                             | —      | _                 | _                 | —                 | —                 | —                | ADM_EN           |  |

| 00.40        | R/W-0                       | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | ADDR<7:0>                   |        |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0                       | R/W-0  | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R-0              | R-1              |  |

| 15:8         | UTXISE                      | L<1:0> | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |

| 7.0          | R/W-0                       | R/W-0  | R/W-0             | R-1               | R-0               | R-0               | R/W-0, HS        | R-0              |  |

| 7:0          | URXISE                      | L<1:0> | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend:           | HS = Set by hardware | HC = Cleared by hardwar            | re                 |  |  |

|-------------------|----------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

- bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

- bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion.

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            | FSEL15<4:0>       |                   |                   |                  |                  |  |  |  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | FLTEN14           | MSEL1             | 4<1:0>            |                   | FSEL14<4:0>       |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            |                   | F                 | SEL13<4:0>        |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | FLTEN12           | MSEL1             | 2<1:0>            | FSEL12<4:0>       |                   |                   |                  |                  |  |  |  |

## REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31    | FLTEN15: Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The hits in this register can only be modified if the correspondir                                                                                                                                                                                                                         |

**Note:** The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED)

|                                       | · · · · · · · · · · · · · · · · · · ·                       |

|---------------------------------------|-------------------------------------------------------------|

| bit 15                                | FLTEN13: Filter 13 Enable bit                               |

|                                       | 1 = Filter is enabled                                       |

|                                       | 0 = Filter is disabled                                      |

| bit 14-13                             | MSEL13<1:0>: Filter 13 Mask Select bits                     |

|                                       | 11 = Acceptance Mask 3 selected                             |

|                                       | 10 = Acceptance Mask 2 selected                             |

|                                       | 01 = Acceptance Mask 1 selected                             |

|                                       | 00 = Acceptance Mask 0 selected                             |

| bit 12-8                              | FSEL13<4:0>: FIFO Selection bits                            |

|                                       | 11111 = Message matching filter is stored in FIFO buffer 31 |

|                                       | 11110 = Message matching filter is stored in FIFO buffer 30 |

|                                       | •                                                           |

|                                       | •                                                           |

|                                       | 00001 = Message matching filter is stored in FIFO buffer 1  |

|                                       | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7                                 | FLTEN12: Filter 12 Enable bit                               |

|                                       | 1 = Filter is enabled                                       |

|                                       | 0 = Filter is disabled                                      |

| bit 6-5                               | MSEL12<1:0>: Filter 12 Mask Select bits                     |

|                                       | 11 = Acceptance Mask 3 selected                             |

|                                       | 10 = Acceptance Mask 2 selected                             |

|                                       | 01 = Acceptance Mask 1 selected                             |

|                                       | 00 = Acceptance Mask 0 selected                             |

| bit 4-0                               | FSEL12<4:0>: FIFO Selection bits                            |

|                                       | 11111 = Message matching filter is stored in FIFO buffer 31 |

|                                       | 11110 = Message matching filter is stored in FIFO buffer 30 |

|                                       | •                                                           |

|                                       |                                                             |

|                                       | 00001 = Message matching filter is stored in FIFO buffer 1  |

|                                       | 00000 = Message matching filter is stored in FIFO buffer 0  |

|                                       |                                                             |

| · · · · · · · · · · · · · · · · · · · |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24     |                   | —                 | —                 | —                 |                   | —                 |                  | _                |  |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10     | _                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0      | _                 | —                 | —                 | —                 | _                 | R                 | RXBUFSZ<6:4>     |                  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |

| 7:0       |                   | RXBUF             | 3UFSZ<3:0> — — —  |                   |                   |                   | _                |                  |  |

# REGISTER 25-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

# Legend:

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

1111111 = RX data Buffer size for descriptors is 2032 bytes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.</li

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 |                   |                   |                   |                   |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 15:8      | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 10.0      | _                 | TXBUSE            | RXBUSE            | _                 | _                 | _                 | EWMARK           | FWMARK           |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       | RXDONE            | PKTPEND           | RXACT             | _                 | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |

# **REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31-15 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | TXBUSE: Transmit BVCI Bus Error Interrupt bit                                                                                                                                                                                                                   |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the TX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 13    | RXBUSE: Receive BVCI Bus Error Interrupt bit                                                                                                                                                                                                                    |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the RX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

| bit 9     | EWMARK: Empty Watermark Interrupt bit                                                                                                                                                                                                                           |

|           | <ul><li>1 = Empty Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                          |

|           | This bit is set when the RX Descriptor Buffer Count is less than or equal to the value in the RXEWM bit (ETHRXWM<0:7>) value. It is cleared by BUFCNT bit (ETHSTAT<16:23>) being incremented by hardware. Writing a '0' or a '1' has no effect.                 |

| bit 8     | FWMARK: Full Watermark Interrupt bit                                                                                                                                                                                                                            |

|           | <ul><li>1 = Full Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                           |

|           | This bit is set when the RX Descriptor Buffer Count is greater than or equal to the value in the RXFWM bit (ETHRXWM<16:23>) field. It is cleared by writing the BUFCDEC (ETHCON1<0>) bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect. |

| bit 7     | RXDONE: Receive Done Interrupt bit                                                                                                                                                                                                                              |

|           | <ul><li>1 = RX packet was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                      |

|           | This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                      |

|           |                                                                                                                                                                                                                                                                 |

| Note:     | It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.                                                                    |

#### REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | -                 | —                 | _                 | —                 | -                 | —                 | _                | —                |  |  |

| 22.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | SCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

# Legend: