Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: **PIN NAMES FOR 100-PIN USB AND CAN DEVICES**

#### **100-PIN TQFP (TOP VIEW)**

#### PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

|       |                              |       | 1                              |

|-------|------------------------------|-------|--------------------------------|

| Pin # | Full Pin Name                | Pin # | Full Pin Name                  |

| 1     | RG15                         | 36    | Vss                            |

| 2     | VDD                          | 37    | Vdd                            |

| 3     | PMD5/RE5                     | 38    | TCK/RA1                        |

| 4     | PMD6/RE6                     | 39    | AC1TX/SCK4/U5TX/U2RTS/RF13     |

| 5     | PMD7/RE7                     | 40    | AC1RX/SS4/U5RX/U2CTS/RF12      |

| 6     | T2CK/RC1                     | 41    | AN12/PMA11/RB12                |

| 7     | T3CK/RC2                     | 42    | AN13/PMA10/RB13                |

| 8     | T4CK/RC3                     | 43    | AN14/PMALH/PMA1/RB14           |

| 9     | T5CK/SDI1/RC4                | 44    | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| 10    | SCK2/U6TX/U3RTS/PMA5/CN8/RG6 | 45    | Vss                            |

| 11    | SDA4/SDI2/U3RX/PMA4/CN9/RG7  | 46    | VDD                            |

| 12    | SCL4/SDO2/U3TX/PMA3/CN10/RG8 | 47    | SS3/U4RX/U1CTS/CN20/RD14       |

| 13    | MCLR                         | 48    | SCK3/U4TX/U1RTS/CN21/RD15      |

| 14    | SS2/U6RX/U3CTS/PMA2/CN11/RG9 | 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4   |

| 15    | Vss                          | 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5   |

| 16    | VDD                          | 51    | USBID/RF3                      |

| 17    | TMS/RA0                      | 52    | SDA3/SDI3/U1RX/RF2             |

| 18    | INT1/RE8                     | 53    | SCL3/SDO3/U1TX/RF8             |

| 19    | INT2/RE9                     | 54    | VBUS                           |

| 20    | AN5/C1IN+/VBUSON/CN7/RB5     | 55    | VUSB3V3                        |

| 21    | AN4/C1IN-/CN6/RB4            | 56    | D-/RG3                         |

| 22    | AN3/C2IN+/CN5/RB3            | 57    | D+/RG2                         |

| 23    | AN2/C2IN-/CN4/RB2            | 58    | SCL2/RA2                       |

| 24    | PGEC1/AN1/CN3/RB1            | 59    | SDA2/RA3                       |

| 25    | PGED1/AN0/CN2/RB0            | 60    | TDI/RA4                        |

| 26    | PGEC2/AN6/OCFA/RB6           | 61    | TDO/RA5                        |

| 27    | PGED2/AN7/RB7                | 62    | Vdd                            |

| 28    | VREF-/CVREF-/PMA7/RA9        | 63    | OSC1/CLKI/RC12                 |

| 29    | VREF+/CVREF+/PMA6/RA10       | 64    | OSC2/CLKO/RC15                 |

| 30    | AVDD                         | 65    | Vss                            |

| 31    | AVss                         | 66    | SCL1/INT3/RA14                 |

| 32    | AN8/C1OUT/RB8                | 67    | SDA1/INT4/RA15                 |

| 33    | AN9/C2OUT/RB9                | 68    | RTCC/IC1/RD8                   |

| 34    | AN10/CVREFOUT/PMA13/RB10     | 69    | SS1/IC2/RD9                    |

| 35    | AN11/PMA12/RB11              | 70    | SCK1/IC3/PMCS2/PMA15/RD10      |

Shaded pins are 5V tolerant. Note 1:

#### TABLE 12: PIN NAMES FOR USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                                       | ")           | L11                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------|

| Not   | PIC32MX764F128L<br>PIC32MX775F256L<br>PIC32MX775F512L<br>PIC32MX795F512L<br>e: The TFBGA package skips from row | "H" to row ' | L1<br>"J" and has no "I" row. A1            |

| Pin # | Full Pin Name                                                                                                   | Pin #        | Full Pin Name                               |

| J3    | PGED2/AN7/RB7                                                                                                   | K8           | Vdd                                         |

| J4    | AVDD                                                                                                            | K9           | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |

| J5    | AN11/ERXERR/AETXERR/PMA12/RB11                                                                                  | K10          | USBID/RF3                                   |

| J6    | TCK/RA1                                                                                                         | K11          | SDA3/SDI3/U1RX/RF2                          |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                                     | L1           | PGEC2/AN6/OCFA/RB6                          |

| J8    | No Connect (NC)                                                                                                 | L2           | VREF-/CVREF-/AERXD2/PMA7/RA9                |

| J9    | No Connect (NC)                                                                                                 | L3           | AVss                                        |

| J10   | SCL3/SDO3/U1TX/RF8                                                                                              | L4           | AN9/C2OUT/RB9                               |

| J11   | D-/RG3                                                                                                          | L5           | AN10/CVREFOUT/PMA13/RB10                    |

| K1    | PGEC1/AN1/CN3/RB1                                                                                               | L6           | AC1TX/SCK4/U5TX/U2RTS/RF13                  |

| K2    | PGED1/AN0/CN2/RB0                                                                                               | L7           | AN13/ERXD1/AECOL/PMA10/RB13                 |

| K3    | VREF+/CVREF+/AERXD3/PMA6/RA10                                                                                   | L8           | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |

| K4    | AN8/C1OUT/RB8                                                                                                   | L9           | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |

| K5    | No Connect (NC)                                                                                                 | L10          | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |

| K6    | AC1RX/SS4/U5RX/U2CTS/RF12                                                                                       | L11          | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                                               |              |                                             |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | Pin Nun         | nber <sup>(1)</sup> |     | Pin | Duffer               |                                                   |  |  |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----|-----|----------------------|---------------------------------------------------|--|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    |     |     | Buffer<br>Type       | Description                                       |  |  |  |  |

| RG0      | —                                             | 90              | A5                  | A61 | I/O | ST                   | PORTG is a bidirectional I/O port                 |  |  |  |  |

| RG1      | —                                             | 89              | E6                  | B50 | I/O | ST                   |                                                   |  |  |  |  |

| RG6      | 4                                             | 10              | E3                  | A7  | I/O | ST                   |                                                   |  |  |  |  |

| RG7      | 5                                             | 11              | F4                  | B6  | I/O | ST                   |                                                   |  |  |  |  |

| RG8      | 6                                             | 12              | F2                  | A8  | I/O | ST                   |                                                   |  |  |  |  |

| RG9      | 8                                             | 14              | F3                  | A9  | I/O | ST                   |                                                   |  |  |  |  |

| RG12     | —                                             | 96              | C3                  | A65 | I/O | ST                   |                                                   |  |  |  |  |

| RG13     | —                                             | 97              | A3                  | B55 | I/O | ST                   | -                                                 |  |  |  |  |

| RG14     | —                                             | 95              | C4                  | B54 | I/O | ST                   |                                                   |  |  |  |  |

| RG15     | —                                             | 1               | B2                  | A2  | I/O | ST                   |                                                   |  |  |  |  |

| RG2      | 37                                            | 57              | H10                 | B31 | Ι   | ST                   | PORTG input pins                                  |  |  |  |  |

| RG3      | 36                                            | 56              | J11                 | A38 | I   | ST                   |                                                   |  |  |  |  |

| T1CK     | 48                                            | 74              | B11                 | B40 |     | ST                   | Timer1 external clock input                       |  |  |  |  |

| T2CK     | —                                             | 6               | D1                  | A5  | I   | ST                   | Timer2 external clock input                       |  |  |  |  |

| T3CK     | —                                             | 7               | E4                  | B4  |     | ST                   | Timer3 external clock input                       |  |  |  |  |

| T4CK     | —                                             | 8               | E2                  | A6  |     | ST                   | Timer4 external clock input                       |  |  |  |  |

| T5CK     | —                                             | 9               | E1                  | B5  |     | ST                   | Timer5 external clock input                       |  |  |  |  |

| U1CTS    | 43                                            | 47              | L9                  | B26 |     | ST                   | UART1 clear to send                               |  |  |  |  |

| U1RTS    | 49                                            | 48              | K9                  | A31 | 0   |                      | UART1 ready to send                               |  |  |  |  |

| U1RX     | 50                                            | 52              | K11                 | A36 | I   | ST                   | UART1 receive                                     |  |  |  |  |

| U1TX     | 51                                            | 53              | J10                 | B29 | 0   | _                    | UART1 transmit                                    |  |  |  |  |

| U3CTS    | 8                                             | 14              | F3                  | A9  | I   | ST                   | UART3 clear to send                               |  |  |  |  |

| U3RTS    | 4                                             | 10              | E3                  | A7  | 0   | _                    | UART3 ready to send                               |  |  |  |  |

| U3RX     | 5                                             | 11              | F4                  | B6  | I   | ST                   | UART3 receive                                     |  |  |  |  |

| U3TX     | 6                                             | 12              | F2                  | A8  | 0   | _                    | UART3 transmit                                    |  |  |  |  |

| U2CTS    | 21                                            | 40              | K6                  | A27 | I   | ST                   | UART2 clear to send                               |  |  |  |  |

| U2RTS    | 29                                            | 39              | L6                  | B22 | 0   |                      | UART2 ready to send                               |  |  |  |  |

| U2RX     | 31                                            | 49              | L10                 | B27 | I   | ST                   | UART2 receive                                     |  |  |  |  |

| U2TX     | 32                                            | 50              | L11                 | A32 | 0   |                      | UART2 transmit                                    |  |  |  |  |

| U4RX     | 43                                            | 47              | L9                  | B26 | 1   | ST                   | UART4 receive                                     |  |  |  |  |

| U4TX     | 49                                            | 48              | K9                  | A31 | 0   | _                    | UART4 transmit                                    |  |  |  |  |

| U6RX     | 8                                             | 14              | F3                  | A9  | I   | ST                   | UART6 receive                                     |  |  |  |  |

| U6TX     | 4                                             | 10              | E3                  | A7  | 0   | _                    | UART6 transmit                                    |  |  |  |  |

| U5RX     | 21                                            | 40              | K6                  | A27 | I   | ST                   | UART5 receive                                     |  |  |  |  |

| U5TX     | 29                                            | 39              | L6                  | B22 | 0   |                      | UART5 transmit                                    |  |  |  |  |

| SCK1     | _                                             | 70              | D11                 | B38 | I/O | ST                   | Synchronous serial clock input/output<br>for SPI1 |  |  |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input    |                     |     |     | nalog = A<br>= Outpu | Analog input P = Power                            |  |  |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

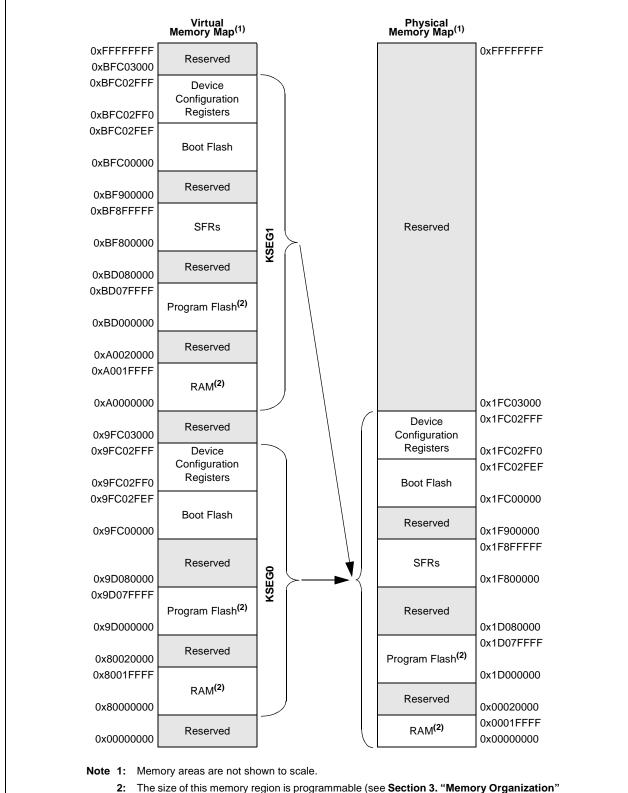

#### FIGURE 4-6: MEMORY MAP ON RESET FOR PIC32MX695F512H, PIC32MX695F512L, PIC32MX795F512H AND PIC32MX795F512L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | _                 | E                 | 3MXARB<2:0       | >                |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

### bit 31-21 **Unimplemented:** Read as '0'

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          |                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                     |

|          | 011 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | 010 = Arbitration Mode 2<br>001 = Arbitration Mode 1 (default)                                                                                                                                                                        |

|          | 000 = Arbitration Mode 0                                                                                                                                                                                                              |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        |                   | —                 | —                 |                   | IP03<2:0> IS03    |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        |                   | —                 | —                 |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0 R/W-0 F     |                   | R/W-0 R/W-0      |                  |  |

| 15.0         |                   | —                 | —                 |                   | IP01<2:0>         | IS01-             | <1:0>            |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |  |

| 7.0          |                   | _                 |                   |                   | IP00<2:0>         | IS00<1:0>         |                  |                  |  |

#### Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP03<2:0>: Interrupt Priority bits                                   |

|-----------|----------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •<br>010 = Interrupt priority is 2                                   |

|           | 010 = Interrupt priority is 2<br>001 = Interrupt priority is 1       |

|           | 000 = Interrupt is disabled                                          |

| bit 25-24 | <b>IS03&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2                                     |

|           | 01 = Interrupt sub-priority is 1                                     |

|           | 00 = Interrupt sub-priority is 0                                     |

| bit 23-21 | Unimplemented: Read as '0'                                           |

| bit 20-18 | IP02<2:0>: Interrupt Priority bits                                   |

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •                                                                    |

|           | 010 = Interrupt priority is 2                                        |

|           | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled         |

| hit 17 16 | •                                                                    |

| DIL 17-10 | <b>IS02&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2<br>01 = Interrupt sub-priority is 1 |

|           | 00 = Interrupt sub-priority is 0                                     |

| hit 15-13 | Unimplemented: Read as '0'                                           |

| 511 10 10 | Chimpionionicu. Nodu do 0                                            |

| Note:     | This register represents a generic definition                        |

| 1         | · · · ·                                                              |

definitions.

ister represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit ns.

NOTES:

#### **Control Registers** 9.2

#### **TABLE 9-1:** PREFETCH REGISTER MAP

| ess                         |                         |               |          |       |       |       |       |           |        | Bi      | ts                  |      |       |            |        |       |           |        |              |

|-----------------------------|-------------------------|---------------|----------|-------|-------|-------|-------|-----------|--------|---------|---------------------|------|-------|------------|--------|-------|-----------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range     | 31/15    | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9   | 24/8    | 23/7                | 22/6 | 21/5  | 20/4       | 19/3   | 18/2  | 17/1      | 16/0   | All Resets   |

| 4000                        | CHECON <sup>(1,2)</sup> | 31:16         | —        |       | —     | _     | _     | _         | —      | _       |                     | —    | _     |            | -      | _     |           | CHECOH | 0000         |

| 4000                        | CHECON                  | 15:0          |          | _     | —     | _     | _     | _         | DCSZ   | <1:0>   | _                   | —    | PREFE | N<1:0>     | _      | F     | PFMWS<2:0 | >      | 0007         |

| 4010                        | CHEACC <sup>(1)</sup>   | 31:16         | CHEWEN   | —     | —     | —     | —     | —         | —      | —       | -                   | —    | —     | _          | —      | —     | —         |        | 0000         |

| 4010                        |                         | 15:0          | —        | —     | —     | —     | —     | —         | —      | —       | -                   | —    | —     | —          |        | CHEID | X<3:0>    |        | 0000         |

| 4020                        | CHETAG <sup>(1)</sup>   |               | LTAGBOOT | —     | —     | —     | —     | —         | —      | —       |                     |      |       | LTAG<      |        |       | -         |        | 00xx         |

| .020                        | 01121710                | 15:0          |          |       |       |       |       | LTAG<     | <15:4> |         |                     |      |       |            | LVALID | LLOCK | LTYPE     | —      | xxx2         |

| 4030                        | CHEMSK <sup>(1)</sup>   | 31:16         | —        | _     | —     | —     | _     | —         |        | —       | —                   | —    | —     | _          | _      | _     |           | —      | 0000         |

|                             |                         | 15:0          |          |       |       |       | L     | MASK<15:5 | >      |         |                     |      |       | —          | —      | —     |           |        | 0000         |

| 4040                        | CHEW0                   | 31:16         |          |       |       |       |       |           |        | CHEWO   | )<31:0>             |      |       |            |        |       |           |        | XXXX         |

|                             |                         | 15:0          |          |       |       |       |       |           |        |         |                     |      |       |            |        |       |           |        | XXXX         |

| 4050                        | CHEW1                   | 31:16         |          |       |       |       |       |           |        | CHEW1   | <31:0>              |      |       |            |        |       |           |        | XXXX         |

|                             |                         | 15:0          |          |       |       |       |       |           |        |         |                     |      |       |            |        |       |           |        | XXXX         |

| 4060                        | CHEW2                   | 31:16<br>15:0 |          |       |       |       |       |           |        | CHEW2   | 2<31:0>             |      |       |            |        |       |           |        | XXXX         |

|                             |                         | 31:16         |          |       |       |       |       |           |        |         |                     |      |       |            |        |       |           |        | xxxx<br>xxxx |

| 4070                        | CHEW3                   | 15:0          |          |       |       |       |       |           |        | CHEWS   | 8<31:0>             |      |       |            |        |       |           |        | XXXX         |

|                             |                         | 31:16         | _        | _     | _     | _     | _     | _         | _      |         |                     |      | CI    | HELRU<24:1 | 6>     |       |           |        | 0000         |

| 4080                        | CHELRU                  | 15:0          |          |       |       |       |       |           |        | CHELR   | J<15:0>             |      | 0.    |            |        |       |           |        | 0000         |

|                             |                         | 31:16         |          |       |       |       |       |           |        |         |                     |      |       |            |        |       |           |        | xxxx         |

| 4090                        | CHEHIT                  | 15:0          |          |       |       |       |       |           |        | CHEHI   | <sup>-</sup> <31:0> |      |       |            |        |       |           |        | xxxx         |

|                             |                         | 31:16         |          |       |       |       |       |           |        |         |                     |      |       |            |        |       |           |        | xxxx         |

| 40A0                        | CHEMIS                  | 15:0          |          |       |       |       |       |           |        | CHEMIS  | 5<31:0>             |      |       |            |        |       |           |        | xxxx         |

| 4000                        | CHEPFABT                | 31:16         |          |       |       |       |       |           |        | CHEPFAI | OT -21-0-           |      |       |            |        |       |           |        | xxxx         |

| 4000                        | CHEFFABI                | 15:0          |          |       |       |       |       |           |        | UNEPFAI | 51<31.0>            |      |       |            |        |       |           |        | xxxx         |

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Reset value is dependent on DEVCFGx configuration. 1:

2:

Note

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 31.24        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 23.10        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 15.0         | _                 | _                 | —                    | _                    | _                 |                   | —                      | _                |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |

|              | DIGLI             | DIVIALI           |                      | DIOLIN               |                   | ONCIULI           | EOFEF <sup>(3,5)</sup> | PIDEF            |  |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear |                           | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

|              |                   |                       |                       |                      |                   | •                         |                  | ,                |

|--------------|-------------------|-----------------------|-----------------------|----------------------|-------------------|---------------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0                   | U-0                   | U-0                  | U-0               | U-0                       | U-0              | U-0              |

| 31.24        | —                 | —                     | —                     | _                    | —                 | _                         | _                | —                |

| 00.40        | U-0               | U-0                   | U-0                   | R/W-0                | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     |                      |                   | FSIZE<4:0> <sup>(1)</sup> | )                |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                | U-0               | U-0                       | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup> | —                 | —                         | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                  | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup> | TXREQ             | RTREN                     | TXPR             | <1:0>            |

#### **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | E<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|---------------------------------------|

|---------------------------------------|-----------|---------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

#### bit 15 Unimplemented: Read as '0'

#### bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

#### 0 = No effect

#### bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message }$

#### bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{This bit is not used and has no effect.}}$   $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$ (FIFO configured as a Receive FIFO)

1 =Only data bytes will be stored in the FIFO

0 = Full message is stored, including identifier

#### bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# TABLE 25-5:ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L,<br/>PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H,<br/>PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX764F128H, PIC32MX764F128H,<br/>PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| sseptimize         and the sector         and the sector <th< th=""><th>:16        5:0        :16        :16    </th><th>30/14<br/></th><th>29/13<br/>—<br/>—<br/>—</th><th>28/12<br/></th><th><b>27/11</b><br/>—<br/>RESET</th><th>26/10</th><th>25/9</th><th>24/8</th><th>its<br/>23/7</th><th>22/6</th><th>21/5</th><th>20/4</th><th>19/3</th><th>18/2</th><th>17/1</th><th>16/0</th><th>All Resets</th></th<> | :16        5:0        :16        :16 | 30/14<br> | 29/13<br>—<br>—<br>— | 28/12<br> | <b>27/11</b><br>—<br>RESET | 26/10      | 25/9 | 24/8          | its<br>23/7 | 22/6 | 21/5 | 20/4   | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------|----------------------|-----------|----------------------------|------------|------|---------------|-------------|------|------|--------|---------------|-----------|-----------|----------|------------|

| 9260         EMAC1<br>SUPP         31:10<br>15:0           9270         EMAC1<br>TEST         31:10<br>15:0           9280         EMAC1<br>31:10         31:10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | :16        5:0        :16        :16 |           |                      | _         | —<br>RESET                 |            |      |               | 23/7        | 22/6 | 21/5 | 20/4   | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

| 9260         EMAC1<br>SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1<br>31:16         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5:0 —<br>:16 —<br>5:0 —<br>:16 —     | -         | _                    |           |                            | —          | _    |               |             |      |      |        |               |           |           |          |            |

| 9260         SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | :16 —<br>5:0 —<br>:16 —              | _         |                      | -         |                            |            |      |               | _           | —    | —    |        | _             | _         | —         | _        | 0000       |

| 9270 TEST 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5:0 <u>—</u><br>:16 —                |           | —                    |           | RMII                       | —          | —    | SPEED<br>RMII | -           | -    | —    | -      | —             | -         | -         | _        | 1000       |

| EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | :16 —                                | -         |                      | _         | —                          | _          | _    | _             | _           | _    | _    | -      | —             | _         | _         |          | 0000       |

| erection EMAC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |           | _                    | _         | _                          | _          | —    | _             | _           | _    | _    | -      | _             | TESTBP    | TESTPAUSE | SHRTQNTA | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                      | -         | _                    | _         | _                          | _          | _    | _             | _           | _    | —    | _      | _             | —         | _         | _        | 0000       |

| 9280 MCFG 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5:0 RESET<br>MGMT                    | -         | _                    | _         | —                          | —          | —    | —             | -           | _    |      | CLKSE  | L<3:0>        |           | NOPRE     | SCANINC  | 0020       |

| 9290 EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | :16 —                                | _         | _                    | _         | —                          | _          | _    | _             | _           | _    | _    | _      | _             | _         | _         | _        | 0000       |

| 9290 MCMD 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5:0 —                                | —         | —                    | —         | _                          | —          | _    | —             | —           | _    | _    | _      | _             | —         | SCAN      | READ     | 0000       |

| 92A0 EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | -         |                      |           |                            |            |      | —             | 0000        |      |      |        |               |           |           |          |            |

| MADR 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      | -         | —                    |           | P                          | HYADDR<4:0 | )>   |               | _           | _    | _    |        | R             | EGADDR<4: | 0>        |          | 0100       |

| 92B0 EMAC1 31:16<br>MWTD 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      | —         | —                    | _         | —                          | —          | —    | —             | _           | _    | —    | —      | —             | —         | _         | —        | 0000       |