Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | -                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512lt-80v-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             | A 1 7 |                   |                           | 4                         |

|-------------------|-------------------------------------------------------|-------|-------------------|---------------------------|---------------------------|

|                   |                                                       | B13   |                   |                           | Conductive<br>Thermal Pad |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1    | B56               | B41                       | A51                       |

|                   | A1                                                    |       |                   |                           |                           |

|                   | Polarity Indicator                                    |       | A68               |                           |                           |

| Package<br>Bump # | Full Pin Name                                         |       | Package<br>Bump # | F                         | ull Pin Name              |

| B8                | Vss                                                   |       | B33               | TDO/RA5                   |                           |

| B9                | TMS/RA0                                               |       | B34               | OSC1/CLKI/RC              | 212                       |

| B10               | AERXD1/INT2/RE9                                       |       | B35               | No Connect (N             | C)                        |

| B11               | AN4/C1IN-/CN6/RB4                                     |       | B36               | AETXCLK/SCL               | .1/INT3/RA14              |

| B12               | Vss                                                   |       | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |

| B13               | AN2/C2IN-/CN4/RB2                                     |       | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |

| B14               | PGED1/AN0/CN2/RB0                                     |       | B39               | SDO1/OC1/INT              | [0/RD0                    |

| B15               | No Connect (NC)                                       |       | B40               | SOSCO/T1CK/               | CN0/RC14                  |

| B16               | PGED2/AN7/RB7                                         |       | B41               | Vss                       |                           |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |       | B42               | OC3/RD2                   |                           |

| B18               | AVss                                                  |       | B43               | ETXD2/IC5/PN              | ID12/RD12                 |

| B19               | AN9/C2OUT/RB9                                         |       | B44               | OC5/PMWR/CI               | N13/RD4                   |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |       | B45               | ETXEN/PMD14               | 4/CN15/RD6                |

| B21               | Vdd                                                   |       | B46               | Vss                       |                           |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |       | B47               | No Connect (N             | C)                        |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |       | B48               | VCAP                      |                           |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |       | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |

| B25               | Vss                                                   |       | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |       | B51               | TRCLK/RA6                 |                           |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |       | B52               | PMD0/RE0                  |                           |

| B28               | No Connect (NC)                                       |       | B53               | Vdd                       |                           |

| B29               | SCL3/SDO3/U1TX/RF8                                    |       | B54               | TRD2/RG14                 |                           |

| B30               | VUSB3V3                                               |       | B55               | TRD0/RG13                 |                           |

| B31               | D+/RG2                                                |       | B56               | PMD3/RE3                  |                           |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

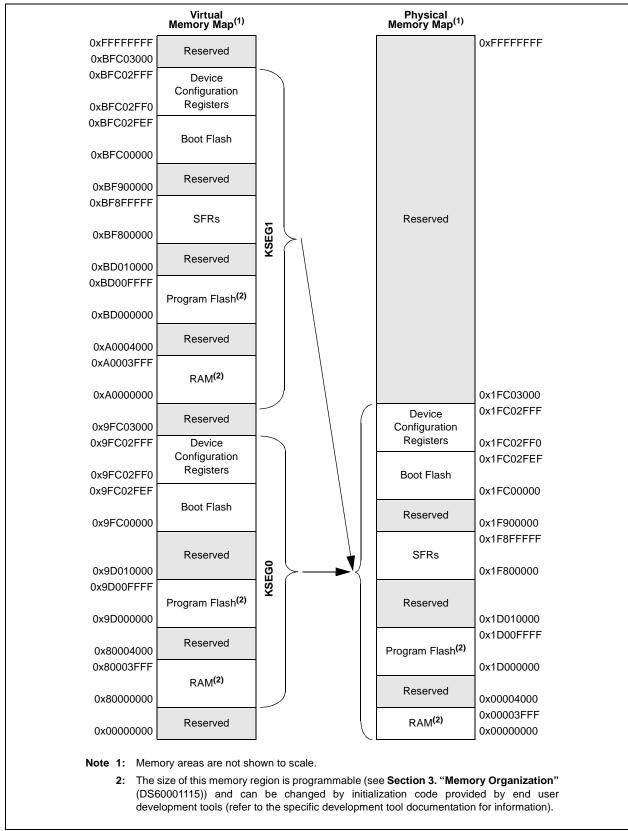

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardware |                                    |                    |  |  |

|------|----------------|--------------------------|------------------------------------|--------------------|--|--|

| R =  | = Readable bit | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |

| -n : | = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | —                 | —                 | _                 | _                 | —                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | —                 | —                 | _                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | —                 | _                 | —                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

## REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **CHBUSY:** Channel Busy bit 1 = Channel is active or has been enabled 0 = Channel is inactive or has been disabled

- bit 14-9 **Unimplemented:** Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 Chain to channel lower in patteral priority (CH1 will be enabled by C

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 =Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

#### bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

- 0 = Channel is disabled on block transfer complete

- bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

#### bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- **Note 1:** The chain selection bit takes effect when chaining is enabled (CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

# PIC32MX5XX/6XX/7XX

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | -                 | -                 | —                 | —                 | _                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 |                   |                   |                   | —                 |                   | —                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | CHPDAT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

## Legend:

| 5                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 |                   | _                 | _                 |                   |                  |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

## REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit  | it W = Writable bit |                      | read as '0'        |

|-------------------|---------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                        |

|           | <ul> <li>1 = Module is enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                            |

|           | <ul><li>1 = Halt in Idle mode</li><li>0 = Continue to operate in Idle mode</li></ul>                                                                      |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                                 |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                            |

|           | <ul><li>1 = 32-bit timer resource capture</li><li>0 = 16-bit timer resource capture</li></ul>                                                             |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                     |

|           | <ul> <li>1 = Timer2 is the counter source for capture</li> <li>0 = Timer3 is the counter source for capture</li> </ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                          |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                     |

|           | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture overflow is occurred</li> <li>0 = No input capture overflow is occurred</li> </ul>                                             |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                              |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

|           |                                                                                                                                                           |

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

## TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |         |        |       |        | •      |              | -             | Bi      | ts    |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|--------|--------------|---------------|---------|-------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10        | 25/9          | 24/8    | 23/7  | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16         | -       | —      | —     | _      |        | _            | —             | -       | _     | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0          | -       | —      | —     | -      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16         | _       | _      | _     | —      | _      | —            | _             | —       | _     | —           | _           | —         | —        |        | -    | _        | 0000       |

| 5240                        |                                 | 15:0          | —       | —      | —     | —      |        |              |               |         | Ba    | ud Rate Ger | erator Regi | ster      |          |        | •    |          | 0000       |

| 5250                        | I2C5TRN                         | 31:16         | —       | —      | —     | —      | _      | —            | _             | —       | _     | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0          | —       | _      | _     | —      | _      | —            | _             | _       |       | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16         | -       |        |       | _      | _      | -            |               | _       | _     | —           | _           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0          | -       |        | —     | —      |        | —            |               | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16         | _       | —      | —     | —      | —      | —            | —             | —       | _     | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | ON      | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16         | —       | _      | _     | _      | _      | _            | —             | —       | _     | —           | —           | _         | _        |        | —    | _        | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT | —     | —      | —      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16         | _       | _      | —     | —      | _      |              | —             |         | _     | _           |             | _         | —        |        | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | -            |               |         |       |             | ADD         | <9:0>     |          |        |      |          | 0000       |

| 5330                        | I2C1MSK                         | 31:16         | _       | _      | _     | _      | _      | -            | _             | -       | _     | _           | —           | -         | _        | -      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       |        | _     | _      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        | 1    |          | 0000       |

| 5340                        | I2C1BRG                         | 31:16         | _       |        |       | _      | _      | —            |               | _       | -     | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0          | _       |        |       | _      |        |              |               |         | Ва    | ud Rate Ger | Ū.          | ster      |          |        | 1    |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16         | _       | —      | —     | _      | _      | _            | _             | _       | _     | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | _            |               | _       |       |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0 | _       | _      |       |        |        | —            |               |         | —     | —           | —           | - Deseive |          | —      | —    | —        | 0000       |

|                             |                                 |               |         |        |       |        |        | _            |               |         |       |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0 | ON      |        | -     | -      |        | -            | —<br>DI001144 | -       | -     | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |               |         | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16         |         |        | _     | _      | _      | —<br>DCI     | —<br>         | -       | -     | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16 | ACKSTAT | TRSTAT |       | _      | _      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0          |         |        |       | _      | _      |              | _             | -       | —     | —           |             | <br><9:0> | —        |        | _    | —        | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |        | _            | _             |         | _     |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0          |         |        |       |        |        |              |               | _       | _     | _           | <br>MSK     | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 | 31:16         |         |        |       |        |        |              |               |         | _     |             |             | < 3.02    |          |        |      | _        | 0000       |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0          | _       |        |       | _      | _      | _            | _             |         | Ra    | ud Rate Ger | erator Regi | ster      |          |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _            | _             | _       | Da    |             |             |           | _        |        | _    | _        | 0000       |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0          | _       | _      | _     |        | _      |              | _             |         |       |             |             | Transmit  | Register |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      |        | _            | _             | _       | _     | _           | _           |           |          |        | _    | _        | 0000       |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0          | _       | _      | _     | _      | _      | _            | _             | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 |               |         |        |       |        |        | Les are show | l<br>         | aire al |       |             |             | 110001100 |          |        |      |          | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

## 21.1 Control Registers

## TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|                                         |                                 |           |           |           |       |       |         |        |        | Bi     | ts      |        |      |       |        |      |       |       |            |

|-----------------------------------------|---------------------------------|-----------|-----------|-----------|-------|-------|---------|--------|--------|--------|---------|--------|------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000 PM0                                | /CON                            | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      |         | _      | _    | _     | —      | _    | —     | _     | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON        | —         | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P  | CS1P   | —    | WRSP  | RDSP  | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —         | —         | —     | —     | —       | —      | —      | —      | —       | —      | —    | —     | —      | —    | —     | —     | 0000       |

| 7010 Pivily                             | NODE                            | 15:0      | BUSY      | IRQM      | <1:0> | INCM  | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITM | A<3:0> |      | WAITE | <1:0> | 0000       |

| 7020 PMA                                |                                 | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7020 PINA                               | IADDR                           | 15:0      | CS2EN/A15 | CS1EN/A14 |       |       |         |        |        |        | ADDR    | <13:0> |      |       |        |      |       |       | 0000       |

| 7000 040                                |                                 | 31:16     |           |           |       |       |         |        |        | DATAOU | T 04.0  |        |      |       |        |      |       |       | 0000       |

| 7030 PMD                                |                                 | 15:0      |           |           |       |       |         |        |        | DATAOU | 1<31:0> |        |      |       |        |      |       |       | 0000       |

| 7040 DM                                 | MDIN                            | 31:16     |           |           |       |       |         |        |        |        | .01.0   |        |      |       |        |      |       |       | 0000       |

| 7040 PM                                 |                                 | 15:0      |           |           |       |       |         |        |        | DATAIN | <31:0>  |        |      |       |        |      |       |       | 0000       |

| 7050 014                                | MAEN                            | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |           |           |       |       |         |        |        | PTEN<  | :15:0>  |        |      |       |        |      |       |       | 0000       |

| 7000 0140                               | 10TAT                           | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      | _       | _      | —    | _     | _      | _    | _     | _     | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF       | IBOV      | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | -     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |  |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | —                 | PTEN14            | _                 | —                 | _                 |                   | PTEN<10:8>       |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Strobe Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- **Note 1:** The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |

| 31:24        | —                       | —                 | _                 | —                 | —                      | —                 | CAL<9                  | ):8>             |

| 23:16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |

| 23.10        |                         |                   |                   | CAL<              | :7:0>                  |                   |                        |                  |

| 15:8         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |

| 0.61         | ON <sup>(1,2)</sup>     |                   | SIDL              | —                 | —                      | -                 |                        | _                |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | —                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |

|              |                         |                   |                   |                   |                        |                   |                        |                  |

### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 **CAL<9:0>:** RTC Drift Calibration bits, which contain a signed 10-bit integer value

| ~0 10    |                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------|

|          | 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute                   |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •<br>1000000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute               |

|          | 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute                     |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute                         |

|          | 000000000 = No adjustment                                                                                |

| bit 15   | ON: RTCC On bit <sup>(1,2)</sup>                                                                         |

|          | 1 = RTCC module is enabled                                                                               |

|          | 0 = RTCC module is disabled                                                                              |

| bit 14   | Unimplemented: Read as '0'                                                                               |

| bit 13   | SIDL: Stop in Idle Mode bit                                                                              |

|          | 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode                                          |

|          | 0 = Continue normal operation in Idle mode                                                               |

| bit 12-8 | Unimplemented: Read as '0'                                                                               |

| bit 7    | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(3)</sup>                                            |

|          | 1 = RTCC Seconds Clock is selected for the RTCC pin                                                      |

|          | 0 = RTCC Alarm Pulse is selected for the RTCC pin                                                        |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit                                                                   |

|          | 1 = RTCC Clock is actively running                                                                       |

|          | 0 = RTCC Clock is not running                                                                            |

| bit 5-4  | Unimplemented: Read as '0'                                                                               |

|          | •                                                                                                        |

| Note 1:  | The ON bit is only writable when RTCWREN = 1.                                                            |

| 2:       | When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the |

|          | SYSCLK cycle immediately following the instruction that clears the module's ON bit.                      |

| 3:       | Requires $RTCOE = 1$ (RTCCON<0>) for the output to be active.                                            |

| 4:       | The RTCWREN bit can only be set when the write sequence is enabled.                                      |

| 5:       | This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).        |

|          |                                                                                                          |

|          |                                                                                                          |

Note: This register is only reset on a Power-on Reset (POR).

© 2009-2016 Microchip Technology Inc.

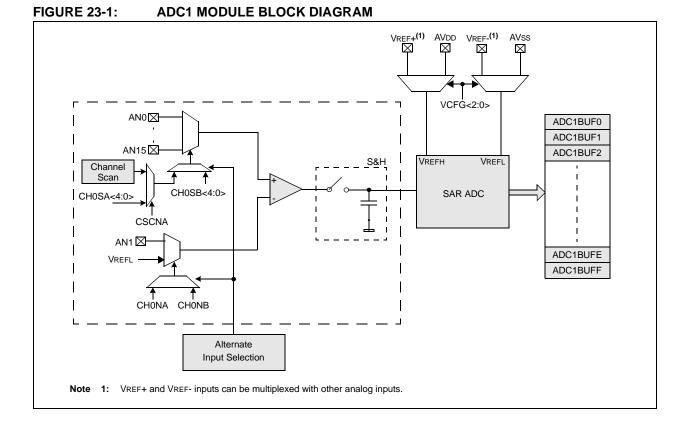

## 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

## TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |                                              |                                              |       |       |       |       |        | Bi          | ts        |          |      |      |      |      |      |      |            |

|-----------------------------|------------------|---------------|----------------------------------------------|----------------------------------------------|-------|-------|-------|-------|--------|-------------|-----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15                                        | 30/14                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |                                              |                                              |       |       |       |       | ADC Re | sult Word B | (ADC1BUFE | 3<31:0>) |      |      |      |      |      |      | 0000       |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |                                              | ADC Result Word C (ADC1BUFC<31:0>) 0000 0000 |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 | ADC Result Word D (ADC1BUFD<31:0>) 0000 0000 |                                              |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 | ADC Result Word E (ADC1BUFE<31:0>) 0000 0000 |                                              |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |                                              |                                              |       |       |       |       | ADC Re | sult Word F | (ADC1BUFF | -<31:0>) |      |      |      |      |      |      | 0000       |

= unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: x = unknown value on Reset

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

## 25.1 Control Registers

### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| No.         No. <th>ŝ</th> <th></th> <th>its</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ŝ                          |                                 |           |       |        |        |       |       |       |         |          | its       |         |       |        |         |         |         |         |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------|-------|--------|--------|-------|-------|-------|---------|----------|-----------|---------|-------|--------|---------|---------|---------|---------|------------|

| 900         8116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13  | 28/12 | 27/11 | 26/10 | 25/9    |          |           | 22/6    | 21/5  | 20/4   | 19/3    | 18/2    | 17/1    | 16/0    | All Resets |

| 100         100         -         SI(1)         -         -         TXT         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< td=""><td></td><td>FTUOONIA</td><td>31:16</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>PTV&lt;</td><td>:15:0&gt;</td><td></td><td></td><td></td><td>1</td><td>1</td><td></td><td>1</td><td>0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | FTUOONIA                        | 31:16     |       |        |        |       |       |       |         | PTV<     | :15:0>    |         |       |        | 1       | 1       |         | 1       | 0000       |

| 9010       FTHC012       15.0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9000                       | ETHCON1                         | 15:0      | ON    | _      | SIDL   | _     | —     | _     | TXRTS   | RXEN     | AUTOFC    | _       | _     | MANFC  |         | —       | _       | BUFCDEC | 0000       |

| Note       9020     PTHXX     31:6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9010                       | ETHCON2                         |           | _     | _      | —      | -     | —     | -     | -       |          | _         |         | _     | _      | _       | -       | _       | _       | 0000       |

| 9020       FH/XS1       15.0       -       -       -       -       -       -       -       000       000       000       ETHRS1       31:6       -       -       -       000       000       000       ETHRS1       31:6       -       -       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3010                       | LINCONZ                         |           | —     | —      | _      | —     | _     |       |         |          |           | >       |       |        |         | —       | —       | —       | 0000       |

| Image: marrow of the strephysical strep                  | 9020                       | ETHTXST                         |           |       |        |        |       |       |       |         |          | R<31:16>  |         |       |        |         |         |         |         | 0000       |