Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

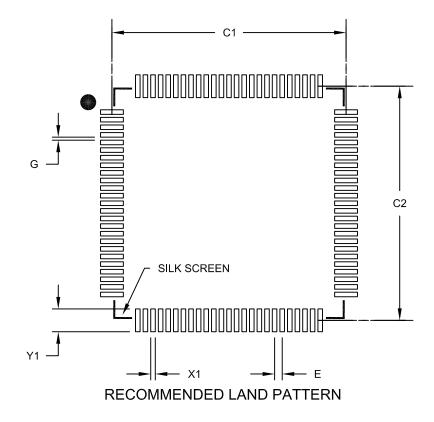

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx795f512lt-80v-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1 | : PINOU            | T I/O DES       |                     | NS (CONT        | INUED | )      |                                                                                                                |  |  |

|-----------|--------------------|-----------------|---------------------|-----------------|-------|--------|----------------------------------------------------------------------------------------------------------------|--|--|

|           |                    | Pin Nun         | nber <sup>(1)</sup> |                 | Pin   | Buffer |                                                                                                                |  |  |

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре  | Туре   | Description                                                                                                    |  |  |

| PMD0      | 60                 | 93              | A4                  | B52             | I/O   | TTL/ST | Parallel Master Port data                                                                                      |  |  |

| PMD1      | 61                 | 94              | B4                  | A64             | I/O   | TTL/ST | (Demultiplexed Master mode) or                                                                                 |  |  |

| PMD2      | 62                 | 98              | B3                  | A66             | I/O   | TTL/ST | address/data (Multiplexed Master modes)                                                                        |  |  |

| PMD3      | 63                 | 99              | A2                  | B56             | I/O   | TTL/ST | nodes)                                                                                                         |  |  |

| PMD4      | 64                 | 100             | A1                  | A67             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD5      | 1                  | 3               | D3                  | B2              | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD6      | 2                  | 4               | C1                  | A4              | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD7      | 3                  | 5               | D2                  | B3              | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD8      | —                  | 90              | A5                  | A61             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD9      | —                  | 89              | E6                  | B50             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD10     | —                  | 88              | A6                  | A60             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD11     | _                  | 87              | B6                  | B49             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD12     | _                  | 79              | A9                  | B43             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD13     | _                  | 80              | D8                  | A54             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD14     | _                  | 83              | D7                  | B45             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMD15     | _                  | 84              | C7                  | A56             | I/O   | TTL/ST |                                                                                                                |  |  |

| PMALL     | 30                 | 44              | L8                  | A29             | ο     | _      | Parallel Master Port address latch<br>enable low byte (Multiplexed Master<br>modes)                            |  |  |

| PMALH     | 29                 | 43              | К7                  | B24             | 0     | _      | Parallel Master Port address latch<br>enable high byte (Multiplexed Master<br>modes)                           |  |  |

| PMRD      | 53                 | 82              | B8                  | A55             | 0     | _      | Parallel Master Port read strobe                                                                               |  |  |

| PMWR      | 52                 | 81              | C8                  | B44             | 0     | _      | Parallel Master Port write strobe                                                                              |  |  |

| VBUS      | 34                 | 54              | H8                  | A37             | I     | Analog | USB bus power monitor                                                                                          |  |  |

| VUSB3V3   | 35                 | 55              | H9                  | B30             | Р     | _      | USB internal transceiver supply. If the<br>USB module is <i>not</i> used, this pin mus<br>be connected to VDD. |  |  |

| VBUSON    | 11                 | 20              | H1                  | A12             | 0     | _      | USB Host and OTG bus power contro<br>output                                                                    |  |  |

| D+        | 37                 | 57              | H10                 | B31             | I/O   | Analog | USB D+                                                                                                         |  |  |

| D-        | 36                 | 56              | J11                 | A38             | I/O   | Analog | USB D-                                                                                                         |  |  |

| USBID     | 33                 | 51              | K10                 | A35             | Ι     | ST     | USB OTG ID detect                                                                                              |  |  |

| C1RX      | 58                 | 87              | B6                  | B49             | I     | ST     | CAN1 bus receive pin                                                                                           |  |  |

| C1TX      | 59                 | 88              | A6                  | A60             | 0     |        | CAN1 bus transmit pin                                                                                          |  |  |

| AC1RX     | 32                 | 40              | K6                  | A27             | I     | ST     | Alternate CAN1 bus receive pin                                                                                 |  |  |

| AC1TX     | 31                 | 39              | L6                  | B22             | 0     | —      | Alternate CAN1 bus transmit pin                                                                                |  |  |

| C2RX      | 29                 | 90              | A5                  | A61             | I     | ST     | CAN2 bus receive pin                                                                                           |  |  |

|           | 21                 | 89              | E6                  | B50             | 0     | —      | CAN2 bus transmit pin                                                                                          |  |  |

| C2TX      |                    |                 | 1                   | 1               | 1     |        | Alternate CAN2 bus receive pin                                                                                 |  |  |

#### PINOLIT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- Shifter and store aligner

### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16 bit wide *rs*, 15 iterations are skipped and for a 24 bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT<br/>LATENCIES AND REPEAT RATES

# 4.2 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

# TABLE 4-2: BUS MATRIX REGISTER MAP

| ress                        | L                       | e         |                |       |       |       |       |           |      |      |          | Bits       |      |           |           |            |          |          |               |

|-----------------------------|-------------------------|-----------|----------------|-------|-------|-------|-------|-----------|------|------|----------|------------|------|-----------|-----------|------------|----------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15          | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7     | 22/6       | 21/5 | 20/4      | 19/3      | 18/2       | 17/1     | 16/0     | All<br>Resets |

| 0000                        |                         | 31:16     | —              |       | —     | —     |       | BMXCHEDMA | —    | _    |          | —          | —    | BMXERRIXI | BMXERRICD | BMXERRDMA  | BMXERRDS | BMXERRIS | 001F          |

| 2000 BMXCON <sup>(1)</sup>  | 15:0                    | —         | -              | _     | _     |       | _     | _         | _    | _    | BMXWSDRM | _          | _    | _         | В         | MXARB<2:0> |          | 0041     |               |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —              | -     | -     | _     | _     | _         | —    | -    | _        | —          | —    | —         | _         | —          | _        | —        | 0000          |

| 2010                        | DIVINDINF DAV /         | 15:0      |                |       |       |       |       |           |      | -    | BMXD     | (PBA<15:0> |      | -         |           | -          | -        |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | —              | —     | —     | —     | —     |           | —    | —    | —        | _          | —    | -         | —         | —          | —        | —        | 0000          |

| 2020                        | DWIXDODDI               | 15:0      | BMXDUDBA<15:0> |       |       |       |       |           |      | 0000 |          |            |      |           |           |            |          |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _              | —     | —     |       | _     | —         | _    | —    | _        | —          | _    | —         | —         | —          | —        | —        | 0000          |

| 2000                        |                         | 15:0      |                |       |       |       |       |           |      |      | BMXDL    | JPBA<15:0> |      |           |           |            |          |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |                |       |       |       |       |           |      |      | BMXDF    | RMSZ<31:0> |      |           |           |            |          |          | xxxx          |

|                             |                         | 15:0      |                |       |       |       |       |           |      |      |          |            |      |           |           |            |          |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —              | —     | -     |       | —     | —         | _    |      | —        | _          | —    | —         |           | BMXPUPB    | A<19:16> |          | 0000          |

|                             |                         | 15:0      |                |       |       |       |       |           |      |      | BMXPL    | JPBA<15:0> |      |           |           |            |          |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |                |       |       |       |       |           |      |      | BMXPF    | MSZ<31:0>  |      |           |           |            |          |          | xxxx          |

|                             |                         | 15:0      |                |       |       |       |       |           |      |      |          |            |      |           |           |            |          |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |                |       |       |       |       |           |      |      | вмхво    | OTSZ<31:0> |      |           |           |            |          |          | 0000          |

|                             |                         | 15:0      |                |       |       |       |       |           |      |      |          |            |      |           |           |            |          |          | 3000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# PIC32MX5XX/6XX/7XX

NOTES:

# PIC32MX5XX/6XX/7XX

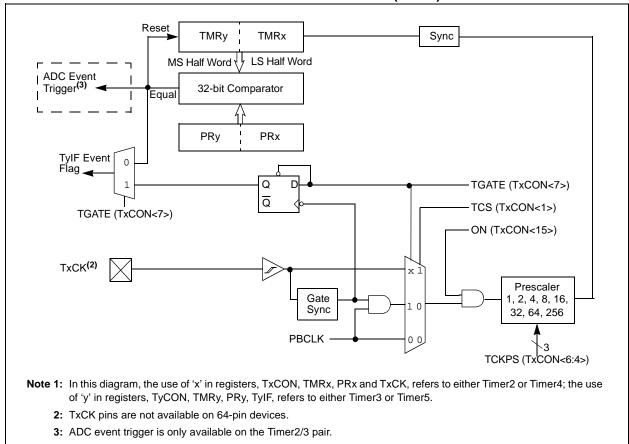

### FIGURE 14-2: TIMER2/3 AND TIMER4/5 BLOCK DIAGRAM (32-BIT)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        |                   | _                   | _                  |                   | _                   |                   |                  | —                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | -                   | _                  | -                 | -                   | _                 | —                | —                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                   | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

#### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS2 and PMCS1 function as Chip Select

- 01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

- 00 = PMCS2 and PMCS1 function as address bits 15 and  $14^{(2)}$

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                         | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|----------------------------------------------------------|------------------|--|--|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                                                    | R/W-0            |  |  |

| 31:24        | —                       | —                 | —                 | —                 | —                      | —                 | - CAL<9:8>                                               |                  |  |  |

| 00.40        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                                                    | R/W-0            |  |  |

| 23:16        |                         |                   |                   | CAL<              | :7:0>                  |                   |                                                          |                  |  |  |

| 15.0         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                                                      | U-0              |  |  |

| 15:8         | ON <sup>(1,2)</sup>     | —                 | SIDL              | —                 | —                      | -                 | 25/17/9/1<br>R/W-0<br>CAL<<br>R/W-0<br>U-0<br>U-0<br>R-0 |                  |  |  |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                                                      | R/W-0            |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | —                 | —                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup>                                   | RTCOE            |  |  |

|              |                         |                   |                   |                   |                        |                   |                                                          |                  |  |  |

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value

| Dit 20-10 | CALS. O. TTO Drift Calibration bits, which contain a signed to bit integer value                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute                                                                                       |

|           | •                                                                                                                                                                            |

|           |                                                                                                                                                                              |

|           | 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute<br>0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute |

|           | •                                                                                                                                                                            |

|           |                                                                                                                                                                              |

|           | 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute<br>0000000000 = No adjustment                                                               |

| bit 15    | ON: RTCC On bit <sup>(1,2)</sup>                                                                                                                                             |

|           | <ul> <li>1 = RTCC module is enabled</li> <li>0 = RTCC module is disabled</li> </ul>                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                  |

|           | 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode                                                                                                              |

|           | 0 = Continue normal operation in Idle mode                                                                                                                                   |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                   |

| bit 7     | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(3)</sup>                                                                                                                |

|           | <ul> <li>1 = RTCC Seconds Clock is selected for the RTCC pin</li> <li>0 = RTCC Alarm Pulse is selected for the RTCC pin</li> </ul>                                           |

| bit 6     | RTCCLKON: RTCC Clock Enable Status bit                                                                                                                                       |

|           | 1 = RTCC Clock is actively running                                                                                                                                           |

|           | 0 = RTCC Clock is not running                                                                                                                                                |

| bit 5-4   | Unimplemented: Read as '0'                                                                                                                                                   |

| Note 1:   | The ON bit is only writable when RTCWREN = 1.                                                                                                                                |

| 2:        | When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the                                                                     |

|           | SYSCLK cycle immediately following the instruction that clears the module's ON bit.                                                                                          |

| 3:        | Requires $RTCOE = 1$ (RTCCON<0>) for the output to be active.                                                                                                                |

| 4:        | The RTCWREN bit can only be set when the write sequence is enabled.                                                                                                          |

| 5:        | This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).                                                                            |

|           |                                                                                                                                                                              |

Note: This register is only reset on a Power-on Reset (POR).

© 2009-2016 Microchip Technology Inc.

| Bit<br>Range       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|

| 04.04              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24              |                   | HR10-             | <3:0>             |                   |                                    | HR01<3:0>         |                  |                  |  |

| 23:16              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

|                    |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                         |                   |                  |                  |  |

| 45.0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8               |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                         |                   |                  |                  |  |

| 7.0                | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |  |

| 7:0                | —                 | —                 | —                 | —                 | —                                  | —                 | —                | —                |  |

|                    |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| Legend:            |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| R = Readable bit V |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |

|                    |                   |                   |                   |                   |                                    |                   |                  |                  |  |

#### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| IX – IXeauable bit            |                            |                                | it, read as 0      |

|-------------------------------|----------------------------|--------------------------------|--------------------|

| -n = Value at POR             | '1' = Bit is set           | '0' = Bit is cleared           | x = Bit is unknown |

|                               |                            |                                |                    |

| bit 31-28 HR10<3:0>: Binary-0 | Coded Decimal Value of Hou | rs bits, 10 digits; contains a | value from 0 to 2  |

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|

| 04-04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24            |                   | YEAR1             | 0<3:0>            |                   |                                    | YEAR01<3:0>       |                  |                  |  |

| 23:16            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

|                  |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                       |                   |                  |                  |  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8             |                   | DAY10             | <3:0>             |                   | DAY01<3:0>                         |                   |                  |                  |  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0              | —                 | —                 | _                 | _                 |                                    |                   |                  |                  |  |

|                  |                   | •                 |                   |                   | •                                  |                   |                  |                  |  |

| Legend:          |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |

0' = Bit is cleared

# REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   | _                 | _                 |                   |                   | WDAY0             | )1<3:0>          |                  |

# REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Logona.           |                  |                        |                    | 1 |

|-------------------|------------------|------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        | I |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |   |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

# PIC32MX5XX/6XX/7XX

|              |                   |                   |                   |                   |                   | •                 |                    | ,                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

| 31:24        | R-x                | R-x                |  |  |  |

| 31.24        | CiFIFOUAn<31:24>  |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 23:16        | R-x                | R-x                |  |  |  |

| 23.10        |                   | CiFIFOUAn<23:16>  |                   |                   |                   |                   |                    |                    |  |  |  |

| 45.0         | R-x                | R-x                |  |  |  |

| 15:8         |                   |                   |                   | CiFIFOU           | An<15:8>          |                   |                    |                    |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7:0          |                   | •                 |                   | CiFIFOU           | IAn<7:0>          |                   |                    |                    |  |  |  |

#### REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24              | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10              | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 15:8               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0               | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 7:0                | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0 — — — CiFIFOCI |                   |                   |                   |                   | CiFIFOCI<4:0      | >                 |                  |                  |

#### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

### 25.1 Control Registers

#### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| No.         No. <th>ŝ</th> <th></th> <th>its</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ŝ                          |                                 |           |                 |                                                                                          |       |       |       |       |         |          | its       |      |      |        |      |      |      |      |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------|-----------------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|---------|----------|-----------|------|------|--------|------|------|------|------|------------|

| 900         8116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15           | 30/14                                                                                    | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    |          |           | 22/6 | 21/5 | 20/4   | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 100         100         -         SI(1)         -         -         TXT         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< td=""><td></td><td>FTUOONIA</td><td>31:16</td><td></td><td colspan="5">PTV&lt;15:0&gt; 0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | FTUOONIA                        | 31:16     |                 | PTV<15:0> 0000                                                                           |       |       |       |       |         |          |           |      |      |        |      |      |      |      |            |

| 9010       FTHC012       15.0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9000                       | ETHCON1                         | 15:0      | ON              | ON - SIDL TXRTS RXEN AUTOFC MANFC BUFCDEC 0                                              |       |       |       |       |         | 0000     |           |      |      |        |      |      |      |      |            |

| Note       9020     PTHXX     31:6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9010                       | ETHCON2                         |           | _               | _                                                                                        | —     | -     | —     | -     | -       |          | _         |      | _    | _      | _    | -    | _    | _    | 0000       |

| 9020       FH/XS1       15.0       -       -       -       -       -       -       -       000       000       000       ETHRS1       31:6       -       -       -       000       000       000       ETHRS1       31:6       -       -       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3010                       | LINGONZ                         |           | —               | —                                                                                        | _     | —     | _     |       |         |          |           | >    |      |        |      | —    | —    | —    | 0000       |

| Image: marrow of the strephysical strep                  | 9020                       | ETHTXST                         |           |                 |                                                                                          |       |       |       |       |         |          | R<31:16>  |      |      |        |      |      |      |      | 0000       |

| 9030       ETHRNS       15.0       -       -       0       0         9040       ETHRND       31:6       -       -       -       00       00       00       15.0       -       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>TXSTADI</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |                                 |           |                 |                                                                                          |       |       |       |       | TXSTADI |          |           |      |      |        |      |      |      | _    | 0000       |

| 9040         ETHHT0         31:6<br>15:0         Image: State                                               | 9030                       | ETHRXST                         |           |                 |                                                                                          |       |       |       |       |         |          | )R<31:16> |      |      |        |      |      |      |      | 0000       |

| 9040         ETHHT0         15.0         Image: Final state stat                                                  |                            |                                 |           |                 |                                                                                          |       |       |       |       | RXSTAD  | DR<15:2> |           |      |      |        |      |      | —    | —    | 0000       |

| 9050         ETHHTI         31.16<br>15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9040                       | ETHHT0                          |           |                 |                                                                                          |       |       |       |       |         | HT<      | 31:0>     |      |      |        |      |      |      |      | 0000       |

| 900         EHH11         15.0         H1<63:32         H1<63:32         H1         000         H1         000         H1         000         H1         000         H1         000         H1         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000         000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                 |           |                 | 0000                                                                                     |       |       |       |       |         |          |           |      |      |        |      |      |      |      |            |

| 9060         ETHPMM         31:16<br>15:0         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:17         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16         91:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9050                       | ETHHT1                          |           |                 |                                                                                          |       |       |       |       |         | HT<6     | 3:32>     |      |      |        |      |      |      |      | 0000       |