# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | M68000                                                                |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                                      |

| Speed                           | 25MHz                                                                 |

| Co-Processors/DSP               | Communications; RISC CPM                                              |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | -                                                                     |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 5.0V                                                                  |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                       |

| Security Features               | -                                                                     |

| Package / Case                  | 132-BQFP Bumpered                                                     |

| Supplier Device Package         | 132-PQFP (46x46)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc68302eh25c |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ble of Contents

### Table Number

Title

#### Page Number

#### Section 5 Signal Description

| Table 5-1. | Signal Definitions                          | 5-1  |

|------------|---------------------------------------------|------|

|            | Bus Signal Summary—Core and External Master |      |

|            | Bus Signal Summary—IDMA and SDMA            |      |

| Table 5-4. | Serial Interface Pin Functions              | 5-13 |

| Table 5-5. | Typical ISDN Configurations                 | 5-14 |

|            | Typical Generic Configurations              |      |

|            | Mode Pin Functions                          |      |

|            | PCM Mode Signals                            |      |

|            | Baud Rate Generator Outputs                 |      |

### Appendix D MC68302 Applications

| Table D-1. | IDMA Registers                                     | D-23 |

|------------|----------------------------------------------------|------|

|            | Channel Mode Register Bits                         |      |

|            | Channel Status Register Bits                       |      |

|            | PCM Highway Pin Names and Functions                |      |

| Table D-5  | PCM Highway Channel Selection with LISY0 and L1SY1 | D-60 |

#### Appendix E SCC Programming Reference

| Table E-1 (a)  | HDLC Programming Mode Receive and Transmit Buffer           |      |

|----------------|-------------------------------------------------------------|------|

|                | Descriptors for SCCx                                        | E-2  |

| Table E-1 (b). | HDLC Programming Model (Continued) General Parameter and    |      |

|                | HDLC Protocol-Specific RAM for SCCx                         | E-2  |

| Table E-1 (c)  | SCCx Register Set                                           | E-3  |

| Table E-1 (d). | General Registers (Only One Set)                            | E-3  |

| Table E-2 (a)  | UART Programming Model Receive and Transmit Buffer          |      |

|                | Descriptors for SCCx                                        | E-15 |

| Table E-2 (b)  | UART Programming Model (Continued) General Parameter and    |      |

|                | UART Protocol-Specific RAM for SCCx                         | E-16 |

| Table E-2 (c)  | SCCx Register Set                                           | E-16 |

| Table E-2 (d). | General Registers (Only One Set)                            | E-16 |

| Table E-3 (a). | Transparent Programming Model Receive and Transmit Buffer   |      |

|                | Descriptors for SCCx                                        | E-31 |

| Table E-3 (b). | Transparent Programming Model (Continued) General Parameter |      |

|                | and Transparent Protocol-Specific RAM for SCCx              | E-31 |

| Table E-3 (c). | SCCx Register Set                                           | E-32 |

| Table E-3 (d). | General Registers (Only One Set)                            | E-32 |

The maximum transfer rate is calculated from the fact that 16 bits are moved every 8 clocks. The calculation is as follows:

| 16 bits x 16M clocks/sec              | 2 bytes x 16M clocks/sec | <br>4M bytes |

|---------------------------------------|--------------------------|--------------|

| (2 bus cycles) x (4 clocks/bus cycle) | 8 clocks                 | <br>sec      |

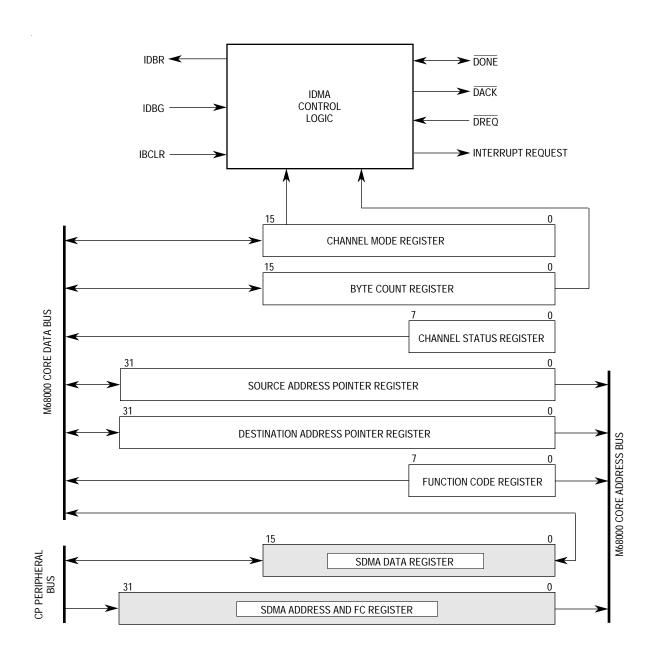

The IDMA controller block diagram is shown in Figure 3-1.

Figure 3-1. IDMA Controller Block Diagram

### 3.1.2 IDMA Registers (Independent DMA Controller)

The IDMA has six registers that define its specific operation. These registers include a 32bit source address pointer register (SAPR), a 32-bit destination address pointer register

The DAPR contains 24 (A23–A0) address bits of the destination operand used by the IDMA to access memory or memory-mapped peripheral controller registers. During the IDMA write cycle, the address on the master address bus is driven from this register. The DAPR may be programmed by the DAPI bit to be incremented or remain constant after each operand transfer.

The register is incremented using unsigned arithmetic and will roll over if overflow occurs. For example, if a register contains \$00FFFFFF and is incremented by one, it will roll over to \$00000000. This register can be incremented by one or two depending on the DSIZE bit and the starting address.

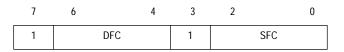

### 3.1.2.4 Function Code Register (FCR)

The FCR is an 8-bit register.

The SFC and the DFC bits define the source and destination function code values that are output by the IDMA and the appropriate address registers during an IDMA bus cycle. The address space on the function code lines may be used by an external memory management unit (MMU) or other memory-protection device to translate the IDMA logical addresses to proper physical addresses. The function code value programmed into the FCR is placed on pins FC2–FC0 during a bus cycle to further qualify the address bus value.

### NOTE

This register is undefined following power-on reset. The user should always initialize it and should not use the function code value "111" in this register.

### 3.1.2.5 Byte Count Register (BCR)

This 16-bit register specifies the amount of data to be transferred by the IDMA; up to 64K bytes (BCR = 0) is permitted. This register is decremented once for each byte transferred successfully. BCR may be even or odd as desired. DMA activity will terminate as soon as this register reaches zero. Thus, an odd number of bytes may be transferred in a 16-bit operand scenario.

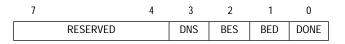

### 3.1.2.6 Channel Status Register (CSR)

The CSR is an 8-bit register used to report events recognized by the IDMA controller. On recognition of an event, the IDMA sets its corresponding bit in the CSR (regardless of the INTE and INTN bits in the CMR). The CSR is a memory-mapped register which may be read at any time. A bit is cleared by writing a one and is left unchanged by writing a zero. More than one bit may be cleared at a time, and the register is cleared at reset.

Bits 7–4—These bits are reserved for future use.

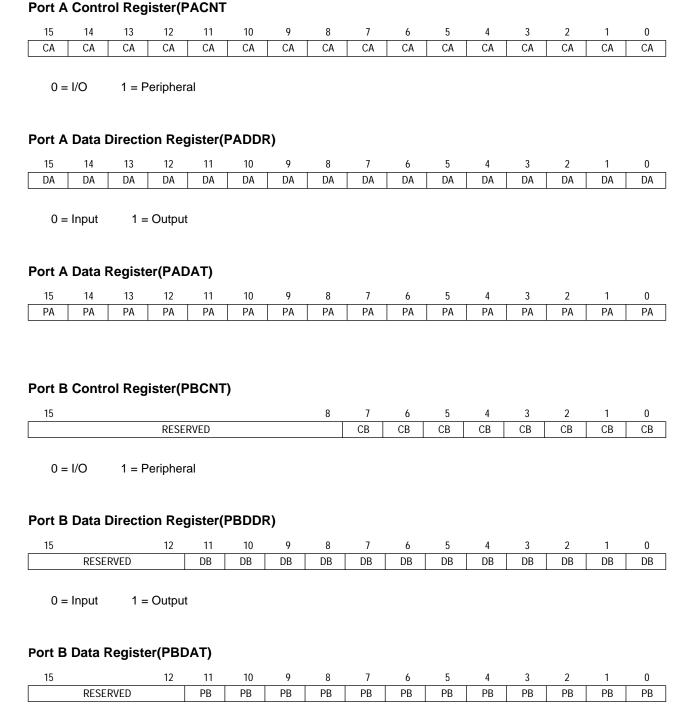

### Figure 3-6. Parallel I/O Port Registers

### 3.4 DUAL-PORT RAM

The CP has 1152 bytes of static RAM configured as a dual-port memory. The dual-port RAM can be accessed by the CP main controller or by one of three bus masters: the M68000 core, the IDMA, or an external master. The M68000 core and the IDMA access the RAM synchro-

# stem Integration Block (SIB)

nously with no wait states. The external master requests the M68000 bus using the BR pin and is granted bus ownership. The external master must then access the RAM synchronously with respect to the IMP system clock with zero or one wait state, or asynchronously as determined by the EMWS and SAM bits in the system control register. Except for several locations initialized by the CP, the dual-port RAM is undefined at power-on reset but is not modified by successive resets. The RAM is divided into two parts: parameter RAM and system RAM.

The 576-byte parameter RAM area includes pointers, counters, and registers used with the serial ports. This area is accessed by the CP during communications processing. Any individual locations not required in a given application may be used as general-purpose RAM.

The 576-byte system RAM is a general-purpose RAM, which may be used as M68000 data and/or program RAM or CP microcode RAM. As data RAM, it can include serial port data buffers or can be used for other purposes such as a no-wait-state cache for the M68000 core. As CP microcode RAM, it is used exclusively to store microcode for the CP main controller, allowing the development of special protocols or protocol enhancements, under special arrangement with Motorola. Appendix C discusses available offerings.

The RAM block diagram is shown in Figure 3-7. The M68000 core, the IDMA, and the external master access the RAM through the IMP bus interface unit (BIU) using the M68000 bus. When an access is made, the BIU generates a wait signal to the CP main controller to prevent simultaneous access of the RAM. The CP main controller waits for one cycle to allow the RAM to service the M68000 bus cycle and then regenerates its RAM cycle. This mechanism allows the RAM to be accessed synchronously by the M68000 core, IDMA, or external master without wait states. Thus, during the four-clock M68000 memory cycle, three internal accesses by the CP main controller may occur. The BIU also provides the DTACK signal output when the RAM and on-chip registers are accessed by any M68000 bus master.

### 4.5.11.13 UART Mode Register.

Each SCC mode register is a 16-bit, memory- mapped, read-write register that controls the SCC operation. The term UART mode register refers to the protocol-specific bits (15–6) of the SCC mode register when that SCC is configured as a UART. The read-write UART mode register is cleared by reset.

| 15   | 14   | 13  | 12  | 11  | 10  | 9   | 8  | 7    | 6  | 5 |                      | 0 |

|------|------|-----|-----|-----|-----|-----|----|------|----|---|----------------------|---|

| TPM1 | TPM0 | RPM | PEN | UM1 | UM0 | FRZ | CL | RTSM | SL |   | COMMON SCC MODE BITS |   |

TPM1–TPM0—Transmitter Parity Mode

TMP1—TMP0 select the type of parity to be performed.

- 00 = Odd parity; always send an odd number of ones.

- 01 = Force low parity; always send a zero in the parity bit position.

- 10 = Even parity; always send an even number of ones.

- 11 = Force high parity; always send a one in the parity bit position.

**RPM**—Receiver Parity Mode

- 0 = Odd parity

- 1 = Even parity

When odd parity is selected, the receiver will count the number of ones in the data word. If the total number of ones is not an odd number, the parity bit is set to one to produce an odd number of ones. If the receiver counts an even number of ones, an error in transmission has occurred. Similarly, for even parity, an even number of ones must result from the calculation performed at both ends of the line.

PEN—Parity Enable

- 0 = No parity

- 1 = Parity is enabled for the transmitter and receiver as determined by the parity mode bits.

### UM1–UM0–UART Mode 1–0

- 00 = Normal UART operation. Multidrop mode is disabled for point-to-point operation and an idle-line wakeup is selected. In the idle-line wakeup mode, the UART receiver is re-enabled by an idle string of 9 to 13 consecutive ones (depending on character length and parity mode).

- 01 = In the multidrop mode, an additional address/data bit is transmitted with each character. The multidrop asynchronous modes are compatible with the Motorola MC68681 DUART, the Motorola MC68HC11 SCI interface, and the Motorola DSP56000 SCI interface. UM0 is also used to select the wakeup mode before enabling the receiver or issuing the ENTER HUNT MODE command. Multidrop mode is enabled and an address bit wakeup is selected. In the address bit wakeup mode, the UART receiver is re-enabled when the last data bit (the 8th or 9th) in a character is one. This configuration means that the received character is an address, which should be processed by all inactive processors. The IMP re-

The 8- or 16-bit control field provides a flow control number and defines the frame type (control or data). The exact use and structure of this field depends upon the protocol using the frame.

Data is transmitted in the data field, which can vary in length depending upon the protocol using the frame. Layer 3 frames are carried in the data field.

Error control is implemented by appending a cyclic redundancy check (CRC) to the frame, which is 16-bits long in most protocols, but may be 32-bits long in some.

When the MODE1–MODE0 bits of an SCC mode register (SCM) select the HDLC mode, then that SCC functions as an HDLC controller. The HDLC controller handles the basic functions of the HDLC/SDLC protocol on either the D channel, a B channel, or from a multiplexed serial interface (IDL, GCI (IOM-2), or PCM highway). When the HDLC controller is used to support the B or D channel of the ISDN, the SCC outputs are internally connected to the physical layer serial interface.

### NOTE

SDLC is fully supported, but the SDLC loop mode (ring configuration) is not supported.

When an SCC in HDLC mode is used with a nonmultiplexed modem interface, then the SCC outputs are connected directly to the external pins. In this case, the serial interface uses seven dedicated pins: transmit data (TXD), receive data (RXD), receive clock (RCLK), transmit clock (TCLK), carrier detect (CD), clear to send (CTS), and request to send (RTS). Other modem signals may be supported through the parallel I/O pins.

The HDLC controller consists of separate transmit and receive sections whose operations are asynchronous with the M68000 core and may be either synchronous or asynchronous with respect to the other SCCs. Up to eight frames may be transmitted or received without M68000 core intervention. When the HDLC controller is connected to one of the multiplexed physical interface options (IDL, GCI, or PCM highway), the receive and transmit clocks are identical and are supplied externally by the physical layer. In non-ISDN applications, each clock can be supplied either from the baud rate generator or externally. The baud rate generator is discussed more fully in 4.5.2 SCC Configuration Register (SCON).

The HDLC controller key features are as follows:

- Flexible Data Buffers with Multiple Buffers per Frame Allowed

- Separate Interrupts for Frames and Buffers (Receive and Transmit)

- Four Address Comparison Registers with Mask

- Maintenance of Five 16-Bit Error Counters

- Flag/Abort/Idle Generation/Detection

- Zero Insertion/Deletion

- NRZ/NRZI Data Encoding

- 16-Bit or 32-Bit CRC-CCITT Generation/Checking

##

If this bit is cleared, the BISYNC controller will look for the SYN1–SYN2 sequence in the data synchronization register.

### NTSYN—No Transmit SYNC

When this bit is set, the SCC operates in a promiscuous, totally transparent mode. See 4.5.16 Transparent Controller for details.

#### **REVD**—Reverse DATA

When this bit is set, the receiver and transmitter will reverse the character bit order, transmitting the most significant bit first. This bit is valid in promiscuous mode.

### BCS—Block Check Sequence

0 = LRC

For even LRC, the PRCRC and PTCRC preset registers in the BISYNC-specific parameter RAM should be initialized to zero before the channel is enabled. For odd LRC, the PRCRC and PTCRC registers should be initialized to ones. The LRC is formed by the Exclusive OR of each 7-bits of data (not including synchronization characters), and the parity bit is added after the final LRC calculation.

The receiver will check character parity when BCS is programmed to LRC and the receiver is not in transparent mode. The transmitter will transmit character parity when BCS is programmed to LRC and the transmitter is not in transparent mode. Use of parity in BISYNC assumes the use of 7-bit data characters.

### 1 = CRC16

The PRCRC and PTCRC preset registers should be initialized to a preset value of all zeros or all ones before the channel is enabled. In both cases, the transmitter sends the calculated CRC non-inverted, and the receiver checks the CRC against zero. Eight-bit characters (without parity) are configured when CRC16 is chosen. The CRC16 polynomial is as follows:

$$\chi^{16} + \chi^{15} + \chi^2 + 1$$

Bit 10—Reserved for future use.

### RTR—Receiver Transparent Mode

- 0 = The receiver is placed in normal mode with SYNC stripping and control character recognition operative.

- 1 = The receiver is placed in transparent mode. SYNCs, DLEs, and control characters are only recognized after a leading DLE character. The receiver will calculate the CRC16 sequence, even if programmed to LRC while in transparent mode. PRCRC should be first initialized to the CRC16 preset value before setting this bit.

### RBCS—Receive Block Check Sequence

The BISYNC receiver internally stores two BCS calculations with a byte delay (eight serial clocks) between them. This enables the user to examine a received data byte and then decide whether or not it should be part of the BCS calculation. This is useful when control

triggers. TCLK2 acts as the SCC2 baud rate generator output if SCC2 is in one of the multiplexed modes.

- RXD2/PA0

- TXD2/PA1

- RCLK2/PA2

- TCLK2/PA3

- <u>CTS2</u>/PA4

- RTS2/PA5

- <u>CD2</u>/PA6

- SDS2/PA7/BRG2

| Table 5-5. Badd Kale Generator Outputs |      |       |       |       |  |  |  |  |  |  |

|----------------------------------------|------|-------|-------|-------|--|--|--|--|--|--|

| Source                                 | NMSI | GCI   | IDL   | РСМ   |  |  |  |  |  |  |

| SCC1                                   | BRG1 | BRG1  | BRG1  | BRG1  |  |  |  |  |  |  |

| SCC2                                   | BRG2 | TCLK2 | TCLK2 | TCLK2 |  |  |  |  |  |  |

| SCC3                                   | BRG3 | TCLK3 | TCLK3 | TCLK3 |  |  |  |  |  |  |

### Table 5-9. Baud Rate Generator Outputs

NOTE: In NMSI mode, the baud rate generator outputs can also appear on the RCLK and TCLK pins as programmed in the SCON register.

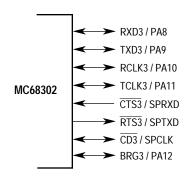

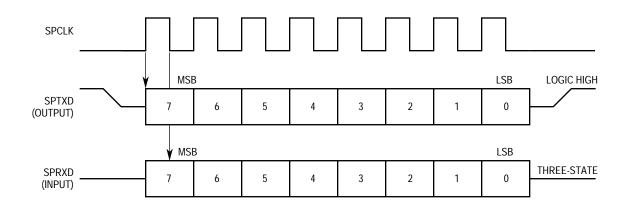

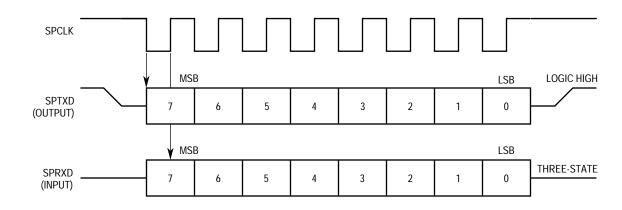

### 5.15 NMSI3 PORT OR PORT A PINS OR SCP PINS

The NMSI3 port or port A pins or SCP pins are shown in Figure 5-12.

Figure 5-12. NMSI3 Port or Port A Pins or SCP Pins

These eight pins can be used either as the NMSI3 port or as the NMSI3 port (less three modem lines) and the SCP port. If the SCP is enabled (EN bit in SPMODE register is set), then the three lines are connected to the SCP port. Otherwise, they are connected to the SCC3 port.

Each of the port A I/O pins can be configured individually to be general-purpose I/O pins or a dedicated function in NMSI3. When they are used as the NMSI3 pins, they function exactly

| MC68302 USER'S MANUAL<br>For More Information On This Product, |

|----------------------------------------------------------------|

| Go to: www.freescale.com                                       |

as the NMSI1 pins (see the previous description). The input buffers have Schmitt triggers. TCLK3 acts as the SCC3 baud rate generator output if SCC3 is in one of the multiplexed modes.

- RXD3/PA8

- TXD3/PA9

- RCLK3/PA10

- TCLK3/PA11

SPRXD/CTS3—SCP Receive Serial Data/NMSI3 Clear-to-Send Pin

This signal functions as the SCP receive data input or may be used as the NMSI3 CTS input pin.

SPTXD/RTS3—SCP Transmit Serial Data/NMSI3 Request-to-Send Pin

This output is the SCP transmit data output or may be used as the NMSI3 RTS pin.

### SPCLK/CD3—SCP Clock/NMSI3 CD Pin

This bidirectional signal is used as the SCP clock output or the NMSI3 CD3 input pin.

### PA12/BRG3

This pin functions as bit 12 of port A or may be used as the SCC3 baud rate generator output clock when SCC3 is operating in NMSI mode.

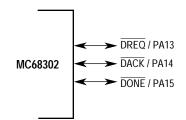

### 5.16 IDMA OR PORT A PINS

The IDMA or port A pins are shown in Figure 5-13.

Each of these three pins can be used either as dedicated pins for the IDMA signals or as general-purpose parallel I/O port A pins. Note that even if one or more of the IDMA pins are used as general-purpose I/O pins, the IDMA can still be used. For example, if DONE is not needed by the IDMA, it can be configured as a general-purpose I/O pin. If the IDMA is used for memory-to-memory transfers only, then all three pins can be used as general-purpose I/O pins. The input buffer of DACK has a Schmitt trigger.

### 6.6 DC ELECTRICAL CHARACTERISTICS—NMSI1 IN IDL MODE

| Characteristic                                       | Symbol          | Min                   | Max                   | Unit | Condition                         |  |  |  |  |  |

|------------------------------------------------------|-----------------|-----------------------|-----------------------|------|-----------------------------------|--|--|--|--|--|

| Input Pin Characteristics: L1CLK, L1SY1, L1RXD, L1GR |                 |                       |                       |      |                                   |  |  |  |  |  |

| Input Low Level Voltage                              | V <sub>IL</sub> | -10%                  | + 20%                 | V    | (% of V <sub>DD</sub> )           |  |  |  |  |  |

| Input High Level Voltage                             | V <sub>IH</sub> | V <sub>DD</sub> - 20% | V <sub>DD</sub> + 10% | V    |                                   |  |  |  |  |  |

| Input Low Level Current                              | IIL             | _                     | ± 10                  | μΑ   | V <sub>in</sub> = V <sub>ss</sub> |  |  |  |  |  |

| Input High Level Current                             | II <sub>H</sub> | _                     | ± 10                  | μΑ   | $V_{in} = V_{DD}$                 |  |  |  |  |  |

| Output Pin Characteristics: L1TXD, SDS1- SDS2, L1RQ  |                 |                       |                       |      |                                   |  |  |  |  |  |

| Output Low Level Voltage                             | V <sub>OL</sub> | 0                     | 1.0                   | V    | I <sub>OL</sub> = 5.0 mA          |  |  |  |  |  |

| Output High Level Voltage                            | V <sub>OH</sub> | V <sub>DD</sub> - 1.0 | V <sub>DD</sub>       | V    | I <sub>OH</sub> = 400 μA          |  |  |  |  |  |

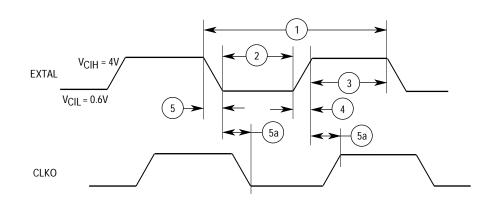

### 6.7 AC ELECTRICAL SPECIFICATIONS—CLOCK TIMING

|      |                                         | Symbol                            | 16.67 | ′ MHz | 20 MHz |      | 25 MHz |      |      |  |

|------|-----------------------------------------|-----------------------------------|-------|-------|--------|------|--------|------|------|--|

| Num. | Characteristic                          |                                   | Min   | Max   | Min    | Max  | Min    | Max  | Unit |  |

|      | Frequency of Operation                  | f                                 | 8     | 16.67 | 8      | 20   | 8      | 25   | MHz  |  |

| 1    | Clock Period (EXTAL) (See note 3)       | t <sub>cyc</sub>                  | 60    | 125   | 50     | 125  | 40     | 125  | ns   |  |

| 2, 3 | Clock Pulse Width (EXTAL)               | t <sub>CL</sub> , t <sub>CH</sub> | 25    | 62.5  | 21     | 62.5 | 16     | 62.5 | ns   |  |

| 4, 5 | Clock Rise and Fall Times (EXTAL)       | t <sub>Cr</sub> , t <sub>Cf</sub> |       | 5     |        | 4    | _      | 4    | ns   |  |

| 5a   | EXTAL to CLKO Delay (See Notes 1 and 2) | t <sub>CD</sub>                   | 2     | 11    | 2      | 9    | 2      | 7    | ns   |  |

(see Figure 6-1, Figure 6-2, Figure 6-3, and Figure 6-4)

NOTE:

1. CLKO loading is 50 pF max.

2. CLKO skew from the rising and falling edges of EXTAL will not differ from each other by more than 1 ns, if the EXTAL rise time equals the EXTAL fall time.

3. You may not stop the clock input at any time.

Figure 6-1. Clock Timing Diagram

Figure 6-9. External Master Internal Asynchronous Write Cycle Timing Diagram

MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

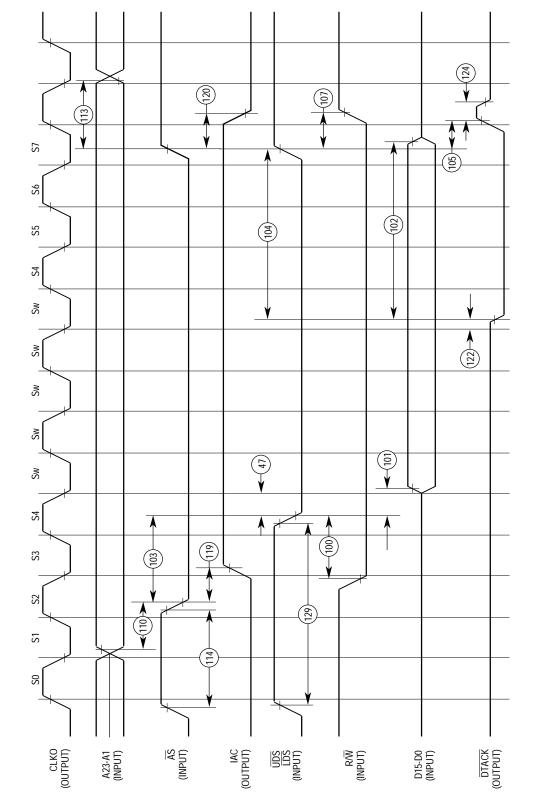

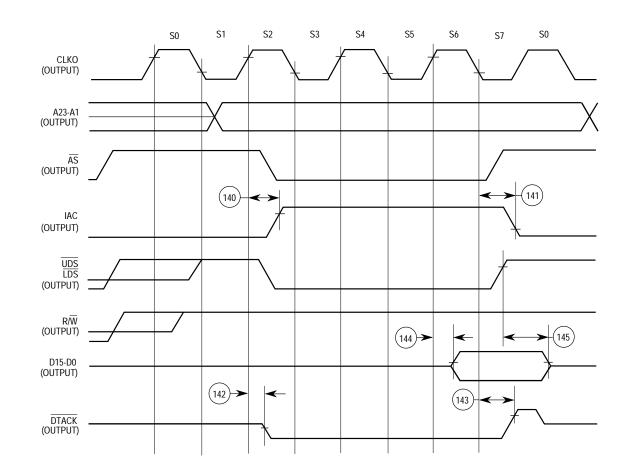

### 6.12 AC ELECTRICAL SPECIFICATIONS—INTERNAL MASTER INTERNAL READ/WRITE CYCLES (see Figure 6-13)

|      |                               |                     | 16.67 MHz |     | 20 MHz |     | 25 MHz |     |      |  |

|------|-------------------------------|---------------------|-----------|-----|--------|-----|--------|-----|------|--|

| Num. | Characteristic                | Symbol              | Min       | Max | Min    | Max | Min    | Max | Unit |  |

| 140  | Clock High to IAC High        | t <sub>CHIAH</sub>  | _         | 40  | _      | 35  | _      | 27  | ns   |  |

| 141  | Clock Low to IAC Low          | t <sub>CLIAL</sub>  |           | 40  |        | 35  |        | 27  | ns   |  |

| 142  | Clock High to DTACK Low       | t <sub>CHDTL</sub>  | _         | 45  | _      | 40  | _      | 30  | ns   |  |

| 143  | Clock Low to DTACK High       | t <sub>CLDTH</sub>  | _         | 40  | _      | 35  | —      | 27  | ns   |  |

| 144  | Clock High to Data-Out Valid  | t <sub>CHDOV</sub>  | _         | 30  | —      | 25  | _      | 20  | ns   |  |

| 145  | AS High to Data-Out Hold Time | t <sub>ASHDOH</sub> | 0         |     | 0      |     | 0      | _   | ns   |  |

Figure 6-13. Internal Master Internal Read/Write Cycle Timing Diagram

NOTE: Transmitted data bits shift on rising edges; received bits are sampled on falling edges.

(a) CI = 0

NOTE: Transmitted data bits shift on falling edges; received bits are sampled on rising edges.

(b) CI = 1

### Figure D-31. SCP Timing

### D.9 AN APPLETALK<sup>®</sup> NODE WITH THE MC68302 AND MC68195

The following paragraphs describe a hardware design that uses the MC68195 LocalTalk Adaptor (LA) to interface the MC68302 to AppleTalk. The LA is designed to work directly with the MC68302 for this purpose. The design is also suitable to those wishing to build a proprietary HDLC-based LAN.

The design as shown works with a set of LocalTalk chip drivers, that allow frames to be sent and received on the network. If these drivers are to be used, the interface between the LA and the MC68302 must be identical to that shown in Figure D-32.

# C Programming Reference Freescale Semiconductor, Inc.

- **OPCODE**—Command Opcode

- 00 = STOP TRANSMIT Command.

- 01 = RESTART TRANSMIT Command.

- 10 = ENTER HUNT MODE Command.

- 11 = Reset receiver BCS generator (used only in BISYNC mode).

BIT 3—Reserved (should be set to zero by the user when the command register is written)

CH. NUM.—Channel Number

- 00 = SCC1.

- 01 = SCC2.

- 10 = SCC3.

- 11 = Reserved.

FLG—Command Semaphore Flag (set by the user and cleared by the CP upon command completion)

- 0 = CP is ready to receive a new command (should be checked before issuing the next command to the CP)

- 1= Command register contains a command to be executed or one that is currently being executed.

**E.1.1.2 Serial Interface Mode Register (SIMODE).** This 16-bit register is located at offset \$8B4. The SIMODE register is used to configure the serial interface mode for the three SCCs.

| 15   | 14        | 13     | 12     | 11   | 10   | 9    | 8    |

|------|-----------|--------|--------|------|------|------|------|

| SETZ | SYNC/SCIT | SDIAG1 | SDIAG0 | SDC2 | SDC1 | B2RB | B2RA |

|      |           |        |        |      |      |      |      |

| 7    | 6    | 5   | 4   | 3    | 2    | 1   | 0   |

|------|------|-----|-----|------|------|-----|-----|

| B1RB | B1RA | DRB | DRA | MSC3 | MSC2 | MS1 | MS0 |

SETZ—Set L1 TXD to Zero (valid only for the GCI interface)

0 = Normal operation.

1 = L1 TXD output set to a logic zero (used in GCI activation).

SYNC/SCIT—SYNC Mode/SCIT Select Support

- 0 = One pulse wide prior to the 8-bit data.

- 1 = N pulses wide and envelopes the N-bit data.

### SDIAG1, SDIAG0—Serial Interface Diagnostic Mode

- 00 = Normal operation.

- 01 = Automatic echo.

- 10 = Internal loopback.

- 11 = Loopback control.

# C Programming Reference Freescale Semiconductor, Inc.

- CR-Rx CRC Error

- 0 = This frame does not contain a CRC error.

- 1 = This frame contains a CRC error.

### OV—Overrun

- 0 = No receiver overrun occurred.

- 1 = A receiver overrun condition occurred during frame reception.

CD-Carrier Detect Lost (valid only in NMSI mode)

- 0 = No CD lost was detected.

- 1 = CD was negated during frame reception.

**E.1.1.4.2 Receive Buffer Data Length.** This 16-bit value is written by the IMP to indicate the number of data bytes received into the data buffer.

**E.1.1.4.3 Receive Buffer Pointer.** This 32-bit value is written by the user to indicate the address where the data is to be stored.

**E.1.1.5 TRANSMIT BUFFER DESCRIPTORS.** Each SCC has eight transmit buffer descriptors. Each buffer descriptor consists of four words as shown below. Reserved bits in registers should be written as zeros.

**E.1.1.5.1 Transmit BD Control/Status Word.** To initialize the buffer, the user should write bits 15-10 and bits 1-0. The IMP clears bit 15 when the buffer is transmitted or closed due to an error and sets bits 1-0 depending on which error occurred.

### R—Ready

- 0 = This data buffer is not currently ready for transmission.

- 1 = This data buffer has been prepared by the user for transmission but has not yet been fully transmitted. Must be set by the user to enable transmission of the buffer.

### X—External Buffer

- 0 = The data buffer associated with this BD is in internal dual-port RAM.

- 1 = The data buffer associated with this BD is in external memory.

### W-Wrap (final BD in table)

- 0 = This is not the last BD in the transmit BD table.

- 1 = This is the last BD in the transmit BD table.

**E.3.1.2 PER SCC REGISTERS.** Each of the three SCCs has a set of the following six registers. These registers configure the SCC and the protocol operation. Some parameters and register bits are protocol independent. The transparent functions have been given for those parameters and bits that are protocol specific.

**E.3.1.2.1 Serial Configuration Register (SCON).** This 16-bit register is located at offset \$882 (SCC1), \$892 (SCC2), and \$8A2 (SCC3). The SCON register is used to select the clock source and baud rate for the SCC.

| 15   | 14   | 13  | 12  | 11   | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0    |

|------|------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| WOMS | EXTC | TCS | RCS | CD10 | CD9 | CD8 | CD7 | CD6 | CD5 | CD4 | CD3 | CD2 | CD1 | CD0 | DIV4 |

WOMS—Wired-OR Mode Select

- 0 = TXD driver operates normally.

- 1 = TXD driver functions as an open-drain output and may be wired together with other TXD pins.

EXTC—External Clock Source

- 0 = The internal main clock is the source of the baud rate generator.

- 1 = The external clock on the TIN1 pin is the source for the baud rate generator.

TCS—Transmit Clock Source

- 0 = Transmit clock source is the baud rate generator output.

- 1 = Transmit clock source is the clock signal on TCLK pin.

RCS—Receive Clock Source

- 0 = Receive clock source is the baud rate generator output.

- 1 = Receive clock source is the clock signal on TCLK pin.

CD1 0-CD0—Clock Divider

Used to preset the 11-bit counter that is decremented at the prescaler output rate.

DIV4—SCC Clock Prescaler Divide by 4

- 0 = Divide-by-1 prescaler.

- 1 = Divide-by-4 prescaler.

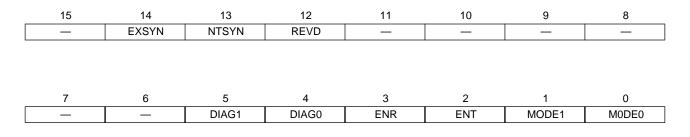

**E.3.1.2.2 SCC Mode Register (SCM).** This 16-bit register is located at offset \$884 (SCC1), \$894 (SCC2), and \$8A4 (SCC3) The SCM register configures the operation of the SCC and defines transparent-specific parameters. Note that reserved bits in registers should be written as zeros.

### E—Empty

- 0 = This data buffer is full or has been closed due to an error condition.

- 1 = This data buffer is empty; must be set by the user to enable reception into this buffer.

- X—External Buffer

- 0 = The data buffer associated with this BD is in internal dual-port RAM.

- 1 = The data buffer associated with this BD is in external memory.

- W-Wrap (final BD in table)

- 0 = This is not the last BD in the receive BD table.

- 1 = This is the last BD in the receive BD table.

- I-Interrupt

- 0 = No interrupt is generated when this buffer is closed.

- 1 = The RX bit in the event register is set when this buffer is closed.

Bits 11-2—Reserved for future use; should be written with zero by the user.

### OV-Overrun

- 0 = No receiver overrun occurred.

- 1 = A receiver overrun condition occurred during frame reception.

CD-Carrier Detect Lost (valid only in NMSI mode)

- 0 = No CD lost was detected.

- 1 = CD was negated during frame reception.

**E.3.1.4.2 Receive Buffer Data Length.** This 16-bit value is written by the IMP to indicate the number of data bytes received into the data buffer.

**E.3.1.4.3 Receive Buffer Pointer.** This 32 bit value is written by the user to indicate the address where the data is to be stored.

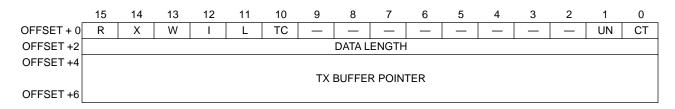

**E.3.1.5 TRANSMIT BUFFER DESCRIPTORS.** Each SCC has eight transmit buffer descriptors. Each buffer descriptor consists of four words as shown below. Reserved bits in registers should be written as zeros.

|            | 15                | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0  |

|------------|-------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|----|----|

| OFFSET + 0 | R                 | Х  | W  | Ι  | L  | —  | — | — | — | _ | — | _ | _ | _ | UN | СТ |

| OFFSET +2  | DATA LENGTH       |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

| OFFSET +4  |                   |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

|            | TX BUFFER POINTER |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

| OFFSET +6  |                   |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

**E.3.1.5.1 Transmit BD Control/Status Word.** To initialize the buffer, the user should write bits 15-11 and clear bits 1-0. The IMP clears bit 15 when the buffer is transmitted or closed due to an error and sets bits 1-0 depending on which error occurred.

does not correctly "equate" locations in parameter RAM to intended addresses. A simple typo in an assembler EQU or a C #DEFINE directive can cause 1) the intended parameter not to be set and 2) another parameter to be set to a wrong value.

### 17. Function Code, Initialize, Reset

To use IDMA, SDMA, and/or DRAM refresh, their corresponding function code registers MUST be initialized. Setting the function codes in these registers to "111" will prevent the MC68302 chip selects from asserting. Failure to initialize these registers often results in their function codes having the value "111", since these registers are in dualport RAM and do not have predefined values upon a total system reset.

### 18. Function Code, External Bus Master

When an external bus master is using the chip selects on the MC68302 with the external master's external memory accesses, make sure that the external bus master drives the function code lines to something other than "111". If the function code lines are driven or left floating to "111", the external cycle will be interpreted by the MC68302 as an interrupt acknowledge cycle, and the chip selects will not be asserted during the cycle.

### 19. BAR, Write

The BAR MUST BE written by an instruction following a total system reset of the MC68302 since this register resides in the MC68302, not in the memory. It is not sufficient or required for the EPROM on the target board to have the desired BAR value stored in the EPROM location \$0F2 (the address of BAR). When using an emulator, a symptom of this problem can be that the code works in the emulator overlay memory, but not on the target.

### 20. DRAM Refresh

When using the DRAM refresh unit, one cannot refresh locations \$0F0–0FF of an external DRAM if an MC68302 chip select is used to select that DRAM. Locations \$0F0– 0FF are designated as the reserved area of the IMP that contains the BAR and SCR, and chip selects will not activate on accesses to these addresses. The remedy is simply to use a different DRAM refresh starting address besides \$0. Also note that the DRAM refresh access is a byte read, not a word read.

### 21. Watchdog Timer

If the MC68302 watchdog timer is never turned off or refreshed, an unexpected interrupt at level 4 can occur. Also, an unexpected RESET can occur if the WDOG pin is externally connected to HALT and RESET. The solution is to disable the watchdog timer after reset. Note that the watchdog timer is not related to the hardware watchdog, which is a completely separate unit that monitors bus activity.

### 22. Underrun, Overrun, Clock Lines, Schmitt-Triggers

If a transmit underrun or a receive overrun is reported but the data rates are too slow to suggest an actual underrun or overrun, the problem may be in the clock lines. Glitched or badly ringing clocks (on the TCLK or RCLK pins) can cause SCCs to enter either of the above error states. Even though Schmitt-triggers are implemented on the IMP clocks lines, a very slow rise/fall time coupled with a large amount of noise on the lines can override the hysteresis protection and affect the ability of the SCC to correctly sample and clock data. Internal clocks generated by the IMP do not cause this problem.