#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFl

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | M68000                                                      |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                            |

| Speed                           | 16MHz                                                       |

| Co-Processors/DSP               | Communications; RISC CPM                                    |

| RAM Controllers                 | DRAM                                                        |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | ·                                                           |

| Ethernet                        | · .                                                         |

| SATA                            | · .                                                         |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | -40°C ~ 85°C (TA)                                           |

| Security Features               | -                                                           |

| Package / Case                  | 144-LQFP                                                    |

| Supplier Device Package         | 144-LQFP (20x20)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68302cag16vc |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Paragraph<br>Number | Title Pag<br>Numbe                                 |  |

|---------------------|----------------------------------------------------|--|

| 5.6                 | Data Bus Pins (D15—D0)5-7                          |  |

| 5.7                 | Bus Control Pins                                   |  |

| 5.8                 | Bus Arbitration Pins                               |  |

| 5.9                 | Interrupt Control Pins 5-11                        |  |

| 5.10                | MC68302 Bus Interface Signal Summary 5-12          |  |

| 5.11                | Physical Layer Serial Interface Pins               |  |

| 5.12                | Typical Serial Interface Pin Configurations        |  |

| 5.13                | NMSI1 or ISDN Interface Pins                       |  |

| 5.14                | NMSI2 Port or Port a Pins5-17                      |  |

| 5.15                | NMSI3 Port or Port A Pins or SCP Pins              |  |

| 5.16                | IDMA or Port A Pins                                |  |

| 5.17                | IACK or PIO Port B Pins                            |  |

| 5.18                | Timer Pins                                         |  |

| 5.19                | Parallel I/O Pins with Interrupt Capability        |  |

| 5.20                | Chip-Select Pins                                   |  |

| 5.21                | No-Connect Pins                                    |  |

| 5.22                | When to Use Pullup Resistors5-23                   |  |

|                     | Section 6                                          |  |

|                     | Electrical Characteristics                         |  |

| 6.1                 | Maximum Ratings6-1                                 |  |

| 6.2                 | Thermal Characteristics                            |  |

| 6.3                 | Power Considerations                               |  |

| 6.4                 | Power Dissipation6-3                               |  |

| 6.5                 | DC Electrical Characteristics                      |  |

| 6.6                 | DC Electrical Characteristics—NMSI1 in IDL Mode6-5 |  |

| 6.7                 | AC Electrical Specifications—Clock Timing          |  |

| 6.8                 | AC Electrical Specifications—IMP Bus Master Cycles |  |

| 6.9                 | AC Electrical Specifications—DMA6-13               |  |

| 6.10                | AC Electrical Specifications—External Master       |  |

| 6.1  | Maximum Ratings6-1                                                   |

|------|----------------------------------------------------------------------|

| 6.2  | Thermal Characteristics6-1                                           |

| 6.3  | Power Considerations                                                 |

| 6.4  | Power Dissipation6-3                                                 |

| 6.5  | DC Electrical Characteristics                                        |

| 6.6  | DC Electrical Characteristics—NMSI1 in IDL Mode                      |

| 6.7  | AC Electrical Specifications—Clock Timing                            |

| 6.8  | AC Electrical Specifications—IMP Bus Master Cycles                   |

| 6.9  | AC Electrical Specifications—DMA                                     |

| 6.10 | AC Electrical Specifications—External Master                         |

|      | Internal Asynchronous Read/Write Cycles                              |

| 6.11 | AC Electrical Specifications—External Master Internal Synchronous    |

|      | Read/Write Cycles                                                    |

| 6.12 | AC Electrical Specifications—Internal Master                         |

|      | Internal Read/Write Cycles                                           |

| 6.13 | AC Electrical Specifications—Chip-Select Timing Internal             |

|      | Master                                                               |

| 6.14 | AC Electrical Specifications—Chip-Select Timing External Master 6-25 |

| 6.15 | AC Electrical Specifications—Parallel I/O                            |

| 6.16 | AC Electrical Specifications—Interrupts                              |

| 6.17 | AC Electrical Specifications—Timers                                  |

| 6.18 | AC Electrical Specifications—Serial Communications Port              |

| 6.19 | AC Electrical Specifications—IDL Timing                              |

| 6.20 | AC Electrical Specifications—GCI Timing                              |

| 6.21 | AC Electrical Specifications—PCM Timing                              |

| 6.22 | AC Electrical Specifications—NMSI Timing                             |

| Mnemonic | Description                        |

|----------|------------------------------------|

| ABCD     | Add Decimal with Extend            |

| ADD      | Add                                |

| AND      | Logical AND                        |

| ASL      | Arithmetic Shift Left              |

| ASR      | Arithmetic Shift Right             |

| Bcc      | Branch Conditionally               |

| BCHG     | Bit Test and Change                |

| BCLR     | Bit Test and Clear                 |

| BRA      | Branch Always                      |

| BSET     | Bit Test and Set                   |

| BSR      | Branch to Subroutine               |

| BTST     | Bit Test                           |

| CHK      | Check Register Against Bounds      |

| CLR      | Clear Operand                      |

| CMP      | Compare                            |

| DBcc     | Decrement and Branch Conditionally |

| DIVS     | Signed Divide                      |

| DIVU     | Unsigned Divide                    |

| EOR      | Exclusive OR                       |

| EXG      | Exchange Registers                 |

| EXT      | Sign Extend                        |

| JMP      | Jump                               |

| JSR      | Jump to Subroutine                 |

| LEA      | Load Effective Address             |

| LINK     | Link Stack                         |

| LSL      | Logical Shift Left                 |

| LSR      | Logical Shift Right                |

| Mnemonic | Description                  |

|----------|------------------------------|

| MOVE     | Move Source to Destination   |

| MULS     | Signed Multiply              |

| MULU     | Unsigned Multiply            |

| NBCD     | Negate Decimal with Extend   |

| NEG      | Negate                       |

| NOP      | No Operation                 |

| NOT      | Ones Complement              |

| OR       | Logical OR                   |

| PEA      | Push Effective Address       |

| RESET    | Reset External Devices       |

| ROL      | Rotate Left without Extend   |

| ROR      | Rotate Right without Extend  |

| ROXL     | Rotate Left with Extend      |

| ROXR     | Rotate Right with Extend     |

| RTE      | Return from Exception        |

| RTR      | Return and Restore           |

| RTS      | Return from Subroutine       |

| SBCD     | Subtract Decimal with Extend |

| Scc      | Set Conditionally            |

| STOP     | Stop                         |

| SUB      | Subtract                     |

| SWAP     | Swap Data Register Halves    |

| TAS      | Test and Set Operand         |

| TRAP     | Trap                         |

| TRAPV    | Trap on Overflow             |

| TST      | Test                         |

| UNLK     | Unlink                       |

CFC—Compare Function Code

- 0 = The FC bits in the BAR are ignored. Accesses to the IMP 4K-byte block occur without comparing the FC bits.

- 1 = The FC bits in the BAR are compared. The address space compare logic uses the FC bits to detect address matches.

#### Bits 11–0—Base Address

The high address field is contained in bit 11–0 of the BAR. These bits are used to set the starting address of the dual-port RAM. The address compare logic uses only the most significant bits to cause an address match within its block size.

## 2.8 MC68302 MEMORY MAP

The following tables show the additional registers added to the M68000 to make up the MC68302. All of the registers are memory-mapped. Four entries in the M68000 exception vectors table (located in low RAM) are reserved for addresses of system configuration registers (see Table 2-6) that reside on-chip. These registers have fixed addresses of \$0F0–\$0FF. All other on-chip peripherals occupy a 4K-byte relocatable address space. When an on-chip register or peripheral is accessed, the internal access (IAC) pin is asserted.

| Address | Name | Width | Description             | Reset Value |

|---------|------|-------|-------------------------|-------------|

| \$0F0   | RES  | 16    | Reserved                |             |

| \$0F2*  | BAR  | 16    | Base Address Register   | BFFF        |

| \$0F4*  | SCR  | 32    | System Control Register | 0000 0F00   |

| \$0F8   | RES  | 16    | Reserved                |             |

| \$0FA   | CKCR | 16    | Clock Control Register  | 0000        |

| \$0FC   | RES  | 32    | Reserved                |             |

Table 2-6. System Configuration Register

\*Reset only upon a total system reset.

The internal 1176-byte dual-port RAM has 576 bytes of system RAM (see Table 2-7) and 576 bytes of parameter RAM (see Table 2-8).

Table 2-7. System RAM

| Address    | Width     | Block | Description       |

|------------|-----------|-------|-------------------|

| Base + 000 |           |       |                   |

| •          |           |       |                   |

| •          | 576 Bytes | RAM   | User Data Memory  |

| •          |           |       |                   |

| Base + 23F |           |       |                   |

| Base +240  |           |       |                   |

| •          |           |       | Reserved          |

| •          |           |       |                   |

| •          |           |       | (Not Implemented) |

| Base + 3FF |           |       |                   |

The parameter RAM contains the buffer descriptors for each of the three SCC channels, the SCP, and the two SMC channels. The memory structures of the three SCC channels are

# stem Integration Block (SIB)

Option 2. The external peripheral can generate the vector. In this case the external device must decode the interrupt acknowledge cycle, put out the 8-bit vector, and generate DTACK. The decoding of the interrupt acknowledge cycle can be provided by the IACK7, IACK6, and IACK1 signals (enabled in the PBCNT register) if either normal or dedicated mode is chosen. These signals eliminate the need for external logic to perform the decoding of the A19–A16, A3–A1, and FC2–FC0 pins externally to detect the interrupt acknowledge cycle. If the IACK signals are not needed, they can be regained as general purpose parallel I/O pins. The external device must generate DTACK in this mode, and DTACK is an input to the IMP.

Option 3. The external peripheral can assert the AVEC pin to cause the M68000 to use an autovector. In this case, DTACK should not be asserted by the external device. AVEC is recognized by the M68000 core on the falling edge of S4 and should meet the asynchronous setup time to the falling edge of S4. The IACK signals can be used to help generate the AVEC signal for priority levels 1, 6, and 7, if needed.

#### NOTE

If AVEC is asserted during an interrupt acknowledge cycle, an autovector is taken, regardless of the vector on the bus. AVEC should not be asserted during level 4 interrupt acknowledge cycles.

When the IMP generates the vector, the following procedure is used. The three most significant bits of the interrupt vector number are programmed by the user in the GIMR. These three bits are concatenated with five bits generated by the interrupt controller to provide an 8-bit vector number to the core. The interrupt controller's encoding of the five low-order bits of the interrupt vector is shown in Table 3-5. An example vector calculation is shown in Figure 3-4. When the core initiates an interrupt acknowledge cycle for level 4 and there is no internal interrupt pending, the interrupt controller encodes the error code 00000 onto the five low-order bits of the interrupt vector.

- 2. BG will be an input to the IDMA and SDMA from the external M68000 bus, rather than being an output from the MC68302. When BG is sampled as low by the MC68302, it waits for AS, BERR, HALT, and BGACK to be negated, and then asserts BGACK and performs one or more bus cycles. See Section 6 for timing diagrams.

- 3. BCLR will be an input to the IDMA, but will remain an output from the SDMA.

- 4. The interrupt controller will output its interrupt request lines (IPL0, IPL1, IPL2) normally sent to the M68000 core on pins IOUT0, IOUT1, and IOUT2, respectively. AVEC, RMC, and CS0, which share pins with IOUT0, IOUT1, and IOUT2, respectively, are not available in this mode.

DISCPU should remain continuously high during disable CPU mode operation. Although the  $\overline{CS0}$  pin is not available as an output from the device in disable CPU mode, it may be enabled to provide  $\overline{DTACK}$  generation. In disable CPU mode, BR0 is initially \$C000.

Accesses by an external master to the MC68302 RAM and registers may be asynchronous or synchronous to the MC68302 clock. (This feature is actually available regardless of disable CPU mode). See the SAM and EMWS bits in the SCR for details.

In disable CPU mode, the interrupt controller may be programmed to generate or not generate interrupt vectors during interrupt acknowledge cycles. When multiple MC68302 devices share a single M68000 bus, vector generation at level 4 should be prevented on all but one MC68302. When using disable CPU mode to implement an interface, such as between the MC68020 and a single MC68302, vector generation can be enabled. For this purpose, the VGE bit is defined.

VGE—Vector Generation Enable

- 0 = In disable CPU mode, the MC68302 will not output interrupt vectors during interrupt acknowledge cycles.

- 1 = In disable CPU mode, the MC68302 will output interrupt vectors for internal level 4 interrupts (and for levels 1, 6, and/or 7 as enabled in the interrupt controller) during interrupt acknowledge cycles.

## NOTE

Do not use the function code value "111" during external accesses to the IMP, except during interrupt acknowledge cycles.

In disable CPU mode, the low-power modes will be entered immediately upon the setting of the LPEN bit in the SCR by an external master. In this case, low-power mode will continue until the LPEN bit is cleared. Users may wish to use a low-power mode in conjunction with disable CPU mode to save power consumed by the disabled M68000 core.

All MC68302 functionality not expressly mentioned in this section is retained in disable CPU mode and operates identically as before.

## NOTE

Even without the use of the disable CPU logic, another processor can be granted access to the IMP on-chip peripherals by re-

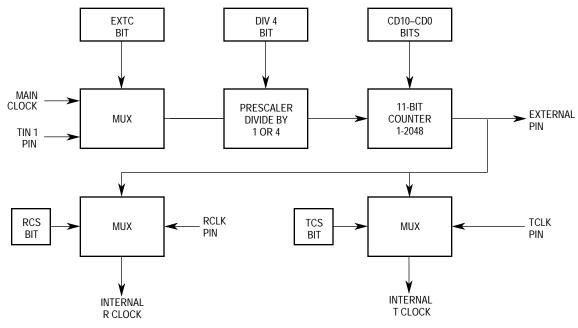

#### CD10-CD0-Clock Divider

The clock divider bits and the prescaler determine the baud rate generator output clock rate. CD10–CD0 are used to preset an 11-bit counter that is decremented at the prescaler output rate. The counter is not otherwise accessible to the user. When the counter reaches zero, it is reloaded with the clock divider bits. Thus, a value of \$7FF in CD10–CD0 produces the minimum clock rate (divide by 2048); a value of \$000 produces the maximum clock rate (divide by 1).

#### NOTE

Because of SCC clocking restrictions, the maximum baud rate that may be used to clock an SCC is divide by 3.

When dividing by an odd number, the counter ensures a 50% duty cycle by asserting the terminal count once on a clock high and next on a clock low. The terminal count signals the counter expiration and toggles the clock.

## DIV4—SCC Clock Prescaler Divide by 4

The SCC clock prescaler bit selects a divide-by-1 (DIV4 = 0) or divide-by-4 (DIV4 = 1) prescaler for the clock divider input. The divide-by-4 option is useful in generating very slow baud rates.

Figure 4-12. SCC Baud Rate Generator

## 4.5.2.1 Asynchronous Baud Rate Generator Examples

The UART circuitry always uses a clock that is 16x the baud rate. The ratio of the 16x UART clock to the system parallel clock must not exceed 1:2.5. For an internally supplied clock, an integer divider value must be used; therefore, the divider must be 3 or greater. Thus, using a clock divider value of 3 (programmed as 2 in the SCON) and a 16.67-MHz crystal gives a UART clock rate of 5.56 MHz and a baud rate of 347 kbaud. Assuming again a 16.67-MHz

|            | 15 0                                                                            | 0 |

|------------|---------------------------------------------------------------------------------|---|

| OFFSET + 0 | STATUS AND CONTROL                                                              | Т |

| OFFSET + 2 | DATA LENGTH                                                                     |   |

| OFFSET + 4 | HIGH-ORDER DATA BUFFER POINTER (only lower 8 bits used, upper 8 bits must be 0) |   |

| OFFSET+6   | LOW-ORDER DATA BUFFER POINTER                                                   |   |

#### Figure 4-16. SCC Buffer Descriptor Format

For frame-oriented protocols (HDLC, BISYNC, DDCMP, V.110), a frame may reside in as many buffers as are necessary (transmit or receive). Each buffer has a maximum length of 64K–1 bytes. The CP does not assume that all buffers of a single frame are currently linked to the BD table, but does assume that the unlinked buffers will be provided by the processor in time to be either transmitted or received. Failure to do so will result in a TXE error being reported by the CP.

For example, assume the first six buffers of the transmit BD table have been transmitted and await processing by the M68000 core (with all eight buffers used in the circular queue), and a three-buffer frame awaits transmission. The first two buffers may be linked to the remaining two entries in the table as long as the user links the final buffer into the first entry in the BD table before the IMP attempts its transmission. If the final buffer is not linked in time to the BD table by the time the CP attempts its transmission, the CP will report an underrun error.

Buffers allocated to an SCC channel may be located in either internal or external memory. Memory allocation occurs for each BD individually. If internal memory is selected, the CP uses only the lower 11 address bits (A10–A0) as an offset to the internal dual-port RAM. Accesses to the internal memory by the CP are one clock cycle long and occur without arbitration. If external memory is selected, the pointers to the data buffers are used by the CP as 24 bits of address.

Extra caution should be used if function codes are included in the decoding of the external buffer address (e.g., in the on-chip chip select logic). The function code of this SCC channel must be set before external buffers can be accessed; it can then be changed only when the user is sure that the CP is not currently accessing external buffers for that channel. There are six separate function code registers located in the parameter RAM for the three SCC channels: three for receive data buffers (RFCR) and three for transmit data buffers (TFCR).

#### NOTE

The RFCR and TFCR function codes should never be initialized to "111."

The CP processes the transmit BDs in a straightforward fashion. Once the transmit side of an SCC is enabled, it starts with the first BD in that SCC's transmit BD table, periodically checking a bit to see if that BD is "ready". Once it is ready, it will process that BD, reading a word at a time from its associated buffer, doing certain required protocol processing on the data, and moving resultant data to the SCC transmit FIFO. When the first buffer has been processed, the CP moves on to the next BD, again waiting for that BD's "ready" bit to be set. Thus, the CP does no look-ahead BD processing, nor does it skip over BDs that are not ready. When the CP sees the "wrap" bit set in a BD, it goes back to the beginning of the BD

## CR—Rx CRC Error

This frame contains a CRC error.

## **OV**—Overrun

A receiver overrun occurred during frame reception.

## **CD**—Carrier Detect Lost

The carrier detect signal was negated during frame reception. This bit is valid only when working in NMSI mode.

## Data Length

The data length is the number of octets written to this BD's data buffer by the HDLC controller. It is written by the CP once as the BD is closed.

When this BD is the last BD in the frame (L = 1), the data length contains the total number of frame octets (including any previous linked receive data buffers and two or four bytes for the CRC) in the frame. This behavior is useful for determining the total number of octets received, even if MFLR was exceeded.

## NOTE

The actual amount of memory allocated for this buffer should be even and greater than or equal to the contents of maximum receive buffer length register (MRBLR).

## **Rx Buffer Pointer**

The receive buffer pointer, which always points to the first location of the associated data buffer, may reside in either internal or external memory.

## NOTE

The Rx buffer pointer must be even, and the upper 8 bits must of the pointer must be zero for the function codes to operate correctly.

## 4.5.12.11 HDLC Transmit Buffer Descriptor (Tx BD)

Data is presented to the HDLC controller for transmission on an SCC channel by arranging it in buffers referenced by the channel's Tx BD table. The HDLC controller confirms transmission (or indicates error conditions) using the BDs to inform the M68000 core that the buffers have been serviced. The Tx BD is shown in Figure 4-28.

|            | 15                                                                  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0  |

|------------|---------------------------------------------------------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|----|----|

| OFFSET + 0 | R                                                                   | Х  | W  | I  | L  | TC | _ | — | _ | — | _ | — | — | _ | UN | СТ |

| OFFSET + 2 | FSET + 2                                                            |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

| OFFSET + 4 | DATA LENGTHTX BUFFER POINTER (24-bits used, upper 8 bits must be 0) |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

| OFFSET + 6 |                                                                     |    |    |    |    |    |   |   |   |   |   |   |   |   |    |    |

## Figure 4-28. HDLC Transmit Buffer Descriptor

sion of a block. For the receiver, the ENQ character designates the end of the block, but no CRC is expected.

Following control character reception (i.e., end of the block), the RCH bit in the BISYNC mask register should be set, re-enabling interrupts for each byte of received data.

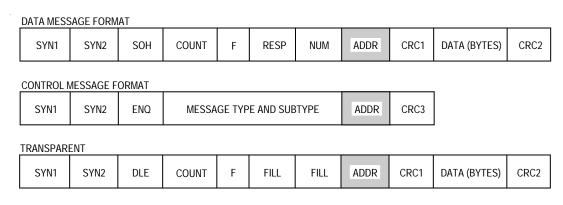

## 4.5.14 DDCMP Controller

The byte-oriented digital data communications message protocol (DDCMP) was originated by DEC for use in networking products. The three classes of DDCMP frames are transparent (or maintenance) messages, data messages, and control messages (see Figure 4-34). Each class of frame starts with a standard two octet synchronization pattern and ends with a CRC. Depending upon the frame type, a separate CRC may be present for the header as well as the data portions of the frame. These CRCs use the same 16-bit generator polynomial as that used in HDLC.

## Figure 4-34. Typical DDCMP Frames

The most notable feature of the DDCMP frame is that the frame length is transmitted within the frame itself. Thus, any character pattern can be transmitted in the data field since the character count is responsible for ending the frame, not a special character. For this to work properly, the header containing the frame length must be protected, causing a need for a CRC in the frame header.

The bulk of the frame is divided into fields whose meaning depends on the frame type. Defined control characters are only used in the fixed-length frame headers (the fields between the synchronization octets and the first CRC). The following fields are one byte each: SYN1, SYN2, SOH, RESP, NUM, ADDR, ENQ, DLE, and FILL. The following fields are two bytes each: COUNT + F, CRC1, CRC2, and CRC3. The DATA field is a variable number of bytes, as defined in the COUNT field.

DDCMP communications can be either synchronous or asynchronous, with both types using the same frame format. Synchronous DDCMP frames require the physical layer to transmit the clock along with data over the link. Asynchronous DDCMP frames are composed of asynchronous UART characters, which together form the frame. The receiver and transmitter clocks are not linked; the receiver resynchronizes itself every byte using the start and stop bits of each UART character.

| Address                                                                                                    | Name                                                  | Width                                        | Description                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCC Base + 9C<br>SCC Base + 9E<br>SCC Base + A0 #<br>SCC Base + A2                                         | RCRC<br>CRCC<br>PCRC<br>TCRC                          | Word<br>Word<br>Word<br>Word                 | Temp Receive CRC<br>CRC16 Constant<br>Preset CRC16<br>Temp Transmit CRC                                                                                 |

| SCC Base + A4 #<br>SCC Base + A5 #<br>SCC Base + A6<br>SCC Base + A7 #<br>SCC Base + A8<br>SCC Base + A9 # | DSYN1<br>DSOH<br>Reserved<br>DENQ<br>Reserved<br>DDLE | Byte<br>Byte<br>Byte<br>Byte<br>Byte<br>Byte | DDCMP SYN1 Character<br>DDCMP SOH Character<br>DDCMP ENQ Character<br>DDCMP DLE Character                                                               |

| SCC Base + AA #<br>SCC Base + AC #<br>SCC Base + AE #<br>SCC Base + B0 #                                   | CC Base + AC # CRC2EC<br>CC Base + AE # NMARC         |                                              | CRC1 Error Counter<br>CRC2 Error Counter<br>Nonmatching Address Received Counter<br>Discard Message Counter                                             |

| SCC Base + B2<br>SCC Base + B4                                                                             | RMLG<br>RMLG_CNT                                      | Word<br>Word                                 | Received Message Length<br>Received Message Length Counter                                                                                              |

| SCC Base + B8 #DADDR1SCC Base + BA #DADDR2SCC Base + BC #DADDR3                                            |                                                       | Word<br>Word<br>Word<br>Word<br>Word         | User-Defined Frame Address Mask<br>User-Defined Frame Address<br>User-Defined Frame Address<br>User-Defined Frame Address<br>User-Defined Frame Address |

#### Table 4-10. DDCMP Specific Parameter RAM

# Initialized by the user (M68000 core).

#### 4.5.14.4 DDCMP Programming Model

The M68000 core configures each SCC to operate in one of four protocols by the MODE1– MODE0 bits in the SCC mode register. If MODE1–MODE0 = 10, DDCMP operation is selected with synchronous links. For asynchronous links, MODE1–MODE0 = 01 (ASYNC) should be selected, and the DDCMP bit in the UART mode register should be set. The SYN1–SYN2 synchronization characters are programmed in the data synchronization register (DSR). See 4.5.4 SCC Data Synchronization Register (DSR) for more programming information. The DDCMP controller uses the same basic data structure as the UART, HDLC, and BISYNC controllers.

The DDCMP controller generates and checks the CRC16 message trailer. It can be preset to ones or zeros by writing to the preset CRC (PCRC) register before enabling the receiver or the transmitter. The received message length (RMLG) is the header byte count value as determined by the receiver, and the received message length counter (RMLG \_ CNT) is the temporary received data downcounter.

Receive and transmit errors are reported in their respective BDs. The line status signals ( $\overline{CD}$  and  $\overline{CTS}$ ) may be read in the SCC status register and a maskable interrupt is generated upon each status change (see 4.5.2 SCC Configuration Register (SCON)).

#### 4.5.14.5 DDCMP Command Set.

The following commands are issued to the command register:

#### STOP TRANSMIT Command

After a hardware or software reset and the enabling of the channel in the SCC mode register, the channel is in the transmit enable mode and starts polling the first BD in the table approximately every eight transmit clocks.

The channel STOP TRANSMIT command disables the transmission of messages on the transmit channel. If this command is received by the DDCMP controller during message

mmunications Processor (CP)

Bit 7—This bit is reserved and should be set to zero.

#### SMD3-SMD0-SMC Mode Support

- X00X = GCI—The monitor channel is not used.

- 001X = GCI—The monitor channel data and the A and E control bits are internally controlled according to the monitor channel protocol.

- 101X = GCI—The monitor channel data and the A and E control bits are received and transmitted transparently by the IMP.

X100 = IDL—The M and A channels are in hunt-on-zero mode.

X101 = IDL—Only the M channel is in hunt-on-zero mode.

X110 = IDL—Only the A channel is in hunt-on-zero mode.

X111 = IDL—Regular operation; no channel is in hunt-on-zero mode.

#### LOOP—Local Loopback Mode

- 0 = Normal mode

- 1 = Local loopback mode. In GCI mode, EN1 and EN2 must also be set.

EN2—SMC2 Enable

- 0 = Disable SMC2

- 1 = Enable SMC2

EN1—SMC1 Enable

- 0 = Disable SMC1

- 1 = Enable SMC1

## 4.7.3 SMC Commands

The following commands issued to the CP command register (see 4.3 Command Set) are used only when GCI is selected for the serial channels physical interface.

## TRANSMIT ABORT REQUEST Command

This receiver command may be issued when the IMP implements the monitor channel protocol. When issued, the IMP sends an abort request on the A bit.

#### TIMEOUT Command

This transmitter command may be issued when the IMP implements the monitor channel protocol. It is issued because the device is not responding or because GCI A bit errors are detected. When issued, the IMP sends an abort request on the E bit.

## 4.7.4 SMC Memory Structure and Buffers Descriptors

The CP uses several memory structures and memory-mapped registers to communicate with the M68000 core. All the structures detailed in the following paragraphs reside in the dual-port RAM of the IMP (see Figure 3-4). The SMC buffer descriptors allow the user to define one data byte at a time for each transmit channel and receive one data byte at a time for each receive channel.

These eight pins can be used either as NMSI1 in nonmultiplexed serial interface (NMSI) mode or as an ISDN physical layer interface in IDL, GCI, and PCM highway modes. The input buffers have Schmitt triggers.

Table 5-7 shows the functionality of each pin in NMSI, GCI, IDL, and PCM highway modes.

| Signal Name | ame NMSI1 |       |   | GCI    |   | IDL    | PCM |       |  |

|-------------|-----------|-------|---|--------|---|--------|-----|-------|--|

| RXD1/L1RXD  | I         | RXD1  | I | L1RXD  | I | L1RXD  | I   | L1RXD |  |

| TXD1/L1TXD  | 0         | TXD1  | 0 | L1TXD  | 0 | L1TXD  | 0   | L1TXD |  |

| RCLK1/L1CLK | I/O       | RCLK1 | I | L1CLK  | I | L1CLK  | I   | L1CLK |  |

| TCLK1/L1SY0 | I/O       | TCLK1 | 0 | SDS1   | 0 | SDS1   | I   | L1SY0 |  |

| CD1/L1SY1   | I         | CD1   | I | L1SYNC | I | L1SYNC | I   | L1SY1 |  |

| CTS1/L1GR   | I         | CTS1  | I | L1GR   | I | L1GR   |     |       |  |

| RTS1/L1RQ   | 0         | RTS1  | 0 | GCIDCL | 0 | L1RQ   | 0   | RTS   |  |

| BRG1        | 0         | BRG1  | 0 | BRG1   | 0 | BRG1   | 0   | BRG1  |  |

#### NOTES:

1. In IDL and GCI mode, SDS2 is output on the PA7 pin.

2. CD1 may be used as an external sync in NMSI mode.

3. RTS is the RTS1, RTS2, or RTS3 pin according to which SCCs are connected to the PCM highway.

#### RXD1/L1RXD—Receive Data/Layer-1 Receive Data

This input is used as the NMSI1 receive data in NMSI mode and as the receive data input in IDL, GCI, and PCM modes.

## TXD1/L1TXD—Transmit Data/Layer-1 Transmit Data

This output is used as NMSI1 transmit data in NMSI mode and as the transmit data output in IDL, GCI, and PCM modes. TXD1 may be configured as an open-drain output in NMSI mode. L1TXD in IDL and PCM mode is a three-state output. In GCI mode, it is an open-drain output.

## RCLK1/L1CLK—Receive Clock/Layer-1 Clock

This pin is used as an NMSI1 bidirectional receive clock in NMSI mode or as an input clock in IDL, GCI, and PCM modes. In NMSI mode, this signal is an input when SCC1 is working with an external clock and is an output when SCC1 is working with its baud rate generator. The RCLK1 output can be three-stated by setting bit 12 in the CKCR register (see 3.9 Clock Control Register).

## TCLK1/L1SY0/SDS1—Transmit Clock/PCM Sync/Serial Data Strobe 1

This pin is used as an NMSI1 bidirectional transmit clock in NMSI mode, as a sync signal in PCM mode, or as the SDS1 output in IDL/GCI modes. In NMSI mode, this signal is an input when SCC1 is working with an external clock and is an output when SCC1 is working with its baud rate generator. The TCLK1 output can be three-stated by setting bit 13 in the CKCR register (see 3.9 Clock Control Register).

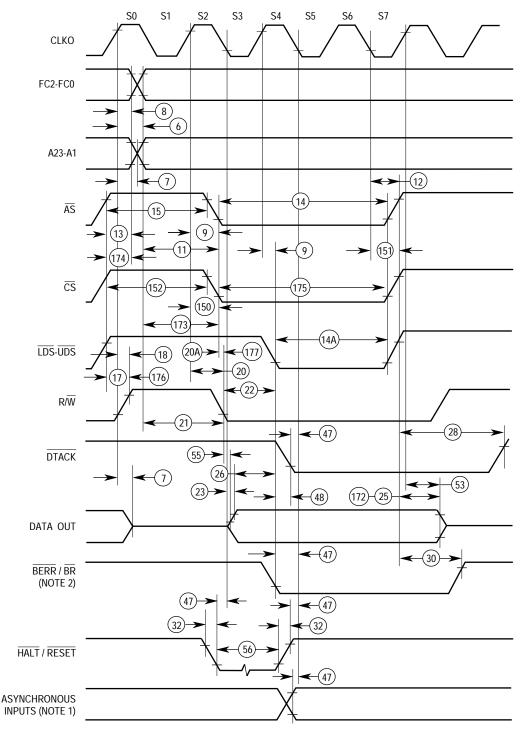

NOTES:

- 1. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is <u>lin</u>ear between between 0.8 volt and 2.0 volts.

- 2. Because of loading variations, R/W may be valid after AS even though both are initiated by the rising edge of S2 (specification #20A)

- 3. Each wait state is a full clock cycle inserted between S4 and S5.

#### Figure 6-3. Write Cycle Timing Diagram

## 6.10 AC ELECTRICAL SPECIFICATIONS—EXTERNAL MASTER INTERNAL ASYNCHRONOUS READ/WRITE CYCLES

(see Figure 6-8 and Figure 6-9)

|      |                                                                    |                     | 16.67 MHz |     | 20 MHz |     | 25 MHz |     |      |

|------|--------------------------------------------------------------------|---------------------|-----------|-----|--------|-----|--------|-----|------|

| Num. | Characteristic                                                     | Symbol              | Min       | Max | Min    | Max | Min    | Max | Unit |

| 100  | $R/\overline{W}$ Valid to $\overline{DS}$ Low                      | t <sub>RWVDSL</sub> | 0         | _   | 0      |     | 0      | _   | ns   |

| 101  | DS Low to Data-In Valid                                            | t <sub>DSLDIV</sub> |           | 30  |        | 25  |        | 20  | ns   |

| 102  | DTACK Low to Data-In Hold Time                                     | t <sub>DKLDH</sub>  | 0         |     | 0      |     | 0      |     | ns   |

| 103  | $\overline{AS}$ Valid to $\overline{DS}$ Low                       | t <sub>ASVDSL</sub> | 0         |     | 0      |     | 0      |     | ns   |

| 104  | $\overline{DTACK}$ Low to $\overline{AS}$ , $\overline{DS}$ High   | t <sub>DKLDSH</sub> | 0         | —   | 0      |     | 0      |     | ns   |

| 105  | DS High to DTACK High                                              | t <sub>DSHDKH</sub> |           | 45  | _      | 40  | —      | 30  | ns   |

| 106  | $\overline{\text{DS}}$ Inactive to $\overline{\text{AS}}$ Inactive | t <sub>DSIASI</sub> | 0         | —   | 0      | —   | 0      |     | ns   |

| 107  | DS High to R/W High                                                | t <sub>DSHRWH</sub> | 0         | —   | 0      | —   | 0      | —   | ns   |

| 108  | DS High to Data High Impedance                                     | t <sub>DSHDZ</sub>  | —         | 45  | —      | 40  | —      | 30  | ns   |

| 108A | $\overline{\text{DS}}$ High to Data-Out Hold Time (see Note)       | t <sub>DSHDH</sub>  | 0         |     | 0      |     | 0      |     | ns   |

| 109A | Data Out Valid to DTACK Low                                        | t <sub>DOVDKL</sub> | 15        | _   | 15     | _   | 10     | _   | ns   |

NOTE: If  $\overline{AS}$  is negated before  $\overline{DS}$ , the data bus could be three-stated (spec 126) before  $\overline{DS}$  is negated.

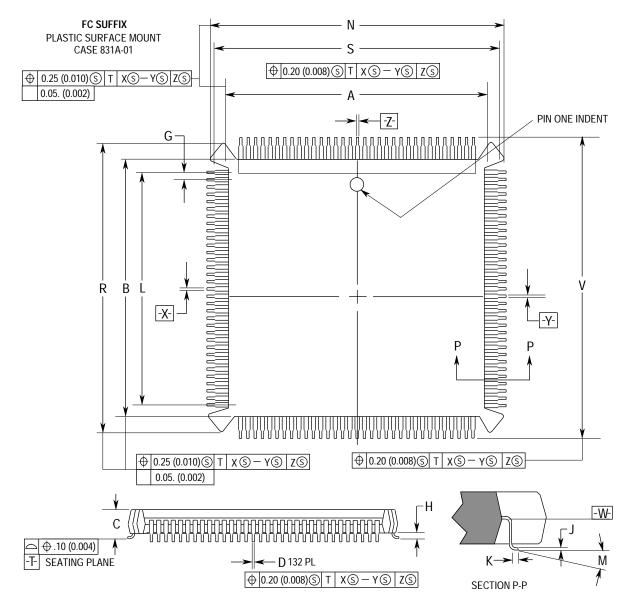

## 7.2.2 Plastic Surface Mount (PQFP)

|     | MILLIN   | IETERS | INCHES    |       |  |  |

|-----|----------|--------|-----------|-------|--|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |  |

| Α   | 24.06    | 24.20  | 0.947     | 0.953 |  |  |

| В   | 24.06    | 24.20  | 0.947     | 0.953 |  |  |

| С   | 4.07     | 4.57   | 0.160     | 0.180 |  |  |

| D   | 0.21     | 0.30   | 0.008     | 0.012 |  |  |

| G   | 0.64 BSC |        | 0.025 BSC |       |  |  |

| Н   | 0.51     | 1.01   | 0.020     | 0.040 |  |  |

| ſ   | 0.16     | 0.20   | 0.006     | 0.008 |  |  |

| Κ   | 0.51     | 0.76   | 0.020     | 0.030 |  |  |

| Μ   | 0°       | 8°     | 0°        | 8°    |  |  |

| Ν   | 27.88    | 28.01  | 1.097     | 1.103 |  |  |

| R   | 27.88    | 28.01  | 1.097     | 1.103 |  |  |

| S   | 27.31    | 27.55  | 1.075     | 1.085 |  |  |

| V   | 27.31    | 27.55  | 1.075     | 1.085 |  |  |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCHES

- 3. DIM A, B, N, AND R DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION FOR DIMENSIONS A AND B IS 0.25 (0.010). FOR DIMENSIONS N AND R IS 0.18 (0.007).

- 0.25 (0.010), FOR DIMENSIONS N AND R IS 0.18 (0.007).

4. DATUM PLANE -W- IS LOCATED AT THE UNDERSIDE OF LEADS WHERE LEADS EXIT PACKAGE BODY.

- DATUMS X-Y AND Z TO BE DETERMINED WHERE CENTER LEADS EXIT PACKAGE BODY AT DATUM -W-.

- 6. DIM S AND V TO BE DETERMINED AT SEATING PLANE, DATUM -T-.

- 7. DIM A, B, N AND R TO BE DETERMINED AT DATUM PLANE -W-.

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

C68302 Applications

NP

Freescale Semiconductor, Inc.

|           | BSET.B              | #\$7,(A2)                       | ·Cot Boody bit of Ty BD                                               |

|-----------|---------------------|---------------------------------|-----------------------------------------------------------------------|

| * Tho Tr  |                     |                                 | ;Set Ready bit of Tx BD<br>ot checked since the only one is CTS lost, |

|           |                     |                                 | TTS is ignored in this application.                                   |

|           |                     |                                 | it to the next Tx BD                                                  |

| 1110 101  | BTST.B              | #\$05,(A2)                      | itest Wrap bit                                                        |

|           | BNE.B               | REINIT2                         | ; If set, reinit A2 to 700640                                         |

|           | ADDA.W              | #\$08,A2                        | ;else inc A2 by 8 to next Tx BD                                       |

|           | BRA.B               | CONT                            | Jump to Continue on                                                   |

| REINIT2 N | MOVEA.L             | #\$700640,A2                    | Reinitialize A2                                                       |

| * Determ  | ine what t          |                                 | "echo" will be and then go to OUTERLOOP                               |

| CONT      | ADDO.W              | #\$1,A1                         | ;Increment A1 to next byte to send                                    |

|           | CMPA.L              | #\$30004,A1                     | ;Is A1 = 30004? ***                                                   |

|           | BEQ.B               | NEWA1                           | ;If so, go to NEWA1                                                   |

|           | BRA.B               | OUTLOOP                         | ;Jump back to outerloop and wait                                      |

| NEWA1     | SUBO.W              | #\$02.A1                        | ;Set Al back to 30002 ?***                                            |

|           | BRA.B               | OUTLOOP                         | ;Jump back to outerloop and wait                                      |

| * The two | o lines wi          | th *** above ar                 | re dependent on the number of Rx BDs used.                            |

| * If the  | number is           | increased, thes                 | se values should be increased by the same                             |

| * amount  | . These ar          | e the only lines                | s dependent on the Rx BD or Tx BD setup.                              |

| *******   | * * * * * * * * * * | * * * * * * * * * * * * * * * * | ****************                                                      |

| *SCC3 I   | nterrupt            | Routine                         |                                                                       |

|           | ORG                 | \$30500                         |                                                                       |

|           | CLR.L               | D1                              | ;clear D1                                                             |

|           | MOVE.B              | SCCE3,D1                        | ;Move SCCE3 status to D1                                              |

|           | MOVE.B              | #\$15,SCCE3                     | ;Clear only BRK. BSY and RX in SCCE3.                                 |

|           | BTST.B              | <u> </u>                        | ;Is BSY set?                                                          |

|           | BISI.B<br>BNE.B     | #\$2.D1<br>BUSY                 | ;Jump to BUSY handler if set                                          |

|           | DINE.D              | BUD1                            | , oump to bost nandler if set                                         |

|           |                     |                                 |                                                                       |

| * Test Bi | reak:               |                                 |                                                                       |

| BRKTEST   | BTST.B              | #\$4,D1                         | ;Is BRK set?                                                          |

|           | BNE.B               | BREAK                           | ;Jump to BREAK handler if set                                         |

| *Test Red | ceive:              |                                 |                                                                       |

| RECTEST   | BTST.B              | #\$0,D1                         | ;Is RX set?                                                           |

|           | BNE.B               | RECEIVE                         | ;Jump to RECEIVE handler if set                                       |

|           | JMP                 | ALMDONE                         | ;Jump to About Done (impossible)                                      |

| * Busy ha | andler:             |                                 |                                                                       |

| BUSY      | ADDQ.B              | #1,D5                           | ;Inc Busy counter (no receive buffers)                                |

|           | BSET.B              | #\$F,(A0)                       | ;set Empty bit of current Rx BD                                       |

|           | JMP                 | BRKTEST                         | ;Jump to test for BREAK                                               |

| *D11      |                     |                                 |                                                                       |

| *Break ha |                     |                                 | umbia and income the literation                                       |

| BREAK     | NOP                 | 411                             | ;This code ignores received breaks                                    |

| * The UAP |                     |                                 | number of breaks received                                             |

| *Dogo'    | JMP                 | RECTEST                         | ;Jump to test for RECEIVE                                             |

|           | handler:            | H1 D2                           | 'Ingroment numbers of shows we show ?                                 |

| RECEIVE   | ADDQ.W              | #1,D3                           | ;Increment number of chars received                                   |

|           | ADDQ.B              | #1,D6                           | ;D6 inc by 1 (character ready to send)                                |

|           | ADDQ.W              | #1,A0                           | ;Inc A0 to point to Rx BD byte status                                 |

|           | CMPI.B              | #\$0,(A0)                       | ;Does status = 00?                                                    |

|           | BNE.B               | BSTAT                           | Jump to Bad Status it not 00                                          |

| INCPTR    | SUBQ.W              | #1,A0                           | ;Dec A0 to point to beginning of Rx BD                                |

|           | ANDI.W              | #\$FF00,(A0)                    | Clear out Rx BD status                                                |

|           |                     | 11 T = 2 0 0 / (110 /           |                                                                       |

|           |                     |                                 |                                                                       |

MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

SCCs on the MC68302 can do this very efficiently because of their sophisticated DMA capability, and very little MC68000 core intervention is required.

Third, some applications require the switching of data without interfering with the protocol encoding itself. For instance, in a multiplexer, data from a high-speed time-multiplexed serial stream is multiplexed into multiple low-speed data streams. In this case, the idea is to switch the data path but not alter the protocol encoded on that data path.

Finally, some applications require a special protocol that does not fall under the category of HDLC, UART, etc. In some instances, transparent mode can be used; however, care should be taken to understand the capabilities of transparent mode before trying this. The most important issue is how this new protocol recognizes its frames on the receiving end. Transparent mode on the MC68302 was designed to work well receiving continuous streams of data (no gaps in the data exist over time). This is different from receiving transparent frames; al-though there is some support for this, it is limited on the MC68302.

## D.8.3 Physical Interface to Accompany Transparent Mode

Before discussing the details of transparent mode timing, we need to chose the physical interface to go with the transparent mode. The timings associated with transparent mode differ based on the physical interface chosen.

The MC68302 supports the following four physical interfaces:

- Nonmultiplexed Serial Interface—NMSI

- Pulse Code Modulation Highway—PCM

- Interchip Digital Link—IDL

- General Circuit Interface—GCI

You will probably chose either an NMSI or PCM highway interface, unless you are designing an ISDN-based system. If you are designing an ISDN-based system, you will probably choose either an IDL or GCI interface. The following paragraphs discuss all the interfaces, but special attention is given to the NMSI.

#### NOTE

The following discussion assumes some knowledge of the interfaces. For more applications information on these interfaces, refer to 4.4 Serial Channels Physical Interface.

The most commonly used physical interface on the MC68302 is the nonmultiplexed serial interface (NMSI). The NMSI consists of seven basic modem (RS-232) signals: TXD, TCLK, RXD, RCLK, RTS, CTS, and CD. Each of the three SCCs can have its own set of these signals, as shown in Figure D-21.

# C Programming Reference Freescale Semiconductor, Inc.

BIT 15—Reserved for future use; should be written with zero.

#### EXSYN—External Sync

When set, the SCC receiver uses the L1SY1/CD1, CD2, or CD3 pins to synchronize the receiver and transmitter to the beginning of a transparent frame.

#### NTSYN—No Transmit SYNC

This bit must be set for the SCC to operate in the transparent mode.

### REVD—Reverse Data

When this bit is set, the receiver and transmitter will reverse the character bit order, transmitting the most significant bit first.

Bits 11-6—Reserved for future use; should be written with zero.

### DIAG1, DIAG0—Diagnostic Mode

- 00 = Normal operation.

- 01 = Loopback mode.

- 10 = Automatic echo.

- 11 = Software operation.

### ENR—Enable Receiver

- 0 = Receiver is disabled.

- 1 = Receiver is enabled

## ENT—Enable Transmitter

- 0 = Transmitter is disabled.

- 1 = Transmitter is enabled.

## MODE1, MODE0—Channel Mode

- 00 = HDLC.

- 01 = Asynchronous (UART and DDCMP).

- 10 = Synchronous DDCMP and V.110.

- 11 = BISYNC and Promiscuous (Transparent).

**E.3.1.2.3 SCC Data Synchronization Register (DSR).** This 16-bit register is located at offset \$886 (SCC1), \$896 (SCC2), and \$8A6 (SCC3). The DSR specifies the pattern used for the receive frame synchronization procedure if the EXSYN bit is cleared. For transparent, the DSR may be set to any desired pattern. The DSR value after reset is \$7E7E.

| 15   | 8 | 7    | 0 |

|------|---|------|---|

| SYN2 |   | SYN1 |   |

**E.3.1.2.4 Transparent Event Register (SCCE).** This 8-bit register is located at offset \$888 (SCC1), \$898 (SCC2), and \$8A8 (SCC3) on D15-D8 of a 16-bit data bus. The SCCE is used to report events recognized by the transparent channel. Bits must be cleared by the user to avoid missing interrupt events. Bits are cleared by writing ones to the corresponding bit positions

#### MC68360 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

Exception 3-66 Processing 2-7 Exceptions 3-14 Grant (BG) 5-11 Grant Acknowledge (BGACK) 5-11 Latencies 3-58 Master 2-7, 3-56, 3-58, 4-5 Request (BR) 5-11 SDMA Retry 4-41 Signal Summary 5-13 Bus Error on SDMA Access 4-41 Bus Master 4-5 BUSW 2-1, 3-39, 5-6, See Signals, See Timers

#### С

C/I Channel 4-141 Carrier Detect Lost 4-61 CD 4-28, 4-40 **CEPT** 4-19 Chip-Select 2-13 Address Decode Conflict 3-44 AS 3-42 Base Address 3-48 Base Register 3-45 BERR 3-44, 3-46 Block Sizes 3-45 CS0 3-44, 3-46, 3-55, 5-23 DTACK 3-42, 3-47, 3-48 **EMWS 3-43 Option Register 3-45** Priority 3-43 Read-Only 3-48 **RESET** 3-44 **RMSCT 3-45** Test and Set 3-45 Write Protect Violation 3-44 Write-Only 3-48 **Chip-Select Timing 6-24** Circular Queue 4-32 Clear-to-Send Report 4-63 Clock Asynchronous Baud Rate 4-26 **Baud Rate Generator 4-25** CLKO 3-49, 5-5 **Clock Divider 4-26** Crystal 3-50

EXTAL 3-49 Synchronous Baud Rate 4-27 XTAL 3-49 Clock Divider 4-26 CMOS Level 5-2 Command 4-5 ENTER HUNT MODE Command 4-36, 4-37, 4-54, 4-126, 4-128, 4-130 **RESET BCS CALCULATION Command** 4-101 **RESTART TRANSMIT Command 4-73**, 4-92, 4-128 STOP TRANSMIT Command 4-36, 4-37, 4-42, 4-48, 4-49, 4-69, 4-71, 4-128, 4-130 TIMEOUT Command 4-142 TRANSMIT ABORT REQUEST Command 4-142 Command Execution Latency 4-7 Command Register 4-5 **Communications Processor 4-1** Configuration MC68302 IMP Control 2-12 System Registers 2-14 CP 1-6, 4-1 **CQFP** 7-2 CR 4-5 CS0 3-44, 3-46, 3-55, 5-23 CTS 4-28, 4-40

## D

**DACK 5-20** Data Type Asynchronous Bit Rate Adaption 4-119 **FIFO** 4-120 **Overrun Error** 4-120 Rx BD 4-120 SCCE 4-123 SCCM 4-124 Synchronization Error 4-120 Synchronous Bit Rate Adaption 4-118 **Terminal Equipment 4-117** Transmitter Underrun 4-120 Tx BD 4-122 V.110 80-Bit Frames 4-119 V.110 Event Register 4-123 V.110 Mask Register 4-124

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

Bus Semiconductor, Inc CP 1-3 0 Instructions eescal Interrupt

**IDL** Signals 4-12 Idle Status 4-40 IDMA (Independent DMA Controller) 3-54, 3-58, 5-10, 5-11, 5-20 AS 3-14 **BERR 3-15 BGACK 3-14** BR 3-14 Cycle 3-12 **Error** 3-14 Exceptions 3-14 **Bus Arbitration 3-14** DONE 3-4, 3-8, 3-13 DREQ 3-5, 3-6, 3-8, 3-12 DTACK 3-9, 3-21 External Burst Mode 3-11 Halt 3-14, 3-15 **MOVEP** 3-10 **Operand Packing 3-10 Registers** 3-31 **Reset** 3-14 **Retry** 3-14 Transfer Rate 3-2 **IMP** Features IMR 3-14, 3-32, 4-39 Instruction Type Variations 2-5 BERR 3-14, 3-15 HALT 3-14, 3-15 MOVE 2-19 **MOVEP** 3-10 Read-Modify-Write 2-11, 2-19 **RESET** 3-14 RTE 3-29 Test and Set 2-11 Internal Loopback 4-20 Internal Registers 1-6, 2-16 Internal Requests (INRQ) 3-17, See Interrupt Acknowledge 2-7, 2-8, 2-11, 2-13, 3-17, 3-19, 3-20 Autovector 2-8, 2-11 AVEC 3-18, 3-22, 5-12

**BCLR** 3-18 Control Pins 5-11 Controller 3-15 **DTACK 3-21 EXRQ** 3-17 FC2-FC0 3-17 IACK7 3-18, 3-22, 5-21 IMR 3-32, 4-39 **INRQ** 3-17 IOUT0 5-12 IOUT0/IOUT1/IOUT2 3-55 IPL2-IPL0 3-17, 3-19 IPR 3-20, 3-26, 4-39 IRQ1 3-17 **IRQ6** 3-17 IRQ7 3-17, 3-19 ISR 3-28, 4-39 Masking 3-20 Mode Dedicated 2-11 Normal 2-11 Nested 3-19 PB11 3-19, 3-21 Pending 5-10 Priority 3-20 Processing 2-11 Registers SR 2-2, 2-11 Request 3-58 **RTE 3-29 SCCE** 4-39 SCCM 4-39 Spurious 2-9, 2-11 SR 3-17, 3-20 Vector 3-17, 3-21, 3-27 Vector Number 3-22 Interrupt Acknowledge 2-11 Interrupt Pending Register (IPR) 3-20 IOM2 4-14 **IOUT0** 5-12 IOUT0/IOUT1/IOUT2 3-55 IOUT0/IOUT1/IOUT2 3-55, See Disable CPU, See Interrupt, See Signals **IPEND 3-58, See Signals** IPL2-IPL0 3-17, 3-19, 5-11, See Interrupt, See Signals **IPR 4-39**