#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                  | Active                                                     |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | M68000                                                     |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                           |

| Speed                           | 16MHz                                                      |

| Co-Processors/DSP               | Communications; RISC CPM                                   |

| RAM Controllers                 | DRAM                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers |                                                            |

| Ethernet                        | -                                                          |

| SATA                            |                                                            |

| USB                             |                                                            |

| Voltage - I/O                   | 5.0V                                                       |

| Operating Temperature           | -40°C ~ 85°C (TA)                                          |

| Security Features               | <u>.</u>                                                   |

| Package / Case                  | 132-BQFP Bumpered                                          |

| Supplier Device Package         | 132-PQFP (46x46)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68302ceh16c |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2. To clear bits 0 and 1 of SCC1, execute "MOVE.B #\$03,SCCE1"

- 3. To clear all bits in SCCE1, execute "MOVE.B #\$ff, SCCE1"

where SCCE1 is equated to the actual address of SCCE1.

#### NOTE

DO NOT use read-modify-write instructions to clear bits in an event register, or ALL bits in that register will inadvertently be cleared. Read-modify-write instructions include BSET, BCLR, AND, OR, etc. These instructions read the contents of a location, perform an operation, and write the result back, leaving the rest of the bits unchanged. Thus, if a bit is a one when read, it will be written back with a one, clearing that bit. For example, the instruction "BSET.B #0,SCCE1" will actually clear ALL bits in SCCE1, not just bit 0.

Table 3-7 shows the dedicated function of each pin. The third column shows the input to the peripheral when the pin is used as a general-purpose I/O pin.

| PBCNT Bit = 1<br>Pin Function | PBCNT Bit = 0<br>Pin Function | Input to Interrupt<br>Control and Timers |

|-------------------------------|-------------------------------|------------------------------------------|

| IACK7                         | PB0                           | _                                        |

| IACK6                         | PB1                           | _                                        |

| IACK1                         | PB2                           |                                          |

| TIN1                          | PB3                           | GND                                      |

| TOUT1                         | PB4                           | —                                        |

| TIN2                          | PB5                           | GND                                      |

| TOUT2                         | PB6                           |                                          |

| WDOG                          | PB7                           | _                                        |

Table 3-7. Port B Pin Functions

### 3.3.2.2 PB11-PB8

PB11–PB8 are four general-purpose I/O pins continuously available as general-purpose I/ O pins and, therefore, are not referenced in the PBCNT. PB8 operates like PB11–PB9 except that it can also be used as the DRAM refresh controller request pin, as selected in the system control register (SCR).

The direction of each pin is determined by the corresponding bit in the PBDDR. The port pin is configured as an input if the corresponding PBDDR bit is cleared; it is configured as an output if the corresponding PBDDR bit is set. PBDDR11–PBDDR8 are cleared on total system reset, configuring all PB11–PB8 pins as general-purpose input pins. (Note that the port pins do not have internal pullup resistors). The GIMR is also cleared on total system reset so that if any PB11–PB8 pin is left floating it will not cause a spurious interrupt.

The PB11–PB8 pins are accessed through the PBDAT. Data written to PBDAT11–PBDAT8 is stored in an output latch. If the port pin is configured as an output, the output latch data is gated onto the port pin. In this case, when PBDAT11–PBDAT8 is read, the contents of the output latch associated with the output port pin are read. If a port B pin is configured as an input, data written to PBDAT is still stored in the output latch but is prevented from reaching the port pin. In this case, when PBDAT is read, the state of the port pin is read.

When a PB11–PB8 pin is configured as an input, a high-to-low change will cause an interrupt request signal to be sent to the IMP interrupt controller. Each of the four interrupt requests is associated with a fixed internal interrupt priority level within level 4. (The priority at which each bit requests an interrupt is detailed in Table 3-4.) Each request can be masked independently in the IMP interrupt controller by clearing the appropriate bit in the IMR (PB11–PB8). The input signals to PB11–PB8 must meet specifications 190 and 191 shown in Table 6.16 of the AC Electrical Specifications.

## 3.3.3 I/O Port Registers

The I/O port consists of three memory-mapped read-write 16-bit registers for port A and three memory-mapped read-write 16-bit registers for port B. Refer to Figure 3-6 for the I/O port registers. The reserved bits are read as zeros.

- 1. Calculate what the mask should be. For a 1 Megabyte block, the address lines A0 through A19 are used to address bytes within the block, so they need to be masked out.

- 2. Write \$3E00 to OR2 (DTACK=1 for 1 wait state, M23-M20 = 1 to use these bits in the comparison, M19-M13 = 0 to mask these address bits, MRW = 0 to enable the chip select for both read and write, and CFC = 0 to mask off function code comparison).

- 3. Write \$0401 to BR2 (FC2-FC0 = 0 don't care, A23-A13 = base address, RW = 0 don't care, and EN =1 to enable the chip select.

#### NOTE

The mask bits in the OR are used to mask the individual address bits, so in the previous example, if bit 12 (M23) was changed to a zero, then CS2 would assert for a 1 Megabyte block beginning at \$200000 and a 1 Megabyte block at \$A00000.

## 3.7 ON-CHIP CLOCK GENERATOR

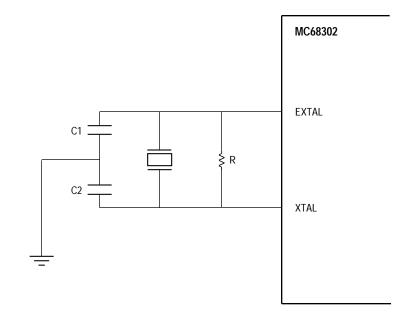

The IMP has an on-chip clock generator that supplies clocks to both the internal M68000 core and peripherals and to an external pin. The clock circuitry uses three dedicated pins: EXTAL, XTAL, and CLKO.

The external clock/crystal (EXTAL) input provides two clock generation options. EXTAL may be used to interface the internal generator to an external crystal (see Figure 3-10). Typical circuit parameters are C1 = C2 = 25 pF and R = 700 k $\Omega$  using a parallel resonant crystal. Typical crystal parameters are Co < 10 pF and Rx = 50  $\Omega$ . The equivalent load capacitance (CL) of this circuit is 20 pF, calculated as (C1 + C<sub>in</sub>)/2, where C1 = C2 = 25 pF and C<sub>in</sub> = 15 pF maximum on the EXTAL pin.

Figure 3-10. Using an External Crystal

# stem Integration Block (SIB)

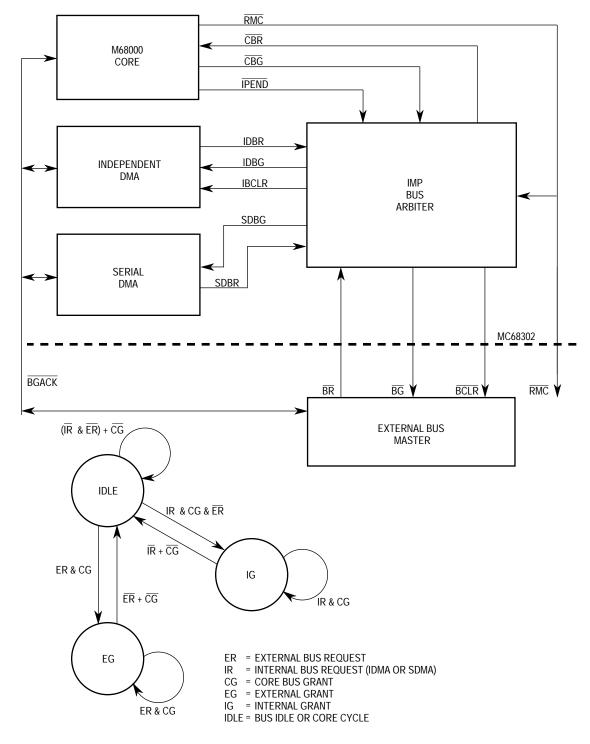

After system reset, this bit defaults to zero. If BCLM is set, then the typical maximum interrupt latency is about 78 clocks in a zero-wait-state system. This assumes a standard instruction mix, that the IDMA is just beginning a four-bus-cycle transfer when the interrupt becomes pending, and that an SDMA has an access pending (one bus cycle). Interrupt execution time is 44 clocks and includes the time to execute the interrupt acknowledge cycle, save the status register and PC value on the stack, and then vector to the first location of the interrupt service routine. Thus, the calculation is 78 = 14 (instruction completion) + 20 (DMAs) + 44 (interrupt execution).

SDMA operation is not affected by the BCLM bit. Note that the SDMA accesses only one byte/word of external memory at a time before giving up the bus and that accesses are relatively infrequent. External bus master operation may or may not be affected by the BCLM bit, depending on whether the BCLR signal is used to clear the external master off the bus.

Without using the BCLM bit, the maximum interrupt latency includes the maximum time that the IDMA or external bus master could use the bus in the worst case. Note that the IDMA can limit its bus usage if its requests are generated internally.

#### NOTE

The IPA status bit will be set, regardless of the BCLM value.

#### SAM—Synchronous Access Mode

This bit controls how external masters may access the MC68302 peripheral area. This bit is not relevant for applications that do not have external bus masters that access the MC68302. In applications such as disable CPU mode, in which the M68000 core is not operating, the user should note that SAM may be changed by an external master on the first access of the MC68302, but that first write access must be asynchronous with three wait states. (If DTACK is used to terminate bus cycles, this change need not influence hardware.)

- 0 = Asynchronous accesses. All accesses to the MC68302 internal RAM and registers (including BAR and SCR) by an external master are asynchronous to the MC68302 clock. Read and write accesses are with three wait states, and DTACK is asserted by the MC68302 assuming three wait-state accesses. This is the default value.

- 1 = Synchronous accesses. All accesses to the MC68302 internal RAM and registers (including BAR and SCR) must be synchronous to the MC68302 clock. Synchronous read accesses may occur with one wait state if EMWS is also set to one.

## 3.8.4 Disable CPU Logic (M68000)

The MC68302 can be configured to operate solely as a peripheral to an external processor. In this mode, the on-chip M68000 CPU should be disabled by strapping DISCPU high during system reset (RESET and HALT asserted simultaneously). The internal accesses to the MC68302 peripherals and memory may be asynchronous or synchronous. During synchronous reads, one wait state may be used if required (EMWS bit set). The following pins change their functionality in this mode:

1. BR will be an output from the IDMA and SDMA to the external M68000 bus, rather than being an input to the MC68302.

Figure 3-12. IMP Bus Arbiter

stem Integration Block (SIB)

#### 3.8.7.2.2 Lowest Power Mode

In this mode, the processor frequency can be further reduced beyond the minimum system frequency limit (e.g., lower than the limit of 8 MHz). In this mode, the LPREC bit must be set to one by the user, causing the M68000 core to be reset as the lowest power mode is exited. The M68000 core is given an internal reset sequence for 16 to 32 clock cycles, and execution resumes with the fetching of the reset vector. The RESET pin does not externally assert during the internal reset sequence. The entire M68000 core status is lost in this mode (A0–A7, D0–D7, PC, SR, etc.); however, the IMP peripheral status is retained (this includes the dual-port RAM, internal registers, BAR, etc.).

The following list gives a step-by-step example of how to use the lowest power mode. For this example, an external wakeup signal is issued to the PB11 pin to exit the lowest power mode.

- 1. Set the lower byte of the SCR (location \$F7) to \$FF. This sets the LPREC bit, the LPEN bit, and sets the clock divider to its maximum value (divide by 1024).

- 2. Disable all interrupts except PB11 in the IMR.

- Turn off any unneeded peripherals, such as the SCCs, by clearing the ENR and ENT bits. Also turn off any unneeded baud rate generators by setting the EXTC bits in the SCON registers. This procedure can save as much as 4 mA per SCC at 16.67 MHz. (EXTC is cleared by default after reset.)

- 4. Execute the STOP instruction. Lowest power mode is now entered.

- 5. A wakeup signal comes from the system to the PB11 pin.

- 6. The IMP then generates the PB11 interrupt and a reset is automatically generated to the M68000 core.

- 7. After the IMP is reset, software processing continues from the exception vector table reset vector address. The M68000 is reset, but the rest of the IMP retains its state.

### 3.8.7.2.3 Lowest Power Mode with External Clock

After the IMP is safely in the lowest power mode the EXTAL frequency can be externally reduced to a lower frequency. In this mode, the clock dividing should not be done in the LPCD bits, but rather externally on the EXTAL pin.

#### NOTE

The input to EXTAL must be greater than or equal to 25kHz.

The major difference in this mode, is that the entire IMP is now running at a lower clock rate. Any IMP on-chip peripherals and any bus cycles executed by one of the on-chip masters are thus slowed down.

#### NOTE

The use of external clocks with the SCCs allows the original serial rates to be maintained; however, before attempting this, the SCC performance data should be carefully reviewed (see Ap-

mmunications Processor (CP)

The IDL interface supports the CCITT I.460 recommendation for data rate adaptation. The IDL interface can access each bit of the B channel as an 8-kbps channel. A serial interface mask register (SIMASK) for the B channels specifies which bits are supported by the IDL interface. The receiver will support only the bits enabled by SIMASK. The transmitter will transmit only the bits enabled by the mask register and will three-state L1TXD otherwise.

Refer to Figure 4-6 for an example of supporting two bits in the B1 channel and three bits in the B2 channel.

## 4.4.2 GCI Interface

The normal mode of the GCI (also known as ISDN-Oriented Modular rev 2.2 (IOM2)) ISDN bus is fully supported by the IMP. The IMP also supports channel 0 of the Special Circuit Interface T (SCIT) interface, and in channel 2 of SCIT, supports the D channel access control for S/T interface terminals, using the command/indication (C/I) field. The IMP does not support the Telecom IC (TIC) bus.

The GCI bus consists of four lines: two data lines, a clock, and a frame synchronization line. Usually an 8-kHz frame structure defines the various channels within the 256-kbps data rate as indicated in Figure 4-8. However, the interface can also be used in a multiplexed frame structure on which up to eight physical layer devices multiplex their GCI channels. L1SY1 must provide the channel SYNC. In this mode, the data rate would be 2048 kbps.

The GCI clock rate is twice the data rate. The clock rate for the IMP must not exceed the ratio of 1:2.5 serial clock to parallel clock. Thus, for a 16.67-MHz system clock, the serial clock rate must not exceed 6.67 MHz.

The IMP also supports another line for D-channel access control—the L1GR line. This signal is not part of the GCI interface definition and may be used in proprietary interfaces.

#### NOTE

When the L1GR line is not used, it should be pulled high. The IMP has two data strobe lines (SDS1 and SDS2) for selecting either or both of the B1 and B2 channels and the data rate clock (L1CLK). These signals are used for interfacing devices that do not support the GCI bus. They are configured with the SIMASK register and are active only for bits that are not masked.

The monitor channel is used to transfer data between layer-1 devices and the control unit (i.e., the M68000 core). The command/indication channel is used to control activation/deactivation procedures or for the switching of test loops by the control unit.

The IMP supports all five channels of the GCI channel 0. The following table shows where each channel can be routed. The two B channels can be concatenated and routed to the same SCC channel.

| GCI Channel 0 | Serial Controllers |

|---------------|--------------------|

| D             | SCC1, SCC2, SCC3   |

| B1            | SCC1, SCC2, SCC3   |

| B2            | SCC1, SCC2, SCC3   |

| M             | SMC1               |

| C/I           | SMC2               |

The GCI interface supports the CCITT I.460 recommendation for data rate adaptation. The GCI interface can access each bit of the B channel as an 8-kbps channel. The mask register (SIMASK) for the B channels specifies which bits are supported by the GCI interface. The receiver will receive only the bits that are enabled by SIMASK; the transmitter will transmit only the bits that are enabled by SIMASK and will not drive the L1TXD pin otherwise (L1TXD in GCI mode is an open-drain output).

The IMP supports contention detection on the D channel. When the IMP has data to transmit on the D channel, it checks bit 4 of the SCIT C/I channel 2. The physical layer device monitors the physical layer bus for activity on the D channel and indicates with this bit that the channel is free. If a collision is detected on the D channel, the physical layer device sets bit 4 of C/I channel 2 to logic high. The IMP then aborts its transmission and retransmits the frame when this bit is asserted again. This procedure is handled automatically for the first two buffers of a frame. The L1GR line may also be used for access to the S interface D channel. This signal is checked by the IMP, and the physical layer device should indicate that the S interface D channel is free by asserting L1GR.

In the deactivated state, the clock pulse is disabled, and the data line is a logic one. The layer-1 device activates the IMP by enabling the clock pulses and by an indication in the channel 0 C/I channel. The IMP will then report to the M68000 core by a maskable interrupt that a valid indication is in the SMC2 receive buffer descriptor.

When the M68000 core activates the line, it sets SETZ in the serial interface mode (SIMO-DE) register, causing the data output from L1TXD to become a logic zero. Code 0 (command timing TIM) will be transmitted on channel 0 C/I channel to the layer-1 device until the SETZ is reset. The physical layer device will resume transmitting the clock pulses and will give an indication in the channel 0 C/I channel. The M68000 core should reset SETZ to enable data output.

## 4.4.3 PCM Highway Mode

In PCM highway mode, one, two, or all three SCCs can be multiplexed together to support various time-division multiplexed interfaces. PCM highway supports the standard T1 and CEPT interfaces as well as user-defined interfaces. In this mode, the NMSI1 pins have new names and functions (see Table 4-2).

If RTS is programmed to be asserted by the SCC, it will be asserted once buffered data is loaded into the transmit FIFO and a falling TCLK edge occurs. The following table shows the transmit data delays.

| Protocol Type                      | From<br>RTS Low | From<br>CTS Low |

|------------------------------------|-----------------|-----------------|

| Asynchronous Protocols (16x clock) | 0               | 48              |

| Synchronous Protocols (1x clock)   | 1               | 3.5             |

| Table 4-5. Transmit Data Delay | (TCLK Periods) |

|--------------------------------|----------------|

|--------------------------------|----------------|

NOTES:

1.  $\overline{\text{RTS}}$  low values assume  $\overline{\text{CTS}}$  is already asserted when  $\overline{\text{RTS}}$  is asserted.

2. CTS low values assume CTS met the asynchronous setup time;

otherwise, an additional clock may be added.

RTS is negated by the SCC one clock after the last bit in the frame. Figure 4-13 shows a diagram of synchronous mode timing from RTS low. Figure 4-14 shows a diagram of synchronous mode timing delays from CTS low.

The SCC samples  $\overline{\text{CTS}}$  on the every rising edge of the TCLK. If  $\overline{\text{CTS}}$  is negated when  $\overline{\text{RTS}}$  is asserted, a CTS lost error occurs. If a synchronous protocol is used, the transmit data will be aborted after four additional bits are transmitted. If an asynchronous protocol is used, the transmit data will be aborted after three additional bits are transmitted. See the transmit error section of each protocol for further details and steps to be taken following a CTS lost error.

The SCC latches its first bit of valid receive data on the same clock edge (rising RCLK) that samples  $\overline{CD}$  as low. The only exception is when the EXSYN bit is set in the SCC mode register for the BISYNC and Transparent protocols.

If  $\overline{CD}$  is negated during frame reception, a CD lost error occurs and the SCC will quit receiving data within four additional bit times. At this point, any residue of bits less than 8 bits (or 16 bits in HDLC or transparent modes) will be discarded and not written to memory. Thus, the last bit written to memory will be within plus or minus four bit times from the point at which  $\overline{CD}$  was negated.

#### NOTE

The CTS lost error and CD lost error (with CTS and CD under automatic control) is not intended to implement a flow control method in the UART protocol. The software operation of the DIAG1–DIAG0 bits should be chosen if UART flow control is desired, with transmission being temporarily suspended by the FRZ bit in the UART event register. CTS lost and CD lost, as defined here, are intended to implement the aborting of transmission and reception as defined in many synchronous protocols.

01 = Loopback mode

In this mode, the transmitter output is internally connected to the receiver input while the receiver and the transmitter operate normally. The value on the RXD pin is ignored. For the NMSI2 and NMSI3 pins, the TXD pin may be programmed to either show the transmitted data or not show the data by programming port A par-

the SCC mode register when that SCC is configured for HDLC. The read-write HDLC mode register is cleared by reset.

| 15   | 14   | 13   | 12   | 11  | 10  | 9 | 8   | 7   | 6   | 5 |                      | 0 |  |

|------|------|------|------|-----|-----|---|-----|-----|-----|---|----------------------|---|--|

| NOF3 | NOF2 | NOF1 | NOF0 | C32 | FSE | _ | RTE | FLG | ENC |   | COMMON SCC MODE BITS |   |  |

NOF3–NOF0—Minimum Number of Flags between Frames or before Frames (0 to 15 Flags)

If NOF3–NOF0 = 0000, then no flags will be inserted between frames. Thus, the closing flag of one frame will be followed immediately by the opening flag of the next frame in the case of back-to-back frames.

C32-CRC16/CRC32

$\begin{array}{l} 0 = & 16 \text{-bit CCITT CRC } (X^{16} + X^{12} + X^{5} + 1) \\ 1 = & 32 \text{-bit CCITT CRC } (X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} \\ & + & X^{5} + X^{4} + X^{2} + X^{1} + 1) \end{array}$

FSE—Flag Sharing Enable

- 0 = Normal operation

- 1 = If NOF3–NOF0 = 0000, then a single shared flag is transmitted between back- toback frames. Other values of NOF3–NOF0 are decremented by one when FSE is set. This is useful in Signaling System #7 applications.

Bit 9—Reserved for future use.

### RTE—Retransmit Enable

- 0 = No automatic retransmission will be performed.

- 1 = Automatic retransmit enabled

Automatic retransmission occurs if a CTS lost condition happens on the first or second buffer of the frame. See 4.5.12.8 HDLC Error-Handling Procedure.

FLG—Transmit Flags/Idles between Frames and Control the RTS Pin

- 0 = Send ones between frames; RTS is negated between frames. If NOF–NOF0 is greater than zero, RTS will be negated for a multiple of eight transmit clocks. The HDLC controller can transmit ones in both the NRZ and NRZI data encoding formats. The CP polls the Tx BD ready bit every 16 transmit clocks.

- 1 = Send flags between frames. RTS is always asserted. The CP polls the Tx BD ready bit every eight transmit clocks.

### NOTE

This bit may be dynamically modified. If toggled from a one to a zero between frames, a maximum of two additional flags will be transmitted before the idle condition will begin. Toggling FLG will never result in partial flags being transmitted.

#

If this bit is cleared, the BISYNC controller will look for the SYN1–SYN2 sequence in the data synchronization register.

#### NTSYN—No Transmit SYNC

When this bit is set, the SCC operates in a promiscuous, totally transparent mode. See 4.5.16 Transparent Controller for details.

#### **REVD**—Reverse DATA

When this bit is set, the receiver and transmitter will reverse the character bit order, transmitting the most significant bit first. This bit is valid in promiscuous mode.

#### BCS—Block Check Sequence

0 = LRC

For even LRC, the PRCRC and PTCRC preset registers in the BISYNC-specific parameter RAM should be initialized to zero before the channel is enabled. For odd LRC, the PRCRC and PTCRC registers should be initialized to ones. The LRC is formed by the Exclusive OR of each 7-bits of data (not including synchronization characters), and the parity bit is added after the final LRC calculation.

The receiver will check character parity when BCS is programmed to LRC and the receiver is not in transparent mode. The transmitter will transmit character parity when BCS is programmed to LRC and the transmitter is not in transparent mode. Use of parity in BISYNC assumes the use of 7-bit data characters.

#### 1 = CRC16

The PRCRC and PTCRC preset registers should be initialized to a preset value of all zeros or all ones before the channel is enabled. In both cases, the transmitter sends the calculated CRC non-inverted, and the receiver checks the CRC against zero. Eight-bit characters (without parity) are configured when CRC16 is chosen. The CRC16 polynomial is as follows:

$$\chi^{16} + \chi^{15} + \chi^2 + 1$$

Bit 10—Reserved for future use.

#### RTR—Receiver Transparent Mode

- 0 = The receiver is placed in normal mode with SYNC stripping and control character recognition operative.

- 1 = The receiver is placed in transparent mode. SYNCs, DLEs, and control characters are only recognized after a leading DLE character. The receiver will calculate the CRC16 sequence, even if programmed to LRC while in transparent mode. PRCRC should be first initialized to the CRC16 preset value before setting this bit.

#### RBCS—Receive Block Check Sequence

The BISYNC receiver internally stores two BCS calculations with a byte delay (eight serial clocks) between them. This enables the user to examine a received data byte and then decide whether or not it should be part of the BCS calculation. This is useful when control

#### Data Length

The data length is the number of octets that the V.110 controller has written to this BD data buffer. It is written by the CP once as the BD is closed. The V.110 controller will write nine bytes of data to the buffer. It will not write the all-zeros byte to the buffer.

#### NOTE

The actual buffer size should be greater than or equal to 10 bytes.

**Rx Buffer Pointer**

This pointer contains the address of the associated data buffer. The buffer may reside in either internal or external memory.

#### NOTE

The Rx buffer pointer must be even, and the upper 8 bits of the pointer must be zero for the function codes to operate correctly.

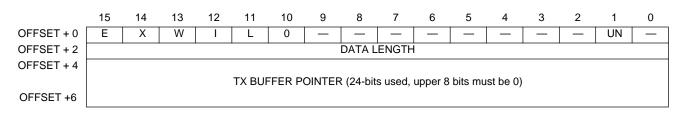

### 4.5.15.8 V.110 Transmit Buffer Descriptor (Tx BD)

Data is presented to the CP for transmission on an SCC channel by arranging it in buffers referenced by the channel's Tx BD table. The CP confirms transmission (or indicates error conditions) using the BDs to inform the M68000 core whether the buffers have been serviced. The Tx BD is shown in Figure 4-41.

Figure 4-41. V.110 Transmit Buffer Descriptor

The first word contains status and control bits. Bits 15–10 are prepared by the user before transmission. Bit 1 is set by the V.110 controller after the buffer has been transmitted. Bit 15 is set by the user and cleared by the V.110 controller.

#### R-Ready

- 0 = This buffer is not currently ready for transmission. The user is free to manipulate this BD and its associated buffer. The V.110 controller clears this bit after the buffer has been fully transmitted (or after an error condition is encountered).

- 1 = The data buffer has been prepared for transmission by the user (but not yet transmitted). No fields of this BD may be written by the user once this bit is set.

#### X—External Buffer

- 0 = The buffer associated with this BD is in internal dual-port RAM.

- 1 = The buffer associated with this BD is in external memory.

Signal Description

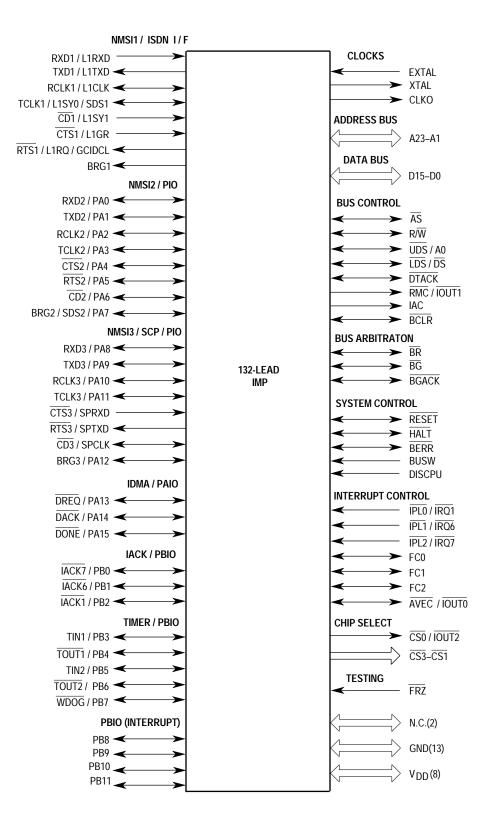

Figure 5-1. Functional Signal Groups

## 6.10 AC ELECTRICAL SPECIFICATIONS—EXTERNAL MASTER INTERNAL ASYNCHRONOUS READ/WRITE CYCLES

(see Figure 6-8 and Figure 6-9)

|      |                                                                    |                     | 16.67 | MHz | 20 I | MHz | 25 I | MHz |      |

|------|--------------------------------------------------------------------|---------------------|-------|-----|------|-----|------|-----|------|

| Num. | Characteristic                                                     |                     | Min   | Max | Min  | Max | Min  | Max | Unit |

| 100  | $R/\overline{W}$ Valid to $\overline{DS}$ Low                      | t <sub>RWVDSL</sub> | 0     | _   | 0    |     | 0    | _   | ns   |

| 101  | DS Low to Data-In Valid                                            | t <sub>DSLDIV</sub> |       | 30  |      | 25  |      | 20  | ns   |

| 102  | DTACK Low to Data-In Hold Time                                     | t <sub>DKLDH</sub>  | 0     |     | 0    |     | 0    |     | ns   |

| 103  | $\overline{AS}$ Valid to $\overline{DS}$ Low                       | t <sub>ASVDSL</sub> | 0     |     | 0    |     | 0    |     | ns   |

| 104  | $\overline{DTACK}$ Low to $\overline{AS}$ , $\overline{DS}$ High   | t <sub>DKLDSH</sub> | 0     | —   | 0    |     | 0    |     | ns   |

| 105  | DS High to DTACK High                                              | t <sub>DSHDKH</sub> |       | 45  | _    | 40  | —    | 30  | ns   |

| 106  | $\overline{\text{DS}}$ Inactive to $\overline{\text{AS}}$ Inactive | t <sub>DSIASI</sub> | 0     | —   | 0    | —   | 0    |     | ns   |

| 107  | DS High to R/W High                                                | t <sub>DSHRWH</sub> | 0     | —   | 0    | —   | 0    | —   | ns   |

| 108  | DS High to Data High Impedance                                     | t <sub>DSHDZ</sub>  | _     | 45  | —    | 40  | —    | 30  | ns   |

| 108A | $\overline{\text{DS}}$ High to Data-Out Hold Time (see Note)       | t <sub>DSHDH</sub>  | 0     |     | 0    |     | 0    |     | ns   |

| 109A | Data Out Valid to DTACK Low                                        | t <sub>DOVDKL</sub> | 15    | _   | 15   | _   | 10   | _   | ns   |

NOTE: If  $\overline{AS}$  is negated before  $\overline{DS}$ , the data bus could be three-stated (spec 126) before  $\overline{DS}$  is negated.

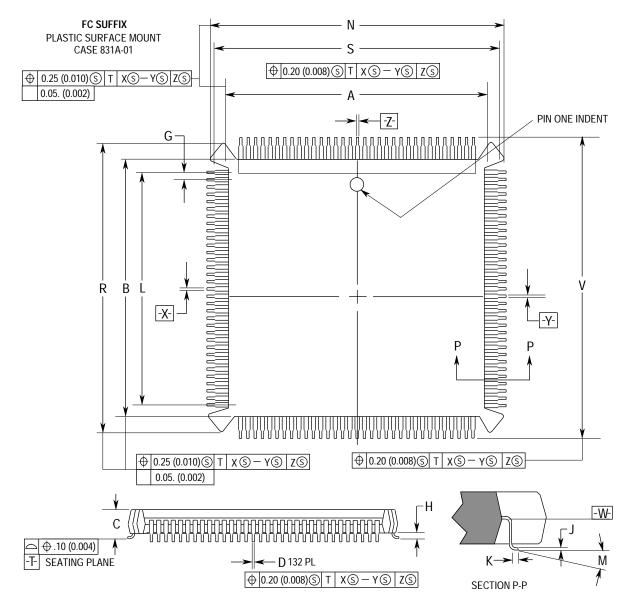

## 7.2.2 Plastic Surface Mount (PQFP)

|     | MILLIN | IETERS | INCHES |       |  |  |

|-----|--------|--------|--------|-------|--|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |  |

| Α   | 24.06  | 24.20  | 0.947  | 0.953 |  |  |

| В   | 24.06  | 24.20  | 0.947  | 0.953 |  |  |

| С   | 4.07   | 4.57   | 0.160  | 0.180 |  |  |

| D   | 0.21   | 0.30   | 0.008  | 0.012 |  |  |

| G   | 0.64   | BSC    | 0.025  | 5 BSC |  |  |

| Н   | 0.51   | 1.01   | 0.020  | 0.040 |  |  |

| ſ   | 0.16   | 0.20   | 0.006  | 0.008 |  |  |

| Κ   | 0.51   | 0.76   | 0.020  | 0.030 |  |  |

| Μ   | 0°     | 8°     | 0°     | 8°    |  |  |

| Ν   | 27.88  | 28.01  | 1.097  | 1.103 |  |  |

| R   | 27.88  | 28.01  | 1.097  | 1.103 |  |  |

| S   | 27.31  | 27.55  | 1.075  | 1.085 |  |  |

| V   | 27.31  | 27.55  | 1.075  | 1.085 |  |  |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCHES

- 3. DIM A, B, N, AND R DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION FOR DIMENSIONS A AND B IS 0.25 (0.010). FOR DIMENSIONS N AND R IS 0.18 (0.007).

- 0.25 (0.010), FOR DIMENSIONS N AND R IS 0.18 (0.007).

4. DATUM PLANE -W- IS LOCATED AT THE UNDERSIDE OF LEADS WHERE LEADS EXIT PACKAGE BODY.

- DATUMS X-Y AND Z TO BE DETERMINED WHERE CENTER LEADS EXIT PACKAGE BODY AT DATUM -W-.

- 6. DIM S AND V TO BE DETERMINED AT SEATING PLANE, DATUM -T-.

- 7. DIM A, B, N AND R TO BE DETERMINED AT DATUM PLANE -W-.

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

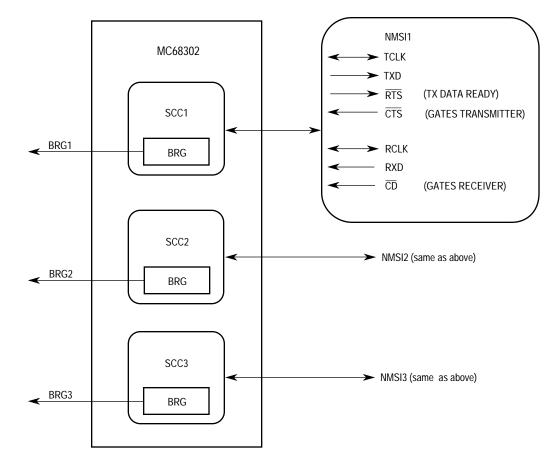

NMSI — Nonmultiplexed serial interface (also called the modem I/F).

### Figure D-21. NMSI Pin Definitions

The other three physical interfaces, PCM highway, IDL, and GCI, are called multiplexed interfaces since they allow data from one, two, or all three SCCs to be time multiplexed together on the same pins. If a multiplexed interface is chosen, the first SCC to use that interface must be SCC1, since the three multiplexed modes share pins with SCC1 (see Figure D-22). After choosing a multiplexed mode, you can decide independently whether SCC2 and SCC3 should be part of the multiplexed interface or whether they should have their own set of NMSI pins.

If you are working in ISDN, transparent mode can be quite useful in sending and receiving transparent data over the 2B + D interface. IDL and GCI allow the SCCs to transmit and receive data on the two 64 kbps B channels and on the one 16 kbps D channel in basic rate ISDN. If you are not interfacing to a 2B + D ISDN environment, you can probably rule out using IDL and GCI.

Product.

#### NOF3-NOF0—Number of Flags

Minimum number of flags between frames or before frames specifies the number of flags (0-15) to be inserted between frames or before a frame is transmitted.

C32—CRC16/CRC32

- 0 = 16-bit CRC.

- 1 = 32-bit CRC.

FSE—Flag Sharing Enable

- 0 = Normal operation.

- 1 = Transmits a single shared flag between back-to-back frames if NOF3-NOF2 = 0. Other values of NOF3-NOF2 are decremented by 1.

- BIT 9—Reserved for future use

- 0 = No retransmission.

- 1 = Retransmit enabled.

FLG—Transmit Flags/Idles between Frames and Control the RTS Pin

- 0 = Send ones between frames;  $\overline{\text{RTS}}$  negated between frames.

- 1 = Send flags between frames; RTS is always asserted.

- ENC—Data Encoding Format

- 0 = Non-return to zero (NRZ).

- 1 = Non-return to zero inverted (NRZI).

- DIAG1, DIAG0—Diagnostic Mode

- 00 = Normal operation.

- 01 = Loopback mode.

- 10 = Automatic echo.

- 11 = Software operation.

### ENR—Enable Receiver

- 0 = Receiver is disabled.

- 1 = Receiver is enabled.

- ENT—Enable Transmitter

- 0 = Transmitter is disabled.

- 1 = Transmitter is enabled.

### MODE1, MODE0—Channel Mode

- 00 = HDLC.

- 01 = Asynchronous (UART and DDCMP).

- 10 = Synchronous DDCMP and V.110.

- 11 = BISYNC and Promiscuous (Transparent).

RTE—Retransmit Enable

**E.2.1.1 COMMUNICATIONS PROCESSOR (CP) REGISTERS.** The CP has one set of three registers that configure the operation of the serial interface for all three SCCs. These registers are discussed in the next three subsections.

**E.2.1.1.1 Command Register (CR).** The command register is an 8-bit register located at offset \$860 (on D15-D8 of a 16-bit data bus). This register is used to issue commands to the CP. The user should set the FLG bit when a command is written to the command register. The CP clears the FLG bit during command processing to indicate that it is ready for the next command.

| 7   | 6   | 5   | 4      | 3 | 2     | 1    | 0   |  |

|-----|-----|-----|--------|---|-------|------|-----|--|

| RST | GCI | OPC | OPCODE |   | CH. I | NUM. | FLG |  |

RST—Software Reset Command (set by the user and cleared by the CP)

- 0 = No software reset command issued or cleared by CP during software reset sequence.

- 1 = Software reset command (FLG bit should also be set if it is not already set).

GCI—GCI Commands

- 0 = Normal operation.

- 1 = The OPCODE bits are used for GCI commands (user should set CH. NUM. to 10 and FLG to 1).

OPCODE—Command Opcode

- 00 = STOP TRANSMIT Command.

- 01 = RESTART TRANSMIT Command.

- 10 = ENTER HUNT MODE Command.

- 11 = Reset receiver BCS generator (used only in BISYNC mode).

BIT 3—Reserved (should be set to zero by the user when the command register is written)

CH. NUM.—Channel Number

- 00 = SCC1.

- 01 = SCC2.

- 10 = SCC3.

- 11 = Reserved.

FLG—Command Semaphore Flag (set by the user and cleared by the CP upon command completion)

- 0 = CP is ready to receive a new command (should be checked before issuing the next command to the CP).

- 1 = Command register contains a command to be executed or one that is currently being executed.

# INDEX

#### Α

Address AS 3-42 Decode Conflict 2-13 Decode Conflict 3-44, 3-52, 3-53 Error 2-9 Mode 2-3 Space 2-6 AS 2-11, 3-14, 3-42, 3-53, 3-59 Asynchronous Baud Rate 4-26 Automatic echo 4-30 AVEC 2-8, 2-11, 3-18, 3-22, 3-55, 5-12

#### В

Base Address Register (BAR) 2-12 **Basic Rate ISDN** 1-6 Baud Rate Generator 4-25, 5-19 **BCLM 3-56** BCLR 3-18, 3-51, 3-54, 3-55, 3-58, 4-5, 5-10 BCLR See Interrupt BCLR See Signals BERR 2-13, 3-44, 3-46, 3-52, 3-53, 3-59, 3-60, 5-6 Channel Number 3-67 BERR See Signals BG 3-54, 3-56, 3-58, 3-59, 5-11 BGACK 3-56, 3-59, 4-4, 5-11 **BISYNC** 4-91 **BDLE** 4-91 BISYNC 4-91 Carrier Detect Lost 4-92 Clear-To-Send Lost 4-92 Control Characters 4-89, 4-102 CRC Error 4-93 **DLE** 4-85 **DLE-DLE** 4-87 DLE-SYNC 4-87 **DSR** 4-88

Event Register 4-96, 4-98, 4-100 **EXSYN** 4-93 **FIFO** 4-92 Frames 4-85 Mask Register 4-101 Memory Map 4-87 **Overrun Error** 4-92 Parity Error 4-92 Programming the BISYNC 4-101 **RESET BCS CALCULATION Command** 4-101 **RESTART TRANSMIT Command 4-92 RTS** 4-95 **Rx BD 4-95 SCCE** 4-100 SCCM 4-101 SYN1-SYN2 4-87 **SYNCs** 4-85 Transmitter Underrun 4-92 Tx BD 4-97 **BISYNC** Controller 4-84 BISYNC MODE Register 4-93 Block Check Sequence 4-94 BR 3-54, 3-56, 3-58, 3-59, 5-11 Buffer 4-36 **BDs** 4-34 Buffer Descriptor 4-32 Circular Queue 4-32 Descriptors 2-14, 3-66 RBD TBD Transmit BDs 4-34 Buffer Descriptor 4-32 Bus Arbiter 3-58 Arbitration 3-14, 3-56, 5-11 Bandwidth 3-5, 3-66 Cycle 3-12 Cycles 3-2, 3-59 Error 2-9, 2-11, 2-13

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

IRQ1 3-17, 5-12, See Interrupt, See Signals IRQ6 3-17, See Interrupt, See Signals IRQ7 3-17, 3-19, See Interrupt, See Signals ISDN 5-14, Terminal Adaptor 4-11 ISR 4-39

#### L

L1SY0 4-17 LAPB 4-67 LAPD 4-67 Loopback Control 4-20 Loopback Mode 4-29, 4-137 External Loopback 4-30 Internal Loopback 4-20 Loopback Control 4-20 Lowest Power Mode 3-62 RESET 3-62 with External Clock 3-62 Low-Power 4-43 Low-Power 4-43 Low-Power Mode 3-61 LPEN 3-63 LPREC 3-64

#### Μ

Main Controller 4-1 MAX\_IDL 4-47 MC145474 4-11 MC68000/MC68008 Modes 2-1 Microcode 3-34 Mode Dedicated 2-11 Normal 2-11 Modem Signals 4-19 Monitor Channel Protocol 4-141 MOVE 2-19, See Instructions MRBLR 4-36 Multiplexed Interfaces 4-8

#### Ν

NC1 5-23 NC1 See Signals Nested Interrupt 3-19 NMSI 4-7, 4-19, 5-14 BRG1 5-18 CD1 5-17 CTS1 5-17 Modem Signals 4-19 NMSI1 5-15 NMSI2 5-18 NMSI3 5-19 RTS1 5-17 SIMODE 4-19 Normal Operation 4-28

## 0

One-Clock-Prior Mode 4-17 Output Delays 4-30

#### Ρ

Parallel I/O Port **DREQ** 3-31 IMR 3-32 PB11 3-31, 3-32 PB8 3-32, 3-66 Port A 3-29, 5-18, 5-19, 5-20 **Control Register 3-29** Data Direction Register (PADDR) 3-30 Port B 3-29, 5-21, 5-22 **Control Register 3-31** Data Direction Register (PBDDR) 3-31 Parameter RAM 3-34 Parity Error 4-61 PB11 3-19, 3-21, 3-31, 3-32, See DRAM Refresh, See Interrupt, See Parallel I/O Port, See Signals PB8 3-32, 3-66 **PCM** 4-7 PCM Channel 4-17 PCM Highway 5-14, 5-15 Envelope Mode 4-17 L1SY0 4-17 **One-Clock-Prior Mode 4-17** PCM Channel 4-17 PCM Highway Mode 4-16 **RTS** 4-18 **SIMODE 4-19** Time Slots 4-18 Pending Interrupt 5-10 Performance 4-23 Pin Assignments 7-1

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com