# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | M68000                                                                 |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                                       |

| Speed                           | 16MHz                                                                  |

| Co-Processors/DSP               | Communications; RISC CPM                                               |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 5.0V                                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 132-BQFP Bumpered                                                      |

| Supplier Device Package         | 132-PQFP (46x46)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68302eh16cr2 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

| 4.5.15.2            | Rate Adaption of 48- and 56-kbps User Rates to 64 kbps | 4-116          |

| 4.5.15.3            | Adaption for Asynchronous Rates up to 19.2 kbps        | 4-117          |

| 4.5.15.4            | V.110 Controller Overview.                             | 4-117          |

| 4.5.15.5            | V.110 Programming Model                                | 4-118          |

| 4.5.15.6            | Error-Handling Procedure                               |                |

| 4.5.15.7            | V.110 Receive Buffer Descriptor (Rx BD)                | 4-118          |

| 4.5.15.8            | V.110 Transmit Buffer Descriptor (Tx BD)               | 4-120          |

| 4.5.15.9            | V.110 Event Register                                   | 4-121          |

| 4.5.15.10           | V.110 Mask Register                                    | 4-122          |

| 4.5.16              | Transparent Controller                                 | 4-122          |

| 4.5.16.1            | Transparent Channel Buffer Transmission Processing     | 4-123          |

| 4.5.16.2            | Transparent Channel Buffer Reception Processing        | 4-124          |

| 4.5.16.3            | Transparent Memory Map                                 | 4-125          |

| 4.5.16.4            | Transparent Commands                                   | 4-126          |

| 4.5.16.5            | Transparent Synchronization                            | 4-126          |

| 4.5.16.6            | Transparent Error-Handling Procedure                   |                |

| 4.5.16.7            | Transparent Mode Register                              |                |

| 4.5.16.8            | Transparent Receive Buffer Descriptor (RxBD)           | 4-130          |

| 4.5.16.9            | Transparent Transmit Buffer Descriptor (Tx BD)         | 4-131          |

| 4.5.16.10           | Transparent Event Register                             | 4-133          |

| 4.5.16.11           | Transparent Mask Register                              | 4-134          |

| 4.6                 | Serial Communication Port (SCP)                        | 4-134          |

| 4.6.1               | SCP Programming Model                                  | 4-136          |

| 4.6.2               | SCP Transmit/Receive Buffer Descriptor                 | 4-137          |

| 4.6.3               | SCP Transmit/Receive Processing                        | 4-137          |

| 4.7                 | Serial Management Controllers (SMCs)                   | 4-138          |

| 4.7.1               | Overview                                               |                |

| 4.7.1.1             | Using IDL with the SMCs                                | 4-138          |

| 4.7.1.2             | Using GCI with the SMCs                                | 4-138          |

| 4.7.2               | SMC Programming Model                                  | 4-139          |

| 4.7.3               | SMC Commands                                           |                |

| 4.7.4               | SMC Memory Structure and Buffers Descriptors           | 4-140          |

| 4.7.4.1             | SMC1 Receive Buffer Descriptor                         | 4-141          |

| 4.7.4.2             | SMC1 Transmit Buffer Descriptor                        | 4-142          |

| 4.7.4.3             | SMC2 Receive Buffer Descriptor                         | 4-142          |

| 4.7.4.4             | SMC2 Transmit Buffer Descriptor                        | 4-143          |

| 4.7.5               | SMC Interrupt Requests                                 | 4-143          |

### Section 5 Signal Description

| 5.1 | Functional Groups         | 5-1 |

|-----|---------------------------|-----|

| 5.2 | Power Pins                |     |

| 5.3 | Clocks                    | 5-4 |

| 5.4 | System Control            | 5-5 |

| 5.5 | Address Bus Pins (A23–A1) |     |

| Paragraph<br>Number | Title                                                                               | Page<br>Number |

|---------------------|-------------------------------------------------------------------------------------|----------------|

| D.3.2               | MC68302 Buffer Processing                                                           | D-8            |

| D.3.3               | New Pointers                                                                        | D-9            |

| D.3.4               | Initial Conditions                                                                  | D-10           |

| D.3.5               | Transmit Algorithm                                                                  | D-10           |

| D.3.6               | Interrupt Routine                                                                   | D-10           |

| D.3.7               | Final Comments                                                                      | D-11           |

| D.3.8               | HDLC Code Listing                                                                   |                |

| D.4                 | Configuring A Uart on the MC68302                                                   |                |

| D.4.1               | Purpose of the Code                                                                 |                |

| D.4.2               | Organization of Buffers                                                             |                |

| D.4.3               | Assumptions about the System                                                        |                |

| D.4.4               | UART Features Not Discussed                                                         | D-19           |

| D.4.5               | UART Code Listing                                                                   |                |

| D.5                 | Independent DMA in the MC68302                                                      | D-23           |

| D.5.1               | IDMA Overview                                                                       |                |

| D.5.2               | IDMA Software Initialization                                                        | D-24           |

| D.5.3               | IDMA Bus Arbitration Signals                                                        | D-24           |

| D.5.4               | Triggering External IDMA Transfers                                                  |                |

| D.5.5               | Performing Internally Generated IDMA Transfers                                      | D-24           |

| D.5.6               | External Cycles Examples                                                            | D-26           |

| D.5.7               | Internal Interrupt Sequence                                                         | D-29           |

| D.5.8               | Final Notes                                                                         | D-30           |

| D.6                 | MC68302 Multiprotocol Controller Tied to IDL Bus Forms and ISDN Voice/data Terminal | D-30           |

| D.6.1               | M68000 Core                                                                         |                |

| D.6.2               | Communications Processor                                                            |                |

| D.6.3               | System Integration Block                                                            |                |

| D.6.4               | IDL Bus                                                                             |                |

| D.6.5               | IDL Bus Specification                                                               |                |

| D.6.6               | IMP/IDL Interconnection                                                             |                |

| D.6.7               | Serial Interface Configuration                                                      |                |

| D.6.8               | SCC Configuration                                                                   |                |

| D.6.9               | Parallel I/O Port A Configuration                                                   |                |

| D.6.10              | SCP Bus                                                                             |                |

| D.6.11              | SCP Configuration                                                                   |                |

| D.6.12              | SCP Data Transactions                                                               |                |

| D.6.13              | Additional IMP To S/T Chip Connections                                              |                |

| D.6.14              | Initialization of the MC145475                                                      |                |

| D.6.15              | MC145554 CODEC Filter                                                               |                |

| D.7                 | Interfacing a Master MC68302 to One or More Slave MC68302s                          |                |

| D.7.1               | Synchronous vs. Asynchronous Accesses                                               |                |

| D.7.2               | Clocking                                                                            |                |

| D.7.3               | Programming the Base Address Registers (BARs)                                       |                |

| D.7.4               | Dealing with Interrupts                                                             |                |

| D.7.5               | Arbitration                                                                         |                |

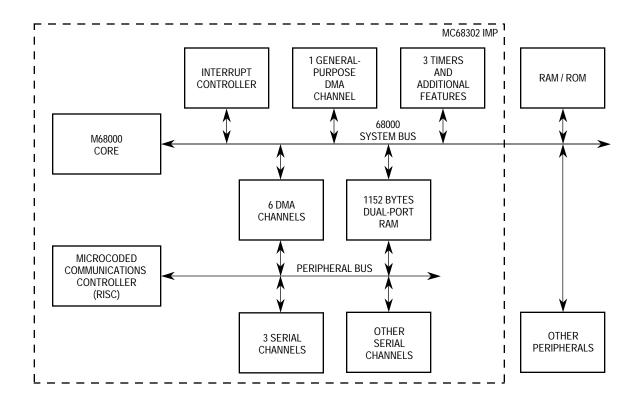

The use of a unique arbitration scheme and synchronous transfers between the microprocessor and dual-port RAM gives zero wait-state operation to the M68000 microprocessor core. The dual-port RAM can be accessed by the CP main controller (RISC) once every clock cycle for either read or write operations. When the M68000 core accesses the dualport RAM, each access is pipelined along with the CP accesses so that data is read or written without conflict. The net effect is the loss of a single memory access by the CP main controller per M68000 core access.

The buffer memory structure of the MC68302 can be configured to closely match I/O channel requirements by careful selection of buffer size and buffer linking. The interrupt structure is also programmable so that the on-chip M68000 processor can be off-loaded from the peripheral bit-handling functions to perform higher layer application software or protocol processing.

# **1.4 NMSI COMMUNICATIONS-ORIENTED ENVIRONMENT**

When the interface to equipment or proprietary networks requires the use of standard control and data signals, the MC68302 can be programmed into the nonmultiplexed serial interface (NMSI) mode. This mode, which is available for one, two, or all three SCC ports, can be selected while the other ports use one of the multiplexed interface modes (IDL, GCI, or PCM highway).

identical. When any SCC, SCP, or SMC channel buffer descriptors or parameters are not used, their parameter RAM area can be used for additional memory. For detailed information about the use of the buffer descriptors and protocol parameters in a specific protocol, see 4.5 Serial Communication Controllers (SCCs). Base + 67E contains the MC68302 revision number. Revision A parts (mask 1B14M) correspond to the value \$0001. Revision B parts (mask 2B14M and 3B14M which are described in this manual) correspond to the value \$0002. Revision C and D parts have revision number \$0003.

| Address    | Width  | Block | Description                  |

|------------|--------|-------|------------------------------|

| Base + 400 | 4 Word | SCC1  | Rx BD 0                      |

| Base + 408 | 4 Word | SCC1  | Rx BD 1                      |

| Base + 410 | 4 Word | SCC1  | Rx BD 2                      |

| Base + 418 | 4 Word | SCC1  | Rx BD 3                      |

| Base + 420 | 4 Word | SCC1  | Rx BD 4                      |

| Base + 428 | 4 Word | SCC1  | Rx BD 5                      |

| Base + 430 | 4 Word | SCC1  | Rx BD 6                      |

| Base + 438 | 4 Word | SCC1  | Rx BD 7                      |

| Base + 440 | 4 Word | SCC1  | Tx BD 0                      |

| Base + 448 | 4 Word | SCC1  | Tx BD 1                      |

| Base + 450 | 4 Word | SCC1  | Tx BD 2                      |

| Base + 458 | 4 Word | SCC1  | Tx BD 3                      |

| Base + 460 | 4 Word | SCC1  | Tx BD 4                      |

| Base + 468 | 4 Word | SCC1  | Tx BD 5                      |

| Base + 470 | 4 Word | SCC1  | Tx BD 6                      |

| Base + 478 | 4 Word | SCC1  | Tx BD 7                      |

| Base + 480 |        | SCC1  |                              |

| •          |        |       |                              |

| •          |        |       | Specific Protocol Parameters |

| •          |        | 0004  |                              |

| Base + 4BF |        | SCC1  |                              |

| Base + 4C0 |        |       |                              |

| •          |        |       | Reserved                     |

| •          |        |       | (Not Implemented)            |

|            |        |       |                              |

| Base + 4FF |        |       |                              |

| Base + 500 | 4 Word | SCC2  | Rx BD 0                      |

| Base + 508 | 4 Word | SCC2  | Rx BD 1                      |

| Base + 510 | 4 Word | SCC2  | Rx BD 2                      |

| Base + 518 | 4 Word | SCC2  | Rx BD 3                      |

| Base + 520 | 4 Word | SCC2  | Rx BD 4                      |

| Base + 528 | 4 Word | SCC2  | Rx BD 5                      |

| Base + 530 | 4 Word | SCC2  | Rx BD 6                      |

| Base + 538 | 4 Word | SCC2  | Rx BD 7                      |

| Base + 540 | 4 Word | SCC2  | Tx BD 0                      |

| Base + 548 | 4 Word | SCC2  | Tx BD 1                      |

| Base + 550 | 4 Word | SCC2  | Tx BD 2                      |

| Base + 558 | 4 Word | SCC2  | Tx BD 3                      |

| Base + 560 | 4 Word | SCC2  | Tx BD 4                      |

| Base + 568 | 4 Word | SCC2  | Tx BD 5                      |

| Base + 570 | 4 Word | SCC2  | Tx BD 6/DRAM Refresh         |

| Base + 578 | 4 Word | SCC2  | Tx BD 7/DRAM Refresh         |

#### Table 2-8. Parameter RAM

NP

| Table 2-3. Internal Registers                                                                                                                                                                                                                  |                                                                                                                                        |                                                                                   |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| Base + 840<br>Base + 842<br>Base + 844<br>Base + 846<br>Base + 848<br>! Base + 849<br>Base + 844<br>Base + 84C<br>Base + 84C<br>Base + 84C<br>Base + 850<br>Base + 852<br>Base + 854<br>Base + 856<br>Base + 858<br>! Base + 859<br>Base + 85A | TMR1<br>TRR1<br>TCR1<br>TCN1<br>RES<br>TER1<br>WRR<br>WCN<br>RES<br>TMR2<br>TRR2<br>TCR2<br>TCR2<br>TCR2<br>TCR2<br>RES<br>TER2<br>RES | 16<br>16<br>16<br>16<br>8<br>8<br>16<br>16<br>16<br>16<br>16<br>8<br>8<br>8<br>16 | Timer<br>Timer<br>Timer<br>Timer<br>Timer<br>WD<br>WD<br>Timer<br>Timer<br>Timer<br>Timer<br>Timer<br>Timer<br>Timer<br>Timer | Timer Unit 1 Mode Register<br>Timer Unit 1 Reference Register<br>Timer Unit 1 Capture Register<br>Timer Unit 1 Counter<br>Reserved<br>Timer Unit 1 Event Register<br>Watchdog Reference Register<br>Watchdog Counter<br>Reserved<br>Timer Unit 2 Mode Register<br>Timer Unit 2 Reference Register<br>Timer Unit 2 Capture Register<br>Timer Unit 2 Counter<br>Reserved<br>Timer Unit 2 Event Register<br>Reserved | 0000<br>FFFF<br>0000<br>0000<br>FFFF<br>0000<br>0000<br>FFFF<br>0000<br>0000<br>0000 |  |  |  |  |

| Base + 85C<br>Base + 85E                                                                                                                                                                                                                       | RES                                                                                                                                    | 16<br>16                                                                          | Timer<br>Timer                                                                                                                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                      |  |  |  |  |

| Base + 860                                                                                                                                                                                                                                     | CR                                                                                                                                     | 8                                                                                 | СР                                                                                                                            | Command Register                                                                                                                                                                                                                                                                                                                                                                                                  | 00                                                                                   |  |  |  |  |

| Base + 861<br>•<br>Base + 87F                                                                                                                                                                                                                  |                                                                                                                                        |                                                                                   |                                                                                                                               | Reserved<br>(Not Implemented)                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                      |  |  |  |  |

| Base + 880<br>Base + 882<br>Base + 884<br>Base + 886<br>! Base + 888<br>Base + 889<br>Base + 888<br>Base + 88B<br>Base + 88C<br>Base + 88D<br>Base + 88E                                                                                       | RES<br>SCON1<br>SCM1<br>DSR1<br>SCCE1<br>RES<br>SCCM1<br>RES<br>SCCS1<br>RES<br>RES                                                    | 16<br>16<br>16<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>16                 | SCC1<br>SCC1<br>SCC1<br>SCC1<br>SCC1<br>SCC1<br>SCC1<br>SCC1                                                                  | Reserved<br>SCC1 Configuration Register<br>SCC1 Mode Register<br>SCC1 Data Sync. Register<br>SCC1 Event Register<br>Reserved<br>SCC1 Mask Register<br>Reserved<br>SCC1 Status Register<br>Reserved<br>Reserved                                                                                                                                                                                                    | 0004<br>0000<br>7E7E<br>00<br>00<br>00                                               |  |  |  |  |

| Base + 890<br>Base + 892<br>Base + 894<br>Base + 896<br>! Base + 898<br>Base + 899<br>Base + 899<br>Base + 89B<br>Base + 89C<br>Base + 89D<br>Base + 89E                                                                                       | RES<br>SCON2<br>SCM2<br>DSR2<br>SCCE2<br>RES<br>SCCM2<br>RES<br>SCCS2<br>RES<br>RES                                                    | 16<br>16<br>16<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>16                 | SCC2<br>SCC2<br>SCC2<br>SCC2<br>SCC2<br>SCC2<br>SCC2<br>SCC2                                                                  | Reserved<br>SCC2 Configuration Register<br>SCC2 Mode Register<br>SCC2 Data Sync. Register<br>SCC2 Event Register<br>Reserved<br>SCC2 Mask Register<br>Reserved<br>SCC2 Status Register<br>Reserved                                                                                                                                                                                                                | 0004<br>0000<br>7E7E<br>00<br>00<br>00                                               |  |  |  |  |

### Table 2-9. Internal Registers

now receives as its input, given that some of its pins have been reassigned, is shown in Table 3-6. If an input pin to a channel (for example  $\overline{CD2}$  or  $\overline{CTS2}$ ) is used as a general-purpose I/O pin, then the input to the peripheral is automatically connected internally to V<sub>DD</sub> or GND, based on the pin's function. This does not affect the operation of the port pins in their general-purpose I/O function.

# NOTE

If the  $\overline{\text{DREQ}}/\text{PA13}$  pin is selected to be PA13, then  $\overline{\text{DREQ}}$  is tied low. If the IDMA is programmed for external requests, then it always recognizes an external request, and the entire block will be transferred in one burst.

| PACNT Bit = 1<br>Pin Function | PACNT Bit = 0<br>Pin Function | Input to<br>SCC2/SCC3/IDMA |

|-------------------------------|-------------------------------|----------------------------|

| RXD2                          | PAO                           | GND                        |

| TXD2                          | PA1                           | —                          |

| RCLK2                         | PA2                           | GND                        |

| TCLK2                         | PA3                           | RCLK2 #                    |

| CTS2                          | PA4                           | GND                        |

| RTS2                          | PA5                           | —                          |

| CD2                           | PA6                           | GND                        |

| SDS2/BRG2                     | PA7                           | —                          |

| RXD3                          | PA8                           | GND                        |

| TXD3                          | PA9                           | —                          |

| RCLK3                         | PA10                          | GND                        |

| TCLK3                         | PA11                          | RCLK3 #                    |

| BRG3                          | PA12                          |                            |

| DREQ                          | PA13                          | GND                        |

| DACK                          | PA14                          | _                          |

| DONE                          | PA15                          | V <sub>DD</sub>            |

| Table 3-6. | Port A Pin | Functions |

|------------|------------|-----------|

|            |            |           |

# Allows a single external clock source on the RCLK pin to clock both the SCC receiver and transmitter.

# 3.3.2 Port B

Port B has 12 pins. PB7–PB0 may be configured as general-purpose I/O pins or as dedicated peripheral interface pins; whereas, PB11–PB8 are always maintained as four generalpurpose pins, each with interrupt capability.

# 3.3.2.1 PB7-PB0

Each port B pin may be configured as a general-purpose I/O pin or as a dedicated peripheral interface pin. PB7–PB0 functions exactly like PA15–PA0, except that PB7–PB0 is controlled by the port B control register (PBCNT), the port B data direction register (PBDDR), and the port B data register (PBDAT), and PB7 is configured as an open-drain output (WDOG) upon total system reset.

- 2. BG will be an input to the IDMA and SDMA from the external M68000 bus, rather than being an output from the MC68302. When BG is sampled as low by the MC68302, it waits for AS, BERR, HALT, and BGACK to be negated, and then asserts BGACK and performs one or more bus cycles. See Section 6 for timing diagrams.

- 3. BCLR will be an input to the IDMA, but will remain an output from the SDMA.

- 4. The interrupt controller will output its interrupt request lines (IPL0, IPL1, IPL2) normally sent to the M68000 core on pins IOUT0, IOUT1, and IOUT2, respectively. AVEC, RMC, and CS0, which share pins with IOUT0, IOUT1, and IOUT2, respectively, are not available in this mode.

DISCPU should remain continuously high during disable CPU mode operation. Although the  $\overline{CS0}$  pin is not available as an output from the device in disable CPU mode, it may be enabled to provide  $\overline{DTACK}$  generation. In disable CPU mode, BR0 is initially \$C000.

Accesses by an external master to the MC68302 RAM and registers may be asynchronous or synchronous to the MC68302 clock. (This feature is actually available regardless of disable CPU mode). See the SAM and EMWS bits in the SCR for details.

In disable CPU mode, the interrupt controller may be programmed to generate or not generate interrupt vectors during interrupt acknowledge cycles. When multiple MC68302 devices share a single M68000 bus, vector generation at level 4 should be prevented on all but one MC68302. When using disable CPU mode to implement an interface, such as between the MC68020 and a single MC68302, vector generation can be enabled. For this purpose, the VGE bit is defined.

VGE—Vector Generation Enable

- 0 = In disable CPU mode, the MC68302 will not output interrupt vectors during interrupt acknowledge cycles.

- 1 = In disable CPU mode, the MC68302 will output interrupt vectors for internal level 4 interrupts (and for levels 1, 6, and/or 7 as enabled in the interrupt controller) during interrupt acknowledge cycles.

# NOTE

Do not use the function code value "111" during external accesses to the IMP, except during interrupt acknowledge cycles.

In disable CPU mode, the low-power modes will be entered immediately upon the setting of the LPEN bit in the SCR by an external master. In this case, low-power mode will continue until the LPEN bit is cleared. Users may wish to use a low-power mode in conjunction with disable CPU mode to save power consumed by the disabled M68000 core.

All MC68302 functionality not expressly mentioned in this section is retained in disable CPU mode and operates identically as before.

# NOTE

Even without the use of the disable CPU logic, another processor can be granted access to the IMP on-chip peripherals by re-

tools are 1) the ready bit in the transmit buffer descriptor, 2) the ENT bit, 3) the STOP TRANSMIT command, 4) the RESTART TRANSMIT command, and 5) the FRZ bit in the SCM (UART mode only).

#### ENR—Enable Receiver

When ENR is set, the receiver is enabled. When it is cleared, the receiver is disabled, and any data in the receive FIFO is lost. If ENR is cleared during data reception, the receiver aborts the current character. ENR may be set or cleared regardless of whether serial clocks are present. To restart reception, the ENTER HUNT MODE command should be issued before ENR is set again.

#### ENT—Enable Transmitter

When ENT is set, the transmitter is enabled; when ENT is cleared, the transmitter is disabled. If ENT is cleared, the transmitter will abort any data transmission, clear the transmit data FIFO and shift register, and force the TXD line high (idle). Data already in the transmit shift register will not be transmitted. ENT may be set or cleared regardless of whether serial clocks are present.

The STOP TRANSMIT command additionally aborts the current frame and would normally be given to the channel before clearing ENT. The command does not clear ENT automatically. In a similar manner, to restart transmission, the user should issue the RESTART TRANSMIT command and then set ENT. The command register is described in 4.3 Command Set. The specific actions taken with each command vary somewhat according to protocol and are discussed in each protocol section.

# MODE1-MODE0-Channel Mode

- 00 = HDLC

- 01 = Asynchronous (UART and DDCMP)

- 10 = Synchronous DDCMP and V.110

- 11 = BISYNC and Promiscuous Transparent

# 4.5.4 SCC Data Synchronization Register (DSR)

Each DSR is a 16-bit, memory-mapped, read-write register. DSR specifies the pattern used in the frame synchronization procedure of the SCC in the synchronous protocols. In the UART protocol it is used to configure fractional stop bit transmission. After reset, the DSR defaults to \$7E7E (two FLAGs); thus, no additional programming is necessary for the HDLC protocol. For BISYNC, DDCMP, and V.110, the contents of the DSR should be written before the channel is enabled. Note that for the DDCMP, SYN1 must equal SYN2 must equal DSYN1 for proper operation.

| 15 8 | 7 0  |

|------|------|

| SYN2 | SYN1 |

# NOTE

The DSR register has no relationship to the RS-232 signal "data set ready," which is also abbreviated DSR.

- T2,T1—Message Type

- 00 = Data message

- 01 = Control message

- 10 = Maintenance message

- 11 = Reserved

Bits 7–6—Reserved for future use.

# CF—CRC Follow Error

The character following the CRC for this message was not one of SOH, ENQ, DLE, SYN, or IDLE. The receiver then enters hunt mode.

#### FR—Framing Error

A character with a framing error was received. The associated character may be found at the last location in this buffer. A framing error is detected by the UART controller when no stop bit is detected in the receive data string.

#### NOTE

This error can occur only on asynchronous DDCMP links.

### PR—Parity Error

A character with a parity error was received. The associated character may be found at the last location in this buffer.

## NOTE

This error can occur only on asynchronous DDCMP links.

#### CR—Rx CRC Error

A message with a CRC error was received in the header (CRC1) or data (CRC2) fields or a control message (CRC3).

# OV—Overrun

A receiver overrun occurred during message reception.

# CD—Carrier Detect Lost

The CD signal was negated during message reception. This bit is valid only when working in NMSI mode.

# Data Length

The data length is the number of octets that the DDCMP controller has written to this BD's data buffer. It is written by the CP once as the BD is closed.

# NOTE

The actual buffer size should be greater than or equal to eight (to ensure the header is received in one buffer).

the buffer, sets the overrun (OV) bit in the BD, and generates the RX interrupt (if enabled). The receiver then enters hunt mode immediately.

- 2. Carrier Detect Lost During Message Reception—When this error occurs and the channel is not programmed to control this line with software, the channel terminates reception, closes the buffer, sets the carrier detect lost (CD) bit in the BD, and generates the RX interrupt (if enabled). This error has the highest priority; the rest of the message is lost and no other errors are checked. The receiver then enters hunt mode immediately.

- 3. Busy Condition—If the RISC controller tries to use an Rx BD that is not empty, the busy condition is encountered. No data is received and the current Rx BD is left unmodified. After new buffers are provided, the user should issue the ENTER HUNT MODE command.

# 4.5.16.7 Transparent Mode Register

Each SCC mode register is a 16-bit, memory-mapped, read-write register that controls the SCC operation. The term transparent mode register refers to the protocol-specific bits (15–6) of the SCC mode register when that SCC is configured for transparent mode. The transparent mode register is cleared by reset. All undefined bits should be written with zero.

| 15 | 14    | 13    | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5 0                  |

|----|-------|-------|------|----|----|---|---|---|---|----------------------|

| _  | EXSYN | NTSYN | REVD | _  | _  | — | — | — | _ | COMMON SCC MODE BITS |

Bit 15—Reserved for future use; should be written with zero.

#### EXSYN — External Sync Mode

When this mode is selected, the receiver and transmitter expect external logic to indicate the beginning of the data field by using the  $\overline{CD1}/L1SY1$  pin, if SCC1 is used, and the  $\overline{CD2}$  and  $\overline{CD3}$  pins, respectively, if SCC2 or SCC3 is used. In this mode, there is no carrier detect function for the SCC.

When the channel is programmed to work through the serial channels physical interface (IDL or GCI) and EXSYN is set, the layer 1 logic carries out the synchronization using the L1SY1 pin. In PCM mode, the L1SY1–L1SY0 pins are used. In NMSI mode, the  $\overline{\text{CD}}$  pins (and the  $\overline{\text{CD}}$  timing) are used to synchronize the data.  $\overline{\text{CD}}$  should go low on the second valid data bit of the receive data stream.

If this bit is cleared, the receiver will look for the SYN1–SYN2 sequence in the data synchronization register to achieve synchronization, and the transmitter uses the  $\overline{\text{CTS}}$  pin according to the DIAG1–DIAG0 bits in the SCM. The receiver also uses the  $\overline{\text{CD}}$  pin according to the DIAG1–DIAG0 bits in the SCM.

#### NTSYN—No Transmit SYNC

This bit must be set for the SCC to operate in a totally transparent (promiscuous) mode.

# REVD—Reverse Data

When this bit is set, the receiver and transmitter will reverse the character bit order, transmitting the most significant bit first.

### 4.7.4.2 SMC1 Transmit Buffer Descriptor

The CP reports information about this transmit byte through the BD.

| 15 | 14 | 13 | 12 | 10 | 9  | 8  | 7 |      | 0 |

|----|----|----|----|----|----|----|---|------|---|

| R  | L  | AR |    | _  | AB | EB |   | DATA |   |

#### R—Ready

- 0 = This bit is cleared by the CP after transmission. The Tx BD is now available to the M68000 core.

- 1 = This bit is set by the M68000 core to indicate that the data byte associated with this BD is ready for transmission.

In GCI mode, when the IMP implements the monitor channel protocol, it will clear this bit after receiving an acknowledgment on the A bit. When the SMC1 data should be transmitted and this bit is cleared, the channel will retransmit the previous data until new data is provided by the M68000 core.

#### L-Last (EOM)

This bit is valid only in GCI mode when the IMP implements the monitor channel protocol. When this bit is set, the SMC1 channel will transmit the buffer's data and then the end of message (EOM) indication on the E bit.

#### AR—Abort Request

This bit is valid only in GCI mode when the IMP implements the monitor channel protocol. This bit is set by the IMP when an abort request was received on the A bit. The SMC1 transmitter will transmit EOM on the E bit.

Bits 12–10—Reserved for future use.

#### AB—Transmit A Bit Value

This bit is valid only in GCI mode when the monitor channel is in transparent mode.

#### EB—Transmit E Bit Value

This bit is valid only in GCI mode when the monitor channel is in transparent mode.

#### Data—Data Field

The data field contains the data to be transmitted by SMC1.

#### 4.7.4.3 SMC2 Receive Buffer Descriptor

In the IDL mode, this BD is identical to the SMC1 receive BD. In the GCI mode, SMC2 is used to control the C/I channel.

| 15 | 14 6     | 5   | 2 | 1 | 0 |

|----|----------|-----|---|---|---|

| E  | RESERVED | C/I |   | 0 | 0 |

#### FRZ—Freeze Activity

The FRZ pin is used to freeze the activity of selected peripherals. This is useful for system debugging purposes. Refer to 3.8 System Control for more details on which peripherals are affected. FRZ should be continuously negated during total system reset.

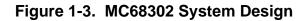

# 5.5 ADDRESS BUS PINS (A23-A1)

The address bus pins are shown in Figure 5-4.

Figure 5-4. Address Bus Pins

A23—A1 form a 24-bit address bus when combined with UDS/A0. The address bus is a bidirectional, three-state bus capable of addressing 16M bytes of data (including the IMP internal address space). It provides the address for bus operation during all cycles except CPU space cycles. In CPU space cycles, the CPU reads a peripheral device vector number.

These lines are outputs when the IMP (M68000 core, SDMA or IDMA) is the bus master and are inputs otherwise.

# 5.6 DATA BUS PINS (D15-D0)

The data bus pins are shown in Figure 5-5.

Figure 5-5. Data Bus Pins

This 16-bit, bidirectional, three-state bus is the general-purpose data path. It can transmit and accept data in either word or byte lengths. For all 16-bit IMP accesses, byte 0, the high-order byte of a word, is available on D15–D8, conforming to the standard M68000 format.

When working with an 8-bit bus (BUSW is low), the data is transferred through the low-order byte (D7–D0). The high-order byte (D15–D8) is not used for data transfer, but D8-D15 are outputs during write cycles and are not three-stated.

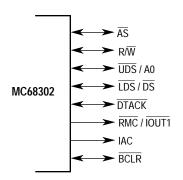

# 5.7 BUS CONTROL PINS

The bus control pins are shown in Figure 5-6.

Figure 5-6. Bus Control Pins

### Address Strobe

This bidirectional signal indicates that there is a valid address on the address bus. This line is an output when the IMP (M68000 core, SDMA or IDMA) is the bus master and is an input otherwise.

## R/W-Read/Write

This bidirectional signal defines the data bus transfer as a read or write cycle. It is an output when the IMP is the bus master and is an input otherwise.

# UDS/A0—Upper Data Strobe/Address 0

This bidirectional line controls the flow of data on the data bus. When using a 16-bit data bus, this pin functions as upper data strobe ( $\overline{\text{UDS}}$ ). When using an 8-bit data bus, this pin functions as A0. When used as A0 (i.e., the BUSW pin is low), then the pin takes on the timing of the other address pins, as opposed to the strobe timing. This line is an output when the IMP is the bus master and is an input otherwise.

# LDS/DS—Lower Data Strobe/Data Strobe

This bidirectional line controls the flow of data on the data bus. When using a 16-bit data bus, this pin functions as lower data strobe ( $\overline{LDS}$ ). When using an 8-bit data bus, this pin functions as  $\overline{DS}$ . This line is an output when the IMP (M68000 core, SDMA or IDMA) is the bus master and is an input otherwise.

# DTACK—Data Transfer Acknowledge

This bidirectional signal indicates that the data transfer has been completed. DTACK can be generated internally in the chip-select logic either for an IMP bus master or for an external bus master access to an external address within the chip-select ranges. It will also be generated internally during any access to the on-chip dual-port RAM or internal regis-

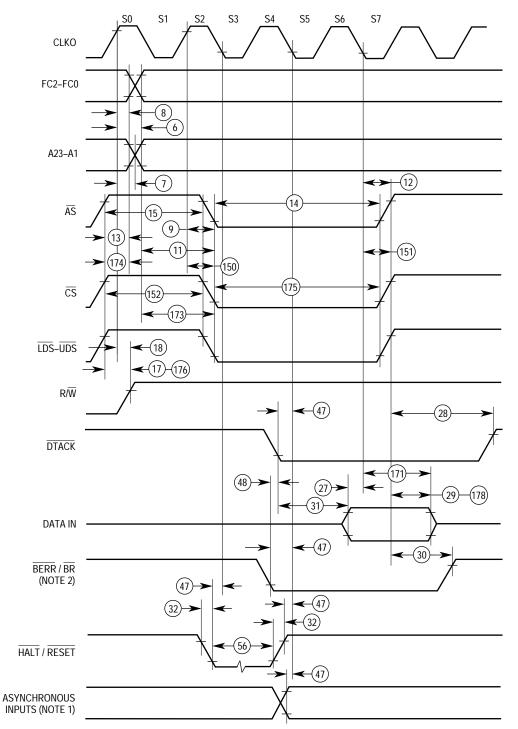

NOTES:

- Setup time for the asynchronous inputs IPL2–IPL0 guarantees their recognition at the next falling edge of the clock.

- 2. BR need fall at this time only to insure being recognized at the end of the bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is linear between 0.8 volts and 2.0 volts.

Figure 6-2. Read Cycle Timing Diagram

# 6.22 AC ELECTRICAL SPECIFICATIONS—NMSI TIMING

The NMSI mode uses two clocks, one for receive and one for transmit. Both clocks can be internal or external. When t he clock is internal, it is generated by the internal baud rate generator and it is output on TCLK or RCLK. All the timing is related to the external clock pin. The timing is specified for NMSI1. It is also valid for NMSI2 and NMSI3 (see Figure 6-24).

|      |                                                          | 16.67 MHz<br>Internal<br>Clock |      | z 16.67 MHz<br>External<br>Clock |       | 20 MHz<br>Internal<br>Clock |      | 20 MHz<br>External<br>Clock |     | 25 MHz<br>Internal<br>Clock |      | 25 MHz<br>External<br>Clock |     |      |

|------|----------------------------------------------------------|--------------------------------|------|----------------------------------|-------|-----------------------------|------|-----------------------------|-----|-----------------------------|------|-----------------------------|-----|------|

| Num. | Characteristic                                           |                                |      |                                  |       |                             |      |                             |     |                             |      |                             |     | Unit |

|      |                                                          | Min                            | Max  | Min                              | Max   | Min                         | Max  | Min                         | Max | Min                         | Max  | Min                         | Мах |      |

| 315  | RCLK1 and TCLK1 Fre-<br>quency (see Note 1)              |                                | 5.55 | _                                | 6.668 | _                           | 6.66 | —                           | 8   |                             | 8.33 | —                           | 10  | MHz  |

| 316  | RCLK1 and TCLK1 Low (see Note 4)                         | 65                             | _    | P+10                             | _     | 55                          | —    | P+10                        |     | 45                          | —    | P+10                        | _   | ns   |

| 316a | RCLK1 and TCLK1 High                                     | 65                             | —    | 55                               | _     | 55                          | —    | 45                          |     | 45                          | —    | 35                          | —   | ns   |

| 317  | RCLK1 and TCLK1 Rise/Fall<br>Time (see Note 3)           | _                              | 20   |                                  | _     | —                           | 17   | —                           |     | _                           | 14   | —                           | _   | ns   |

| 318  | TXD1 Active Delay from<br>TCLK1 Falling Edge             | 0                              | 40   | 0                                | 70    | 0                           | 30   | 0                           | 50  | 0                           | 25   | 0                           | 40  | ns   |

| 319  | RTS1 Active/Inactive Delay<br>from TCLK1 Falling Edge    | 0                              | 40   | 0                                | 100   | 0                           | 30   | 0                           | 80  | 0                           | 25   | 0                           | 65  | ns   |

| 320  | CTS1 Setup Time to TCLK1<br>Rising Edge                  | 50                             | _    | 10                               |       | 40                          | _    | 7                           | _   | 35                          | _    | 7                           |     | ns   |

| 321  | RXD1 Setup Time to RCLK1<br>Rising Edge                  | 50                             | _    | 10                               |       | 40                          |      | 7                           | _   | 35                          | _    | 7                           |     | ns   |

| 322  | RXD1 Hold Time from<br>RCLK1 Rising Edge (see<br>Note 2) | 10                             | _    | 50                               |       | 7                           | _    | 40                          |     | 7                           | _    | 35                          | _   | ns   |

| 323  | CD1 Setup Time to RCLK1<br>Rising Edge                   | 50                             | _    | 10                               |       | 40                          | _    | 7                           | _   | 35                          | _    | 7                           | _   | ns   |

#### NOTES:

- 1. The ratio CLKO/TCLK1 and CLKO/RCLK1 must be greater than or equal to 2.5/1 for external clock. The input clock to the baud rate generator may be either an internal clock or TIN1, and may be as fast as EXTAL. However, the output of the baud rate generator must provide a CLKO/TCLK1 and CLKO/RCLK1 ratio greater than or equal to 3/1. In asynchronous mode (UART), the bit rate is 1/16 of the TCLK1/RCLK1 clock rate.

- 2. Also applies to  $\overline{\text{CD}}$  hold time when  $\overline{\text{CD}}$  is used as an external sync in BISYNC or totally transparent mode.

- 3. Schmitt triggers used on input buffers.

- 4. Where P = 1/CLKO. Thus, for a 16.67-MHz CLKO rate, P = 60 ns.

C68302 Applications

\* 00700608 1000 0000 0003 0003 (wrap bit set)

| BAR    | EQU | \$0F2    |

|--------|-----|----------|

| GIMR   | EQU | \$700812 |

| IPR    | EQU | \$700814 |

| IMR    | EQU | \$700816 |

| ISR    | EQU | \$700818 |

| PACNT  | EQU | \$70081e |

| SIMODE | EQU | \$7008b4 |

| SCON3  | EQU | \$7008a2 |

| SCM3   | EQU | \$700&4  |

| SCCE3  | EQU | \$7008a8 |

| SCCM3  | EQU | \$7008aa |

|        |     |          |

#### \*SCC3 Initialization Code

ORG \$30300 MOVE.W #\$700.BAR ; BAR = 0700\* Base Address - S700000, so ALL MC68302 on-chip peripherals begin at \* address S700xxx.

MOVE.W #\$00A0, GIMR ;GIMR = 00a0#\$FFFF,IPR ;clear IPR MOVE.W MOVE.L #\$30500,\$2a0 ;SCC3 vector initialization MOVE.W #\$0300,PACNT ; PACNT = 0300\* Causes the SCC3 TXD3 and RXD3 pins to be enabled. TCLK3 and RCLK3 \* pins are left as parallel 1/0 pins. ;SIMODE = 0000 (its reset value) MOVE.W #50,SIMODE \* SCC3 is set up for NMSI (i.e. modem) operation. No multiplexed \* modes are used on the other SCCs. MOVE.W #\$00d8,SCON3 ;SCON3=00d8 for ~9600 baud at 16.67 MHz \* Baud Rate generator is used for transmit and receive. Rate is 9556bps. MOVE.W #\$171,SCM3 ;SCM3 = 0171 \* No parity. Normal UART operation. 8-bit characters. 2 Stop bits. \* The CD and CTS lines not used to enable reception and transmission, \* but do cause a status change in the SCC3 Event register. MOVE.L #\$5000000,S700640 ;Set up Tx BD 0 Status and Count MOVE.L #\$30000,\$700644 ;Set up Tx BD 0 Buffer Address MOVE.L #\$70000000,\$700648 ;Set up Tx BD 1 Status and Count MOVE.L #\$30001,\$70064c ;Set up Tx BD 1 Buffer Address \* Set up 2 Tx BDs MOVE.L #\$d0000000,\$700600 ;Set up Rx BD 0 Status and Count MOVE.L #\$30002,\$700604 ;Set up Rx BD 0 Buffer Address MOVE.L #\$f0000000,\$700608 ;Set up Rx BD 1 Status and Count MOVE.L #\$30003,\$70060c ;Set up Rx BD 1 Buffer Address \* Set up 2 Rx BDs MOVE.W #\$0,\$700680 ;clear RFCR/TFCR (Function code setup) \* Must be initialized to a value other than 7, or won't work with chip selects ;MRBLR = 0001 (one-byte receive MOVE.W #\$1,\$700682 buffers) \* This combined with the "l" bit set in the Rx BD, gives interrupts on each \* character received.

MOVE.W #\$4,\$70069c ;MAX\_IDL don't care since MRBLR =1. \* Normally set to a small value, it closes a receive buffer if a certain number

Semiconductor, Inc

reescale

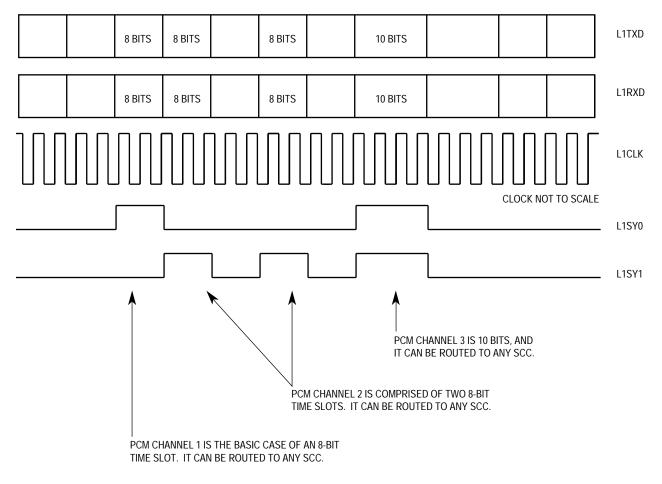

The PCM highway interface has three  $\overline{\text{RTS}}$  signals. One of these signals is asserted when an SCC wants to transmit over the PCM Highway just like in NMSI mode), and stays continuously asserted until the entire frame is transmitted (regardless of how many time slots the transmission takes). Which  $\overline{\text{RTS}}$  signal asserts depends on which SCC is transmitting; there is one  $\overline{\text{RTS}}$  signal for each SCC. Notice, however, that there is no  $\overline{\text{CTS}}$  signal, so there is nothing to hold off the transfer. If the  $\overline{\text{RTS}}$  signals are not needed, they can be ignored or reassigned as parallel I/O lines.

Figure D-29. Routing Channels in PCM Envelope Mode

What other signals are missing from PCM mode? First, there is no  $\overline{CD}$  signal for the receiver. The receiver is enabled whenever the ENR bit is set. However, you could say there is a  $\overline{CD}$  (sync) of sorts that is implemented with the L1SY1 and L1SY0 pins. Two pins are used since not only is the timing important, but also the selection of the PCM channel as well.

The way transparent mode works with a PCM highway interface is very similar to the operation of the gated clocks example discussed previously. Whether or not a time slot environment is present, PCM mode gives greater control over what intervals transparent data can be transmitted and received. However, in PCM mode, the clocks are gated by the physical interface on the MC68302 as opposed to external hardware.

**E.2.1.1 COMMUNICATIONS PROCESSOR (CP) REGISTERS.** The CP has one set of three registers that configure the operation of the serial interface for all three SCCs. These registers are discussed in the next three subsections.

**E.2.1.1.1 Command Register (CR).** The command register is an 8-bit register located at offset \$860 (on D15-D8 of a 16-bit data bus). This register is used to issue commands to the CP. The user should set the FLG bit when a command is written to the command register. The CP clears the FLG bit during command processing to indicate that it is ready for the next command.

| 7   | 6   | 5   | 4   | 3 | 2     | 1    | 0   |  |

|-----|-----|-----|-----|---|-------|------|-----|--|

| RST | GCI | OPC | ODE | — | CH. I | NUM. | FLG |  |

RST—Software Reset Command (set by the user and cleared by the CP)

- 0 = No software reset command issued or cleared by CP during software reset sequence.

- 1 = Software reset command (FLG bit should also be set if it is not already set).

GCI—GCI Commands

- 0 = Normal operation.

- 1 = The OPCODE bits are used for GCI commands (user should set CH. NUM. to 10 and FLG to 1).

OPCODE—Command Opcode

- 00 = STOP TRANSMIT Command.

- 01 = RESTART TRANSMIT Command.

- 10 = ENTER HUNT MODE Command.

- 11 = Reset receiver BCS generator (used only in BISYNC mode).

BIT 3—Reserved (should be set to zero by the user when the command register is written)

CH. NUM.—Channel Number

- 00 = SCC1.

- 01 = SCC2.

- 10 = SCC3.

- 11 = Reserved.

FLG—Command Semaphore Flag (set by the user and cleared by the CP upon command completion)

- 0 = CP is ready to receive a new command (should be checked before issuing the next command to the CP).

- 1 = Command register contains a command to be executed or one that is currently being executed.

|             |          | 1                                                      |             | -        | 1                                                      |

|-------------|----------|--------------------------------------------------------|-------------|----------|--------------------------------------------------------|

| Initialized | Offset   | Name                                                   | Initialized | Offset   | Name                                                   |

| by User     | Hex      |                                                        | by User     | Hex      |                                                        |

| Yes         | 00       | Rx BD 0 Control/Status                                 | Yes         | 40       | Tx BD 0 Control/Status                                 |

| Yes         | 02       | Rx BD 0 Data Count<br>Rx BD 0 Data Pointer (High Word) | Yes<br>Yes  | 42<br>44 | Tx BD 0 Data Count<br>Tx BD 0 Data Pointer (High Word) |

| Yes         | 06       | Rx BD 0 Data Pointer (Low Word)                        | Yes         | 46       | Tx BD 0 Data Pointer (Low Word)                        |

| Yes         | 08       | Rx BD 1 Control/Status                                 | Yes         | 48       | Tx BD 1 Control/Status                                 |

| Yes         | 0A<br>0C | Rx BD 1 Data Count<br>Rx BD 1 Data Pointer (High Word) | Yes<br>Yes  | 4A<br>4C | Tx BD 1 Data Count<br>Tx BD 1 Data Pointer (High Word) |

| Yes         | ŐĔ       | Rx BD 1 Data Pointer (Low Word)                        | Yes         | 4E       | Tx BD 1 Data Pointer (Low Word)                        |

| Yes         | 10       | Rx BD 2 Control/Status                                 | Yes         | 50       | Tx BD 2 Control/Status                                 |

| Yes         | 12<br>14 | Rx BD 2 Data Count<br>Rx BD 2 Data Pointer (High Word) | Yes<br>Yes  | 52<br>54 | Tx BD 2 Data Count<br>Tx BD 2 Data Pointer (High Word) |

| Yes         | 16       | Rx BD 2 Data Pointer (Low Word)                        | Yes         | 56       | Tx BD 2 Data Pointer (Low Word)                        |

| Yes         | 18       | Rx BD 3 Control/Status                                 | Yes         | 58       | Tx BD 3 Control/Status                                 |

| Yes         | 1A       | Rx BD 3 Data Count<br>Rx BD 3 Data Pointer (High Word) | Yes<br>Yes  | 5A       | Tx BD 3 Data Count<br>Tx BD 3 Data Pointer (High Word) |

| Yes         | 1C<br>1E | Rx BD 3 Data Pointer (Low Word)                        |             | 5C<br>5E | Tx BD 3 Data Pointer (Low Word)                        |

| Yes         | 20       | Rx BD 4 Control/Status                                 | Yes         | 60       | Tx BD 4 Control/Status                                 |

| Yes         | 22<br>24 | Rx BD 4 Data Count<br>Rx BD 4 Data Pointer (High Word) | Yes<br>Yes  | 62<br>64 | Tx BD 4 Data Count<br>Tx BD 4 Data Pointer (High Word) |

| Yes         | 26       | Rx BD 4 Data Pointer (Low Word)                        | Yes         | 66       | Tx BD 4 Data Pointer (Low Word)                        |

| Yes         | 28       | Rx BD 5 Control/Status                                 | Yes         | 68       | Tx BD 5 Control/Status                                 |

| Yes         | 2Ă<br>2C | Rx BD 5 Data Count<br>Rx BD 5 Data Pointer (High Word) | Yes<br>Yes  | 6A<br>6C | Tx BD 5 Data Count<br>Tx BD 5 Data Pointer (High Word) |

| Yes         | 2Ĕ       | Rx BD 5 Data Pointer (Low Word)                        | Yes         | 6E       | Tx BD 5 Data Pointer (Low Word)                        |

| Yes         | 30       | Rx BD 6 Control/Status                                 | Yes         | 70       | Tx BD 6 Control/Status                                 |

| Yes         | 32<br>34 | Rx BD 6 Data Count<br>Rx BD 6 Data Pointer (High Word) | Yes<br>Yes  | 72<br>74 | Tx BD 6 Data Count<br>Tx BD 6 Data Pointer (High Word) |

| Yes         | 36       | Rx BD 6 Data Pointer (Low Word)                        |             | 74<br>76 | Tx BD 6 Data Pointer (Low Word)                        |

| Yes         | 38       | Rx BD 7 Control/Status                                 | Yes         | 78       | Tx BD 7 Control/Status                                 |

| Yes         | 3A<br>3C | Rx BD 7 Data Count<br>Rx BD 7 Data Pointer (High Word) | Yes<br>Yes  | 7A<br>7C | Tx BD 7 Data Count<br>Tx BD 7 Data Pointer (High Word) |

| Yes         | 3E       | Rx BD 7 Data Pointer (Low Word)                        |             | 7E       | Tx BD 7 Data Pointer (Low Word)                        |

|             |          |                                                        |             |          |                                                        |

# Table E-1. (a)Transparent Programming ModelReceive and Transmit Buffer Descriptors for SCCx

NOTE: The offset is from the MC68302 base address + (\$400 for SCC1, \$500 for SCC2, or \$600 for SCC3)

# Table E-1 (b). Transparent Programming Model (Continued)General Parameter and Transparent Protocol-Specific RAM for SCCx

| Initialized<br>by User | Offset<br>Hex | Na                                       | Initialized by<br>User                   | Offset<br>Hex | Name     |          |

|------------------------|---------------|------------------------------------------|------------------------------------------|---------------|----------|----------|

| Yes                    | 80            | RFCR                                     | TFCR                                     |               | A2       | Reserved |

| Yes                    | 82            | MRI                                      |                                          | A4            | Reserved |          |

|                        | 84            | Rx Interr                                |                                          | A6            | Reserved |          |

|                        | 86            | Reserved                                 | Rx Internal Buffer No.                   |               | A8       | Reserved |

|                        | 88<br>8A      | Rx Internal Data P<br>Rx Internal Data P |                                          | AA            | Reserved |          |

|                        | 8C            | Rx Internal                              |                                          | AC            | Reserved |          |

|                        | 8E            | Rx T                                     |                                          | AE            | Reserved |          |

|                        | 90            | Tx Interr                                |                                          | B0            | Reserved |          |

|                        | 92            | Reserved                                 | Tx Internal Buffer No.                   |               | B2       | Reserved |

|                        | 94<br>96      | Tx Internal Data P<br>TX Internal Data F | ointer (High Word)<br>Pointer (Low Word) |               | B4       | Reserved |

|                        | 98            | Tx Internal                              |                                          | B6            | Reserved |          |

|                        | 9A            | Tx T                                     |                                          | B8            | Reserved |          |

|                        | 9C            | Rese                                     |                                          | BA            | Reserved |          |

|                        | 9E            | Rese                                     |                                          | BC            | Reserved |          |

|                        | A0            | Rese                                     |                                          | BE            | Reserved |          |

NOTE: The offset is from the MC68302 base address + (\$400 for SCC1, \$500 for SCC2, or \$600 for SCC3).