# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | M68000                                                                 |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                                       |

| Speed                           | 20MHz                                                                  |

| Co-Processors/DSP               | Communications; RISC CPM                                               |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 5.0V                                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 132-BQFP Bumpered                                                      |

| Supplier Device Package         | 132-PQFP (46x46)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68302eh20cr2 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MC68302 can also be used in applications such as board-level industrial controllers performing real-time control applications with a local control bus and an X.25 packet network connection. Such a system provides the real-time response to a demanding peripheral while permitting remote monitoring and communication through an X.25 packet network.

### **1.2 FEATURES**

The features of the IMP are as follows:

- On-Chip HCMOS MC68000/MC68008 Core Supporting a 16- or 8-Bit M68000 Family-System

- IB Including:

- -Independent Direct Memory Access (IDMA) Controller with Three Handshake Signals: DREQ, DACK, and DONE.

- -Interrupt Controller with Two Modes of Operation

- -Parallel Input/Output (I/O) Ports, Some with Interrupt Capability

- -On-Chip 1152-Byte Dual-Port RAM

- -Three Timers Including a Watchdog Timer

- -Four Programmable Chip-Select Lines with Wait-State Generator Logic

- -Programmable Address Mapping of the Dual-Port RAM and IMP Registers

- -On-Chip Clock Generator with Output Signal

- -System Control:

Bus Arbitration Logic with Low-Interrupt Latency Support System Status and Control Logic Disable CPU Logic (M68000) Hardware Watchdog Low-Power (Standby) Modes Freeze Control for Debugging **DRAM Refresh Controller**

- CP Including:

- -Main Controller (RISC Processor)

- -Three Independent Full-Duplex Serial Communications Controllers (SCCs)

- -Supporting Various Protocols:

- High-Level/Synchronous Data Link Control (HDLC/SDLC)

- Universal Asynchronous Receiver Transmitter (UART)

- Binary Synchronous Communication (BISYNC)

Synchronous/Asynchronous Digital Data Communications Message Protocol (DDCMP)

- **Transparent Modes**

- V.110 Rate Adaption

- —Six Serial DMA Channels for the Three SCCs

- -Flexible Physical Interface Accessible by SCCs Including:

- Motorola Interchip Digital Link (IDL)

- General Circuit Interface (GCI, also known as IOM<sup>3</sup>-2)

- Pulse Code Modulation (PCM) Highway Interface

<sup>&</sup>lt;sup>3.</sup> IOM is a trademark of Siemens AG

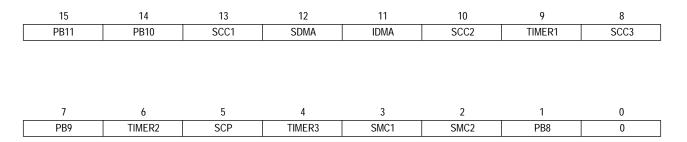

#### 3.2.5.4 Interrupt In-Service Register (ISR).

Each bit in the 16-bit ISR corresponds to an INRQ interrupt source. In a vectored interrupt environment, the interrupt controller sets the ISR bit when the vector number corresponding to the INRQ interrupt source is passed to the core during an interrupt acknowledge cycle. The user's interrupt service routine should clear this bit during the servicing of the interrupt. (If an event register exists for this peripheral, its bits should also be cleared by the user program.) To clear a bit in the ISR, the user writes a one to that bit. The user can only clear bits in this register, and bits that are written with zeros will not be affected. The ISR is cleared at reset.

This register may be read by the user to determine which INRQ interrupts are currently being processed. More than one bit in the ISR may be a one if the capability is used to allow higher priority level 4 interrupts to interrupt lower priority level 4 interrupts. See 3.2.2.3 Nested Interrupts for more details.

The user can control the extent to which level 4 interrupts may interrupt other level 4 interrupts by selectively clearing the ISR. A new INRQ interrupt will be processed if it has a higher priority than the highest priority INRQ interrupt having its ISR bit set. Thus, if an INRQ interrupt routine lowers the 3-bit mask in the M68000 core to level 3 and also clears its ISR bit at the beginning of the interrupt routine, then a lower priority INRQ interrupt it as long as the lower priority is higher than any other ISR bits that are set.

If the INRQ error vector is taken, no bit in the ISR is set. Bit 0 of the ISR is always zero.

### 3.2.6 Interrupt Handler Examples

The following examples illustrate proper interrupt handling on the IMP. Nesting of level 4 interrupts (a technique described earlier) is not implemented in the following examples.

Example 1—Timer 3 (Software Watchdog Timer) Interrupt Handler

- 1. Vector to interrupt handler.

- 2. (Handle Event)

- 3. Clear the TIMER3 bit in the ISR.

- 4. Execute RTE instruction.

Example 2— SCC1 Interrupt Handler

1. Vector to interrupt handler.

counter after reference is reached, ICLK = 01 to use the master clock, and RST = 1 to enabled the timer).

Fine adjustments can be made to the timer by varying the TRR up or down.

### 3.5.3 Timer 3 - Software Watchdog Timer

A watchdog timer is used to protect against system failures by providing a means to escape from unexpected input conditions, external events, or programming errors. Timer 3 may be used for this purpose. Once started, the watchdog timer must be cleared by software on a regular basis so that it never reaches its timeout value. Upon reaching the timeout value, the assumption may be made that a system failure has occurred, and steps can be taken to recover or reset the system.

#### 3.5.3.1 Software Watchdog Timer Operation

The watchdog timer counts from zero to a maximum of 32767 (16.67 seconds at 16.00 MHz) with a resolution or step size of 8192 clock periods (0.5 ms at 16.00 MHz). This timer uses a 16-bit counter with an 8-bit prescaler value.

The watchdog timer uses the main clock divided by 16 as the input to the prescaler. The prescaler circuitry divides the clock input by a fixed value of 256. The output of this prescaler circuitry is connected to the input of the 16-bit counter. Since the least significant bit of the WCN is not used in the comparison with the WRR reference value, the effective value of the prescaler is 512.

The timer counts until the reference value is reached and then starts a new time count immediately. Upon reaching the reference value, the counter asserts the  $\overline{WDOG}$  output for a period of 16 master clock (CLKO) cycles, and issues an interrupt to the interrupt controller. The value of the timer can be read any time.

To use the software watchdog function directly with the M68000 core, the timer 3 open-drain output pin (WDOG) can be connected externally to the  $\overline{IPL2}$ - $\overline{IPL0}$  pins to generate a level 7 interrupt (normal mode), to  $\overline{IRQ7}$  (dedicated mode), or to the  $\overline{RESET}$  and  $\overline{HALT}$  pin. After a total system reset, the WDOG pin function is enabled on pin PB7. The timer 3 counter is automatically enabled after reset.

The software watchdog timer has an 8-bit prescaler that is not accessible to the user, a readonly 16-bit counter, and a reference register (WRR).

#### 3.5.3.2 Software Watchdog Reference Register (WRR)

WRR is a 16-bit register containing the reference value for the timeout. The EN bit of the register enables the timer. WRR appears as a memory-mapped read-write register to the user.

When operating in the MC68008 mode (BUSW is low), writing to the high byte of WRR will disable the timer compare logic until the low byte is written.

Reset initializes the register to \$FFFF, enabling the watchdog timer and setting it to the maximum timeout period. This causes a timeout to occur if there is an error in the boot program.

FRZ1—Freeze Timer 1 Enable

- 0 = Freeze timer 1 logic is disabled.

- 1 = Freeze timer 1 logic is enabled.

After system reset, this bit defaults to zero.

FRZ2—Freeze Timer 2 Enable

- 0 = Freeze timer 2 logic is disabled.

- 1 = Freeze timer 2 logic is enabled.

After system reset, this bit defaults to zero.

FRZW—Freeze Watchdog Timer Enable

- 0 = Freeze watchdog timer logic is disabled.

- 1 = Freeze watchdog timer logic is enabled.

After system reset, this bit defaults to zero.

No other MC68302 peripherals are directly affected by the freeze logic; however, consequential errors such as receiver overruns in the SCC FIFOs may occur due to the CP main controller being disabled. Note that use of the freeze logic does not clear any IPR bits that were already set.

### 3.10 DYNAMIC RAM REFRESH CONTROLLER

The communications processor (CP) main (RISC) controller may be configured to handle the dynamic RAM (DRAM) refresh task without any intervention from the M68000 core. Use of this feature requires a timer or SCC baud rate generator (either from the MC68302 or externally), the I/O pin PB8, and two transmit buffer descriptors from SCC2 (Tx BD6 and Tx BD7).

The DRAM refresh controller routine executes in 25 clock cycles. Assuming a refresh cycle every 15.625  $\mu$ s, two wait state DRAMs, and a 16.67-MHz EXTAL frequency, this routine uses about 10 percent of the microcontroller bandwidth and 4 percent of the M68000 bus bandwidth. The refresh cycle will not be executed during a period that a bus exception (i.e., RESET, HALT, or BERR) is active. The refresh cycle is a standard M68000-type read cycle (an SDMA byte read cycle). It does not generate row address strobe (RAS) and column address strobe (CAS) to the external DRAM. These functions require an external PAL. Use of the DRAM refresh controller will slightly reduce the maximum possible serial data rates of the SCCs.

### 3.10.1 Hardware Setup

An output of timer 1 or timer 2 (the TOUT pin) or one of the SCC's baud rate generator outputs (BRG3–BRG1) should be connected externally to PB8. A high-to-low transition on this edge causes a request to be generated to the main controller to perform one refresh cycle. The DRAM refresh request takes priority over all SCC channels and commands given to the CP command register.

A block diagram of an MC68302 DRAM system is shown in Figure 3-13. The MC68302 generates standard M68000 read and write cycles that must be converted to DRAM read and write cycles. The address buffers provide the multiplexing of the row and column addresses

##

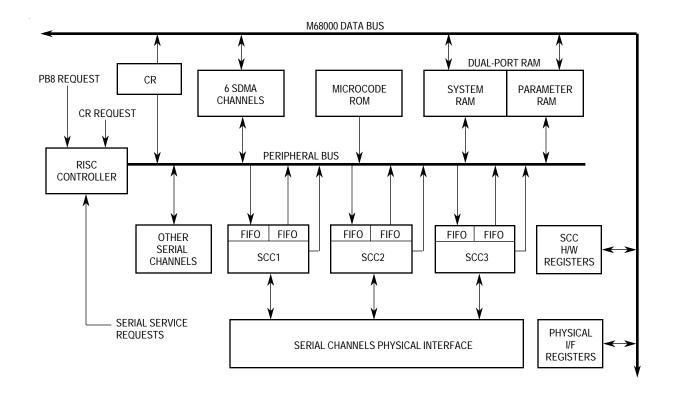

buffer descriptors of the serial channels. Also, a number of protocol-specific parameters are exchanged through several parameter RAM areas in the internal dual-port RAM.

The RISC controller uses the peripheral bus to communicate with all its peripherals. Each SCC has a separate transmit and receive FIFO. Depending on the protocol chosen, the transmit FIFO is either 3 bytes or 4 words, and the receive FIFO is either 3 bytes or 3 words. Each SCC is configured by parameters written to the dual-port RAM and by SCC hardware registers that are written by the M68000 core (or an external master). The SCC registers that configure each SCC are the SCON, DSR, and SCM. There are three sets of these registers, one for each SCC. The serial channels physical interface is configured by the M68000 core through the SIMODE and SIMASK registers.

Figure 4-1. Simplified CP Architecture

Simultaneous access of the dual-port RAM by the main controller and the M68000 core (or external processor) is prevented. During a standard four-clock cycle access of the dual-port RAM by the M68000 core, three main controller accesses are permitted. The main controller is delayed one clock cycle, at most, in accessing the dual-port RAM.

The main controller has a priority scheduler that determines which microcode routine is called when more than one internal request is pending. Requests are serviced in the following priority:

- 1. CP or System Reset

- 2. SDMA Bus Error

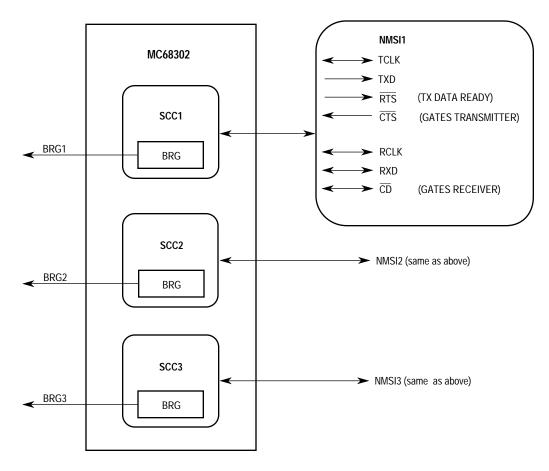

RTS, CTS, and CD are multiplexed with the SCP. See 4.6 Serial Communication Port (SCP) for more details on the SCP.

NMSI — Nonmultiplexed serial interface (also called the modem I/F).

#### Figure 4-3. NMSI Physical Interface

The other three physical interfaces, PCM, IDL, and GCI here are called multiplexed interfaces since they allow data from one, two, or all three SCCs to be time multiplexed together on the same pins. Note that if a multiplexed mode is chosen, the first SCC to use that mode must be SCC1 since the three multiplexed modes share pins with SCC1. After choosing a multiplexed mode, the user may decide whether SCC2 and SCC3 should be part of the multiplexed interface or whether they should have their own set of NMSI pins (see Figure 4-4). If SCC2 or SCC3 is part of the multiplexed interface, all NMSI2 and NMSI3 pins may be used for other functions such as parallel I/O. If a multiplexed mode is chosen, the baud rate generator clock is output on the BRG or TCLK pin, depending on whether the NMSI mode or multiplexed mode, respectively, was chosen for that SCC.

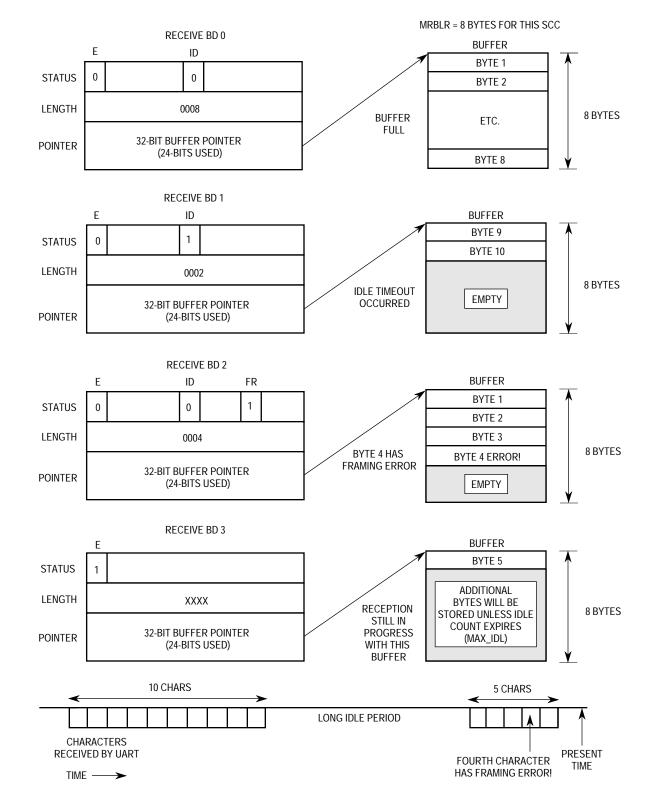

Figure 4-21. UART Rx BD Example

#### UN-Underrun

The HDLC controller encountered a transmitter underrun condition while transmitting the associated data buffer.

#### CT—CTS Lost

CTS in NMSI mode or L1GR (layer-1 grant) in IDL/GCI mode was lost during frame transmission. If data from more than one buffer is currently in the FIFO when this error occurs, this bit will be set in the Tx BD that is currently open.

#### Data Length

The data length is the number of octets the HDLC controller should transmit from this BD's data buffer. It is never modified by the CP. The value of this field should be greater than zero.

#### Tx Buffer Pointer

The transmit buffer pointer, which contains the address of the associated data buffer, may be even or odd. The buffer may reside in either internal or external memory.

#### NOTE

For correct operation of the function codes, the upper 8 bits of the pointer must be initialized to zero.

#### 4.5.12.12 HDLC Event Register

The SCC event register (SCCE) is called the HDLC event register when the SCC is operating as an HDLC controller. It is an 8-bit register used to report events recognized by the HDLC channel and to generate interrupts. Upon recognition of an event, the HDLC controller sets its corresponding bit in the HDLC event register. Interrupts generated by this register may be masked in the HDLC mask register.

The HDLC event register is a memory-mapped register that may be read at any time. A bit is cleared by writing a one; writing a zero does not affect a bit's value. More than one bit may be cleared at a time. All unmasked bits must be cleared before the CP will clear the internal interrupt request. This register is cleared at reset.

An example of the timing of various events in the HDLC event register is shown in Figure 4-29.

## mmunications Processor (CP)

If the L bit is set, the frame ends, and the transmission of ones resumes until a new buffer is made ready. RTS is negated during this period. Regardless of whether or not the next buffer is available immediately, the next buffer will not begin transmission until achieving synchronization.

The transmit buffer length and starting address may be even or odd; however, since the transparent transmitter reads a word at a time, better performance can be achieved with an even buffer length and starting address. For example, if a transmit buffer begins on an odd-byte boundary and is 10 bytes in length (the worst case), six word reads will result, even though only 10 bytes will be transmitted.

Any whole number of bytes may be transmitted. If the REVD bit in the transparent mode register is set, each data byte will be reversed in its bit order before transmission.

If the interrupt (I) bit in the Tx BD is set, then the TX bit will be set in the transparent event register following the transmission of the buffer. The TX bit can generate a maskable interrupt.

#### 4.5.16.2 Transparent Channel Buffer Reception Processing

When the M68000 core enables the transparent receiver, it will enter hunt mode. In this mode, it waits to achieve synchronization before receiving data. See 4.5.16.5 Transparent Synchronization for details.

Once data reception begins, the transparent receiver begins moving data from the receive FIFO to the receive buffer, always moving a 16-bit word at a time. After each word is moved to memory, the RCH bit in the transparent event register is set, which can generate a maskable interrupt, if desired. The transparent receiver continues to move data to the receive buffer until the buffer is completely full, as defined by the byte count in MRBLR. The receive buffer length (stored in MRBLR) and starting address must always be even, so the minimum receive buffer length must be 2.

After a buffer is filled, the transparent receiver moves to the next Rx BD in the table and begins moving data to its associated buffer. If the next buffer is not available when needed, a busy condition is signified by the setting of the BSY bit in the transparent event register, which can generate a maskable interrupt.

Received data is always packed into memory a word at a time, regardless of how it is received. For example, in NMSI mode, the first word of data will not be moved to the receive buffer until after the sixteenth receive clock occurs. In PCM highway mode, the same principle applies except that the clocks are only internally active during an SCC time slot. For example, if each SCC time slot is seven bits long, the first word of data will not be moved to the receive buffer until after the second bit of the third time slot, regardless of how much time exists between individual time slots.

Once synchronization is achieved for the receiver, the reception process continues unabated until a busy condition occurs, a  $\overline{CD}$  lost condition occurs, or a receive overrun occurs. The busy condition error should be followed by an ENTER HUNT MODE command to the

**Product.**

#### 4.7.4.1 SMC1 Receive Buffer Descriptor

The CP reports information about the received byte using this (BD).

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7 |      | 0 |

|----|----|----|----|----|----|----|----|---|------|---|

| E  | L  | ER | MS |    | _  | AB | EB |   | DATA |   |

#### E—Empty

- 0 = This bit is cleared by the CP to indicate that the data byte associated with this BD is now available to the M68000 core.

- 1 = This bit is set by the M68000 core to indicate that the data byte associated with this BD is empty.

In GCI mode, when the IMP implements the monitor channel protocol, the IMP will wait until this bit is set by the M68000 core before acknowledging the monitor channel data. In other modes (transparent GCI and IDL), additional received data bytes will be discarded until the empty bit is set by the M68000 core.

#### L-Last (EOM)

This bit is valid only in GCI mode when the IMP implements the monitor channel protocol. This bit is set when the end-of-message (EOM) indication is received on the E bit.

#### NOTE

When this bit is set, the data byte is not valid.

#### **ER**—Error Condition

This bit is valid only in GCI mode when the IMP implements the monitor channel protocol and the L bit is set. This bit is set when an error condition occurs on the monitor channel protocol. A new byte is transmitted before the IMP acknowledges the previous byte.

#### MS—Data Mismatch

This bit is valid only in GCI mode when the IMP implements the monitor channel protocol. This bit is set when two different consecutive bytes are received and is cleared when the last two consecutive bytes match. The IMP waits for the reception of two identical consecutive bytes before writing new data to the receive BD.

Bits 11–10—Reserved for future use.

#### AB—Received A Bit

This bit is valid only in GCI mode when the monitor channel is in transparent mode.

#### EB—Received E Bit

This bit is valid only in GCI mode when the monitor channel is in transparent mode.

#### Data—Data Field

The data field contains the byte of data received by SMC1.

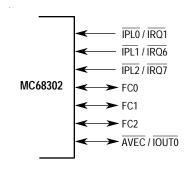

### **5.9 INTERRUPT CONTROL PINS**

The interrupt control pins are shown in Figure 5-9.

#### Figure 5-9. Interrupt Control Pins

These inputs have dual functionality:

- IPL0/IRQ1

- IPL1/IRQ6

- IPL2/IRQ7—Interrupt Priority Level 2–0/Interrupt Request 1,6,7

As IPL2–IPL0 (normal mode), these input pins indicate the encoded priority level of the external device requesting an interrupt. Level 7 is the highest (nonmaskable) priority; whereas, level 0 indicates that no interrupt is requested. The least significant bit is IPL0, and the most significant bit is IPL2. These lines must remain stable until the M68000 core signals an interrupt acknowledge through FC2–FC0 and A19–A16 to ensure that the interrupt is properly recognized.

As IRQ1, IRQ6, and IRQ7 (dedicated mode), these inputs indicate to the MC68302 that an external device is requesting an interrupt. Level 7 is the highest level and cannot be masked. Level 1 is the lowest level. Each one of these inputs (except for level 7) can be programmed to be either level-sensitive or edge-sensitive. The M68000 always treats a level 7 interrupt as edge sensitive.

#### FC2–FC0—Function Codes 2–0

These bidirectional signals indicate the state and the cycle type currently being executed. The information indicated by the function code outputs is valid whenever  $\overline{\text{AS}}$  is active.

These lines are outputs when the IMP (M68000 core, SDMA, or IDMA) is the bus master and are inputs otherwise. The function codes output by the M68000 core are predefined; whereas, those output by the SDMA and IDMA are programmable. The function code lines are inputs to the chip-select logic and IMP internal register decoding in the BAR.

#### AVEC/IOUT0—Autovector Input/Interrupt Output 0

In normal operation, this signal functions as the input  $\overline{AVEC}$ .  $\overline{AVEC}$ , when asserted during an interrupt acknowledge cycle, indicates that the M68000 core should use automatic vectoring for an interrupt. This pin operates like  $\overline{VPA}$  on the MC68000, but is used for au-

#### NOTE

When using SCC1 in the NMSI mode with the internal baud rate generator operating, the TCLK1 and RCLK1 pins will always output the baud rate generator clock unless disabled in the CKCR register. Thus, if a dynamic selection between an internal and external clock source is required in an application, the clock pins should be disabled first in the CKCR register before switching the TCLK1 and RCLK1 lines. On SCC2 and SCC3, contention may be avoided by disabling the clock line outputs in the PACNT register.

In PCM mode, L1SY1–L1SY0 are encoded signals used to create channels that can be independently routed to the SCCs.

| L1SY1 | L1SY0 | Data (L1RXD, L1TXD) is Routed to SCC    |

|-------|-------|-----------------------------------------|

| 0     | 0     | L1TXD is Three-Stated, L1RXD is Ignored |

| 0     | 1     | CH-1                                    |

| 1     | 0     | CH-2                                    |

| 1     | 1     | CH-3                                    |

Table 5-8. PCM Mode Signals

NOTE: CH-1, 2, and 3 are connected to the SCCs as determined in the SIMODE register.

In IDL/GCI modes, the SDS2–SDS1 outputs may be used to route the B1 and/or B2 channels to devices that do not support the IDL or GCI buses. This is configured in the serial interface mode (SIMODE) and serial interface mask (SIMASK) registers.

#### CD1/L1SY1—Carrier Detect/Layer-1 Sync

This input is used as the NMSI1 carrier detect ( $\overline{CD}$ ) pin in NMSI mode, as a PCM sync signal in PCM mode, and as an L1SYNC signal in IDL/GCI modes.

If the  $\overline{\text{CD1}}$  pin has changed for more than one receive clock cycle, the IMP asserts the appropriate bit in the SCC1 event register. If the SCC1 channel is programmed not to support  $\overline{\text{CD1}}$  automatically (in the SCC1 mode register), then this pin may be used as an external interrupt source. The current value of  $\overline{\text{CD1}}$  may be read in the SCCS1 register. See 4.5.8.3 SCC Status Register (SCCs) for details.  $\overline{\text{CD1}}$  may also be used as an external sync in NMSI mode.

#### CTS1/L1GR—Clear to Send/Layer-1 Grant

This input is the NMSI1  $\overline{\text{CTS}}$  signal in the NMSI mode or the grant signal in the IDL/GCI mode. If this pin is not used as a grant signal in GCI mode, it should be connected to V<sub>DD</sub>.

If the  $\overline{\text{CTS1}}$  pin has changed for more than one transmit clock cycle, the IMP asserts the appropriate bit in the SCC1 event register and optionally aborts the transmission of that frame.

ctrical Characteristics

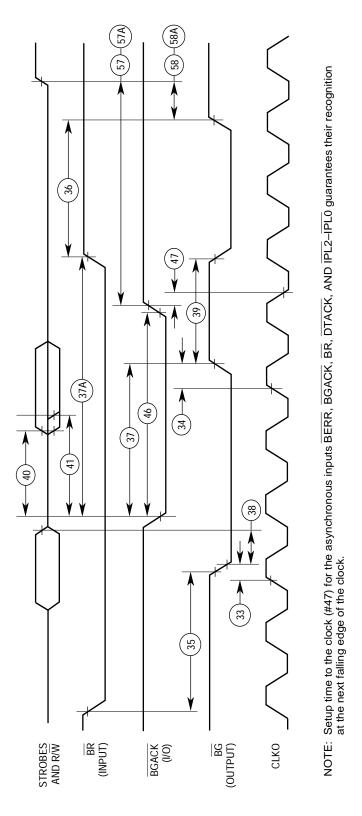

Figure 6-5. Bus Arbitration Timing Diagram

MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

## SECTION 7 MECHANICAL DATA AND ORDERING INFORMATION

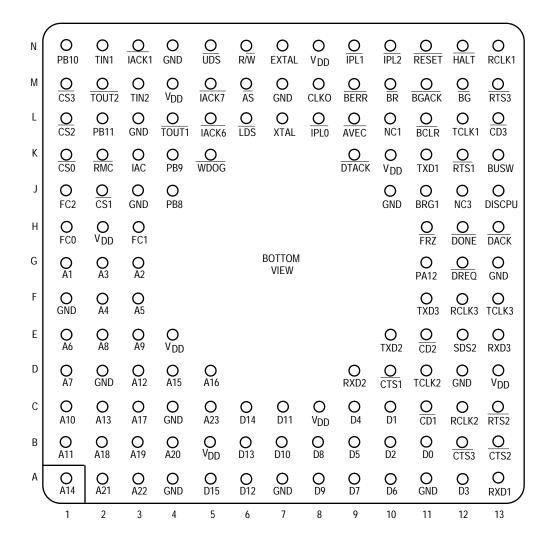

#### 7.1 PIN ASSIGNMENTS

7.1.1 Pin Grid Array (PGA)

channel was always SCC1.

- 7. This data applies to MC68302 masks 2B14M, 3B14M, or later.

- 8. The following explanation concerns a fast HDLC channel and two slower channels: When the fast HDLC is 1:9, two HDLCs can run at 1:224. Thus, with a 16.67-MHz dock, SCC1 can run at 1.85 Mbps; SCC2 and SCC3 can run at 74 kbps. Two HDLCs can also run without equal values: one at 1:128 and one at 1:238. When the fast HDLC is 1:10, two HDLCs can run at 1:128. When the fast HDLC is 1:9, two UARTs can run at 1:396 (\*16). When the fast HDLC is 1:10, two UARTs can run at 1:10 (\*16).

- Performance results above showed no receive overruns or transmit underruns in several minutes of continuous transmission/reception. Reduction of the above ratios by a single value (e.g., 1:35 reduced to 1:34) did show an overrun or underrun within several minutes.

- 10. All results assume the DRAM refresh controller is not operating; otherwise, performance is slightly reduced.

- 11. Unless specifically stated, all table results assume continuous full-duplex operation. Results for half-duplex were not measured, but will be roughly 2x better.

Since operation at very high data rates is characteristic of HDLC-framed channels rather than BISYNC-, DDCMP-, or async-framed channels, the user can also use the MC68302 in conjunction with either the Motorola MC68605 1984 CCITT X.25 LAPB controller, the MC68606 CCITT Q.921 multilink LAPD controller, or the MC145488 dual data link controller. These devices fully support operation at T1/CEPT rates (and above) and can operate with their serial clocks "gated" onto subchannels of such an interface. These devices are full M68000 bus masters. The MC68605 and MC68606 perform the full data-link layer protocol as well as support various transparent modes within HDLC-framed operation. The MC145488 provides HDLC-framed and totally transparent operation on two full-duplex channels.

Freescale Semiconductor, Inc.

## C Programming Reference Freescale Semiconductor, Inc.

- **OPCODE**—Command Opcode

- 00 = STOP TRANSMIT Command.

- 01 = RESTART TRANSMIT Command.

- 10 = ENTER HUNT MODE Command.

- 11 = Reset receiver BCS generator (used only in BISYNC mode).

BIT 3—Reserved (should be set to zero by the user when the command register is written)

CH. NUM.—Channel Number

- 00 = SCC1.

- 01 = SCC2.

- 10 = SCC3.

- 11 = Reserved.

FLG—Command Semaphore Flag (set by the user and cleared by the CP upon command completion)

- 0 = CP is ready to receive a new command (should be checked before issuing the next command to the CP)

- 1= Command register contains a command to be executed or one that is currently being executed.

**E.1.1.2 Serial Interface Mode Register (SIMODE).** This 16-bit register is located at offset \$8B4. The SIMODE register is used to configure the serial interface mode for the three SCCs.

| 15   | 14        | 13     | 12     | 11   | 10   | 9    | 8    |

|------|-----------|--------|--------|------|------|------|------|

| SETZ | SYNC/SCIT | SDIAG1 | SDIAG0 | SDC2 | SDC1 | B2RB | B2RA |

|      |           |        |        |      |      |      |      |

| 7    | 6    | 5   | 4   | 3    | 2    | 1   | 0   |

|------|------|-----|-----|------|------|-----|-----|

| B1RB | B1RA | DRB | DRA | MSC3 | MSC2 | MS1 | MS0 |

SETZ—Set L1 TXD to Zero (valid only for the GCI interface)

0 = Normal operation.

1 = L1 TXD output set to a logic zero (used in GCI activation).

SYNC/SCIT—SYNC Mode/SCIT Select Support

- 0 = One pulse wide prior to the 8-bit data.

- 1 = N pulses wide and envelopes the N-bit data.

#### SDIAG1, SDIAG0—Serial Interface Diagnostic Mode

- 00 = Normal operation.

- 01 = Automatic echo.

- 10 = Internal loopback.

- 11 = Loopback control.

#### NOF3-NOF0—Number of Flags

Minimum number of flags between frames or before frames specifies the number of flags (0-15) to be inserted between frames or before a frame is transmitted.

C32—CRC16/CRC32

- 0 = 16-bit CRC.

- 1 = 32-bit CRC.

FSE—Flag Sharing Enable

- 0 = Normal operation.

- 1 = Transmits a single shared flag between back-to-back frames if NOF3-NOF2 = 0. Other values of NOF3-NOF2 are decremented by 1.

- BIT 9—Reserved for future use

- 0 = No retransmission.

- 1 = Retransmit enabled.

FLG—Transmit Flags/Idles between Frames and Control the RTS Pin

- 0 = Send ones between frames;  $\overline{\text{RTS}}$  negated between frames.

- 1 = Send flags between frames; RTS is always asserted.

- ENC—Data Encoding Format

- 0 = Non-return to zero (NRZ).

- 1 = Non-return to zero inverted (NRZI).

- DIAG1, DIAG0—Diagnostic Mode

- 00 = Normal operation.

- 01 = Loopback mode.

- 10 = Automatic echo.

- 11 = Software operation.

#### ENR—Enable Receiver

- 0 = Receiver is disabled.

- 1 = Receiver is enabled.

- ENT—Enable Transmitter

- 0 = Transmitter is disabled.

- 1 = Transmitter is enabled.

#### MODE1, MODE0—Channel Mode

- 00 = HDLC.

- 01 = Asynchronous (UART and DDCMP).

- 10 = Synchronous DDCMP and V.110.

- 11 = BISYNC and Promiscuous (Transparent).

RTE—Retransmit Enable

| Initialized<br>by User | Offset<br>Hex | Name                                   |          |  |  |  |  |

|------------------------|---------------|----------------------------------------|----------|--|--|--|--|

|                        | 00            | Reserved                               | eserved  |  |  |  |  |

| Yes                    | 02            | SCC Configuration Register (SCON)      |          |  |  |  |  |

| Yes                    | 04            | SCC Mode Register (SCM)                |          |  |  |  |  |

| Yes                    | 06            | SCC Data Synchronization Register (DSF | R)       |  |  |  |  |

| Yes                    | 08            | Event Register (SCCE)                  | Reserved |  |  |  |  |

| Yes                    | 0A            | Mask Register (SCCM)                   | Reserved |  |  |  |  |

|                        | 0C            | Status Register (SCCS)                 | Reserved |  |  |  |  |

|                        | 0E            | Reserved                               |          |  |  |  |  |

#### Table E-1 (c). SCCx Register Set

NOTE: The offset is from the MC68302 base address + (\$880 for SCC1, \$890 for SCC2, or \$8A0 for SCC3).

| Initialized<br>by User | Offset<br>Hex | Name                                    |          |  |  |  |

|------------------------|---------------|-----------------------------------------|----------|--|--|--|

|                        | 860           | Command Register (CR)                   | Reserved |  |  |  |

| Yes                    | 8B2           | Serial Interface Mask Register (SIMASK) |          |  |  |  |

| Yes                    | 8B4           | Serial Interface Mask Register (SIMODE) |          |  |  |  |

NOTE: The offset is from the MC68302 base address.

**E.3.1.1 COMMUNICATIONS PROCESSOR (CP) REGISTERS.** The CP has one set of three registers that configure the operation of the serial interface for all three SCCs. These registers are discussed in the following paragraphs.

**E.3.1.1.1 Command Register (CR).** The command register is an 8-bit register located at offset \$860 (on D15-D8 of a 16-bit data bus). This register is used to issue commands to the CP. The user should set the FLG bit when a command is written to the command register. The CP clears the FLG bit during command processing to indicate that it is ready for the next command. Reserved bits in registers should be written as zeros.

| 7   | 6   | 5   | 4      | 3 | 2     | 1    | 0   |

|-----|-----|-----|--------|---|-------|------|-----|

| RST | GCI | OPC | OPCODE |   | CH. I | NUM. | FLG |

RST—Software Reset Command (set by the user and cleared by the CP)

- 0 = No software reset command issued or cleared by CP during software reset sequence.

- 1 = Software reset command (FLG bit should also be set if it is not already set).

GCI-GCI Commands

- 0 = Normal operation.

- 1 = The OPCODE bits are used for GCI commands (user should set CH. NUM. to 10 and FLG to 1).

does not correctly "equate" locations in parameter RAM to intended addresses. A simple typo in an assembler EQU or a C #DEFINE directive can cause 1) the intended parameter not to be set and 2) another parameter to be set to a wrong value.

#### 17. Function Code, Initialize, Reset

To use IDMA, SDMA, and/or DRAM refresh, their corresponding function code registers MUST be initialized. Setting the function codes in these registers to "111" will prevent the MC68302 chip selects from asserting. Failure to initialize these registers often results in their function codes having the value "111", since these registers are in dualport RAM and do not have predefined values upon a total system reset.

#### 18. Function Code, External Bus Master

When an external bus master is using the chip selects on the MC68302 with the external master's external memory accesses, make sure that the external bus master drives the function code lines to something other than "111". If the function code lines are driven or left floating to "111", the external cycle will be interpreted by the MC68302 as an interrupt acknowledge cycle, and the chip selects will not be asserted during the cycle.

#### 19. BAR, Write

The BAR MUST BE written by an instruction following a total system reset of the MC68302 since this register resides in the MC68302, not in the memory. It is not sufficient or required for the EPROM on the target board to have the desired BAR value stored in the EPROM location \$0F2 (the address of BAR). When using an emulator, a symptom of this problem can be that the code works in the emulator overlay memory, but not on the target.

#### 20. DRAM Refresh

When using the DRAM refresh unit, one cannot refresh locations \$0F0–0FF of an external DRAM if an MC68302 chip select is used to select that DRAM. Locations \$0F0– 0FF are designated as the reserved area of the IMP that contains the BAR and SCR, and chip selects will not activate on accesses to these addresses. The remedy is simply to use a different DRAM refresh starting address besides \$0. Also note that the DRAM refresh access is a byte read, not a word read.

#### 21. Watchdog Timer

If the MC68302 watchdog timer is never turned off or refreshed, an unexpected interrupt at level 4 can occur. Also, an unexpected RESET can occur if the WDOG pin is externally connected to HALT and RESET. The solution is to disable the watchdog timer after reset. Note that the watchdog timer is not related to the hardware watchdog, which is a completely separate unit that monitors bus activity.

#### 22. Underrun, Overrun, Clock Lines, Schmitt-Triggers

If a transmit underrun or a receive overrun is reported but the data rates are too slow to suggest an actual underrun or overrun, the problem may be in the clock lines. Glitched or badly ringing clocks (on the TCLK or RCLK pins) can cause SCCs to enter either of the above error states. Even though Schmitt-triggers are implemented on the IMP clocks lines, a very slow rise/fall time coupled with a large amount of noise on the lines can override the hysteresis protection and affect the ability of the SCC to correctly sample and clock data. Internal clocks generated by the IMP do not cause this problem.