#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | M68000                                                               |

| Number of Cores/Bus Width       | 1 Core, 8/16-Bit                                                     |

| Speed                           | 25MHz                                                                |

| Co-Processors/DSP               | Communications; RISC CPM                                             |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | -                                                                    |

| SATA                            | -                                                                    |

| USB                             | -                                                                    |

| Voltage - I/O                   | 5.0V                                                                 |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                      |

| Security Features               | -                                                                    |

| Package / Case                  | 144-LQFP                                                             |

| Supplier Device Package         | 144-LQFP (20x20)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68302pv25c |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

on bytes, words, or long words, and most instructions can use any of the 14 addressing modes.

Combining instruction types, data types, and addressing modes provides over 1000 useful instructions. These instructions include signed and unsigned multiply and divide, quick arithmetic operations, BCD arithmetic, and expanded operations (through traps).

| Mode                                                                                                                                                                                             | Generation                                                                                                                      |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Register Direct Addressing<br>Data Register Direct<br>Address Register Direct                                                                                                                    | EA = Dn<br>EA = An                                                                                                              |  |  |  |  |  |  |  |

| Absolute Data Addressing<br>Absolute Short<br>Absolute Long                                                                                                                                      | EA = (Next Word)<br>EA = (Next Two Words)                                                                                       |  |  |  |  |  |  |  |

| Program Counter Relative Addressing<br>Relative with Offset<br>Relative with Index and Offset                                                                                                    | $EA = (PC) + d_{16}$<br>EA = (PC) + Xn + d8                                                                                     |  |  |  |  |  |  |  |

| Register Indirect Addressing<br>Register Indirect<br>Postincrement Register Indirect<br>Predecrement Register Indirect<br>Register Indirect with Offset<br>Indexed Register Indirect with Offset | $EA = (An)$ $EA = (An), An \leftarrow An + N$ $EA = \leftarrow An - N, EA = (An)$ $EA = (An) + d_{16}$ $EA = (An) + (Xn) + d_8$ |  |  |  |  |  |  |  |

| Immediate Data Addressing<br>Immediate<br>Quick Immediate                                                                                                                                        | DATA = Next Word(s)<br>Inherent Data                                                                                            |  |  |  |  |  |  |  |

| Implied Addressing<br>Implied Register                                                                                                                                                           | EA = SR, USP, SSP, PC                                                                                                           |  |  |  |  |  |  |  |

#### Table 2-1. M68000 Data Addressing Modes

#### NOTES:

| EA = | Effective Address |

|------|-------------------|

|------|-------------------|

- An = Address Register

- Dn = Data Register

- Xn = Address or Data Register Used as an Index Register

- SR = Status Register

- PC = Program Counter

- () = Contents of

- d<sub>8</sub> = 8-Bit Offset (Displacement)

- d16 = 16-Bit Offset (Displacement)

- N = 1 for byte, 2 for word, and 4 for long word. If An is the stack pointer and the operand size is byte, N = 2 to keep the stack pointer on a word boundary.

- = Replaces

## 2.5 INTERRUPT PROCESSING

Seven interrupt levels are provided by the M68000 core. If the IMP's interrupt controller is placed in the normal mode, six levels are available to the user. If the interrupt controller is in the dedicated mode, three levels are available to the user. In either mode, level 4 is reserved for the on-chip peripherals. Devices may be chained externally within one of the available priority levels, allowing an unlimited number of external peripheral devices to interrupt the processor. The SR contains a 3-bit mask indicating the current processor priority level. Interrupts are inhibited for all priority levels less than or equal to the current processor priority (see Figure 2-2).

An interrupt request is made to the processor by encoding the request on the interrupt request lines (normal mode) or by asserting the appropriate request line (dedicated mode). Rather than forcing immediate exception processing, interrupt requests arriving at the processor are made pending to be detected between instruction executions.

If the priority of the pending interrupt is lower than or equal to the current processor priority, execution continues with the next instruction, and the interrupt exception processing is post-poned.

If the priority of the pending interrupt is greater than the current processor priority, the exception processing sequence is started. A copy of the SR is saved, the privilege state is set to supervisor state, tracing is suppressed, and the processor priority level is set to the level of the interrupt being acknowledged. The processor fetches the vector number from the interrupting device, classifying the reference as an interrupt acknowledge on the address bus. If external logic requests automatic vectoring (via the AVEC pin), the processor internally generates a vector number determined by the interrupt level number. If external logic indicates a bus error, the interrupt is considered spurious, and the generated vector number references the spurious interrupt vector number.

# 2.6 M68000 SIGNAL DIFFERENCES

The MC68302 core supports one additional signal not visible on the standard M68000: RMC. Asserted externally on read-modify-write cycles, the RMC signal is typically used as a bus lock to ensure integrity of instructions using the locked read-modify-write operation of the test and set (TAS) instruction. The RMC signal from the M68000 core is applied to the MC68302 arbiter and can be programmed to prevent the arbiter from issuing bus grants until the completion of an MC68000-core-initiated read-modify-write cycle.

The MC68302 can be programmed to use the  $\overline{RMC}$  signal to negate address strobe ( $\overline{AS}$ ) at the end of the read portion of the cycle and assert  $\overline{AS}$  at the beginning of the write portion of the cycle (See 3.8.3 System Control Bits).

Two M6800 signals are omitted from the MC68302: valid memory address ( $\overline{VMA}$ ) and enable (E). The valid peripheral address ( $\overline{VPA}$ ) signal is retained, but is only used on the MC68302 as  $\overline{AVEC}$  to direct the core to use an autovector during interrupt acknowledge cycles.

When working in the MC68008 mode (BUSW is low), writing the high byte of TRR1 and TRR2 will disable the timer's compare logic until the low byte is written.

TRR1 and TRR2 are set to all ones by reset. The reference value is not "reached" until TCN increments to equal TRR.

## 3.5.2.3 Timer Capture Registers (TCR1, TCR2)

Each TCR is a 16-bit register used to latch the value of the counter during a capture operation when an edge occurs on the respective TIN1 or TIN2 pin. TCR1 and TCR2 appear as memory-mapped read-only registers to the user.

When working in the MC68008 mode (BUSW is low), reading the high byte of TCR1 and TCR2 will disable the timer's capture logic until the low byte is read.

TCR1 and TCR2 are cleared at reset.

### 3.5.2.4 Timer Counter (TCN1, TCN2)

TCN1 and TCN2 are 16-bit up-counters. Each is memory-mapped and can be read and written by the user. A read cycle to TCN1 and TCN2 yields the current value of the timer and does not affect the counting operation.

When working in the MC68008 mode (BUSW is low), reading the high byte of TCN1 and TCN2 will latch the low byte into a temporary register; a subsequent read cycle on the low byte yields the value of the temporary register.

A write cycle to TCN1 and TCN2 causes both the counter register and the corresponding prescaler to be reset to zero. In MC68008 mode (BUSW is low), a write cycle to either the high or low byte of the TCN will reset the counter register and the corresponding prescaler to zero.

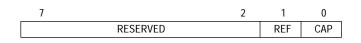

## 3.5.2.5 Timer Event Registers (TER1, TER2)

Each TER is an 8-bit register used to report events recognized by any of the timers. On recognition of an event, the timer will set the appropriate bit in the TER, regardless of the corresponding interrupt enable bits (ORI and CE) in the TMR. TER1 and TER2, which appear to the user as memory-mapped registers, may be read at any time.

A bit is cleared by writing a one to that bit (writing a zero does not affect a bit's value). More than one bit may be cleared at a time. Both bits must be cleared before the timer will negate the INRQ to the interrupt controller. This register is cleared at reset.

### CAP—Capture Event

The counter value has been latched into the TCR. The CE bits in the TMR are used to enable the interrupt request caused by this event.

FRZ1—Freeze Timer 1 Enable

- 0 = Freeze timer 1 logic is disabled.

- 1 = Freeze timer 1 logic is enabled.

After system reset, this bit defaults to zero.

FRZ2—Freeze Timer 2 Enable

- 0 = Freeze timer 2 logic is disabled.

- 1 = Freeze timer 2 logic is enabled.

After system reset, this bit defaults to zero.

FRZW—Freeze Watchdog Timer Enable

- 0 = Freeze watchdog timer logic is disabled.

- 1 = Freeze watchdog timer logic is enabled.

After system reset, this bit defaults to zero.

No other MC68302 peripherals are directly affected by the freeze logic; however, consequential errors such as receiver overruns in the SCC FIFOs may occur due to the CP main controller being disabled. Note that use of the freeze logic does not clear any IPR bits that were already set.

# 3.10 DYNAMIC RAM REFRESH CONTROLLER

The communications processor (CP) main (RISC) controller may be configured to handle the dynamic RAM (DRAM) refresh task without any intervention from the M68000 core. Use of this feature requires a timer or SCC baud rate generator (either from the MC68302 or externally), the I/O pin PB8, and two transmit buffer descriptors from SCC2 (Tx BD6 and Tx BD7).

The DRAM refresh controller routine executes in 25 clock cycles. Assuming a refresh cycle every 15.625  $\mu$ s, two wait state DRAMs, and a 16.67-MHz EXTAL frequency, this routine uses about 10 percent of the microcontroller bandwidth and 4 percent of the M68000 bus bandwidth. The refresh cycle will not be executed during a period that a bus exception (i.e., RESET, HALT, or BERR) is active. The refresh cycle is a standard M68000-type read cycle (an SDMA byte read cycle). It does not generate row address strobe (RAS) and column address strobe (CAS) to the external DRAM. These functions require an external PAL. Use of the DRAM refresh controller will slightly reduce the maximum possible serial data rates of the SCCs.

# 3.10.1 Hardware Setup

An output of timer 1 or timer 2 (the TOUT pin) or one of the SCC's baud rate generator outputs (BRG3–BRG1) should be connected externally to PB8. A high-to-low transition on this edge causes a request to be generated to the main controller to perform one refresh cycle. The DRAM refresh request takes priority over all SCC channels and commands given to the CP command register.

A block diagram of an MC68302 DRAM system is shown in Figure 3-13. The MC68302 generates standard M68000 read and write cycles that must be converted to DRAM read and write cycles. The address buffers provide the multiplexing of the row and column addresses

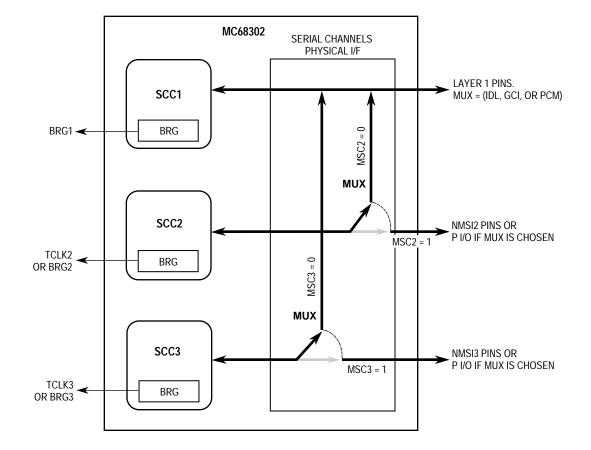

#### Figure 4-4. Multiplexed Mode on SCC1 Opens Additional Configuration Possibilities

There are five serial channel physical interface combinations for the three SCCs (see Table 4-1).

| SCC  | 1    | 2    | 3    | 4    | 5   |

|------|------|------|------|------|-----|

| SCC1 | NMSI | MUX  | MUX  | MUX  | MUX |

| SCC2 | NMSI | NMSI | MUX  | NMSI | MUX |

| SCC3 | NMSI | NMSI | NMSI | MUX  | MUX |

Table 4-1. The Five Possible SCC Combinations

NOTE: MUX is defined as one of the following: IDL, GCI, or PCM highway.

The PCM highway interface is a flexible time-division multiplexed interface. It allows the MC68302 to connect to popular time-slot interfaces such as T1 and CEPT as well as userdefined time-slot interfaces.

The IDL and GCI (IOM-2) interfaces are used to connect to semiconductor devices that support the Integrated Services Digital Network (ISDN). IDL and GCI allow the MC68302 to communicate over any of the 2B + D ISDN basic rate channels.

The monitor channel is used to transfer data between layer-1 devices and the control unit (i.e., the M68000 core). The command/indication channel is used to control activation/deactivation procedures or for the switching of test loops by the control unit.

The IMP supports all five channels of the GCI channel 0. The following table shows where each channel can be routed. The two B channels can be concatenated and routed to the same SCC channel.

| GCI Channel 0 | Serial Controllers |

|---------------|--------------------|

| D             | SCC1, SCC2, SCC3   |

| B1            | SCC1, SCC2, SCC3   |

| B2            | SCC1, SCC2, SCC3   |

| M             | SMC1               |

| C/I           | SMC2               |

The GCI interface supports the CCITT I.460 recommendation for data rate adaptation. The GCI interface can access each bit of the B channel as an 8-kbps channel. The mask register (SIMASK) for the B channels specifies which bits are supported by the GCI interface. The receiver will receive only the bits that are enabled by SIMASK; the transmitter will transmit only the bits that are enabled by SIMASK and will not drive the L1TXD pin otherwise (L1TXD in GCI mode is an open-drain output).

The IMP supports contention detection on the D channel. When the IMP has data to transmit on the D channel, it checks bit 4 of the SCIT C/I channel 2. The physical layer device monitors the physical layer bus for activity on the D channel and indicates with this bit that the channel is free. If a collision is detected on the D channel, the physical layer device sets bit 4 of C/I channel 2 to logic high. The IMP then aborts its transmission and retransmits the frame when this bit is asserted again. This procedure is handled automatically for the first two buffers of a frame. The L1GR line may also be used for access to the S interface D channel. This signal is checked by the IMP, and the physical layer device should indicate that the S interface D channel is free by asserting L1GR.

In the deactivated state, the clock pulse is disabled, and the data line is a logic one. The layer-1 device activates the IMP by enabling the clock pulses and by an indication in the channel 0 C/I channel. The IMP will then report to the M68000 core by a maskable interrupt that a valid indication is in the SMC2 receive buffer descriptor.

When the M68000 core activates the line, it sets SETZ in the serial interface mode (SIMO-DE) register, causing the data output from L1TXD to become a logic zero. Code 0 (command timing TIM) will be transmitted on channel 0 C/I channel to the layer-1 device until the SETZ is reset. The physical layer device will resume transmitting the clock pulses and will give an indication in the channel 0 C/I channel. The M68000 core should reset SETZ to enable data output.

# 4.4.3 PCM Highway Mode

In PCM highway mode, one, two, or all three SCCs can be multiplexed together to support various time-division multiplexed interfaces. PCM highway supports the standard T1 and CEPT interfaces as well as user-defined interfaces. In this mode, the NMSI1 pins have new names and functions (see Table 4-2).

# mmunications Processor (CP) escale Semiconductor, Inc.

Three characters should first be entered into the UART control character table:

- 1. End of Line—The empty (E) bit is cleared; the reject (R) bit is cleared. When an endof-line character is received, the current buffer is closed (the next BD taken by the IMP) and made available to the M68000 core for processing. This buffer contains an entire S record, which the processor can now check and copy to memory or disk as required.

- XOFF—E should be cleared and R should be set. Whenever the M68000 core receives a control character received interrupt and the receive control character register contains XOFF, the software should immediately stop transmitting to the other station by setting the FRZ bit in the UART mode register. This prevents data from being lost by the other station when it runs out of receive buffers.

- 3. XON—XON should be received after XOFF. E should be cleared and R should be set. The FRZ bit on the transmitter should now be cleared. The IMP automatically resumes transmission of the serial line at the point at which it was previously stopped. Like XOFF, the XON character is not stored in the receive buffer.

To receive the S records, the M68000 core must only wait for the RX interrupt, indicating the reception of a complete S-record buffer. Transmission requires assembling S records into data buffers and linking them to the transmit buffer table (transmission may be temporarily halted by reception of an XOFF character). This scheme minimizes the number of interrupts received by the M68000 core (one per S record) and relieves it from the task of continually scanning for control characters.

# 4.5.12 HDLC Controller

Layer 2 of the seven-layer OSI model is the data link layer. One of the most common layer 2 protocols is HDLC. Many other common layer 2 protocols are heavily based on HDLC, particularly its framing structure: namely, SDLC, SS#7, LAPB, and LAPD. The framing structure of HDLC is shown in Figure 4-24.

| OPENING<br>FLAG | ADDRESS | CONTROL | INFORMATION<br>(OPTIONAL) | CRC     | CLOSING<br>FLAG |

|-----------------|---------|---------|---------------------------|---------|-----------------|

| 8 BITS          | 16 BITS | 8 BITS  | 8N BITS                   | 16 BITS | 8 BITS          |

| Figure 4-24 | . Typical | HDLC Frame |

|-------------|-----------|------------|

|-------------|-----------|------------|

HDLC uses a zero insertion/deletion process (commonly known as bit-stuffing) to ensure that the bit pattern of the delimiter flag does not occur in the fields between flags. The HDLC frame is synchronous and therefore relies on the physical layer to provide a method of clocking and synchronizing the transmitter and receiver.

Since the layer 2 frame can be transmitted over a point-to-point link, a broadcast network, or packet and circuit-switched systems, an address field is needed to carry the frame's destination address. The length of this field is commonly 0, 8, or 16 bits, depending on the data link layer protocol. For instance, SDLC and LAPB use an 8-bit address. SS#7 has no address field at all because it is always used in point-to-point signaling links. LAPD further divides its 16-bit address into different fields to specify various access points within one piece of equipment. It also defines a broadcast address. Some HDLC-type protocols also allow for extended addressing beyond 16-bits.

# mmunications Processor (CP)

cludes it from the BCS. If the second character is a DLE, the BISYNC controller will write it to the buffer and include it in the BCS. If the character is not a DLE or SYNC, the BISYNC controller will examine the control characters table and act accordingly. If the character is not in the table, the buffer will be closed with the DLE follow character error (DL) bit set. If the V bit is not set, the receiver will treat the character as a normal character.

#### NOTE

When using 7-bit characters with parity, the parity bit should be included in the DLE register value.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|----|----|---|---|---|

| V  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   |   | DI | LE |   |   |   |

## 4.5.13.8 BISYNC Error-Handling Procedure

The BISYNC controller reports message reception and transmission error conditions using the channel BDs, the error counters, and the BISYNC event register. The modem interface lines can also be directly monitored in the SCC status register.

Transmission Errors:

- Transmitter Underrun. When this error occurs, the channel terminates buffer transmission, closes the buffer, sets the underrun (UN) bit in the BD, and generates the TXE interrupt (if enabled). The channel resumes transmission after the reception of the RE-START TRANSMIT command. Underrun cannot occur between frames or during a DLE-XXX pair in transparent mode. The FIFO size is three bytes in BISYNC.

- 2. Clear-To-Send Lost During Message Transmission. When this error occurs and the channel is not programmed to control this line with software, the channel terminates buffer transmission, closes the buffer, sets the CTS lost (CT) bit in the BD, and generates the TXE interrupt (if enabled). The channel will resume transmission after the reception of the RESTART TRANSMIT command.

**Reception Errors:**

- Overrun Error. The BISYNC controller maintains an internal three-byte FIFO for receiving data. The CP begins programming the SDMA channel (if the data buffer is in external memory) and updating the CRC when the first word is received into the FIFO. If a FIFO overrun occurs, the BISYNC controller writes the received data byte to the internal FIFO over the previously received byte. The previous character and its status bits are lost. Following this, the channel closes the buffer, sets the overrun (OV) bit in the BD, and generates the RX interrupt (if enabled). The receiver then enters hunt mode immediately.

- 2. Carrier Detect Lost During Message Reception. When this error occurs and the channel is not programmed to control this line with software, the channel terminates message reception, closes the buffer, sets the carrier detect lost (CD) bit in the BD, and generates the RX interrupt (if enabled). This error is the highest priority; the rest of the message is lost and no other errors are checked in the message. The receiver then enters hunt mode immediately.

- 3. Parity Error. When this error occurs, the channel writes the received character to the

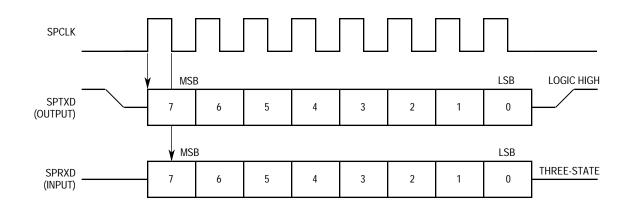

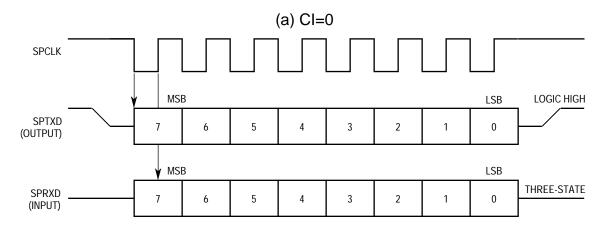

NOTE: Transmitted data bits shift on rising edges; received bits are sampled on falling edges.

NOTE: Transmitted data bits shift on falling edges; received bits are sampled on rising edges.

(b) CI=1

#### Figure 4-44. SCP Timing

The SCP can be configured to operate in a local loopback mode, which is useful for local diagnostic functions.

Note that the least significant bit of the SCP is labeled as data bit 0 on the serial line; whereas, other devices, such as the MC145554 CODEC, may label the most significant bit as data bit 0. The MC68302 SCP bit 7 (most significant bit) is shifted out first.

The SCP key features are as follows:

- Three-Wire Interface (SPTXD, SPRXD, and SPCLK)

- Full-Duplex Operation

- Clock Rate up to 4.096 MHz

- Programmable Clock Generator

- Local Loopback Capability for Testing

When working with an 8-bit bus (BUSW is low), the data is transferred through the low-order byte (D7–D0). The high-order byte (D15–D8) is not used for data transfer, but D8-D15 are outputs during write cycles and are not three-stated.

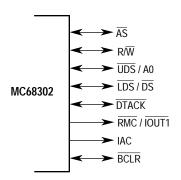

# 5.7 BUS CONTROL PINS

The bus control pins are shown in Figure 5-6.

Figure 5-6. Bus Control Pins

#### AS—Address Strobe

This bidirectional signal indicates that there is a valid address on the address bus. This line is an output when the IMP (M68000 core, SDMA or IDMA) is the bus master and is an input otherwise.

#### R/W-Read/Write

This bidirectional signal defines the data bus transfer as a read or write cycle. It is an output when the IMP is the bus master and is an input otherwise.

### UDS/A0—Upper Data Strobe/Address 0

This bidirectional line controls the flow of data on the data bus. When using a 16-bit data bus, this pin functions as upper data strobe ( $\overline{\text{UDS}}$ ). When using an 8-bit data bus, this pin functions as A0. When used as A0 (i.e., the BUSW pin is low), then the pin takes on the timing of the other address pins, as opposed to the strobe timing. This line is an output when the IMP is the bus master and is an input otherwise.

### LDS/DS—Lower Data Strobe/Data Strobe

This bidirectional line controls the flow of data on the data bus. When using a 16-bit data bus, this pin functions as lower data strobe ( $\overline{LDS}$ ). When using an 8-bit data bus, this pin functions as  $\overline{DS}$ . This line is an output when the IMP (M68000 core, SDMA or IDMA) is the bus master and is an input otherwise.

### DTACK—Data Transfer Acknowledge

This bidirectional signal indicates that the data transfer has been completed. DTACK can be generated internally in the chip-select logic either for an IMP bus master or for an external bus master access to an external address within the chip-select ranges. It will also be generated internally during any access to the on-chip dual-port RAM or internal regis-

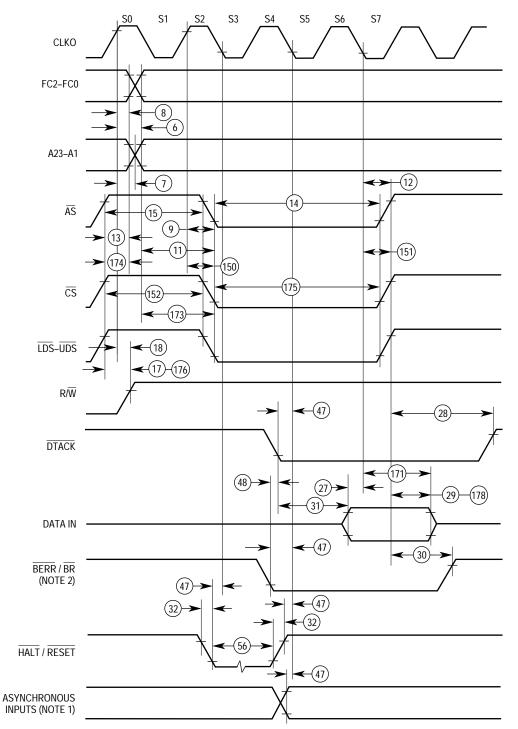

# 6.8 AC ELECTRICAL SPECIFICATIONS-IMP BUS MASTER CYCLES

(see Figure 6-2, Figure 6-3, Figure 6-4, and Figure 6-5))

|      |                                                                                                       |                                     | 16.67 | ' MHz | 20  | MHz | 25 I | MHz |      |

|------|-------------------------------------------------------------------------------------------------------|-------------------------------------|-------|-------|-----|-----|------|-----|------|

| Num. | Characteristic                                                                                        | Symbol                              | Min   | Max   | Min | Max | Min  | Max | Unit |

| 6    | Clock High to FC, Address Valid                                                                       | t <sub>CHFCADV</sub>                | 0     | 45    | 0   | 40  | 0    | 30  | ns   |

| 7    | Clock High to Address, Data Bus High Impedance (Maximum)                                              | t <sub>CHADZ</sub>                  |       | 50    |     | 42  | _    | 33  | ns   |

| 8    | Clock High to Address, FC Invalid (Mini-<br>mum)                                                      | t <sub>CHAFI</sub>                  | 0     | _     | 0   | —   | 0    | _   | ns   |

| 9    | Clock High to $\overline{AS}$ , $\overline{DS}$ Asserted (see Note 1)                                 | t <sub>CHSL</sub>                   | 3     | 30    | 3   | 25  | 3    | 20  | ns   |

| 11   | Address. FC Valid to $\overline{AS}$ , $\overline{DS}$ Asserted (Read) AS Asserted Write (see Note 2) | t <sub>AFCVSL</sub>                 | 15    | _     | 12  | _   | 10   | _   | ns   |

| 12   | Clock Low to $\overline{AS}$ , $\overline{DS}$ Negated (see Note 1)                                   | t <sub>CLSH</sub>                   | _     | 30    |     | 25  |      | 20  | ns   |

| 13   | $\overline{\text{AS}}$ , $\overline{\text{DS}}$ Negated to Address, FC Invalid (see Note 2)           | t <sub>SHAFI</sub>                  | 15    | _     | 12  | _   | 10   | _   | ns   |

| 14   | $\overline{\text{AS}}$ (and $\overline{\text{DS}}$ Read) Width Asserted (see Note 2)                  | t <sub>SL</sub>                     | 120   | _     | 100 | _   | 80   | _   | ns   |

| 14A  | DS Width Asserted, Write (see Note 2)                                                                 | t <sub>DSL</sub>                    | 60    |       | 50  |     | 40   | _   | ns   |

| 15   | $\overline{\text{AS}}$ , $\overline{\text{DS}}$ Width Negated (see Note 2)                            | t <sub>SH</sub>                     | 60    | —     | 50  | _   | 40   | —   | ns   |

| 16   | Clock High to Control Bus High Impedance                                                              | t <sub>CHCZ</sub>                   |       | 50    | —   | 42  |      | 33  | ns   |

| 17   | $\overline{AS}$ , $\overline{DS}$ Negated to R/ $\overline{W}$ Invalid (see Note 2)                   | t <sub>SHRH</sub>                   | 15    | —     | 12  |     | 10   |     | ns   |

| 18   | Clock High to R/W High (see Note 1)                                                                   | t <sub>CHRH</sub>                   | _     | 30    | _   | 25  | _    | 20  | ns   |

| 20   | Clock High to $R/\overline{W}$ Low (see Note 1)                                                       | t <sub>CHRL</sub>                   | _     | 30    | _   | 25  |      | 20  | ns   |

| 20A  | $\overline{\text{AS}}$ Asserted to R/W Low (Write) (see Notes 2 and 6)                                | t <sub>ASRV</sub>                   | _     | 10    |     | 10  |      | 7   | ns   |

| 21   | Address FC Valid to $R/\overline{W}$ Low (Write) (see Note 2)                                         | t <sub>AFCVRL</sub>                 | 15    | _     | 12  | _   | 10   | _   | ns   |

| 22   | $R/\overline{W}$ Low to $\overline{DS}$ Asserted (Write) (see Note 2)                                 | t <sub>RLSL</sub>                   | 30    |       | 25  |     | 20   | _   | ns   |

| 23   | Clock Low to Data-Out Valid                                                                           | t <sub>CLDO</sub>                   | _     | 30    | _   | 25  | _    | 20  | ns   |

| 25   | AS, DS, Negated to Data-Out Invalid (Write) (see Note 2)                                              | t <sub>SHDOI</sub>                  | 15    | _     | 12  | _   | 10   | _   | ns   |

| 26   | Data-Out Valid to $\overline{\text{DS}}$ Asserted (Write) (see Note 2)                                | t <sub>DOSL</sub>                   | 15    | _     | 12  | _   | 10   | _   | ns   |

| 27   | Data-In Valid to Clock Low (Setup Time on Read) (see Note 5)                                          | t <sub>DICL</sub>                   | 7     | _     | 6   | _   | 5    | _   | ns   |

| 28   | AS, DS Negated to DTACK Negated (Asynchronous Hold) (see Note 2)                                      | t <sub>SHDAH</sub>                  | 0     | 110   | 0   | 95  | 0    | 75  | ns   |

| 29   | $\overline{\text{AS}}$ , $\overline{\text{DS}}$ Negated to Data-In Invalid (Hold Time on Read)        | t <sub>SHDII</sub>                  | 0     | _     | 0   | —   | 0    | _   | ns   |

| 30   | AS, DS Negated to BERR Negated                                                                        | t <sub>SHBEH</sub>                  | 0     | —     | 0   |     | 0    |     | ns   |

| 31   | DTACK Asserted to Data-In Valid (Setup Time) (see Notes 2 and 5)                                      | t <sub>DALDI</sub>                  |       | 50    | _   | 42  | —    | 33  | ns   |

| 32   | HALT and RESET Input Transition Time                                                                  | t <sub>RHr</sub> , t <sub>RHf</sub> |       | 150   | —   | 150 |      | 150 | ns   |

| 33   | Clock High to BG Asserted                                                                             | t <sub>CHGL</sub>                   | _     | 30    | _   | 25  | _    | 20  | ns   |

| 34   | Clock High to BG Negated                                                                              | t <sub>CHGH</sub>                   |       | 30    | _   | 25  |      | 20  | ns   |

| 35   | $\overline{BR}$ Asserted to $\overline{BG}$ Asserted (see Note 11)                                    | t <sub>BRLGL</sub>                  | 2.5   | 4.5   | 2.5 | 4.5 | 2.5  | 4.5 | clks |

| 36   | BR Negated to BG Negated (see Note 7)                                                                 | t <sub>BRHGH</sub>                  | 1.5   | 2.5   | 1.5 | 2.5 | 1.5  | 2.5 | clks |

NOTES:

- Setup time for the asynchronous inputs IPL2–IPL0 guarantees their recognition at the next falling edge of the clock.

- 2. BR need fall at this time only to insure being recognized at the end of the bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is linear between 0.8 volts and 2.0 volts.

Figure 6-2. Read Cycle Timing Diagram

## 6.13 AC ELECTRICAL SPECIFICATIONS—CHIP-SELECT TIMING INTERNAL MASTER (see Figure 6-14)

|      |                                                                         |                       | 16.67 | ' MHz | 20  | MHz | 25 I | MHz |      |

|------|-------------------------------------------------------------------------|-----------------------|-------|-------|-----|-----|------|-----|------|

| Num. | Characteristic                                                          | Symbol                | Min   | Мах   | Min | Max | Min  | Max | Unit |

| 150  | Clock High to $\overline{CS}$ , $\overline{IACK}$ Low (see Note 2)      | t <sub>CHCSIAKL</sub> | 0     | 40    | 0   | 35  | 0    | 27  | ns   |

| 151  | Clock Low to CS, IACK High (see Note 2)                                 | t <sub>CLCSIAKH</sub> | 0     | 40    | 0   | 35  | 0    | 27  | ns   |

| 152  | CS Width Negated                                                        | t <sub>CSH</sub>      | 60    | _     | 50  | _   | 40   | _   | ns   |

| 153  | Clock High to DTACK Low (0 Wait State)                                  | t <sub>CHDTKL</sub>   | _     | 45    |     | 40  | _    | 30  | ns   |

| 154  | Clock Low to DTACK Low (1–6 Wait States)                                | t <sub>CLDTKL</sub>   | _     | 30    | _   | 25  | _    | 20  | ns   |

| 155  | Clock Low to DTACK High                                                 | t <sub>CLDTKH</sub>   | —     | 40    | —   | 35  | —    | 27  | ns   |

| 156  | Clock High to BERR Low (see Note 1)                                     | t <sub>CHBERL</sub>   | _     | 40    |     | 35  | _    | 27  | ns   |

| 157  | Clock Low to $\overline{\text{BERR}}$ High Impedance (see Note 1)       | t <sub>CLBERH</sub>   | _     | 40    | _   | 35  | _    | 27  | ns   |

| 158  | DTACK High to DTACK High Impedance                                      | t <sub>DTKHDTKZ</sub> | _     | 15    |     | 15  | _    | 10  | ns   |

| 171  | Input Data Hold Time from S6 Low                                        | t <sub>IDHCL</sub>    | 5     | _     | 5   | _   | 5    | _   | ns   |

| 172  | CS Negated to Data-Out Invalid (Write)                                  | t <sub>CSNDOI</sub>   | 10    | —     | 10  | —   | 7    | —   | ns   |

| 173  | Address, FC Valid to CS Asserted                                        | t <sub>AFVCSA</sub>   | 15    | _     | 15  | _   | 15   | _   | ns   |

| 174  | CS Negated to Address, FC Invalid                                       | t <sub>CSNAFI</sub>   | 15    | _     | 15  | —   | 12   | _   | ns   |

| 175  | CS Low Time (0 Wait States)                                             | t <sub>CSLT</sub>     | 120   | _     | 100 | _   | 80   | —   | ns   |

| 176  | $\overline{\text{CS}}$ Negated to R/ $\overline{\text{W}}$ Invalid      | t <sub>CSNRWI</sub>   | 10    | _     | 10  | _   | 7    | _   | ns   |

| 177  | $\overline{\text{CS}}$ Asserted to R/ $\overline{\text{W}}$ Low (Write) | t <sub>CSARWL</sub>   | _     | 10    |     | 10  |      | 8   | ns   |

| 178  | CS Negated to Data-In Invalid (Hold Time on Read)                       | t <sub>CSNDII</sub>   | 0     | _     | 0   |     | 0    |     | ns   |

NOTE:

1. This specification is valid only when the ADCE or WPVE bits in the SCR are set.

2. For loading capacitance less than or equal to 50 pF, subtract 4 ns from the maximum value given.

3. Since  $\overline{AS}$  and  $\overline{CS}$  are asserted/negated on the same CLKO edges, no  $\overline{AS}$  to  $\overline{CS}$  relative timings can be specified. However,  $\overline{CS}$  timings are given relative to a number of other signals, in the same manner as  $\overline{AS}$ . See Figure 6-2 and Figure 6-3 for diagrams.

## **D.5.6 External Cycles Examples**

If the MC68302 is the current bus master and no other internal or external resources are arbitrating for the bus, then the IDMA will obtain bus mastership and perform the data movement cycles when the DREQ signal meets the asynchronous setup time prior to the falling edge of clock.

Figure D-7 shows the sequence of a peripheral requesting a data transfer, the IDMA reading data from memory and then writing the data to the peripheral. The source and destination size are the same for this case. DREQ is sampled on the falling edge of CLK and causes the BGACK signal to assert at the conclusion of the current M68000 core bus cycle. The IDMA performs a read cycle using the SAPR to obtain data and then performs a write cycle to place data in the address specified in the DAPR. The fact that DACK asserts in the write cycle indicates that data is being transferred to the requesting peripheral. Note that the BR and BG pins are not affected by the IDMA in this example. They only activate when the device is in the disable CPU mode (see 3.8.4 Disable CPU Logic (M68000)).

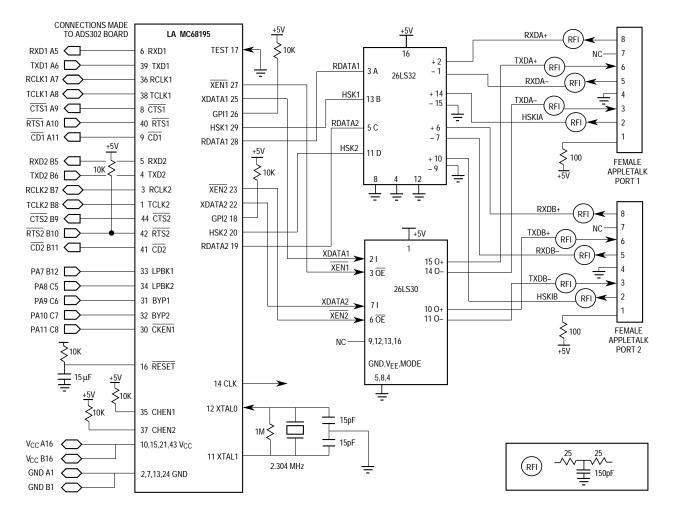

Figure D-32. Local Talk Adaptor Board

- SDC2—Serial Data Strobe Control 2

- 0 = SDS2 signal is asserted during the B2 channel.

- 1 = SDS1 signal is asserted during the B2 channel.

- SDC1—Serial Data Strobe Control 1

- 0 = SDS1 signal is asserted during the B1 channel.

- 1 = SDS2 signal is asserted during the B1 channel.

B2RB, B2RA—B2 Channel Route in IDL/GCI Mode or CH-3 Route in PCM Mode

- 00 = Channel not supported.

- 01 = Route channel to SCC1.

- 10 = Route channel to SCC2 (a MSC2 is cleared).

- 11 = Route channel to SCC3 (if MSC3 is cleared).

- B1 RB, B1 RA—B1 Channel Route in IDL/GCI Mode or CH-2 Route in PCM Mode

- 00 = Channel not supported.

- 01 = Route channel to SCC1.

- 10 = Route channel to SCC2 (a MSC2 is cleared).

- 11 = Route channel to SCC3 (if MSC3 is cleared).

DRB, DRA-D Channel Route in IDL/GCI Mode or CH-1 Route in PCM Mode

- 00 = Channel not supported.

- 01 =Route channel to SCC1.

- 10 = Route channel to SCC2 (a MSC2 is cleared).

- 11 = Route channel to SCC3 (if MSC3 is cleared).

MSC3—SCC3 Connection

- 0 = SCC3 is connected to the multiplexed serial interface.

- 1 = SCC3 is not connected to the multiplexed serial interface.

MSC2—SCC2 Connection

- 0 = SCC2 is connected to the multiplexed serial interface.

- 1 = SCC2 is not connected to the multiplexed serial interface.

MS1, MS0—Mode Supported

- 00 = NMSI mode.

- 01 = PCM mode.

- 10 = IDL mode.

- 11 = GCI interface.

**E.1.1.1.3 Serial Interface Mask Register (SIMASK).** This 16-bit register is located at offset \$8B2. The SIMASK register is used to configure which bits on the B1 and B2 channels are used in the GCI and IDL modes. Bit 0 of SIMASK is the first bit transmitted and received on B1.

| 15 | 8 | 7  | 0 |

|----|---|----|---|

| B2 |   | B1 |   |

**E.1.1.4.1 Receive BD Control/Status Word.** To initialize the buffer, the user should write bits 15-12 and clear bits 11-10 and 5-0. The IMP clears bit 15 when the buffer is closed and sets bits 5-0 depending on which error occurred.

E—Empty

- 0 = This data buffer is full or has been closed due to an error condition.

- 1 = This data buffer is empty; must be set by the user to enable reception into this buffer.

- X—External Buffer

- 0 = The data buffer associated with this BD is in internal dual-port RAM.

- 1 = The data buffer associated with this BD is in external memory.

- W-Wrap (final BD in table)

- 0 = This is not the last BD in the receive BD table.

- 1 = This is the last BD in the receive BD table.

I—Interrupt (The RXF bit in the event register is set when a complete frame is received, independent of the I bit.)

- 0 = The RXB bit in the event register is not set when this buffer is closed.

- 1 = The RXB bit (or RXF bit, if this is the last buffer in a frame) in the event register is set when this buffer is closed.

- L—Last in Frame

- 0 = This buffer is not the last buffer in a frame.

- 1 = This buffer is the last buffer in a frame.

F—First in Frame

- 0 = This buffer is not the first buffer in a frame.

- 1 = This buffer is the first buffer in a frame.

- Bits 9–6—Reserved for future use

- LG—Rx Frame Length Violation

- 0 = No frame length violation occurred.

- 1 = A frame length violation was detected. Up to the number of bytes specified in the maximum frame length will be written to the buffer (or buffers, if multiple buffers per frame).

NO-Rx Nonoctet Aligned Frame

- 0 = An octet aligned frame was received.

- 1 = A nonoctet aligned frame was received.

- AB-Rx Abort Sequence

- 0 = No abort was received.

- 1 = A minimum of seven ones was received during frame reception.

# APPENDIX F DESIGN CHECKLIST

When integrating the MC68302 into an application, it may be helpful to go through the following design checklist. In this checklist are a number of common problems and their resolutions that have been found while debugging real MC68302 applications.

#### 1. Version, Mask

Older versions of the MC68302—called Rev A and Rev B with masks "B14M" written on the device—do not contain all the features listed in this manual. These devices have ceased production and are longer available. A newer version called Rev C, which is identified by mask number "C65T" or later, contains all the features listed in this manual. The missing features in the old versions include clock output control and a few other minor differences.

#### 2. External Pin Configurations

A good checklist of external pin configurations may be found in D.1 Minimum System Configuration. Common problems are also listed in some of the following paragraphs.

#### 3. Clock Present

If you are using an external clock source to the 68302, make sure that it is driving the clock input within 10 msec of powerup. Otherwise, part damage can occur.

### 4. AVEC, DTACK

If  $\overline{\text{AVEC}}$  is not used, it needs to be pulled high (to + 5 V); otherwise, erratic behavior and bus cycles may occur. A pullup resistor may be used, if desired. If  $\overline{\text{AVEC}}$  is used, it should be asserted instead of  $\overline{\text{DTACK}}$  (not in addition to  $\overline{\text{DTACK}}$ ) during interrupt acknowledge cycles.

#### 5. Pullup, DTACK

Sometimes a 10K-ohm resistor may not be strong enough to pull up DTACK to provide adequate rise times to the DTACK signal. This is a loading-dependent issue.

### 6. Pullup, Floating BR, FRZ, BUSW

Unexpected behavior can result if the signals BR, FRZ, BUSW, or other inputs are left floating. Of these, the most common mistake is to leave FRZ floating.

If no external requests are made, BR may be pulled directly high. If external requests are made, BR may need to be pulled high through a resistor, such as 1 K ohm, to guarantee adequate BR rise time to meet bus arbitration specifications.

### 7. Pullup, IPL

IPL lines should be pulled high if not used. These signals may be pulled directly high, if desired.

#### 8. **RESET**, Rise Time

The rise time of the RESET and HALT pins after a total system reset must be within

Exception 3-66 Processing 2-7 Exceptions 3-14 Grant (BG) 5-11 Grant Acknowledge (BGACK) 5-11 Latencies 3-58 Master 2-7, 3-56, 3-58, 4-5 Request (BR) 5-11 SDMA Retry 4-41 Signal Summary 5-13 Bus Error on SDMA Access 4-41 Bus Master 4-5 BUSW 2-1, 3-39, 5-6, See Signals, See Timers

#### С

C/I Channel 4-141 Carrier Detect Lost 4-61 CD 4-28, 4-40 **CEPT** 4-19 Chip-Select 2-13 Address Decode Conflict 3-44 AS 3-42 Base Address 3-48 Base Register 3-45 BERR 3-44, 3-46 Block Sizes 3-45 CS0 3-44, 3-46, 3-55, 5-23 DTACK 3-42, 3-47, 3-48 **EMWS 3-43 Option Register 3-45** Priority 3-43 Read-Only 3-48 **RESET** 3-44 **RMSCT 3-45** Test and Set 3-45 Write Protect Violation 3-44 Write-Only 3-48 **Chip-Select Timing 6-24** Circular Queue 4-32 Clear-to-Send Report 4-63 Clock Asynchronous Baud Rate 4-26 **Baud Rate Generator 4-25** CLKO 3-49, 5-5 Clock Divider 4-26 Crystal 3-50

EXTAL 3-49 Synchronous Baud Rate 4-27 XTAL 3-49 Clock Divider 4-26 CMOS Level 5-2 Command 4-5 ENTER HUNT MODE Command 4-36, 4-37, 4-54, 4-126, 4-128, 4-130 **RESET BCS CALCULATION Command** 4-101 **RESTART TRANSMIT Command 4-73**, 4-92, 4-128 STOP TRANSMIT Command 4-36, 4-37, 4-42, 4-48, 4-49, 4-69, 4-71, 4-128, 4-130 TIMEOUT Command 4-142 TRANSMIT ABORT REQUEST Command 4-142 Command Execution Latency 4-7 Command Register 4-5 **Communications Processor 4-1** Configuration MC68302 IMP Control 2-12 System Registers 2-14 CP 1-6, 4-1 **CQFP** 7-2 CR 4-5 CS0 3-44, 3-46, 3-55, 5-23 CTS 4-28, 4-40

### D

**DACK 5-20** Data Type Asynchronous Bit Rate Adaption 4-119 **FIFO** 4-120 **Overrun Error** 4-120 Rx BD 4-120 SCCE 4-123 SCCM 4-124 Synchronization Error 4-120 Synchronous Bit Rate Adaption 4-118 **Terminal Equipment 4-117** Transmitter Underrun 4-120 Tx BD 4-122 V.110 80-Bit Frames 4-119 V.110 Event Register 4-123 V.110 Mask Register 4-124

#### MC68302 USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

L1SY0 4-129 **NTSYN 4-131** PCM Highway 4-129 **Promiscuous Operation 4-124 RESTART TRANSMIT Command 4-128 REVD** 4-131 **RTS** 4-129 **RXBD** 4-132 SCCE 4-135 SCCM 4-136 STOP TRANSMIT Command 4-128, 4-130 SYN1-SYN2 4-129 Totally Transparent 4-124 Transmitter Underrun 4-130 Transparent Event Register 4-132, 4-134 Transparent Mask Register 4-136 Transparent Memory Map 4-127 **Transparent Synchronization 4-128** Tx BD 4-133 **Transparent Controller 4-124** Transparent Mode 4-140 Transparent Mode Register 4-131 TTL Levels 5-2

### U

**UART** 4-41 Address Recognition 4-50 Asynchronous DDCMP 4-46 Automatic Address Recognition 4-48 Automatic Multidrop Mode 4-50 **Break Characters 4-48 BREAK Sequence** 4-55 BRKCR 4-48, 4-49 Character Length 4-57 Control Characters 4-51 **DDCMP** 4-57 **DSR** 4-56 **ENTER HUNT MODE Command 4-54** FIFO 4-53, 4-54, 4-57 Flow Control 4-51 Fractional Stop Bits 4-46, 4-55 Frame Format 4-44 Framing Error 4-55 FRZ 4-57 Idle Characters 4-47 **IDLE Sequence** 4-55

Multidrop Configuration 4-45 Multidrop Environment 4-50 Multidrop Mode 4-57 Noise Error 4-55 Overrun 4-61 Parity Error 4-55 Parity Mode 4-56 Preamble Sequence 4-63 **PROFIBUS** 4-44 Programming Example 4-67 Reception of Idles 4-61 **RTS** 4-57 RX 4-54, 4-55, 4-60, 4-66 **Rx BD 4-58** SCCE 4-64 **SCCM 4-66** Send Break 4-53 Send Preamble 4-54 Stop Bit 4-58 **STOP TRANSMIT Command 4-49** Transmission Error 4-54 TX 4-53, 4-54, 4-62 Tx BD 4-62 **UADDR1** 4-50 UART Event Register 4-53, 4-60, 4-62, 4-64 **UART Mask Register 4-66** UART Memory Map 4-47 UART Mode Register 4-56 XOFF 4-51, 4-52, 4-67 XON 4-52, 4-67 UART Controller 4-44 User State 2-7 Using GCI 4-140 Using IDL 4-140

#### V

Value 3-38 Vector Generation Enable (VGE) 3-55 Interrupt 3-17, 3-21, 3-27 Number 2-8, 2-11, 3-22 Table 2-12 Vector Generation Enable 3-55 VMA 2-1, See Signals VPA 2-11, 5-12, See Signals