#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | <u>.</u>                                                                  |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1904-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | IDEX                |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants   |               |         |      |

|-------------|---------------|---------|------|

| RETLW       | DATA0         | ;Index0 | data |

| RETLW       | DATA1         | ;Index1 | data |

| RETLW       | DATA2         |         |      |

| RETLW       | DATA3         |         |      |

| my_function | on            |         |      |

| ; LOI       | IS OF CODE    |         |      |

| MOVLW       | LOW constan   | ts      |      |

| MOVWF       | FSR1L         |         |      |

| MOVLW       | HIGH consta   | nts     |      |

| MOVWF       | FSR1H         |         |      |

| MOVIW       | 0[FSR1]       |         |      |

| ; THE PROG  | RAM MEMORY IS | IN W    |      |

| TABI               | LE 3-5:               | SPECIAL   | FUNCTI       | ON REG         | SISTER S       | UMMAR        | Y (CON1     | INUED) |        |                      |                                 |

|--------------------|-----------------------|-----------|--------------|----------------|----------------|--------------|-------------|--------|--------|----------------------|---------------------------------|

| Addr               | Name                  | Bit 7     | Bit 6        | Bit 5          | Bit 4          | Bit 3        | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Ban                | k 2                   |           |              |                |                |              |             |        |        |                      |                                 |

| 10Ch               | LATA                  | PORTA Dat | ta Latch     |                |                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 10Dh               | LATB                  | PORTB Da  | ta Latch     |                |                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 10Eh               | LATC                  | PORTC Da  | ta Latch     |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATD <sup>(3)</sup>   | PORTD Da  | ta Latch     |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATE <sup>(3)</sup>   | -         | _            | _              | _              | _            | LATE2       | LATE1  | LATE0  | xxx                  | uuu                             |

| 111h<br>to<br>115h | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 116h               | BORCON                | SBOREN    | BORFS        | _              | _              | _            |             | _      | BORRDY | 10q                  | uuu                             |

| 117h               | FVRCON                | FVREN     | FVRRDY       | TSEN           | TSRNG          | _            | _           | ADFVR1 | ADFVR0 | 0q0000               | 0q0000                          |

| 118h<br>to<br>11Fh | _                     | Unimpleme | nted         |                | •              |              | •           | •      |        | _                    | _                               |

| Ban                | k 3                   |           |              |                |                |              |             |        |        |                      |                                 |

| 18Ch               | ANSELA                | _         | —            | ANSA5          | —              | ANSA3        | ANSA2       | ANSA1  | ANSA0  | 1- 1111              | 11 1111                         |

| 18Dh               | ANSELB                | _         | —            | ANSB5          | ANSB4          | ANSB3        | ANSB2       | ANSB1  | ANSB0  | 11 1111              | 11 1111                         |

| 18Eh               | —                     | Unimpleme | nted         |                | •              |              |             | •      |        | _                    | _                               |

| 18Fh               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 190h               | ANSELE <sup>(3)</sup> | _         | _            | _              | _              | _            | ANSE2       | ANSE1  | ANSE0  | 111                  | 111                             |

| 191h               | PMADRL                | Program M | emory Addre  | ess Register   | Low Byte       |              |             |        |        | 0000 0000            | 0000 0000                       |

| 192h               | PMADRH                | (2)       |              |                | ess Register I | High Byte    |             |        |        | 1000 0000            | 1000 0000                       |

| 193h               | PMDATL                | Program M | emory Read   | I Data Regist  | ter Low Byte   |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 194h               | PMDATH                | _         | _            | Program M      | emory Read     | Data Registe | r High Byte |        |        | xx xxxx              | uu uuuu                         |

| 195h               | PMCON1                | (2)       | CFGS         | LWLO           | FREE           | WRERR        | WREN        | WR     | RD     | 1000 x000            | 1000 q000                       |

| 196h               | PMCON2                | Program M | emory Conti  | rol Register 2 | 2              |              |             |        |        | 0000 0000            | 0000 0000                       |

| 197h               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    |                                 |

| 198h               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 199h               | RCREG                 | USART Re  | ceive Data F | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |

| 19Ah               | TXREG                 | USART Tra | Insmit Data  | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |

| 19Bh               | SPBRG                 |           |              |                | BRG            | <7:0>        |             |        |        | 0000 0000            | 0000 0000                       |

| 19Ch               | SPBRGH                |           |              |                | BRG<           | <15:8>       |             |        |        | 0000 0000            | 0000 0000                       |

| 19Dh               | RCSTA                 | SPEN      | RX9          | SREN           | CREN           | ADDEN        | FERR        | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| 19Eh               | TXSTA                 | CSRC      | TX9          | TXEN           | SYNC           | SENDB        | BRGH        | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| 19Fh               | BAUD1CON              | ABDOVF    | RCIDL        | _              | SCKP           | BRG16        | _           | WUE    | ABDEN  | 01-0 0-00            |                                 |

| Ban                |                       | 1         | 1            |                |                | 1            | 1           |        | L      |                      | 1                               |

| 20Ch               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

|                    | WPUB                  | WPUB7     | WPUB6        | WPUB5          | WPUB4          | WPUB3        | WPUB2       | WPUB1  | WPUB0  | 1111 1111            | 1111 1111                       |

| 20Eh               | _                     | Unimpleme |              |                |                |              |             |        |        | _                    | _                               |

| 20Fh               | _                     | Unimpleme |              |                |                |              |             |        |        | _                    | _                               |

| 210h               | WPUE                  |           | _            | _              | _              | WPUE3        |             | _      | _      | 1                    | 1                               |

|                    |                       |           |              |                |                |              |             |        |        | ±                    | 1                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-5

Bank 5

211h to 21Fh

29Fh

28Ch

\_ \_

Bank 6

| Бап      | ĸo                                                                                                                                                                    |               |   |   |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---|--|--|

| 30Ch     | _                                                                                                                                                                     | Unimplemented | - | _ |  |  |

| <br>31Fh |                                                                                                                                                                       |               |   |   |  |  |

| Legen    | Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.<br>Shaded locations are unimplemented, read as '0'. |               |   |   |  |  |

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16LF1904/7 only. Note 1:

Unimplemented

Unimplemented

2:

3:

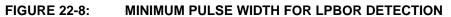

### 5.3 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) is an essential part of the Reset subsystem. Refer to Figure 5-1 to see how the BOR interacts with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit ( $\overline{\text{BOR}}$ ) is changed to indicate that a BOR Reset has occurred. The same bit is set for both the BOR and the LPBOR. Refer to Register 5-2.

### 5.3.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Word 2. When the device is erased, the LPBOR module defaults to disabled.

### 5.3.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is to be OR'd together with the Reset signal of the BOR module to provide the generic BOR signal, which goes to the PCON register and to the power control block.

### 5.4 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Word 1 and the LVP bit of Configuration Word 2 (Table 5-2).

### TABLE 5-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

### 5.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

### 5.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.5** "**PORTE Registers**" for more information.

### 5.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0** "**Watchdog Timer**" for more information.

#### 5.6 **RESET Instruction**

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 5-4 for default conditions after a RESET instruction has occurred.

### 5.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Word 2. See **Section 5.7 "Stack Overflow/Underflow Reset"** for more information.

### 5.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

### 5.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of Configuration Word 1.

### 5.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 6.0 "Oscillator Module"** for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution immediately (see Figure 5-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

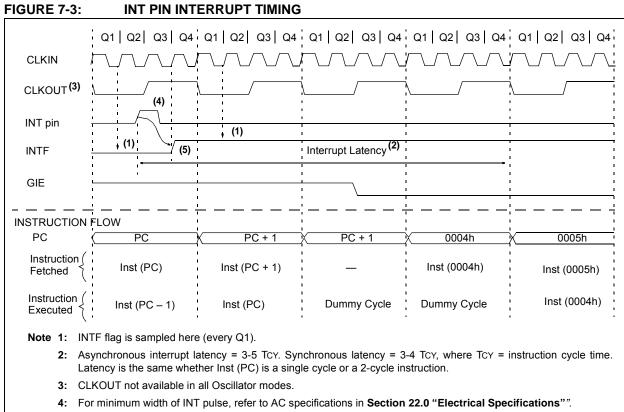

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

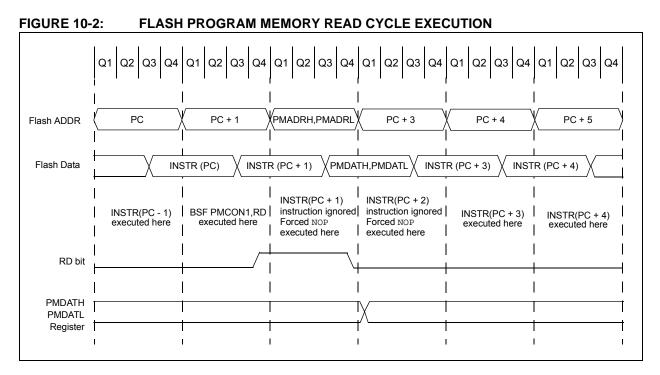

### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program \* memory at the memory address: PROG\_ADDR\_HI : PROG\_ADDR\_LO data will be returned in the variables; \* PROG\_DATA\_HI, PROG\_DATA\_LO BANKSEL PMADRL ; Select Bank for PMCON registers MOVLW PROG\_ADDR\_LO ; MOVWF PMADRL ; Store LSB of address PROG\_ADDR\_HI MOVLW ; MOVWL PMADRH ; Store MSB of address BCF PMCON1,CFGS ; Do not select Configuration Space BSF PMCON1,RD ; Initiate read NOP ; Ignored (Figure 10-1) NOP ; Ignored (Figure 10-1) MOVF PMDATL,W ; Get LSB of word MOVWF PROG\_DATA\_LO ; Store in user location ; Get MSB of word MOVF PMDATH,W MOVWF PROG\_DATA\_HI ; Store in user location

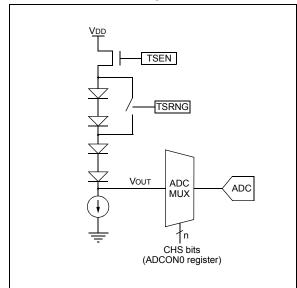

### 14.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between of  $-40^{\circ}$ C and  $+85^{\circ}$ C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

### 14.1 Circuit Operation

Figure 14-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 14-1 describes the output characteristics of the temperature indicator.

### EQUATION 14-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 14-1: TEMPERATURE CIRCUIT DIAGRAM

### 14.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 14-1 shows the recommended minimum VDD vs. range setting.

TABLE 14-1: RECOMMENDED VDD VS. RANGE

| Min. Vdd, TSRNG = 1 | Min. VDD, TSRNG = 0 |  |  |  |  |  |

|---------------------|---------------------|--|--|--|--|--|

| 3.6V                | 1.8V                |  |  |  |  |  |

### 14.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 15.0** "**Analog-to-Digital Converter (ADC) Module**" for detailed information.

### 14.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| R/W-0/0          | R/W-0/0                                | R/W-0/0                                                        | R/W-0/0        | U-0            | U-0             | R/W-0/0         | R/W-0/0      |

|------------------|----------------------------------------|----------------------------------------------------------------|----------------|----------------|-----------------|-----------------|--------------|

| ADFM             |                                        | ADCS<2:0>                                                      |                |                | —               | ADPRE           | EF<1:0>      |

| bit 7            | ·                                      |                                                                |                | •              | •               |                 | bit (        |

| Legend:          |                                        |                                                                |                |                |                 |                 |              |

| R = Readable     | bit                                    | W = Writable                                                   | bit            | U = Unimpler   | nented bit, rea | id as '0'       |              |

| u = Bit is unch  | nanged                                 | x = Bit is unkr                                                | nown           | -n/n = Value a | at POR and BO   | OR/Value at all | other Resets |

| '1' = Bit is set |                                        | '0' = Bit is cle                                               | ared           |                |                 |                 |              |

| bit 6-4          | loaded.<br>0 = Left jus<br>loaded.     | tified. Six Least                                              | Significant bi | ts of ADRESL a |                 |                 |              |

|                  | 100 = Fosc<br>101 = Fosc<br>110 = Fosc | :/8<br>:/32<br>(clock supplied fi<br>:/4<br>:/16               |                |                |                 |                 |              |

| bit 3-2          | Unimpleme                              | nted: Read as '                                                | 0'             |                |                 |                 |              |

| bit 1-0          | 00 = VREF+<br>01 = Reser               | :0>: A/D Positive<br>is connected to<br>ved<br>is connected to | VDD            |                | ation bits      |                 |              |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 22.0 "Electrical Specifications"** for details.

### REGISTER 15-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u          | R/W-x/u                                 | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|-----------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| _                | —                                       | —                 | _                                                     | —                                  | _       | ADRE    | S<9:8>  |  |

| bit 7            |                                         |                   |                                                       |                                    |         |         | bit 0   |  |

|                  |                                         |                   |                                                       |                                    |         |         |         |  |

| Legend:          |                                         |                   |                                                       |                                    |         |         |         |  |

| R = Readable I   | bit                                     | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper two bits of 10-bit conversion result

## **REGISTER 15-6:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADRES<7:0> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

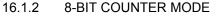

## 16.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 16-1 is a block diagram of the Timer0 module.

### 16.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 16.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

### FIGURE 16-1: BLOCK DIAGRAM OF THE TIMER0

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge is determined by the TMR0SE bit in the OPTION\_REG register.

### 17.10 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), shown in Register 17-2, is used to control Timer1 gate.

| R/W-0/u          | R/W-0/u                                                                                                                                                                                        | R/W-0/u                                                                                                                                                                                                                                                                                             | R/W-0/u                                       | R/W/HC-0/u                        | R-x/x            | R/W-0/u  | R/W-0/u      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|------------------|----------|--------------|--|

| TMR1GE           | T1GPOL                                                                                                                                                                                         | T1GTM                                                                                                                                                                                                                                                                                               | T1GSPM                                        | T1GGO/<br>DONE                    | T1GVAL           | T1GSS    | S<1:0>       |  |

| bit 7            |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                     |                                               |                                   |                  |          | bit C        |  |

| Legend:          |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                     |                                               |                                   |                  |          |              |  |

| R = Readable     | e bit                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                                                                                        | bit                                           | U = Unimpler                      | nented bit, read | d as '0' |              |  |

| u = Bit is uncl  | hanged                                                                                                                                                                                         | x = Bit is unkr                                                                                                                                                                                                                                                                                     | nown                                          |                                   | at POR and BC    |          | other Resets |  |

| '1' = Bit is set | 5                                                                                                                                                                                              | '0' = Bit is clea                                                                                                                                                                                                                                                                                   | ared                                          | HC = Bit is cle                   | eared by hardw   | /are     |              |  |

| bit 7            | If TMR1ON =<br>This bit is ign<br>If TMR1ON =<br>1 = Timer1 c                                                                                                                                  | ored<br><u>1</u> :                                                                                                                                                                                                                                                                                  | rolled by the Ti                              | mer1 gate fundate fundate         | otion            |          |              |  |

| bit 6            | <b>T1GPOL:</b> Tin<br>1 = Timer1 g                                                                                                                                                             | <b>T1GPOL:</b> Timer1 Gate Polarity bit<br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                                                                                       |                                               |                                   |                  |          |              |  |

| bit 5            | <b>T1GTM:</b> Time<br>1 = Timer1 G<br>0 = Timer1 G                                                                                                                                             | er1 Gate Toggle<br>Gate Toggle mo                                                                                                                                                                                                                                                                   | e Mode bit<br>de is enabled<br>de is disabled | and toggle flip-                  |                  |          |              |  |

| bit 4            | <b>T1GSPM:</b> Tin<br>1 = Timer1 g                                                                                                                                                             | ner1 Gate Sing                                                                                                                                                                                                                                                                                      | le-Pulse Mode<br>se mode is ena               | bit<br>bled and is co             | ntrolling Timer1 | gate     |              |  |

| bit 3            | <b>T1GGO/DON</b><br>1 = Timer1 g                                                                                                                                                               | E: Timer1 Gate<br>ate single-puls                                                                                                                                                                                                                                                                   | e Single-Pulse<br>e acquisition is            | Acquisition Sta<br>ready, waiting | for an edge      | started  |              |  |

| bit 2            | T1GVAL: Tim<br>Indicates the                                                                                                                                                                   | <ul> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> <li>T1GVAL: Timer1 Gate Current State bit</li> <li>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.</li> <li>Unaffected by Timer1 Gate Enable (TMR1GE)</li> </ul> |                                               |                                   |                  |          |              |  |

| bit 1-0          | Unaffected by Timer1 Gate Enable (TMR1GE).<br><b>T1GSS&lt;1:0&gt;:</b> Timer1 Gate Source Select bits<br>00 = Timer1 gate pin<br>01 = Timer0 overflow output<br>10 = Reserved<br>11 = Reserved |                                                                                                                                                                                                                                                                                                     |                                               |                                   |                  |          |              |  |

### REGISTER 17-2: T1GCON: TIMER1 GATE CONTROL REGISTER

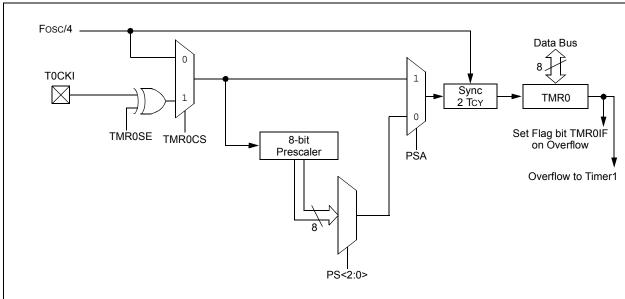

## 18.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- · Programmable clock and data polarity

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 18-1 and Figure 18-2.

### FIGURE 18-1: EUSART TRANSMIT BLOCK DIAGRAM

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz             |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                             | _          | _                           |                   | _          | _                           |                   | _          | _                           |                    | _          | _                           |  |

| 1200   | 1221                          | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1202              | 0.16       | 207                         | 1200               | 0.00       | 143                         |  |

| 2400   | 2404                          | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2404              | 0.16       | 103                         | 2400               | 0.00       | 71                          |  |

| 9600   | 9470                          | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9615              | 0.16       | 25                          | 9600               | 0.00       | 17                          |  |

| 10417  | 10417                         | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10417             | 0.00       | 23                          | 10165              | -2.42      | 16                          |  |

| 19.2k  | 19.53k                        | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.23k            | 0.16       | 12                          | 19.20k             | 0.00       | 8                           |  |

| 57.6k  | —                             | _          | _                           | 57.60k            | 0.00       | 7                           | —                 | _          | _                           | 57.60k             | 0.00       | 2                           |  |

| 115.2k | —                             | _          | —                           | _                 |            | _                           | _                 | _          | _                           | _                  | _          | —                           |  |

#### TABLE 18-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    |                  | _                             | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |  |  |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |  |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _                | _          | —                           |  |  |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | —                           | 9600              | 0.00       | 5                           | —                | _          | —                           |  |  |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | —                | _          | —                           |  |  |

| 19.2k  | —                | _                             | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           |  |  |

| 57.6k  | —                | _                             | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | —                | _          |                             |  |  |

| 115.2k | —                | _                             | _                           | —                | _          | _                           | —                 | _          | _                           | —                | _          | —                           |  |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                |            |                             |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz             |            | Fosc = 18.432 MHz           |                |            | Fosc = 16.000 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                             | —          | —                           |                | —          |                             |                |            | _                           | _              | —          | —                           |

| 1200   | —                             | —          | —                           | —              | —          | —                           | —              | —          | —                           | —              | —          | —                           |

| 2400   | _                             | _          | _                           | _              | _          | _                           | _              | _          | _                           | —              | _          | _                           |

| 9600   | 9615                          | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 56.82k                        | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 113.64k                       | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 5                           |

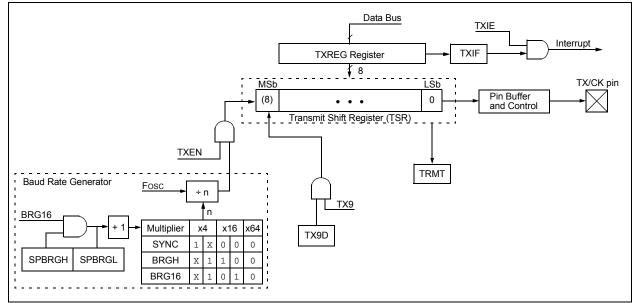

### 19.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16LF1904/6/7 device, the module drives the panels of up to four commons and up to 116 total segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- · Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- 19 Segment pins (PIC16LF1906 only)

- 29 Segment pins (PIC16LF1904/7 only)

• Static, 1/2 or 1/3 LCD Bias

Note: COM3 and SEG15 share the same physical pin on the PIC16LF1906, therefore SEG15 is not available when using 1/4 multiplex displays.

### 19.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 4 LCD Segment Enable registers (LCDSEn)

- Up to 16 LCD data registers (LCDDATAn)

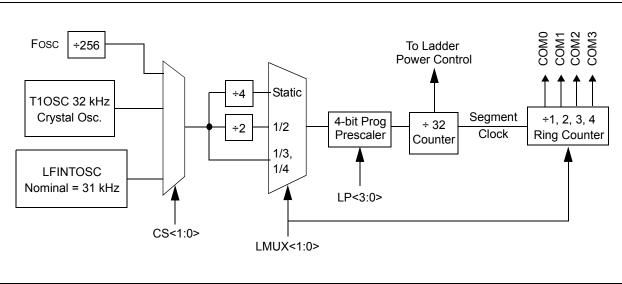

#### FIGURE 19-1: LCD DRIVER MODULE BLOCK DIAGRAM

### 19.2 LCD Clock Source Selection

The LCD module has three possible clock sources:

- Fosc/256

- T10SC

- LFINTOSC

The first clock source is the system clock divided by 256 (Fosc/256). This divider ratio is chosen to provide about 1 kHz output when the system clock is 8 MHz. The divider is not programmable. Instead, the LCD prescaler bits LP<3:0> of the LCDPS register are used to set the LCD frame clock rate.

The second clock source is the T1OSC. This also gives about 1 kHz when a 32.768 kHz crystal is used with the Timer1 oscillator. To use the Timer1 oscillator as a clock source, the T1OSCEN bit of the T1CON register should be set.

The third clock source is the 31 kHz LFINTOSC, which provides approximately 1 kHz output.

The second and third clock sources may be used to continue running the LCD while the processor is in Sleep.

Using bits CS<1:0> of the LCDCON register can select any of these clock sources.

#### 19.2.1 LCD PRESCALER

A 4-bit counter is available as a prescaler for the LCD clock. The prescaler is not directly readable or writable; its value is set by the LP<3:0> bits of the LCDPS register, which determine the prescaler assignment and prescale ratio.

The prescale values are selectable from 1:1 through 1:16.

### FIGURE 19-2: LCD CLOCK GENERATION

| Name                     | Bit 7                              | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Register<br>on Page |

|--------------------------|------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------------|

| INTCON                   | GIE                                | PEIE          | TMR0IE        | INTE          | IOCIE         | TMR0IF        | INTF          | IOCIF         | 65                  |

| LCDCON                   | LCDEN                              | SLPEN         | WERR          | _             | CS1           | CS0           | CS0 LMUX<1:0> |               | 173                 |

| LCDCST                   | —                                  |               |               | —             | —             | l             | _CDCST<2:0    | >             | 176                 |

| LCDDATA0                 | SEG7<br>COM0                       | SEG6<br>COM0  | SEG5<br>COM0  | SEG4<br>COM0  | SEG3<br>COM0  | SEG2<br>COM0  | SEG1<br>COM0  | SEG0<br>COM0  | 177                 |

| LCDDATA1                 | SEG15<br>COM0                      | SEG14<br>COM0 | SEG13<br>COM0 | SEG12<br>COM0 | SEG11<br>COM0 | SEG10<br>COM0 | SEG9<br>COM0  | SEG8<br>COM0  | 177                 |

| LCDDATA2 <sup>(1)</sup>  | SEG23<br>COM0                      | SEG22<br>COM0 | SEG21<br>COM0 | SEG20<br>COM0 | SEG19<br>COM0 | SEG18<br>COM0 | SEG17<br>COM0 | SEG16<br>COM0 | 177                 |

| LCDDATA3                 | SEG7<br>COM1                       | SEG6<br>COM1  | SEG5<br>COM1  | SEG4<br>COM1  | SEG3<br>COM1  | SEG2<br>COM1  | SEG1<br>COM1  | SEG0<br>COM1  | 177                 |

| LCDDATA4                 | SEG15<br>COM1                      | SEG14<br>COM1 | SEG13<br>COM1 | SEG12<br>COM1 | SEG11<br>COM1 | SEG10<br>COM1 | SEG9<br>COM1  | SEG8<br>COM1  | 177                 |

| LCDDATA5 <sup>(1)</sup>  | SEG23<br>COM1                      | SEG22<br>COM1 | SEG21<br>COM1 | SEG20<br>COM1 | SEG19<br>COM1 | SEG18<br>COM1 | SEG17<br>COM1 | SEG16<br>COM1 | 177                 |

| LCDDATA6                 | SEG7<br>COM2                       | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2  | SEG0<br>COM2  | 177                 |

| LCDDATA7                 | SEG15<br>COM2                      | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2  | SEG8<br>COM2  | 177                 |

| LCDDATA8 <sup>(1)</sup>  | SEG23<br>COM2                      | SEG22<br>COM2 | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | 177                 |

| LCDDATA9                 | SEG7<br>COM3                       | SEG6<br>COM3  | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3  | SEG2<br>COM3  | SEG1<br>COM3  | SEG0<br>COM3  | 177                 |

| LCDDATA10                | SEG15<br>COM3                      | SEG14<br>COM3 | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG9<br>COM3  | SEG8<br>COM3  | 177                 |

| LCDDATA11 <sup>(1)</sup> | SEG23<br>COM3                      | SEG22<br>COM3 | SEG20<br>COM3 | SEG19<br>COM3 | SEG18<br>COM3 | SEG17<br>COM3 | SEG16<br>COM3 | SEG15<br>COM3 | 177                 |

| LCDDATA12                | —                                  | _             |               | SEG28<br>COM0 | SEG27<br>COM0 | SEG26<br>COM0 | SEG25<br>COM0 | SEG24<br>COM0 | 177                 |

| LCDDATA15                | —                                  | —             | _             | SEG28<br>COM1 | SEG27<br>COM1 | SEG26<br>COM1 | SEG25<br>COM1 | SEG24<br>COM1 | 177                 |

| LCDDATA18                | —                                  | —             | _             | SEG28<br>COM2 | SEG27<br>COM2 | SEG26<br>COM2 | SEG25<br>COM2 | SEG24<br>COM2 | 177                 |

| LCDDATA21                | —                                  | —             | _             | SEG28<br>COM3 | SEG27<br>COM3 | SEG26<br>COM3 | SEG25<br>COM3 | SEG24<br>COM3 | 177                 |

| LCDPS                    | WFT                                | BIASMD        | LCDA          | WA            |               | LP<           | :3:0>         |               | 174                 |

| LCDREF                   | LCDIRE                             | _             | LCDIRI        | —             | VLCD3PE       | VLCD2PE       | VLCD1PE       | —             | 175                 |

| LCDRL                    | LRLAP<1:0> LRLBP<1:0> — LRLAT<2:0> |               |               |               |               |               |               |               | 184                 |

| LCDSE0                   | SE<7:0>                            |               |               |               |               |               |               |               | 177                 |

| LCDSE1                   | SE<15:8>                           |               |               |               |               |               |               |               |                     |

| LCDSE2                   | SE<23:16>                          |               |               |               |               |               |               |               | 177                 |

| LCDSE3                   |                                    | _             | _             |               |               | SE<28:24>     |               |               | 177                 |

| PIE2                     |                                    | _             | _             |               | _             | LCDIE         | _             | _             | 67                  |

| PIR2                     |                                    |               |               | —             | _             | LCDIF         |               |               | 69                  |

| T1CON                    | TMR1CS1                            | TMR1CS0       | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC        |               | TMR10N        | 139                 |

TABLE 19-8:

SUMMARY OF REGISTERS ASSOCIATED WITH LCD OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the LCD module.

Note 1: PIC16LF1904/7 only.

# FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

| 13 8 7                                                                          | -         | erat       | ions        | 0    |

|---------------------------------------------------------------------------------|-----------|------------|-------------|------|

| OPCODE c                                                                        | I         |            | f (FILE #)  |      |

| d = 0 for destination \<br>d = 1 for destination f<br>f = 7-bit file register a |           | ss         |             |      |

| Bit-oriented file register of<br>13 10 9                                        | · .       | atio<br>76 |             | 0    |

| OPCODE b (F                                                                     | BIT ‡     | #)         | f (FILE #)  |      |

| b = 3-bit bit address<br>f = 7-bit file register a                              | ddre      | ss         |             |      |

| Literal and control operat                                                      | ions      | 5          |             |      |

| General                                                                         | _         |            |             | •    |

| 13 8<br>OPCODE                                                                  | 3 7       |            | k (literal) | 0    |

|                                                                                 |           |            | k (literal) |      |

| k = 8-bit immediate va                                                          | alue      |            |             |      |

| CALL and GOTO instructions                                                      | s on      | ly         |             |      |

| 13 11 10                                                                        |           |            |             | 0    |

| OPCODE                                                                          | ł         | < (lit     | eral)       |      |

| MOVLP instruction only<br>13                                                    | 7         | 6          |             | 0    |

| OPCODE                                                                          |           |            | k (literal) |      |

| k = 7-bit immediate va                                                          |           | 5          | 4           | 0    |

| OPCODE                                                                          |           |            | k (literal) |      |

| k = 5-bit immediate va<br>BRA instruction only<br>13 9                          | alue<br>8 |            |             | 0    |

| OPCODE                                                                          | 0         |            | k (literal) | 0    |

| k = 9-bit immediate v                                                           | alue      |            |             |      |

| FSR Offset instructions 13 7                                                    | 6         | 5          |             | 0    |

| OPCODE                                                                          | n         |            | k (literal) |      |

| n = appropriate FSR<br>k = 6-bit immediate v                                    | alue      | !          |             |      |

| FSR Increment instructions                                                      |           |            | 3 2 1       | 0    |

| 13                                                                              |           |            | n m (mo     | ode) |

|                                                                                 |           |            |             |      |

| 13                                                                              | !         |            |             |      |

| 13<br>OPCODE<br>n = appropriate FSR                                             | !         |            |             | 0    |

#### TABLE 22-10: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated) |         |                                                                  |              |              |              |          |                                                                                                                                             |  |  |

|---------------------------------------------------------|---------|------------------------------------------------------------------|--------------|--------------|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                                            | Sym.    | Characteristic                                                   | Min.         | Тур†         | Max.         | Units    | Conditions                                                                                                                                  |  |  |

| 30                                                      | ТмсL    | MCLR Pulse Width (low)                                           | 2<br>5       | _            | _            | μS<br>μS | VDD = 3.0V, -40°C to +85°C<br>VDD = 3.0V                                                                                                    |  |  |

| 31                                                      | FWDTLP  | Low Frequency Internal Oscillator<br>Frequency                   | 19           | 33           | 52           | kHz      |                                                                                                                                             |  |  |

| 32                                                      | Tost    | Oscillator Start-up Timer Period <sup>(1)</sup>                  |              | 1024         | _            | Tosc     | (Note 2)                                                                                                                                    |  |  |

| 33*                                                     | TPWRT   | Power-up Timer Period, $\overline{PWRTE} = 0$                    | _            | 2048         | _            | Tosc     | Clocked by LFINTOSC                                                                                                                         |  |  |

| 34*                                                     | Tioz    | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset      | _            | —            | 2.0          | μS       |                                                                                                                                             |  |  |

| 35                                                      | VBOR    | Brown-out Reset Voltage: BORV = 0<br>BORV = 1                    | 2.55<br>1.80 | 2.70<br>1.90 | 2.85<br>2.05 | V<br>V   |                                                                                                                                             |  |  |

| 35A*                                                    | VHYST   | Brown-out Reset Hysteresis                                       | 25<br>—      | 50<br>—      | 75<br>100    | mV<br>mV | -40°C to +85°C<br>-40°C to +125°C                                                                                                           |  |  |

| 35B*                                                    | TBORDC  | Brown-out Reset DC Response<br>Time                              | 1            | 3            | 5<br>10      | μs<br>μs | $VDD \le VBOR$ , -40°C to +85°C $VDD \le VBOR$                                                                                              |  |  |

| 35C                                                     | TBORAC  | Brown-out Reset AC Response<br>Time                              |              | 100          | _            | ns       | Transient Response immunity<br>for a noise spike that goes<br>from VDD to VSS and back with<br>10 ns rise and fall times.<br>Guidance only. |  |  |

| 36                                                      | TFVRS   | Fixed Voltage Reference Turn-on<br>Time                          |              | —            | 5            | μS       | Turn on to specified stability                                                                                                              |  |  |

| 37                                                      | Vlpbor  | Low-Power Brown-out Reset<br>Voltage                             | 1.85         | 1.95         | 2.10         | V        | -40°C to +85°C                                                                                                                              |  |  |

| 38*                                                     | VZPHYST | Zero-Power Brown-out Reset<br>Hysteresis                         | 0            | 25           | 60           | mV       | -40°C to +85°C                                                                                                                              |  |  |

| 39*                                                     | Tzpbpw  | Zero-Power Brown-out Reset AC<br>Response Time for BOR detection | 10           | —            | 500          | nVs      | $VDD \le VBOR$ , -40°C to +85°C                                                                                                             |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- **2:** Period of the slower clock.

- 3: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

### 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.