Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1904-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 21.0 "Instruction Set Summary").

| Note: | The C and DC bits operate as Borrow and |         |     |       |               |    |  |  |  |

|-------|-----------------------------------------|---------|-----|-------|---------------|----|--|--|--|

|       | Digit Borrow                            |         | out | bits, | respectively, | in |  |  |  |

|       | subtra                                  | action. |     |       |               |    |  |  |  |

### REGISTER 3-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                                                                     |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                           |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

## PIC16LF1904/6/7

## 6.4 Oscillator Control Registers

## REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0            | R/W-0/0                                       | R/W-1/1                                                        | R/W-1/1      | R/W-1/1         | U-0            | R/W-0/0         | R/W-0/0      |  |  |  |  |

|----------------|-----------------------------------------------|----------------------------------------------------------------|--------------|-----------------|----------------|-----------------|--------------|--|--|--|--|

| _              |                                               | IRCF                                                           | <3:0>        |                 | _              | SCS             | <1:0>        |  |  |  |  |

| oit 7          |                                               |                                                                |              |                 |                |                 | bit C        |  |  |  |  |

| egend:         |                                               |                                                                |              |                 |                |                 |              |  |  |  |  |

| R = Readabl    | le hit                                        | W = Writable                                                   | bit          | U = Unimplem    | nented bit rea | d as '0'        |              |  |  |  |  |

| i = Bit is und |                                               | x = Bit is unkr                                                |              | •               |                | DR/Value at all | other Resets |  |  |  |  |

| 1' = Bit is se | •                                             | '0' = Bit is clea                                              |              |                 |                |                 |              |  |  |  |  |

|                | · ·                                           |                                                                |              |                 |                |                 |              |  |  |  |  |

| oit 7          | Unimplem                                      | nented: Read as '                                              | 0'           |                 |                |                 |              |  |  |  |  |

| oit 6-3        | IRCF<3:0                                      | Internal Oscillat                                              | or Frequency | Select bits     |                |                 |              |  |  |  |  |

|                | 000x = 31 kHz LF                              |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 001x = 31.25 kHz                              |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 0100 = 62.5  kHz                              |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 0101 <b>= 125 kHz</b>                         |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 0110 <b>= 250 kHz</b>                         |                                                                |              |                 |                |                 |              |  |  |  |  |

|                |                                               | 0111 = 500 kHz (default upon Reset)                            |              |                 |                |                 |              |  |  |  |  |

|                |                                               | $125 \text{ kHz}^{(1)}$                                        |              |                 |                |                 |              |  |  |  |  |

|                |                                               | $1001 = 250 \text{ kHz}^{(1)}$<br>1010 = 500 \text{ kHz}^{(1)} |              |                 |                |                 |              |  |  |  |  |

|                | 1010 = 500 kHz <sup>(*)</sup><br>1011 = 1 MHz |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 1100 <b>= 2</b>                               |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 1101 = 4                                      |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 1110 = 8                                      |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 1111 = 16                                     |                                                                |              |                 |                |                 |              |  |  |  |  |

| oit 2          | Unimplem                                      | nented: Read as '                                              | 0'           |                 |                |                 |              |  |  |  |  |

| oit 1-0        | SCS<1:0>                                      | : System Clock S                                               | elect bits   |                 |                |                 |              |  |  |  |  |

|                | 1x = Internal oscillator block                |                                                                |              |                 |                |                 |              |  |  |  |  |

|                | 01 = Seco                                     | ndary oscillator                                               |              |                 |                |                 |              |  |  |  |  |

|                | 00 = Clock                                    | k determined by F                                              | OSC<1:0> in  | Configuration W | ord 1.         |                 |              |  |  |  |  |

| Note 1: D      | unligato fragu                                | ency derived from                                              |              |                 |                |                 |              |  |  |  |  |

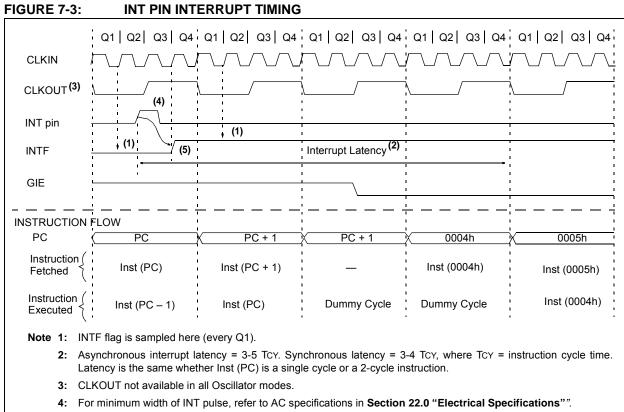

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

## 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1ms. See **Section 22.0 "Electrical Specifications"** for the LFINTOSC tolerances.

## 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word 1. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word 1 are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word 1 are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word 1 are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |

|-----------|--------|----------------|-------------|--|

| 11        | х      | Х              | Active      |  |

| 10        | 37     | Awake          | Active      |  |

| 10        | Х      | Sleep          | Disabled    |  |

| 01        | 1      | ~              | Active      |  |

| 01        | 0      | Х              | Disabled    |  |

| 00        | х      | Х              | Disabled    |  |

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT     |  |  |  |  |

|----------------------------------------------------------|---------|--|--|--|--|

| WDTE<1:0> = 00                                           |         |  |  |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |         |  |  |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared |  |  |  |  |

| CLRWDT Command                                           | Cleared |  |  |  |  |

| Oscillator Fail Detected                                 |         |  |  |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK | 7       |  |  |  |  |

| Change INTOSC divider (IRCF bits) Unaffected             |         |  |  |  |  |

#### 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail event

- WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 9-2 for more information.

### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the <u>device</u> wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0 "Memory Organization"** and STATUS register (**Register 3-1**) for more information.

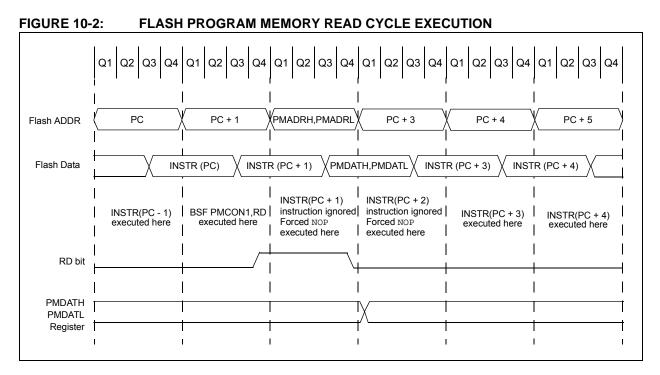

## EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program \* memory at the memory address: PROG\_ADDR\_HI : PROG\_ADDR\_LO data will be returned in the variables; \* PROG\_DATA\_HI, PROG\_DATA\_LO BANKSEL PMADRL ; Select Bank for PMCON registers MOVLW PROG\_ADDR\_LO ; MOVWF PMADRL ; Store LSB of address PROG\_ADDR\_HI MOVLW ; MOVWL PMADRH ; Store MSB of address BCF PMCON1,CFGS ; Do not select Configuration Space BSF PMCON1,RD ; Initiate read NOP ; Ignored (Figure 10-1) NOP ; Ignored (Figure 10-1) MOVF PMDATL,W ; Get LSB of word MOVWF PROG\_DATA\_LO ; Store in user location ; Get MSB of word MOVF PMDATH,W MOVWF PROG\_DATA\_HI ; Store in user location

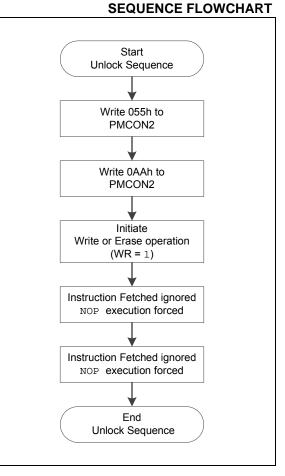

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash Program Memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

## FIGURE 10-3: FLASH PROGRAM MEMORY UNLOCK

## 11.3 PORTC Registers

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 11-6). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-5) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 11-6) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 11.3.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 11-7.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RC0      | T10S0                            |

|          | T1CKI<br>RC0                     |

| RC1      | T10SI                            |

|          | RC1                              |

| RC2      | SEG2                             |

|          | RC2                              |

| RC3      | SEG6                             |

|          | RC3                              |

| RC4      | SEG11                            |

|          | T1G                              |

|          | RC4                              |

| RC5      | SEG10                            |

|          | RC5                              |

| RC6      | SEG9                             |

|          | RC6                              |

|          | TX/CK                            |

| RC7      | SEG8                             |

|          | RC7                              |

|          | RX/DT                            |

### TABLE 11-7: PORTC OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

|              |                   |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SY         | ′NC = 1,   | BRG16 = 1                   |                |                    |                             |  |

|--------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc           | Fosc = 11.0592 MHz |                             |  |

|              | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300          | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0             | 0.00       | 13332                       | 300.0          | 0.00               | 9215                        |  |

| 1200         | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200.1            | 0.01       | 3332                        | 1200           | 0.00               | 2303                        |  |

| 2400         | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2399.5            | -0.02      | 1666                        | 2400           | 0.00               | 1151                        |  |

| 9600         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9592              | -0.08      | 416                         | 9600           | 0.00               | 287                         |  |

| 10417        | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10417             | 0.00       | 383                         | 10433          | 0.16               | 264                         |  |

| 19.2k        | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.23k            | 0.16       | 207                         | 19.20k         | 0.00               | 143                         |  |

| 57.6k        | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.97k            | 0.64       | 68                          | 57.60k         | 0.00               | 47                          |  |

| 115.2k       | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 114.29k           | -0.79      | 34                          | 115.2k         | 0.00               | 23                          |  |

## TABLE 18-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |                  |                             |                |                   |                             |                |                  |                             |  |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz                                     |            |                             | Fos            | Fosc = 4.000 MHz |                             |                | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0          | 0.01             | 3332                        | 300.0          | 0.00              | 3071                        | 300.1          | 0.04             | 832                         |  |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200           | 0.04             | 832                         | 1200           | 0.00              | 767                         | 1202           | 0.16             | 207                         |  |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398           | 0.08             | 416                         | 2400           | 0.00              | 383                         | 2404           | 0.16             | 103                         |  |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615           | 0.16             | 103                         | 9600           | 0.00              | 95                          | 9615           | 0.16             | 25                          |  |

| 10417  | 10417                                                | 0          | 191                         | 10417          | 0.00             | 95                          | 10473          | 0.53              | 87                          | 10417          | 0.00             | 23                          |  |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k         | 0.16             | 51                          | 19.20k         | 0.00              | 47                          | 19.23k         | 0.16             | 12                          |  |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k         | 2.12             | 16                          | 57.60k         | 0.00              | 15                          | —              | —                | —                           |  |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k         | -3.55            | 8                           | 115.2k         | 0.00              | 7                           | —              | _                | —                           |  |

| Name     | Bit 7                                 | Bit 6  | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------------------------------------|--------|---------------------|---------------------|--------|--------|--------|--------|---------------------|

| BAUD1CON | ABDOVF                                | RCIDL  | —                   | SCKP                | BRG16  | _      | WUE    | ABDEN  | 153                 |

| BAUD2CON | ABDOVF                                | RCIDL  | —                   | SCKP                | BRG16  |        | WUE    | ABDEN  | 153                 |

| INTCON   | GIE                                   | PEIE   | TMR0IE              | INTE                | IOCIE  | TMR0IF | INTF   | IOCIF  | 65                  |

| PIE1     | TMR1GIE                               | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | —      | —      | —      | TMR1IE | 66                  |

| PIR1     | TMR1GIF                               | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —      | —      | —      | TMR1IF | 68                  |

| RCSTA    | SPEN                                  | RX9    | SREN                | CREN                | ADDEN  | FERR   | OERR   | RX9D   | 152                 |

| SPBRGL   | EUSART Baud Rate Generator, Low Byte  |        |                     |                     |        |        |        | 154*   |                     |

| SPBRGH   | EUSART Baud Rate Generator, High Byte |        |                     |                     |        |        |        | 154*   |                     |

| TRISC    | TRISC7                                | TRISC6 | TRISC5              | TRISC4              | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 98                  |

| TXREG    | EUSART Transmit Register              |        |                     |                     |        |        |        | 144*   |                     |

| TXSTA    | CSRC                                  | TX9    | TXEN                | SYNC                | SENDB  | BRGH   | TRMT   | TX9D   | 151                 |

#### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous slave transmission.

\* Page provides register information.

Note 1: PIC16LF1904/7 only.

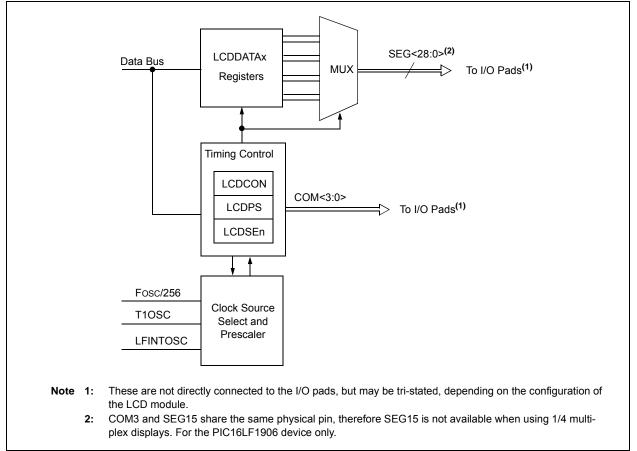

## 19.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16LF1904/6/7 device, the module drives the panels of up to four commons and up to 116 total segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- · Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- 19 Segment pins (PIC16LF1906 only)

- 29 Segment pins (PIC16LF1904/7 only)

• Static, 1/2 or 1/3 LCD Bias

Note: COM3 and SEG15 share the same physical pin on the PIC16LF1906, therefore SEG15 is not available when using 1/4 multiplex displays.

## 19.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 4 LCD Segment Enable registers (LCDSEn)

- Up to 16 LCD data registers (LCDDATAn)

### FIGURE 19-1: LCD DRIVER MODULE BLOCK DIAGRAM

## **REGISTER 19-4: LCDCST: LCD CONTRAST CONTROL REGISTER**

| U-0                                     | U-0 | U-0                                | U-0  | U-0                                                   | R/W-0/0 | R/W-0/0     | R/W-0/0 |  |

|-----------------------------------------|-----|------------------------------------|------|-------------------------------------------------------|---------|-------------|---------|--|

| —                                       | _   | —                                  | _    | -                                                     | I       | LCDCST<2:0> |         |  |

| bit 7                                   |     |                                    |      |                                                       |         |             | bit 0   |  |

|                                         |     |                                    |      |                                                       |         |             |         |  |

| Legend:                                 |     |                                    |      |                                                       |         |             |         |  |

| R = Readable bit W = Writable bit       |     | U = Unimplemented bit, read as '0' |      |                                                       |         |             |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                                    | iown | -n/n = Value at POR and BOR/Value at all other Resets |         |             |         |  |

C = Only clearable bit

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

1' = Bit is set

bit 2-0 LCDCST<2:0>: LCD Contrast Control bits

'0' = Bit is cleared

Selects the resistance of the LCD contrast control resistor ladder

Bit Value = Resistor ladder

000 = Minimum Resistance (Maximum contrast). Resistor ladder is shorted.

001 = Resistor ladder is at 1/7th of maximum resistance

010 = Resistor ladder is at 2/7th of maximum resistance

011 = Resistor ladder is at 3/7th of maximum resistance

100 = Resistor ladder is at 4/7th of maximum resistance

101 = Resistor ladder is at 5/7th of maximum resistance

110 = Resistor ladder is at 6/7th of maximum resistance

111 = Resistor ladder is at maximum resistance (Minimum contrast).

## PIC16LF1904/6/7

## PIC16LF1904/6/7

## 19.12 Configuring the LCD Module

The following is the sequence of steps to configure the LCD module.

- 1. Select the frame clock prescale using bits LP<3:0> of the LCDPS register.

- 2. Configure the appropriate pins to function as segment drivers using the LCDSEn registers.

- 3. Configure the LCD module for the following using the LCDCON register:

- Multiplex and Bias mode, bits LMUX<1:0>

- Timing source, bits CS<1:0>

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCD-DATA0 through LCDDATA21.

- 5. Clear LCD Interrupt Flag, LCDIF bit of the PIR2 register and if desired, enable the interrupt by setting bit LCDIE of the PIE2 register.

- Configure bias voltages by setting the LCDRL, LCDREF and the associated ANSELx registers as needed.

- 7. Enable the LCD module by setting bit LCDEN of the LCDCON register.

## 19.13 Disabling the LCD Module

To disable the LCD module, write all '0's to the LCDCON register.

## 19.14 LCD Current Consumption

When using the LCD module the current consumption consists of the following three factors:

- Oscillator Selection

- · LCD Bias Source

- Capacitance of the LCD segments

The current consumption of just the LCD module can be considered negligible compared to these other factors.

## 19.14.1 OSCILLATOR SELECTION

The current consumed by the clock source selected must be considered when using the LCD module. See **Section 22.0 "Electrical Specifications"** for oscillator current consumption information.

### 19.14.2 LCD BIAS SOURCE

The LCD bias source, internal or external, can contribute significantly to the current consumption. Use the highest possible resistor values while maintaining contrast to minimize current.

## 19.14.3 CAPACITANCE OF THE LCD SEGMENTS

The LCD segments which can be modeled as capacitors which must be both charged and discharged every frame. The size of the LCD segment and its technology determines the segment's capacitance.

## 25.0 PACKAGING INFORMATION

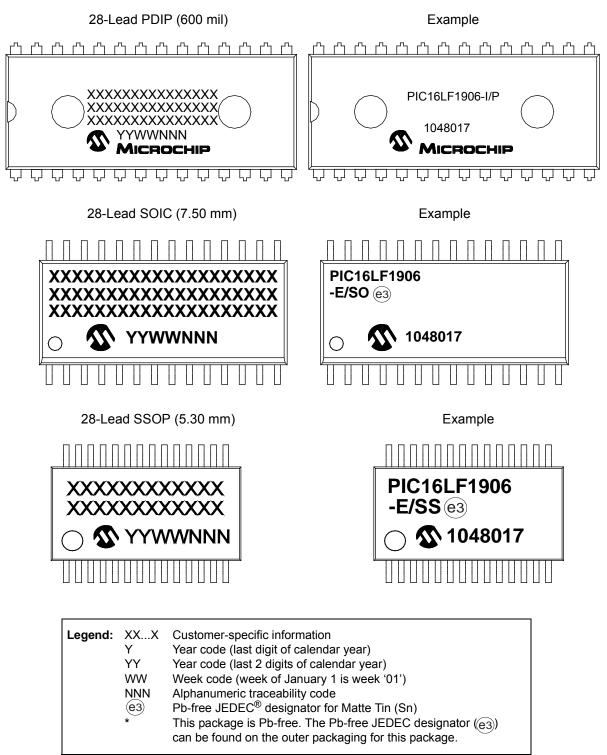

## 25.1 Package Marking Information

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

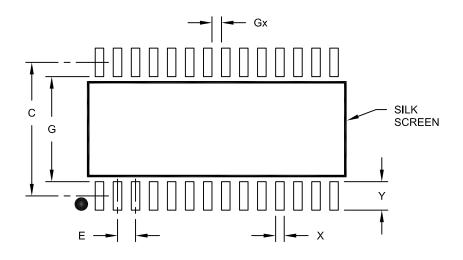

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch            | E           | 1.27 BSC |      |      |

| Contact Pad Spacing      | С           |          | 9.40 |      |

| Contact Pad Width (X28)  | X           |          |      | 0.60 |

| Contact Pad Length (X28) | Y           |          |      | 2.00 |

| Distance Between Pads    | Gx          | 0.67     |      |      |

| Distance Between Pads    | G           | 7.40     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0545-0