Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

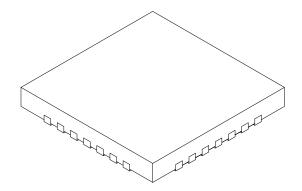

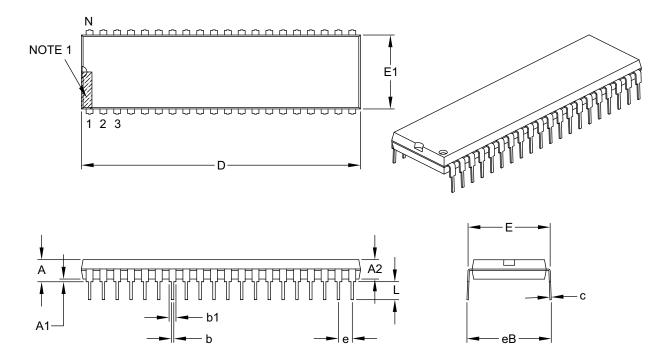

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1904t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

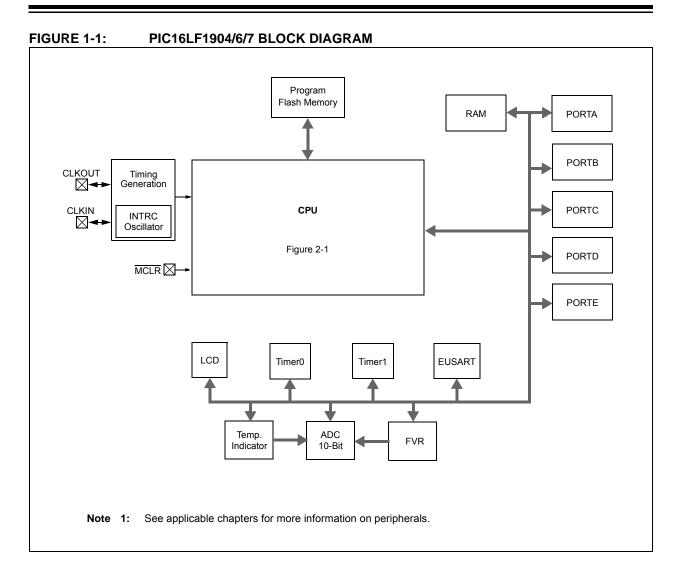

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

### 2.2 16-Level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 3.4 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.5 "Indirect Addressing"** for more details.

## 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 21.0 "Instruction Set Summary**" for more details.

| TABI               | LE 3-5:               | SPECIAL   | FUNCTI           | ON REG         | SISTER S       | UMMAR        | Y (CON1     | INUED) |        |                      |                                 |  |

|--------------------|-----------------------|-----------|------------------|----------------|----------------|--------------|-------------|--------|--------|----------------------|---------------------------------|--|

| Addr               | Name                  | Bit 7     | Bit 6            | Bit 5          | Bit 4          | Bit 3        | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

| Ban                | k 2                   |           |                  |                |                |              |             |        |        |                      |                                 |  |

| 10Ch               | LATA                  | PORTA Dat | PORTA Data Latch |                |                |              |             |        |        |                      |                                 |  |

| 10Dh               | LATB                  | PORTB Da  | ta Latch         |                |                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |  |

| 10Eh               | LATC                  | PORTC Da  | ta Latch         |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |  |

| 10Eh               | LATD <sup>(3)</sup>   | PORTD Da  | ta Latch         |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |  |

| 10Eh               | LATE <sup>(3)</sup>   | _         | _                | _              | _              | _            | LATE2       | LATE1  | LATE0  | xxx                  | uuu                             |  |

| 111h<br>to<br>115h | _                     | Unimpleme | nted             |                |                |              |             |        |        | _                    | _                               |  |

| 116h               | BORCON                | SBOREN    | BORFS            | _              | _              | _            |             | _      | BORRDY | 10q                  | uuu                             |  |

| 117h               | FVRCON                | FVREN     | FVRRDY           | TSEN           | TSRNG          | _            | _           | ADFVR1 | ADFVR0 | 0q0000               | 0q0000                          |  |

| 118h<br>to<br>11Fh | _                     | Unimpleme | nted             |                | •              |              | •           | •      |        | _                    | _                               |  |

| Ban                | k 3                   |           |                  |                |                |              |             |        |        |                      |                                 |  |

| 18Ch               | ANSELA                | _         | —                | ANSA5          | —              | ANSA3        | ANSA2       | ANSA1  | ANSA0  | 1- 1111              | 11 1111                         |  |

| 18Dh               | ANSELB                | _         | —                | ANSB5          | ANSB4          | ANSB3        | ANSB2       | ANSB1  | ANSB0  | 11 1111              | 11 1111                         |  |

| 18Eh               | —                     | Unimpleme | nted             |                | •              |              |             | •      |        | _                    | _                               |  |

| 18Fh               | _                     | Unimpleme | nted             |                |                |              |             |        |        | _                    | _                               |  |

| 190h               | ANSELE <sup>(3)</sup> | _         | _                | _              | _              | _            | ANSE2       | ANSE1  | ANSE0  | 111                  | 111                             |  |

| 191h               | PMADRL                | Program M | emory Addre      | ess Register   | Low Byte       |              |             |        |        | 0000 0000            | 0000 0000                       |  |

| 192h               | PMADRH                | (2)       |                  |                | ess Register I | High Byte    |             |        |        | 1000 0000            | 1000 0000                       |  |

| 193h               | PMDATL                | Program M | emory Read       | I Data Regist  | ter Low Byte   |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |  |

| 194h               | PMDATH                | _         | _                | Program M      | emory Read     | Data Registe | r High Byte |        |        | xx xxxx              | uu uuuu                         |  |

| 195h               | PMCON1                | (2)       | CFGS             | LWLO           | FREE           | WRERR        | WREN        | WR     | RD     | 1000 x000            | 1000 q000                       |  |

| 196h               | PMCON2                | Program M | emory Conti      | rol Register 2 | 2              |              |             |        |        | 0000 0000            | 0000 0000                       |  |

| 197h               | _                     | Unimpleme | nted             |                |                |              |             |        |        | _                    |                                 |  |

| 198h               | _                     | Unimpleme | nted             |                |                |              |             |        |        | _                    | _                               |  |

| 199h               | RCREG                 | USART Re  | ceive Data F     | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |  |

| 19Ah               | TXREG                 | USART Tra | Insmit Data      | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |  |

| 19Bh               | SPBRG                 |           |                  |                | BRG            | <7:0>        |             |        |        | 0000 0000            | 0000 0000                       |  |

| 19Ch               | SPBRGH                |           |                  |                | BRG<           | <15:8>       |             |        |        | 0000 0000            | 0000 0000                       |  |

| 19Dh               | RCSTA                 | SPEN      | RX9              | SREN           | CREN           | ADDEN        | FERR        | OERR   | RX9D   | 0000 000x            | 0000 000x                       |  |

| 19Eh               | TXSTA                 | CSRC      | TX9              | TXEN           | SYNC           | SENDB        | BRGH        | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |  |

| 19Fh               | BAUD1CON              | ABDOVF    | RCIDL            | _              | SCKP           | BRG16        | _           | WUE    | ABDEN  | 01-0 0-00            |                                 |  |

| Ban                |                       | 1         | 1                |                |                | 1            | 1           |        | L      |                      | 1                               |  |

| 20Ch               | _                     | Unimpleme | nted             |                |                |              |             |        |        | _                    | _                               |  |

|                    | WPUB                  | WPUB7     | WPUB6            | WPUB5          | WPUB4          | WPUB3        | WPUB2       | WPUB1  | WPUB0  | 1111 1111            | 1111 1111                       |  |

| 20Eh               | _                     | Unimpleme |                  |                |                |              |             |        |        | _                    | _                               |  |

| 20Fh               | _                     | Unimpleme |                  |                |                |              |             |        |        | _                    | _                               |  |

| 210h               | WPUE                  |           | _                | _              | _              | WPUE3        |             | _      | _      | 1                    | 1                               |  |

|                    |                       |           |                  |                |                |              |             |        |        | ±                    | 1                               |  |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-5

Bank 5

211h to 21Fh

29Fh

28Ch

\_ \_

Bank 6

| Бап      | ĸo |                                                                                                                                            |  |   |

|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------|--|---|

| 30Ch     | _  | Unimplemented                                                                                                                              |  | _ |

| <br>31Fh |    |                                                                                                                                            |  |   |

| Legen    |    | vn, u = unchanged, $q$ = value depends on condition, - = unimplemented, read as '0', r = reserved. cations are unimplemented, read as '0'. |  |   |

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16LF1904/7 only. Note 1:

Unimplemented

Unimplemented

2:

3:

R/P-1

U-1

R/P-1

bit 8

bit 0

#### CLKOUTEN BOREN<1:0> bit 13 R/P-1 R/P-1 R/P-1 R/P-1 R/P-1 U-1 R/P-1 **MCLRE** CP PWRTE WDTE<1:0> FOSC<1:0> bit 7 Legend: R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1' '1' = Bit is set -n = Value when blank or after Bulk Erase '0' = Bit is cleared bit 13-12 Unimplemented: Read as '1' **CLKOUTEN:** Clock Out Enable bit bit 11 1 = CLKOUT function is disabled. I/O function on the CLKOUT pin. 0 = CLKOUT function is enabled on the CLKOUT pin bit 10-9 BOREN<1:0>: Brown-out Reset Enable bits 11 = BOR enabled 10 = BOR enabled during operation and disabled in Sleep 01 = BOR controlled by SBOREN bit of the BORCON register 00 = BOR disabled bit 8 Unimplemented: Read as '1' CP: Code Protection bit bit 7 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled MCLRE: MCLR/VPP Pin Function Select bit bit 6 If LVP bit = 1: This bit is ignored. If LVP bit = 0: $1 = \overline{MCLR}/VPP$ pin function is $\overline{MCLR}$ ; Weak pull-up enabled. 0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUE3 bit. bit 5 **PWRTE:** Power-up Timer Enable bit 1 = PWRT disabled 0 = PWRT enabled bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit 11 = WDT enabled 10 = WDT enabled while running and disabled in Sleep 01 = WDT controlled by the SWDTEN bit in the WDTCON register 00 = WDT disabled bit 2 Unimplemented: Read as '1' bit 1-0 FOSC<1:0>: Oscillator Selection bits 00 = INTOSC oscillator: I/O function on CLKIN pin 01 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

10 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin 11 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

#### **REGISTER 4-1: CONFIGURATION WORD 1**

U-1

U-1

R/P-1

R/P-1

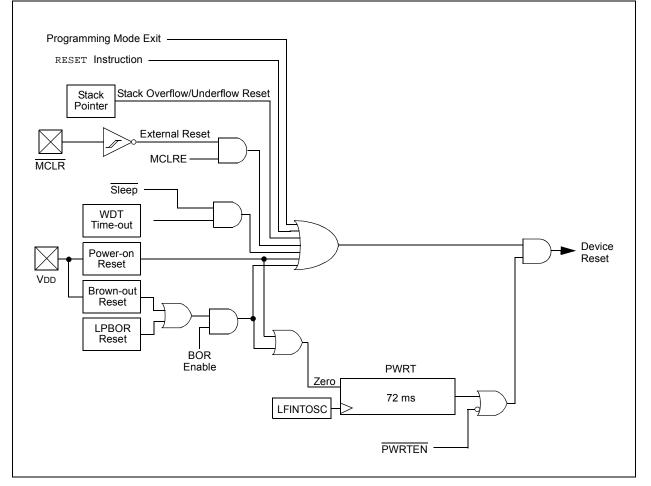

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 5-1.

# 5.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 2011-2016 Microchip Technology Inc.

# 6.4 Oscillator Control Registers

## REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0            | R/W-0/0                              | R/W-1/1              | R/W-1/1      | R/W-1/1                                                                              | U-0            | R/W-0/0  | R/W-0/0 |  |  |  |

|----------------|--------------------------------------|----------------------|--------------|--------------------------------------------------------------------------------------|----------------|----------|---------|--|--|--|

| _              |                                      | IRCF                 | <3:0>        |                                                                                      | _              | SCS      | <1:0>   |  |  |  |

| oit 7          |                                      |                      |              |                                                                                      |                |          | bit C   |  |  |  |

| egend:         |                                      |                      |              |                                                                                      |                |          |         |  |  |  |

| R = Readabl    | le hit                               | W = Writable         | bit          | U = Unimplem                                                                         | nented bit rea | d as '0' |         |  |  |  |

| i = Bit is und |                                      | x = Bit is unkr      |              | U = Unimplemented bit, read as '0'<br>-n/n = Value at POR and BOR/Value at all other |                |          |         |  |  |  |

| 1' = Bit is se | •                                    | '0' = Bit is clea    |              |                                                                                      |                |          |         |  |  |  |

|                | · ·                                  |                      |              |                                                                                      |                |          |         |  |  |  |

| oit 7          | Unimplem                             | nented: Read as '    | 0'           |                                                                                      |                |          |         |  |  |  |

| oit 6-3        | IRCF<3:0                             | Internal Oscillat    | or Frequency | Select bits                                                                          |                |          |         |  |  |  |

|                | 000x = 31                            | kHz LF               |              |                                                                                      |                |          |         |  |  |  |

|                | 001x = 31.25 kHz                     |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 0100 = 62.5  kHz                     |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 0101 <b>= 125 kHz</b>                |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 0110 = 25                            |                      |              |                                                                                      |                |          |         |  |  |  |

|                |                                      | 0 kHz (default upo   | on Reset)    |                                                                                      |                |          |         |  |  |  |

|                | 1000 = 12                            |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1001 <b>= 25</b><br>1010 <b>= 50</b> |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1010 <b>= 50</b><br>1011 <b>= 1</b>  |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1100 <b>= 2</b>                      |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1101 = 4                             |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1110 = 8                             |                      |              |                                                                                      |                |          |         |  |  |  |

|                | 1111 = 16                            |                      |              |                                                                                      |                |          |         |  |  |  |

| oit 2          | Unimplem                             | nented: Read as '    | 0'           |                                                                                      |                |          |         |  |  |  |

| oit 1-0        | SCS<1:0>                             | : System Clock S     | elect bits   |                                                                                      |                |          |         |  |  |  |

|                | 1x = Interr                          | nal oscillator block | Ĩ            |                                                                                      |                |          |         |  |  |  |

|                | 01 = Seco                            | ndary oscillator     |              |                                                                                      |                |          |         |  |  |  |

|                | 00 = Clock                           | k determined by F    | OSC<1:0> in  | Configuration W                                                                      | ord 1.         |          |         |  |  |  |

| Note 1: D      | unligato fragu                       | ency derived from    |              |                                                                                      |                |          |         |  |  |  |

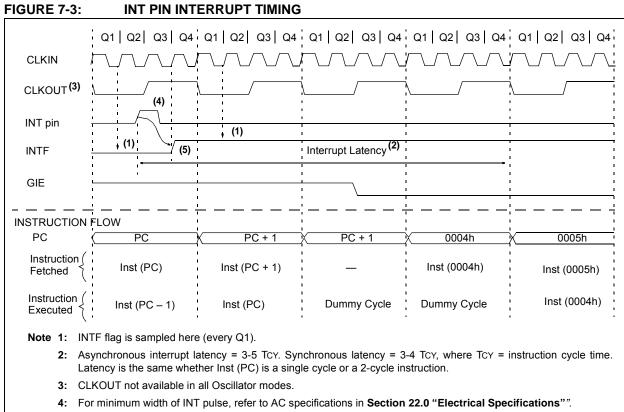

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, stored in little endian format ; ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) INTCON,GIE BCF ; Disable ints so required sequences will execute properly PMADRH ; Bank 3 BANKSEL MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWE PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSROH ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1.WREN ; Enable writes BSF PMCON1,LWLO ; Only Load Write Latches LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWE PMDATT. ; MOVIW FSR0++ ; Load second data byte into upper MOVWF PMDATH ; Check if lower bits of address are '00000' MOVF PMADRL,W 0x1F ; Check if we're on the last of 32 addresses XORLW ANDLW 0x1F STATUS, Z ; Exit if last of 32 words, BTFSC GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh ; Set WR bit to begin write BSF PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction BCF PMCON1,WREN ; Disable writes BSF INTCON, GIE ; Enable interrupts

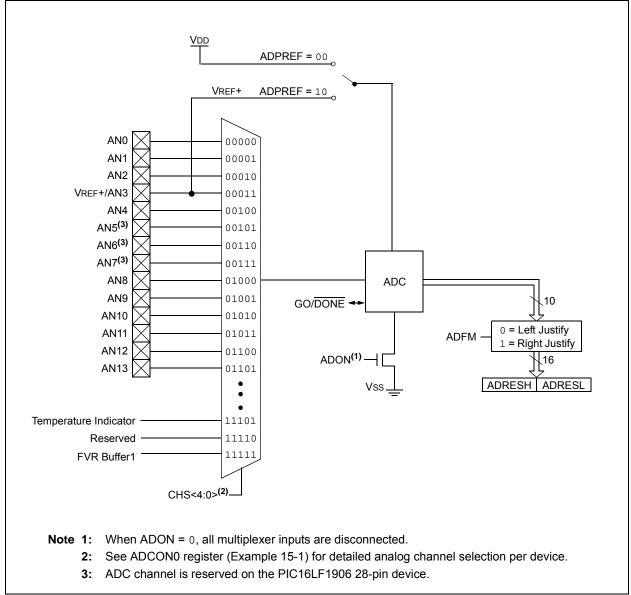

# 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

### FIGURE 15-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

| R/W-0/0          | R/W-0/0                                | R/W-0/0                                                        | R/W-0/0        | U-0            | U-0             | R/W-0/0         | R/W-0/0      |

|------------------|----------------------------------------|----------------------------------------------------------------|----------------|----------------|-----------------|-----------------|--------------|

| ADFM             |                                        | ADCS<2:0>                                                      |                |                | —               | ADPRE           | EF<1:0>      |

| bit 7            | ·                                      |                                                                |                | •              | •               |                 | bit (        |

| Legend:          |                                        |                                                                |                |                |                 |                 |              |

| R = Readable     | bit                                    | W = Writable                                                   | bit            | U = Unimpler   | nented bit, rea | id as '0'       |              |

| u = Bit is unch  | nanged                                 | x = Bit is unkr                                                | nown           | -n/n = Value a | at POR and BO   | OR/Value at all | other Resets |

| '1' = Bit is set |                                        | '0' = Bit is cle                                               | ared           |                |                 |                 |              |

| bit 6-4          | loaded.<br>0 = Left jus<br>loaded.     | tified. Six Least                                              | Significant bi | ts of ADRESL a |                 |                 |              |

|                  | 100 = Fosc<br>101 = Fosc<br>110 = Fosc | :/8<br>:/32<br>(clock supplied fi<br>:/4<br>:/16               |                |                |                 |                 |              |

| bit 3-2          | Unimpleme                              | nted: Read as '                                                | 0'             |                |                 |                 |              |

| bit 1-0          | 00 = VREF+<br>01 = Reser               | :0>: A/D Positive<br>is connected to<br>ved<br>is connected to | VDD            |                | ation bits      |                 |              |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 22.0 "Electrical Specifications"** for details.

### 17.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 17-1 displays the Timer1 enable selections.

| TABLE 17-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 17.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 17-2 displays the clock source selections.

#### 17.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous source may be used:

Asynchronous event on the T1G pin to Timer1

gate

#### 17.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- Note: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON = 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                     |

|---------|---------|---------|----------------------------------|

| 0       | 0       | x       | Instruction Clock (Fosc/4)       |

| 0       | 1       | x       | System Clock (Fosc)              |

| 1       | 0       | 0       | External Clocking on T1CKI Pin   |

| 1       | 0       | 1       | Osc. Circuit on T1OSI/T1OSO Pins |

| 1       | 1       | x       | Reserved                         |

#### TABLE 17-2: CLOCK SOURCE SELECTIONS

| FIGURE 17-5:           | TIMER1 GATE SINGLE-PU                    | PULSE MODE                                                 |

|------------------------|------------------------------------------|------------------------------------------------------------|

|                        |                                          |                                                            |

| TMR1GE                 |                                          |                                                            |

| T1GPOL                 |                                          |                                                            |

| T1GSPM                 |                                          |                                                            |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled on | Cleared by hardware on<br>falling edge of T1GVAL           |

| T1G_IN                 | rising edge of T1G                       |                                                            |

| т1СКІ                  |                                          |                                                            |

| T1GVAL                 |                                          |                                                            |

| Timer1                 | N                                        | N + 1 N + 2                                                |

| TMR1GIF                | — Cleared by software                    | Cleared by<br>Set by hardware on<br>falling edge of T1GVAL |

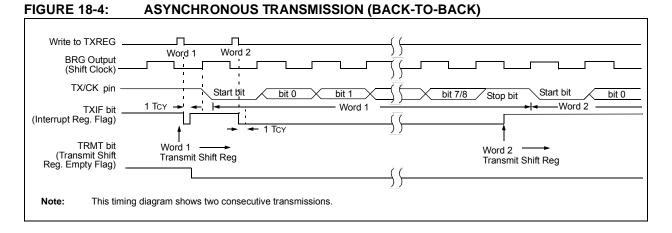

#### TABLE 18-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7                                 | Bit 6 | Bit 5               | Bit 4               | Bit 3        | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|----------|---------------------------------------|-------|---------------------|---------------------|--------------|---------|-------|--------|---------------------|

| BAUD1CON | ABDOVF                                | RCIDL | —                   | SCKP                | BRG16        | —       | WUE   | ABDEN  | 153                 |

| BAUD2CON | ABDOVF                                | RCIDL | —                   | SCKP                | BRG16        | —       | WUE   | ABDEN  | 153                 |

| INTCON   | GIE                                   | PEIE  | TMR0IE              | INTE                | IOCIE        | TMR0IF  | INTF  | IOCIF  | 65                  |

| PIE1     | TMR1GIE                               | ADIE  | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | —            | —       | _     | TMR1IE | 66                  |

| PIR1     | TMR1GIF                               | ADIF  | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —            | —       | _     | TMR1IF | 68                  |

| RCSTA    | SPEN                                  | RX9   | SREN                | CREN                | ADDEN        | FERR    | OERR  | RX9D   | 152                 |

| SPBRGL   |                                       |       | EUSART              | Baud Rate           | Generator, L | ow Byte |       |        | 154*                |

| SPBRGH   | EUSART Baud Rate Generator, High Byte |       |                     |                     |              |         |       |        |                     |

| TXREG    |                                       |       | El                  | JSART Tran          | smit Registe | er      |       |        | 144*                |

| TXSTA    | CSRC                                  | TX9   | TXEN                | SYNC                | SENDB        | BRGH    | TRMT  | TX9D   | 151                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous transmission.

\* Page provides register information.

Note 1: PIC16LF1904/7 only.

### 18.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

RX/DT and TX/CK pin output drivers must be disabled by setting the corresponding TRIS bits.

#### 18.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 18.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 18.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- 3. Clear the CREN and SREN bits.

- If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

| R/W-0/0                   | R/W-0/0                                                                                                                                             | R/C-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                        | R/W-0/0                                | R/W-0/0                               | R/W-1/1          | R/W-1/1      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|---------------------------------------|------------------|--------------|

| LCDEN                     | SLPEN                                                                                                                                               | WERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                          | (                                      | CS<1:0>                               | LMU>             | <1:0>        |

| bit 7                     | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                       |                  | bit          |

|                           |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                       |                  |              |

| Legend:                   | . <b>L</b> :4                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            | II — I heirer                          | lowented bit read                     | aa (0)           |              |

| R = Readable              |                                                                                                                                                     | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | •                                      | lemented bit, read                    |                  |              |

| u = Bit is unch           | •                                                                                                                                                   | x = Bit is unknow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |                                        | e at POR and BOF                      | R/Value at all c | other Resets |

| '1' = Bit is set          |                                                                                                                                                     | '0' = Bit is cleare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed                                                                         | C = Only c                             | learable bit                          |                  |              |

| bit 7                     | LCDEN: LCD                                                                                                                                          | Driver Enable bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t                                                                          |                                        |                                       |                  |              |

|                           |                                                                                                                                                     | er module is enab<br>er module is disat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                        |                                       |                  |              |

| bit 6                     | SLPEN: LCD                                                                                                                                          | Driver Enable in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sleep Mod                                                                  | le bit                                 |                                       |                  |              |

|                           |                                                                                                                                                     | er module is disat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |                                        |                                       |                  |              |