#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

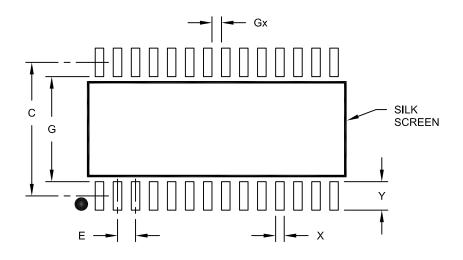

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1906-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-2: PIC16LF1904/6/7 PINOUT DESCRIPTION (CONTINUED)

| Name                          | Function | Input<br>Type | Output<br>Type | Description                         |

|-------------------------------|----------|---------------|----------------|-------------------------------------|

| RD0 <sup>(2)</sup> /COM3      | RD0      | TTL           | CMOS           | General purpose I/O.                |

|                               | COM3     |               | AN             | LCD Analog output.                  |

| RD1 <sup>(2)</sup> /SEG27     | RD1      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG27    |               | AN             | LCD Analog output.                  |

| RD2 <sup>(2)</sup> /SEG28     | RD2      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG28    |               | AN             | LCD Analog output.                  |

| RD3 <sup>(2)</sup> /SEG16     | RD3      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG16    |               | AN             | LCD Analog output.                  |

| RD4 <sup>(2)</sup> /SEG17     | RD4      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG17    | _             | AN             | LCD Analog output.                  |

| RD5 <sup>(2)</sup> /SEG18     | RD5      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG18    | _             | AN             | LCD Analog output.                  |

| RD6 <sup>(2)</sup> /SEG19     | RD6      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG19    | _             | AN             | LCD Analog output.                  |

| RD7 <sup>(2)</sup> /SEG20     | RD7      | TTL           | CMOS           | General purpose I/O.                |

|                               | SEG20    | _             | AN             | LCD Analog output.                  |

| RE0 <sup>(2)</sup> /AN5/SEG21 | RE0      | TTL           | CMOS           | General purpose I/O.                |

|                               | AN5      | AN            |                | A/D Channel 5 input.                |

|                               | SEG21    |               | AN             | LCD Analog output.                  |

| RE1 <sup>(2)</sup> /AN6/SEG22 | RE1      | TTL           | CMOS           | General purpose I/O.                |

|                               | AN6      | AN            | —              | A/D Channel 6 input.                |

|                               | SEG22    | _             | AN             | LCD Analog output.                  |

| RE2 <sup>(2)</sup> /AN7/SEG23 | RE2      | TTL           | CMOS           | General purpose I/O.                |

|                               | AN7      | AN            | —              | A/D Channel 7 input.                |

|                               | SEG23    | _             | AN             | LCD Analog output.                  |

| RE3/MCLR/VPP                  | RE3      | TTL           | CMOS           | General purpose I/O.                |

|                               | MCLR     | ST            | —              | Master Clear with internal pull-up. |

|                               | Vpp      | HV            | —              | Programming voltage.                |

| Vdd                           | Vdd      | Power         | —              | Positive supply.                    |

| Vss                           | Vss      | Power         | —              | Ground reference.                   |

IIL = IIL compatible input SI = SHV = High Voltage XTAL = C

XTAL = Crystal

OD = Open-Drain

= Schmitt Trigger input with I<sup>2</sup>C levels

Note 1: These pins have interrupt-on-change functionality.

2: PIC16LF1906/7 only.

DS40001569D-page 14

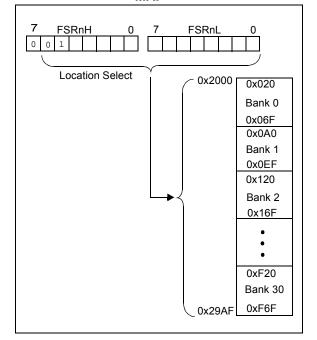

## 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

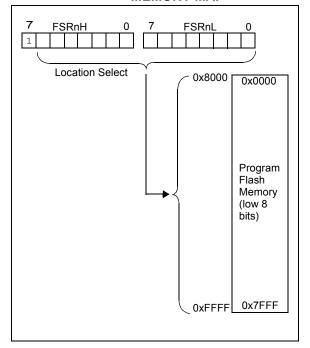

### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

## 5.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation<br>upon release of POR | Device Operation<br>upon wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|-----------------------------------------|-------------------------------------------------|--|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |

| 1.0        | 37     | W.          | Awake    | Active                                  | Waits for BOR ready                             |  |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready                     |                                                 |  |

| 0.1        | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |

| 01         | 0      | х           | Disabled | Begins in                               | nmediately                                      |  |

| 00         | х      | х           | Disabled | Begins immediately                      |                                                 |  |

## TABLE 5-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

PIC16LF1904/6/7

#### 5.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00-1 110x        |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu-u Ouuu        |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu-u Ouuu        |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu-0 uuuu        |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu-u uuuu        |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00-1 11u0        |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu-u uuuu        |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu-u u0uu        |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu-u uuuu        |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul-u uuuu        |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

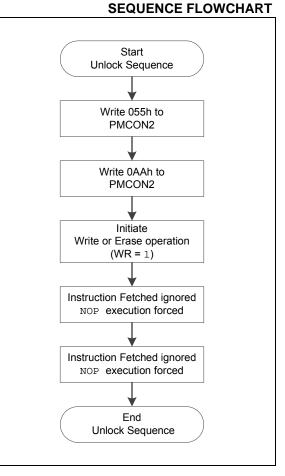

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash Program Memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

## FIGURE 10-3: FLASH PROGRAM MEMORY UNLOCK

## 10.6 Flash Program Memory Control Registers

## REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u             | R/W-x/u | R/W-x/u              | R/W-x/u                                        | R/W-x/u       | R/W-x/u              | R/W-x/u | R/W-x/u |

|---------------------|---------|----------------------|------------------------------------------------|---------------|----------------------|---------|---------|

|                     |         |                      | PMDA                                           | T<7:0>        |                      |         |         |

| bit 7               |         |                      |                                                |               |                      |         | bit 0   |

|                     |         |                      |                                                |               |                      |         |         |

| Legend:             |         |                      |                                                |               |                      |         |         |

| R = Readable bit    |         | W = Writable bit     |                                                | U = Unimpleme | nted bit, read as '  | 0'      |         |

| u = Bit is unchange | d       | x = Bit is unknown   | vn -n/n = Value at POR and BOR/Value at all ot |               | lue at all other Res | sets    |         |

| '1' = Bit is set    |         | '0' = Bit is cleared |                                                |               |                      |         |         |

bit 7-0

PMDAT<7:0>: Read/write value for Least Significant bits of program memory

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|

| _     | —   |         | PMDAT<13:8> |         |         |         |         |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0       | R/W-0/0               | R/W-0/0 | R/W-0/0 |

|------------------|---------|------------------|---------|---------------|-----------------------|---------|---------|

|                  |         |                  | PMAD    | R<7:0>        |                       |         |         |

| bit 7            |         |                  |         |               |                       |         | bit 0   |

|                  |         |                  |         |               |                       |         |         |

| Legend:          |         |                  |         |               |                       |         |         |

| R = Readable bit |         | W = Writable bit |         | U = Unimpleme | ented bit, read as '0 | )'      |         |

| R = Readable bit     | vv = vvritable bit   | U = Unimplemented bit, read as 'U'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|---------|-------------|---------|---------|---------|---------|---------|--|

| —     |         | PMADR<14:8> |         |         |         |         |         |  |

| bit 7 |         |             |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

## 11.2 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-6). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-5) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The TRISB register (Register 11-6) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.2.1 ANSELB REGISTER

The ANSELB register (Register 11-8) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.2.2 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 11-5.

| TABLE 11-5: P | ORTB OUTPUT PRIORITY |

|---------------|----------------------|

|---------------|----------------------|

| Pin Name | Function Priority <sup>(1)</sup>           |

|----------|--------------------------------------------|

| RB0      | SEG0<br>AN12                               |

|          | INT<br>IOC<br>RB0                          |

| RB1      | SEG24<br>AN10<br>VLCD1<br>IOC              |

| RB2      | RB1<br>SEG25<br>AN8<br>VLCD2<br>IOC<br>RB2 |

| RB3      | SEG26<br>AN9<br>VLCD3<br>IOC<br>RB3        |

| RB4      | COM0<br>AN11<br>IOC<br>RB4                 |

| RB5      | COM1<br>AN13<br>IOC<br>RB5                 |

| RB6      | ICDCLK<br>SEG14<br>IOC<br>RB6              |

| RB7      | ICDDAT<br>SEG13<br>IOC<br>RB7              |

Note 1: Priority listed from highest to lowest.

| U-0                                   | U-0                                                                                       | R/W-1/1          | R/W-1/1 | R/W-1/1                            | R/W-1/1       | R/W-1/1            | R/W-1/1 |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------|------------------|---------|------------------------------------|---------------|--------------------|---------|--|--|

| _                                     | _                                                                                         | ANSB5            | ANSB4   | ANSB3                              | ANSB2         | ANSB1              | ANSB0   |  |  |

| bit 7                                 |                                                                                           |                  |         |                                    |               |                    | bit 0   |  |  |

|                                       |                                                                                           |                  |         |                                    |               |                    |         |  |  |

| Legend:                               |                                                                                           |                  |         |                                    |               |                    |         |  |  |

| R = Readable bit W = Writable bit     |                                                                                           |                  | t       | U = Unimplemented bit, read as '0' |               |                    |         |  |  |

| u = Bit is uncha                      | nged                                                                                      | x = Bit is unkno | wn      | -n/n = Value at                    | POR and BOR/\ | alue at all other/ | Resets  |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                                           |                  | ed      |                                    |               |                    |         |  |  |

|                                       |                                                                                           |                  |         |                                    |               |                    |         |  |  |

| bit 7-6                               | Unimplement                                                                               | ed: Read as '0'  |         |                                    |               |                    |         |  |  |

| bit 5-0                               | ANSB<5:0>: Analog Select between Analog or Digital Function on pins RB<5:0>, respectively |                  |         |                                    |               |                    |         |  |  |

ANSB<5:0>: Analog Select between Analog or Digital Function on pins RB<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned to port of digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

## REGISTER 11-9: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1     | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|

| WPUB7       | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

WPUB<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | —      | -      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 99                  |

| LATB   | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 98                  |

| PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 98                  |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 98                  |

| WPUB   | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1  | WPUB0  | 99                  |

#### TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## **REGISTER 11-18: LATE: PORTE DATA LATCH REGISTER**

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-x/u              | R/W-x/u              | R/W-x/u              |

|---------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

|         | —   |     | —   | —   | LATE2 <sup>(2)</sup> | LATE1 <sup>(2)</sup> | LATE0 <sup>(2)</sup> |

| bit 7   |     |     |     |     |                      |                      | bit 0                |

|         |     |     |     |     |                      |                      |                      |

| Logond: |     |     |     |     |                      |                      |                      |

| Le | g | e | r | 1 | d | - |

|----|---|---|---|---|---|---|

|    |   |   |   |   |   |   |

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(1)</sup>

- Note 1: Writes to PORTE are actually written to the corresponding LATE register. Reads from the PORTE register is return of actual I/O pin values.

- 2: LATE<2:0> are not implemented on the PIC16LF1906. Read as '0'.

### **REGISTER 11-19: ANSELE: PORTE ANALOG SELECT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1              | R/W-1/1              | R/W-1/1              |

|-------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

| —     | —   | —   | —   | —   | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |

| bit 7 |     |     |     |     |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on pins RE<2:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSE<2:0> are not implemented on the PIC16LF1906. Read as '0'.

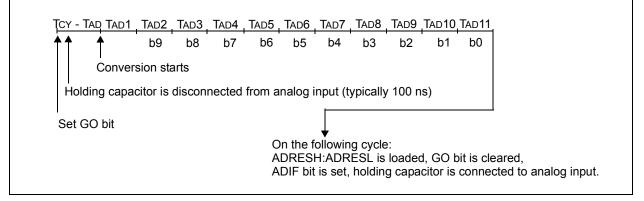

| TABLE 15-1: | ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| ADC Clock     | Period (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                               |  |  |

|---------------|--------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--|--|

| ADC ADCS<2:0> |              | 20 MHz 16 MHz 8 N           |                             | 8 MHz                       | 4 MHz                       | 1 MHz                         |  |  |

| Fosc/2        | 000          | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |  |  |

| Fosc/4        | 100          | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |  |  |

| Fosc/8        | 001          | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |  |  |

| Fosc/16       | 101          | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32       | 010          | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |  |  |

| Fosc/64       | 110          | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |  |  |

| Frc           | x11          | 1.0-6.0 μs <sup>(1,4)</sup>   |  |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

#### 15.2.6 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 15-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|----------|---------|---------|---------|---------|

| _     |         |         | CHS<4:0> |         |         | GO/DONE | ADON    |

| bit 7 |         |         |          |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                             |

|---------|----------------------------------------------------------------------------------------|

| bit 6-2 | CHS<4:0>: Analog Channel Select bits                                                   |

|         | 00000 = ANO                                                                            |

|         | 00001 = AN1                                                                            |

|         | 00010 = AN2                                                                            |

|         | 00011 = AN3                                                                            |

|         | 00100 = AN4                                                                            |

|         | $00101 = AN5^{(3)}$                                                                    |

|         | $00110 = AN6^{(3)}$                                                                    |

|         | $00111 = AN7^{(3)}$                                                                    |

|         | 01000 = AN8                                                                            |

|         | 01001 = AN9                                                                            |

|         | 01010 = AN10<br>01011 = AN11                                                           |

|         | 01100 = AN12                                                                           |

|         | 01101 = AN13                                                                           |

|         | 01110 = Reserved. No channel connected.                                                |

|         | •                                                                                      |

|         | •                                                                                      |

|         | •                                                                                      |

|         | 11100 = Reserved. No channel connected.                                                |

|         | 11101 = Temperature Indicator <sup>(2)</sup>                                           |

|         | 11110 = Reserved. No channel connected.                                                |

|         | 11111 = FVR (Fixed Voltage Reference) Buffer 1 Output <sup>(1)</sup>                   |

| bit 1   | GO/DONE: A/D Conversion Status bit                                                     |

|         | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. |

|         | This bit is automatically cleared by hardware when the A/D conversion has completed.   |

|         | 0 = A/D conversion completed/not in progress                                           |

| bit 0   | ADON: ADC Enable bit                                                                   |

|         | 1 = ADC is enabled                                                                     |

|         | 0 = ADC is disabled and consumes no operating current                                  |

| Note 1: | See Section 13.0 "Fixed Voltage Reference (FVR)" for more information.                 |

| 2:      | See Section 14.0 "Temperature Indicator Module" for more information.                  |

|         | ADC channel is reserved on the PIC16LF1906 28-pin device.                              |

| 5.      | Abe chambers reserved on the Fronce ratio 20-pin device.                               |

## 16.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

### 16.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the pro- |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | cessor from Sleep since the timer is fro- |  |  |  |  |  |  |  |

|       | zen during Sleep.                         |  |  |  |  |  |  |  |

#### 16.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 22.0** "**Electrical Specifications**".

## 16.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

#### 18.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode would typically be used in RS-232 systems. The receiver block diagram is shown in Figure 18-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 18.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

If the RX/DT pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

## 18.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 18.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 18.1.2.5 "Receive Overrun Error" for more information on overrun errors.

| R-0/0            | R-1/1                                                                                                                                                                 | U-0                                   | R/W-0/0        | R/W-0/0        | U-0             | R/W-0/0          | R/W-0/0     |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|----------------|-----------------|------------------|-------------|--|--|--|--|

| ABDOVF           | RCIDL                                                                                                                                                                 | —                                     | SCKP           | BRG16          | —               | WUE              | ABDEN       |  |  |  |  |

| bit 7            |                                                                                                                                                                       |                                       |                |                |                 |                  | bit 0       |  |  |  |  |

|                  |                                                                                                                                                                       |                                       |                |                |                 |                  |             |  |  |  |  |

| Legend:          |                                                                                                                                                                       |                                       |                |                |                 |                  |             |  |  |  |  |

| R = Readable     | bit                                                                                                                                                                   | W = Writable                          | bit            | U = Unimplei   | mented bit, rea | d as '0'         |             |  |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                 | x = Bit is unk                        | nown           | -n/n = Value   | at POR and BC   | R/Value at all c | ther Resets |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                       | '0' = Bit is cle                      | ared           |                |                 |                  |             |  |  |  |  |

| hit 7            |                                                                                                                                                                       | ite Doud Dotes                        | t Overflew bit |                |                 |                  |             |  |  |  |  |

| bit 7            |                                                                                                                                                                       | uto-Baud Detec                        | t Overnow bit  |                |                 |                  |             |  |  |  |  |

|                  | $\frac{\text{Asynchronou}}{1 = \text{Auto-bau}}$                                                                                                                      | <u>s mode</u> .<br>d timer overflov   | wed            |                |                 |                  |             |  |  |  |  |

|                  |                                                                                                                                                                       | d timer did not                       |                |                |                 |                  |             |  |  |  |  |

|                  | Synchronous                                                                                                                                                           |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                                            | _                                     |                |                |                 |                  |             |  |  |  |  |

| bit 6            | RCIDL: Rece                                                                                                                                                           | eive Idle Flag bi                     | t              |                |                 |                  |             |  |  |  |  |

|                  | •                                                                                                                                                                     | Asynchronous mode:                    |                |                |                 |                  |             |  |  |  |  |

|                  | 1 = Receiver is Idle                                                                                                                                                  |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | 0 = Start bit has been received and the receiver is receiving                                                                                                         |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | <u>Synchronous mode</u> :<br>Don't care                                                                                                                               |                                       |                |                |                 |                  |             |  |  |  |  |

| bit 5            | Unimplemen                                                                                                                                                            | ted: Read as '                        | 0'             |                |                 |                  |             |  |  |  |  |

| bit 4            | SCKP: Synchronous Clock Polarity Select bit                                                                                                                           |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                                    |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | <ul> <li>1 = Transmit inverted data to the TX/CK pin</li> <li>0 = Transmit non-inverted data to the TX/CK pin</li> </ul>                                              |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | Synchronous mode:                                                                                                                                                     |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | 1 = Data is clocked on rising edge of the clock                                                                                                                       |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | 0 = Data is clocked on falling edge of the clock                                                                                                                      |                                       |                |                |                 |                  |             |  |  |  |  |

| bit 3            |                                                                                                                                                                       | BRG16: 16-bit Baud Rate Generator bit |                |                |                 |                  |             |  |  |  |  |

|                  | 1 = 16-bit Baud Rate Generator is used<br>0 = 8-bit Baud Rate Generator is used                                                                                       |                                       |                |                |                 |                  |             |  |  |  |  |

| bit 2            | Unimplemen                                                                                                                                                            | ted: Read as '                        | 0'             |                |                 |                  |             |  |  |  |  |

| bit 1            | WUE: Wake-                                                                                                                                                            | up Enable bit                         |                |                |                 |                  |             |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                                    |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | <ul> <li>1 = Receiver is waiting for a falling edge. No character will be received, byte RCIF will be set. WUE will automatically clear after RCIF is set.</li> </ul> |                                       |                |                |                 |                  |             |  |  |  |  |

|                  |                                                                                                                                                                       | is operating no                       | ormally        |                |                 |                  |             |  |  |  |  |

|                  | Synchronous mode:                                                                                                                                                     |                                       |                |                |                 |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                                            |                                       |                |                |                 |                  |             |  |  |  |  |

| bit 0            |                                                                                                                                                                       | o-Baud Detect                         | Enable bit     |                |                 |                  |             |  |  |  |  |

|                  | Asynchronou                                                                                                                                                           |                                       |                |                |                 |                  |             |  |  |  |  |

|                  |                                                                                                                                                                       |                                       |                | clears when au | to-baud is com  | plete)           |             |  |  |  |  |

|                  | 0 = Auto-Bau                                                                                                                                                          | ud Detect mode                        | e is disabled  |                |                 |                  |             |  |  |  |  |

|                  | SYNCHIONOUS                                                                                                                                                           | moue.                                 |                |                |                 |                  |             |  |  |  |  |

## REGISTER 18-3: BAUDCON: BAUD RATE CONTROL REGISTER

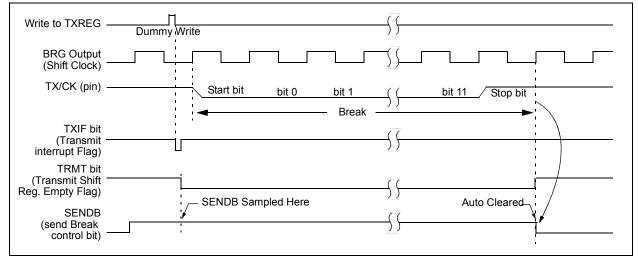

## 18.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-9 for the timing of the Break character sequence.

#### 18.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 18.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 18.4.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### FIGURE 18-9: SEND BREAK CHARACTER SEQUENCE

## 18.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 18.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

The TRIS bits corresponding to the RX/DT and TX/CK pins should be set.

#### 18.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 18.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock and is sampled on the rising edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock and is sampled on the falling edge of each clock.

#### 18.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 18.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RX/DT and TX/ CK I/O pins.

- 4. Disable Receive mode by clearing bits SREN and CREN.

- 5. Enable Transmit mode by setting the TXEN bit.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXIE, GIE and PEIE interrupt enable bits.

- 8. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 9. Start transmission by loading data to the TXREG register.

| Mnen    | nonic, |                                     |              | 14-Bit Opcode |      |      |      | Status   |       |

|---------|--------|-------------------------------------|--------------|---------------|------|------|------|----------|-------|

|         | ands   | Description                         | Cycles       | MSb           |      |      | LSb  | Affected | Notes |

|         |        | BYTE-ORIENTED FILE I                | REGISTER OPE | RATIC         | NS   |      |      |          |       |

| ADDWF   | f, d   | Add W and f                         | 1            | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC  | f, d   | Add with Carry W and f              | 1            | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF   | f, d   | AND W with f                        | 1            | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF    | f, d   | Arithmetic Right Shift              | 1            | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF    | f, d   | Logical Left Shift                  | 1            | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF    | f, d   | Logical Right Shift                 | 1            | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF    | f      | Clear f                             | 1            | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW    | _      | Clear W                             | 1            | 00            | 0001 | 0000 | 00xx | z        |       |

| COMF    | f. d   | Complement f                        | 1            | 00            | 1001 | dfff | ffff | z        | 2     |

| DECF    | f. d   | Decrement f                         | 1            | 0.0           | 0011 | dfff | ffff | z        | 2     |

| INCF    | f. d   | Increment f                         | 1            | 00            |      | dfff |      | z        | 2     |

| IORWF   | f, d   | Inclusive OR W with f               | 1            | 00            | 0100 |      | ffff | Z        | 2     |

| MOVF    | f. d   | Move f                              | 1            | 00            |      | dfff |      | Z        | 2     |

| MOVWF   | f, G   | Move W to f                         | 1            | 00            | 0000 | 1fff |      | 2        | 2     |

| RLF     | f. d   | Rotate Left f through Carry         | 1            | 00            |      | dfff |      | с        | 2     |

| RRF     | f, d   | Rotate Right f through Carry        | 1            | 00            |      | dfff |      | c        | 2     |

| SUBWF   | f, d   | Subtract W from f                   | 1            |               |      | dfff |      | -        | 2     |

| SUBWFB  | f, d   | Subtract with Borrow W from f       | 1            | 00<br>11      |      |      |      |          | 2     |

|         | ,      |                                     | 1            |               |      | dfff |      | C, DC, Z | 2     |

| SWAPF   | f, d   | Swap nibbles in f                   | 1            | 00            |      | dfff |      | 7        | 2     |

| XORWF   | f, d   | Exclusive OR W with f BYTE ORIENTED |              | 00            | 0110 | aiii | ffff | Z        | 2     |

|         |        | -                                   |              |               |      |      |      |          | 4.0   |

| DECFSZ  | f, d   | Decrement f, Skip if 0              | 1(2)         | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ  | f, d   | Increment f, Skip if 0              | 1(2)         | 00            | 1111 | dfff | ffff |          | 1, 2  |

|         |        | BIT-ORIENTED FILE R                 | EGISTER OPER | ATION         | IS   |      |      |          |       |

| BCF     | f, b   | Bit Clear f                         | 1            | 01            | 00bb | bfff | ffff |          | 2     |

| BSF     | f, b   | Bit Set f                           | 1            | 01            | 01bb | bfff | ffff |          | 2     |

|         |        | BIT-ORIENTED S                      | KIP OPERATIO | NS            |      |      |      |          |       |

| BTFSC   | f, b   | Bit Test f, Skip if Clear           | 1 (2)        | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS   | f, b   | Bit Test f, Skip if Set             | 1 (2)        | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL |        |                                     |              |               |      |      |      |          |       |

| ADDLW   | k      | Add literal and W                   | 1            | 11            | 1110 | kkkk | kkkk | C, DC, Z |       |

| ANDLW   | k      | AND literal with W                  | 1            | 11            | 1001 | kkkk | kkkk | Z        |       |

| IORLW   | k      | Inclusive OR literal with W         | 1            | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLB   | k      | Move literal to BSR                 | 1            | 00            | 0000 | 001k | kkkk |          |       |

| MOVLP   | k      | Move literal to PCLATH              | 1            | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW   | k      | Move literal to W                   | 1            | 11            | 0000 | kkkk | kkkk |          |       |

| SUBLW   | k      | Subtract W from literal             | 1            | 11            | 1100 | kkkk | kkkk | C, DC, Z |       |

| CODL    |        |                                     |              |               |      |      |      |          |       |

## TABLE 21-3: PIC16LF1904/6/7 ENHANCED INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

# PIC16LF1904/6/7

## 21.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  |                                                                                               |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \le k \le 255$                                                                                               |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDLW k                                                                                             |