Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1906-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Dedicated low-power 32 kHz oscillator driver

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- Auto-wake-up on start

# PIC16LF190X Family Types

|             | lex<br>ory<br>h)<br>h) |                                 |                      |                              |                      | LCD             |                      |        |             |              |                   |                      |     |

|-------------|------------------------|---------------------------------|----------------------|------------------------------|----------------------|-----------------|----------------------|--------|-------------|--------------|-------------------|----------------------|-----|

| Device      | Data Sheet Index       | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Fl<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | Timers<br>(8/16-bit) | EUSART | Common Pins | Segment Pins | Total Segments    | Debug <sup>(1)</sup> | ХГР |

| PIC16LF1902 | (1)                    | 2048                            | 128                  | 128                          | 25                   | 11              | 1/1                  |        | 4           | 19           | 72 <sup>(3)</sup> | Н                    | Y   |

| PIC16LF1903 | (1)                    | 4096                            | 256                  | 128                          | 25                   | 11              | 1/1                  | _      | 4           | 19           | 72 <sup>(3)</sup> | Н                    | Y   |

| PIC16LF1904 | (2)                    | 4096                            | 256                  | 128                          | 36                   | 14              | 1/1                  | 1      | 4           | 29           | 116               | I/H                  | Y   |

| PIC16LF1906 | (2)                    | 8192                            | 512                  | 128                          | 25                   | 11              | 1/1                  | 1      | 4           | 19           | 72 <sup>(3)</sup> | I/H                  | Y   |

| PIC16LF1907 | (2)                    | 8192                            | 512                  | 128                          | 36                   | 14              | 1/1                  | 1      | 4           | 29           | 116               | I/H                  | Y   |

Note 1: Debugging Methods: (I) – Integrated on Chip; (H) – using Debug Header; (E) – using Emulation Header.

2: One pin is input-only.

3: COM3 and SEG15 share a pin, so the total segments are limited to 72 for 28-pin devices.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS40001455 PIC16LF1902/3 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001569 PIC16LF1904/6/7 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

# PIC16LF1904/6/7

#### TADIE 2 5. SPECIAL EUNCTION DECISTED SUMMARY (CONTINUED)

| TABI                                           | _E 3-5: S               | SPECIAL       | FUNCTI        | ON REG        | ISTER S       | UMMAR         | Y (CONT       | INUED)        |               |                      |                                 |

|------------------------------------------------|-------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------------------|---------------------------------|

| Addr                                           | Name                    | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Ban                                            | k 7                     |               |               |               |               |               |               |               |               | •                    |                                 |

| 38Ch<br><br>393h                               | _                       | Unimpleme     | ented         |               |               |               |               |               |               | _                    | —                               |

| 394h                                           | IOCBP                   | IOCBP7        | IOCBP6        | IOCBP5        | IOCBP4        | IOCBP3        | IOCBP2        | IOCBP1        | IOCBP0        | 0000 0000            | 0000 0000                       |

| 395h                                           | IOCBN                   | IOCBN7        | IOCBN6        | IOCBN5        | IOCBN4        | IOCBN3        | IOCBN2        | IOCBN1        | IOCBN0        | 0000 0000            | 0000 0000                       |

| 396h                                           | IOCBF                   | IOCBF7        | IOCBF6        | IOCBF5        | IOCBF4        | IOCBF3        | IOCBF2        | IOCBF1        | IOCBF0        | 0000 0000            | 0000 0000                       |

| 397h<br>—                                      | _                       | Unimpleme     | ented         | 1             | 1             |               | 1             | 1             |               | -                    | —                               |

| 39Fh                                           |                         |               |               |               |               |               |               |               |               |                      |                                 |

| r                                              | k 8-14                  |               |               |               |               |               |               |               |               |                      |                                 |

| x0Ch<br>or<br>x8Ch<br>to<br>x1Fh<br>or<br>x9Fh | _                       | Unimpleme     | ented         |               |               |               |               |               |               | _                    | _                               |

|                                                | k 15                    |               |               |               |               |               |               |               |               |                      | 1                               |

| 78Ch                                           | _                       | Unimpleme     | ented         |               |               |               |               |               |               | _                    | _                               |

| <br>790h                                       |                         |               |               |               |               |               |               |               |               |                      |                                 |

| 791h                                           | LCDCON                  | LCDEN         | SLPEN         | WERR          | —             | CS1           | CS0           | LMUX1         | LMUX0         | 000- 0011            | 000- 0011                       |

| 792h                                           | LCDPS                   | WFT           | BIASMD        | LCDA          | WA            | LP3           | LP2           | LP1           | LP0           | 0000 0000            | 0000 0000                       |

| 793h                                           | LCDREF                  | LCDIRE        | —             | LCDIRI        | —             | VLCD3PE       | VLCD2PE       | VLCD1PE       | —             | 0-0- 000-            | 0-0- 000-                       |

| 794h                                           | LCDCST                  | —             | _             | —             | _             | —             | LCDCST2       | LCDCST1       | LCDCST0       | 000                  | 000                             |

| 795h                                           | LCDRL                   | LRLAP1        | LRLAP0        | LRLBP1        | LRLBP0        | —             | LRLAT2        | LRLAT1        | LRLAT0        | 0000 -000            | 0000 -000                       |

| 796h                                           | _                       | Unimpleme     |               |               |               |               |               |               |               |                      | _                               |

| 797h                                           | -                       | Unimpleme     | 1             | 077           | 051           | 050           | 0.50          | 054           | 050           | —                    | —                               |

| 798h                                           | LCDSE0                  | SE7           | SE6           | SE5           | SE4           | SE3           | SE2           | SE1           | SE0           | 0000 0000            | uuuu uuuu                       |

| 799h                                           | LCDSE1                  | SE15          | SE14          | SE13          | SE12          | SE11          | SE10          | SE9           | SE8           | 0000 0000            | uuuu uuuu                       |

| 79Ah                                           | LCDSE2                  | SE23          | SE22          | SE21          | SE20          | SE19          | SE18          | SE17          | SE16          | 0000 0000            | uuuu uuuu                       |

| 79Bh                                           | LCDSE3                  | —             |               | —             | SE28          | SE27          | SE26          | SE25          | SE24          | 0 0000               | u uuuu                          |

| 79Dh<br><br>79Fh                               | _                       | Unimpleme     | inted         |               |               |               |               |               |               | _                    | _                               |

| 7A0h                                           | LCDDATA0                | SEG7<br>COM0  | SEG6<br>COM0  | SEG5<br>COM0  | SEG4<br>COM0  | SEG3<br>COM0  | SEG2<br>COM0  | SEG1<br>COM0  | SEG0<br>COM0  | XXXX XXXX            | uuuu uuuu                       |

| 7A1h                                           | LCDDATA1                | SEG15<br>COM0 | SEG14<br>COM0 | SEG13<br>COM0 | SEG12<br>COM0 | SEG11<br>COM0 | SEG10<br>COM0 | SEG9<br>COM0  | SEG8<br>COM0  | XXXX XXXX            | uuuu uuuu                       |

| 7A2h                                           | LCDDATA2 <sup>(3)</sup> | SEG23<br>COM0 | SEG22<br>COM0 | SEG21<br>COM0 | SEG20<br>COM0 | SEG19<br>COM0 | SEG18<br>COM0 | SEG17<br>COM0 | SEG16<br>COM0 | XXXX XXXX            | uuuu uuuu                       |

| 7A3h                                           | LCDDATA3                | SEG7<br>COM1  | SEG6<br>COM1  | SEG5<br>COM1  | SEG4<br>COM1  | SEG3<br>COM1  | SEG2<br>COM1  | SEG1<br>COM1  | SEG0<br>COM1  | XXXX XXXX            | uuuu uuuu                       |

| 7A4h                                           | LCDDATA4                | SEG15<br>COM1 | SEG14<br>COM1 | SEG13<br>COM1 | SEG12<br>COM1 | SEG11<br>COM1 | SEG10<br>COM1 | SEG9<br>COM1  | SEG8<br>COM1  | XXXX XXXX            | uuuu uuuu                       |

| 7A5h                                           | LCDDATA5 <sup>(3)</sup> | SEG23<br>COM1 | SEG22<br>COM1 | SEG21<br>COM1 | SEG20<br>COM1 | SEG19<br>COM1 | SEG18<br>COM1 | SEG17<br>COM1 | SEG16<br>COM1 | XXXX XXXX            | uuuu uuuu                       |

| 7A6h                                           | LCDDATA6                | SEG7<br>COM2  | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2  | SEG0<br>COM2  | XXXX XXXX            |                                 |

| 7A7h                                           |                         | SEG15<br>COM2 | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2  | SEG8<br>COM2  | XXXX XXXX            |                                 |

| 7A8h                                           | LCDDATA8 <sup>(3)</sup> | SEG23<br>COM2 | SEG22<br>COM2 | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | XXXX XXXX            | uuuu uuuu                       |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

Unimplemented, read as '1'. PIC16LF1904/7 only. 2:

3:

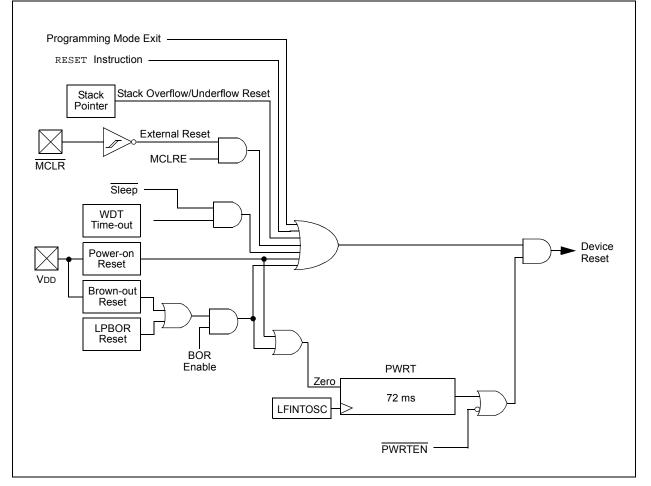

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 5-1.

# 5.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 2011-2016 Microchip Technology Inc.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|-------|-------|---------|-------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE  | IOCIE | TMR0IF  | INTF  | IOCIF  | 65                  |

| OPTION_REG | WPUEN   | INTEDG | TOCS   | T0SE  | PSA   | PS<2:0> |       |        | 130                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE  | _     | _       | _     | TMR1IE | 66                  |

| PIE2       | _       | _      | _      | _     | _     | LCDIE   | _     | _      | 67                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF  | _     | _       | _     | TMR1IF | 68                  |

| PIR2       | _       | _      | _      | _     | _     | LCDIF   |       |        | 69                  |

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupts.

# 9.6 Watchdog Control Register

| U-0            | U-0                    | R/W-0/0                                                          | R/W-1/1        | R/W-0/0                   | R/W-1/1        | R/W-1/1         | R/W-0/0      |

|----------------|------------------------|------------------------------------------------------------------|----------------|---------------------------|----------------|-----------------|--------------|

| _              | —                      |                                                                  |                | WDTPS<4:0>                |                |                 | SWDTEN       |

| oit 7          | ÷                      | ·                                                                |                |                           |                |                 | bit 0        |

|                |                        |                                                                  |                |                           |                |                 |              |

| Legend:        |                        |                                                                  |                |                           |                |                 |              |

| R = Readat     | ole bit                | W = Writable                                                     | bit            | U = Unimpleme             | ented bit, rea | d as '0'        |              |

| u = Bit is ur  | changed                | x = Bit is unkr                                                  | nown           | -m/n = Value at           | POR and B      | OR/Value at all | other Resets |

| '1' = Bit is s | et                     | '0' = Bit is clea                                                | ared           |                           |                |                 |              |

|                |                        |                                                                  |                |                           |                |                 |              |

| bit 7-6        | Unimpleme              | ented: Read as '                                                 | 0'             |                           |                |                 |              |

| bit 5-1        | WDTPS<4:               | 0>: Watchdog Ti                                                  | mer Period S   | elect bits <sup>(1)</sup> |                |                 |              |

|                | Bit Value =            | Prescale Rate                                                    |                |                           |                |                 |              |

|                | 00000 = 1              | :32 (Interval 1 m                                                | s nominal)     |                           |                |                 |              |

|                | 00001 = 1              | :64 (Interval 2 m                                                | s nominal)     |                           |                |                 |              |

|                |                        | :128 (Interval 4 r                                               |                |                           |                |                 |              |

|                |                        | :256 (Interval 8 r                                               |                |                           |                |                 |              |

|                |                        | :512 (Interval 16<br>:1024 (Interval 3                           | ,              |                           |                |                 |              |

|                |                        | :2048 (Interval 6                                                |                |                           |                |                 |              |

|                |                        | :4096 (Interval 1                                                |                |                           |                |                 |              |

|                | 01000 = 1              | :8192 (Interval 2                                                | 56 ms nomin    | al)                       |                |                 |              |

|                |                        | :16384 (Interval                                                 |                | nal)                      |                |                 |              |

|                |                        | :32768 (Interval                                                 |                |                           |                |                 |              |

|                | 01011 = 1              | :65536 (Interval                                                 | 2s nominal)    | (Reset value)             |                |                 |              |

|                | 01100 = 1              | :131072 (2 <sup>17</sup> ) (Ir<br>:262144 (2 <sup>18</sup> ) (Ir | iterval 45 nor | ninal)<br>ninal)          |                |                 |              |

|                | 01101 - 1<br>01110 = 1 | :524288 (2 <sup>19</sup> ) (Ir                                   | iterval 16s no | ominal)                   |                |                 |              |

|                | 01111 = <b>1</b>       | ·1048576 (2 <sup>20</sup> ) (                                    | Interval 32s r | nominal)                  |                |                 |              |

|                | 10000 <b>= 1</b>       | :2097152 (2 <sup>21</sup> ) (                                    | Interval 64s r | nominal)                  |                |                 |              |

|                | 10001 = <b>1</b>       | :4194304 (2 <sup>22</sup> ) (                                    | Interval 128s  | nominal)                  |                |                 |              |

|                | 10010 <b>= 1</b>       | :8388608 (2 <sup>23</sup> ) (                                    | Interval 256s  | nominal)                  |                |                 |              |

|                | 10011 = 🗟              | eserved. Result                                                  | s in minimum   | interval (1:32)           |                |                 |              |

|                | •                      |                                                                  |                |                           |                |                 |              |

|                | •                      |                                                                  |                |                           |                |                 |              |

|                | •<br>11111 = R         | eserved. Result                                                  | s in minimum   | interval (1:32)           |                |                 |              |

| bit 0          |                        |                                                                  |                | Vatchdog Timer bi         | it             |                 |              |

|                | If WDTE<1:             |                                                                  |                | vaterialog miller b       | it i           |                 |              |

|                | This bit is ig         |                                                                  |                |                           |                |                 |              |

|                | If WDTE<1:             |                                                                  |                |                           |                |                 |              |

|                | 1 = WDT is             |                                                                  |                |                           |                |                 |              |

|                | 0 = WDT is             |                                                                  |                |                           |                |                 |              |

|                | If WDTE<1:             |                                                                  |                |                           |                |                 |              |

|                | This bit is ig         |                                                                  |                |                           |                |                 |              |

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

# PIC16LF1904/6/7

| Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-------|-------|-----------|-------|------------|-------|-------|--------|---------------------|

| OSCCON | —     |       | IRCF<3:0> |       |            |       | SCS   | 58     |                     |

| STATUS | —     | _     | —         | TO    | PD         | Z     | DC    | С      | 21                  |

| WDTCON | —     | _     |           |       | WDTPS<4:0> | >     |       | SWDTEN | 75                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|----------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | _        | _         | CLKOUTEN | BORE     | N<1:0> — |         | 20                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | —        | FOSC     | C<1:0>  | 39                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

### 10.6 Flash Program Memory Control Registers

#### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u             | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u         | R/W-x/u             | R/W-x/u              | R/W-x/u |

|---------------------|---------|----------------------|---------|-----------------|---------------------|----------------------|---------|

|                     |         |                      | PMDA    | T<7:0>          |                     |                      |         |

| bit 7               |         |                      |         |                 |                     |                      | bit 0   |

|                     |         |                      |         |                 |                     |                      |         |

| Legend:             |         |                      |         |                 |                     |                      |         |

| R = Readable bit    |         | W = Writable bit     |         | U = Unimpleme   | nted bit, read as ' | 0'                   |         |

| u = Bit is unchange | d       | x = Bit is unknown   |         | -n/n = Value at | POR and BOR/Va      | lue at all other Res | sets    |

| '1' = Bit is set    |         | '0' = Bit is cleared |         |                 |                     |                      |         |

bit 7-0

PMDAT<7:0>: Read/write value for Least Significant bits of program memory

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|----------|---------|---------|

| _     | —   |         |         | PMDA    | AT<13:8> |         |         |

| bit 7 |     |         |         |         |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0       | R/W-0/0               | R/W-0/0 | R/W-0/0 |

|------------------|---------|------------------|---------|---------------|-----------------------|---------|---------|

|                  |         |                  | PMAD    | R<7:0>        |                       |         |         |

| bit 7            |         |                  |         |               |                       |         | bit 0   |

|                  |         |                  |         |               |                       |         |         |

| Legend:          |         |                  |         |               |                       |         |         |

| R = Readable bit |         | W = Writable bit |         | U = Unimpleme | ented bit, read as '0 | )'      |         |

| R = Readable bit     | vv = vvritable bit   | U = Unimplemented bit, read as 'U'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| —     |         |         |         | PMADR<14:8> | >       |         |         |

| bit 7 | bit 0   |         |         |             |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

| R/W-x/x              | R/W-x/x                                                                 | R/W-x/x        | R/W-x/x            | R-x/x     | R/W-x/x                            | R/W-x/x | R/W-x/x |

|----------------------|-------------------------------------------------------------------------|----------------|--------------------|-----------|------------------------------------|---------|---------|

| RA7                  | RA6                                                                     | RA5            | RA4                | RA3       | RA2                                | RA1     | RA0     |

| bit 7                | •                                                                       | ·              |                    |           | •                                  |         | bit 0   |

|                      |                                                                         |                |                    |           |                                    |         |         |

| Legend:              |                                                                         |                |                    |           |                                    |         |         |

| R = Readable bit W = |                                                                         | W = Writable b | W = Writable bit   |           | U = Unimplemented bit, read as '0' |         |         |

| u = Bit is uncha     | nchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all of |                | /Value at all othe | er Resets |                                    |         |         |

|                      | '1' = Bit is set                                                        |                | red                |           |                                    |         |         |

#### REGISTER 11-1: PORTA: PORTA REGISTER

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTA are actually written to the corresponding LATA register. Reads from the PORTA register is return of actual I/O pin values.

#### REGISTER 11-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|--------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3 | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |        |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | <b>TRISA&lt;7:4&gt;:</b> PORTA Tri-State Control bits<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>TRISA3:</b> RA3 Port Tri-State Control bit<br>This bit is always '1' as RA3 is an input only                                                     |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bits<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

#### REGISTER 11-3: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 LATA<7:0>: RA<7:4> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to the corresponding LATA register. Reads from the PORTA register is return of actual I/O pin values.

### 15.2 ADC Operation

#### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 15.2.5 "A/D Conversion  |

|       | Procedure".                              |

#### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 15.2.6 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 15-1: ADCON0: A/D CONTROL REGISTER 0

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|----------|---------|---------|---------|---------|

| _     |         |         | CHS<4:0> |         |         | GO/DONE | ADON    |

| bit 7 |         |         |          |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                             |

|---------|----------------------------------------------------------------------------------------|

| bit 6-2 | CHS<4:0>: Analog Channel Select bits                                                   |

|         | 00000 = ANO                                                                            |

|         | 00001 = AN1                                                                            |

|         | 00010 = AN2                                                                            |

|         | 00011 = AN3                                                                            |

|         | 00100 = AN4                                                                            |

|         | $00101 = AN5^{(3)}$                                                                    |

|         | $00110 = AN6^{(3)}$                                                                    |

|         | $00111 = AN7^{(3)}$                                                                    |

|         | 01000 = AN8                                                                            |

|         | 01001 = AN9                                                                            |

|         | 01010 = AN10<br>01011 = AN11                                                           |

|         | 01100 = AN12                                                                           |

|         | 01101 = AN13                                                                           |

|         | 01110 = Reserved. No channel connected.                                                |

|         | •                                                                                      |

|         | •                                                                                      |

|         | •                                                                                      |

|         | 11100 = Reserved. No channel connected.                                                |

|         | 11101 = Temperature Indicator <sup>(2)</sup>                                           |

|         | 11110 = Reserved. No channel connected.                                                |

|         | 11111 = FVR (Fixed Voltage Reference) Buffer 1 Output <sup>(1)</sup>                   |

| bit 1   | GO/DONE: A/D Conversion Status bit                                                     |

|         | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. |

|         | This bit is automatically cleared by hardware when the A/D conversion has completed.   |

|         | 0 = A/D conversion completed/not in progress                                           |

| bit 0   | ADON: ADC Enable bit                                                                   |

|         | 1 = ADC is enabled                                                                     |

|         | 0 = ADC is disabled and consumes no operating current                                  |

| Note 1: | See Section 13.0 "Fixed Voltage Reference (FVR)" for more information.                 |

| 2:      | See Section 14.0 "Temperature Indicator Module" for more information.                  |

|         | ADC channel is reserved on the PIC16LF1906 28-pin device.                              |

| 5.      | Abe chambers reserved on the Fronce ratio 20-pin device.                               |

# 17.9 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 17-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 17-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u          | R/W-0/u              | R/W-0/u                             | R/W-0/u          | R/W-0/u          | R/W-0/u          | U-0              | R/W-0/u      |

|------------------|----------------------|-------------------------------------|------------------|------------------|------------------|------------------|--------------|

| TMR1CS<1:0>      |                      | T1CKF                               | PS<1:0>          | T1OSCEN          | T1SYNC           | _                | TMR10N       |

| bit 7            |                      |                                     |                  |                  |                  |                  | bit 0        |

|                  |                      |                                     |                  |                  |                  |                  |              |

| Legend:          |                      |                                     |                  |                  |                  |                  |              |

| R = Readable     | bit                  | W = Writable                        | bit              | U = Unimplem     | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged                | x = Bit is unkr                     | nown             | -n/n = Value a   | t POR and BC     | R/Value at all o | other Resets |

| '1' = Bit is set |                      | '0' = Bit is cle                    | ared             |                  |                  |                  |              |

| bit 7-6          | TMD1CS-1.0           | <b>)&gt;:</b> Timer1 Clo            | ak Source Sol    | at hita          |                  |                  |              |

| DIL 7-0          |                      |                                     | sk Source Sele   |                  |                  |                  |              |

|                  | 11 = Reserve         | clock source is                     | nin or oscillato | nr.              |                  |                  |              |

|                  |                      | $\frac{\text{CEN} = 0}{\text{CEN}}$ |                  |                  |                  |                  |              |

|                  | External             | clock from T10                      | CKI pin (on the  | e rising edge)   |                  |                  |              |

|                  | If T1OS              |                                     |                  | ·                |                  |                  |              |

|                  | •                    | oscillator on T1<br>clock source is |                  |                  |                  |                  |              |

|                  |                      | clock source is                     |                  |                  |                  |                  |              |

| bit 5-4          |                      | >: Timer1 Inpu                      |                  | . ,              |                  |                  |              |

|                  | 11 = 1:8 Pres        | scale value                         |                  |                  |                  |                  |              |

|                  | 10 = 1:4 Pres        |                                     |                  |                  |                  |                  |              |

|                  | 01 = 1:2 Pres        |                                     |                  |                  |                  |                  |              |

| bit 3            |                      | P Oscillator En                     | able Control h   | it               |                  |                  |              |

| Sit 0            |                      | d Timer1 oscill                     |                  |                  |                  |                  |              |

|                  |                      | d Timer1 oscill                     |                  |                  |                  |                  |              |

| bit 2            | T1SYNC: Tim          | ner1 External C                     | lock Input Syr   | nchronization Co | ontrol bit       |                  |              |

|                  | <u>TMR1CS&lt;1:0</u> |                                     |                  |                  |                  |                  |              |

|                  |                      | ynchronize exte                     |                  |                  |                  |                  |              |

|                  | 0 = Synchron         | nize external cl                    | OCK INPUT WITH   | system clock (F  | -OSC)            |                  |              |

|                  | <u>TMR1CS&lt;1:0</u> | )> = 0X                             |                  |                  |                  |                  |              |

|                  | This bit is ign      | ored. Timer1 u                      | ses the interna  | al clock when TI | MR1CS<1:0> =     | = 1X.            |              |

| bit 1            | Unimplemen           | ted: Read as '                      | 0'               |                  |                  |                  |              |

| bit 0            | TMR1ON: Tir          | mer1 On bit                         |                  |                  |                  |                  |              |

|                  | 1 = Enables          | -                                   |                  |                  |                  |                  |              |

|                  | 0 = Stops Tir        | mer1<br>mer1 gate flip-             | flon             |                  |                  |                  |              |

|                  |                      | mein gate mp-                       | noh              |                  |                  |                  |              |

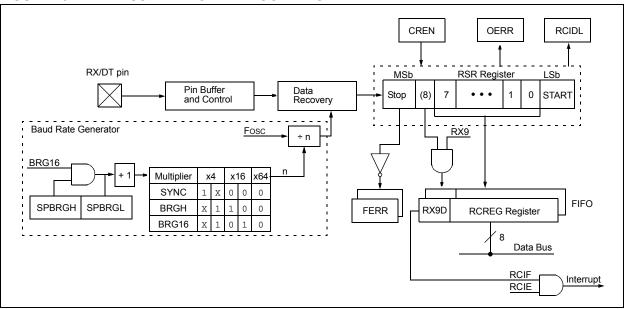

FIGURE 18-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 18-1, Register 18-2 and Register 18-3, respectively.

For all modes of EUSART operation, the TRIS control bits corresponding to the RX/DT and TX/CK pins should be set to '1'. The EUSART control will automatically reconfigure the pin from input to output, as needed.

When the receiver or transmitter section is not enabled then the corresponding RX/DT or TX/CK pin may be used for general purpose input and output.

### 18.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 18-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 18.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 18-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 18.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXIF transmitter interrupt flag is set when the TXEN enable bit is set.

#### 18.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 18.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit Idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true Idle and data bits. The SCKP bit controls transmit data polarity only in Asynchronous mode. In Synchronous mode the SCKP bit has a different function. See **Section 18.5.1.2 "Clock Polarity"**.

#### 18.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of the TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

| Name     | Bit 7                                 | Bit 6  | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------------------------------------|--------|---------------------|---------------------|--------|--------|--------|--------|---------------------|

| BAUD1CON | ABDOVF                                | RCIDL  | —                   | SCKP                | BRG16  | _      | WUE    | ABDEN  | 153                 |

| BAUD2CON | ABDOVF                                | RCIDL  | _                   | SCKP                | BRG16  |        | WUE    | ABDEN  | 153                 |

| INTCON   | GIE                                   | PEIE   | TMR0IE              | INTE                | IOCIE  | TMR0IF | INTF   | IOCIF  | 65                  |

| PIE1     | TMR1GIE                               | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | —      | —      | —      | TMR1IE | 66                  |

| PIR1     | TMR1GIF                               | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —      | —      | —      | TMR1IF | 68                  |

| RCSTA    | SPEN                                  | RX9    | SREN                | CREN                | ADDEN  | FERR   | OERR   | RX9D   | 152                 |

| SPBRGL   | EUSART Baud Rate Generator, Low Byte  |        |                     |                     |        |        |        | 154*   |                     |

| SPBRGH   | EUSART Baud Rate Generator, High Byte |        |                     |                     |        |        | 154*   |        |                     |

| TRISC    | TRISC7                                | TRISC6 | TRISC5              | TRISC4              | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 98                  |

| TXREG    | EUSART Transmit Register              |        |                     |                     |        |        |        |        | 144*                |

| TXSTA    | CSRC                                  | TX9    | TXEN                | SYNC                | SENDB  | BRGH   | TRMT   | TX9D   | 151                 |

#### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous slave transmission.

\* Page provides register information.

Note 1: PIC16LF1904/7 only.

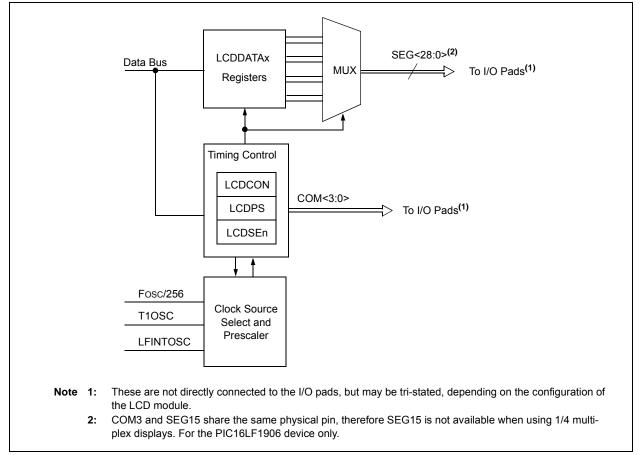

# 19.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16LF1904/6/7 device, the module drives the panels of up to four commons and up to 116 total segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- · Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- 19 Segment pins (PIC16LF1906 only)

- 29 Segment pins (PIC16LF1904/7 only)

• Static, 1/2 or 1/3 LCD Bias

Note: COM3 and SEG15 share the same physical pin on the PIC16LF1906, therefore SEG15 is not available when using 1/4 multiplex displays.

## 19.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 4 LCD Segment Enable registers (LCDSEn)

- Up to 16 LCD data registers (LCDDATAn)

#### FIGURE 19-1: LCD DRIVER MODULE BLOCK DIAGRAM

#### TABLE 19-1: LCD SEGMENT AND DATA REGISTERS

|               | # of LCD Registers |      |  |

|---------------|--------------------|------|--|

| Device        | Segment<br>Enable  | Data |  |

| PIC16LF1904/7 | 3                  | 16   |  |

| PIC16LF1906   | 4                  | 12   |  |

The LCDCON register (Register 19-1) controls the operation of the LCD driver module. The LCDPS register (Register 19-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 19-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

- LCDSE2 SE<23:16>(1)

- LCDSE3 SE<28:24><sup>(1)</sup> (SE<26:24><sup>(2)</sup>)

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA2 SEG<23:16>COM0<sup>(1)</sup>

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA5 SEG<23:16>COM1<sup>(1)</sup>

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA8 SEG<23:16>COM2<sup>(1)</sup>

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

- LCDDATA11 SEG<23:16>COM3(1)

- LCDDATA12 SEG<28:24>COM0<sup>(1)</sup> (SEG<26:24>)<sup>(2)</sup>

- LCDDATA15 SEG<28:24>COM1<sup>(1)</sup> (SEG<26:24>)<sup>(2)</sup>

- LCDDATA18 SEG<28:24>COM2<sup>(1)</sup> (SEG<26:24>)<sup>(2)</sup>

- LCDDATA21 SEG<28:24>COM3<sup>(1)</sup> (SEG<26:24>)<sup>(2)</sup>

Note 1: PIC16LF1904/7 only.

2: PIC16LF1906 only.

As an example, LCDDATAn is detailed in Register 19-6.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

| R/W-0/0                   | R/W-0/0                                                                                                                                             | R/C-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                        | R/W-0/0                                | R/W-0/0                               | R/W-1/1          | R/W-1/1      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|---------------------------------------|------------------|--------------|

| LCDEN                     | SLPEN                                                                                                                                               | WERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                          | (                                      | CS<1:0>                               | LMU>             | <1:0>        |

| bit 7                     | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                       |                  | bit          |

|                           |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                       |                  |              |