Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1906t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | IDEX                |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

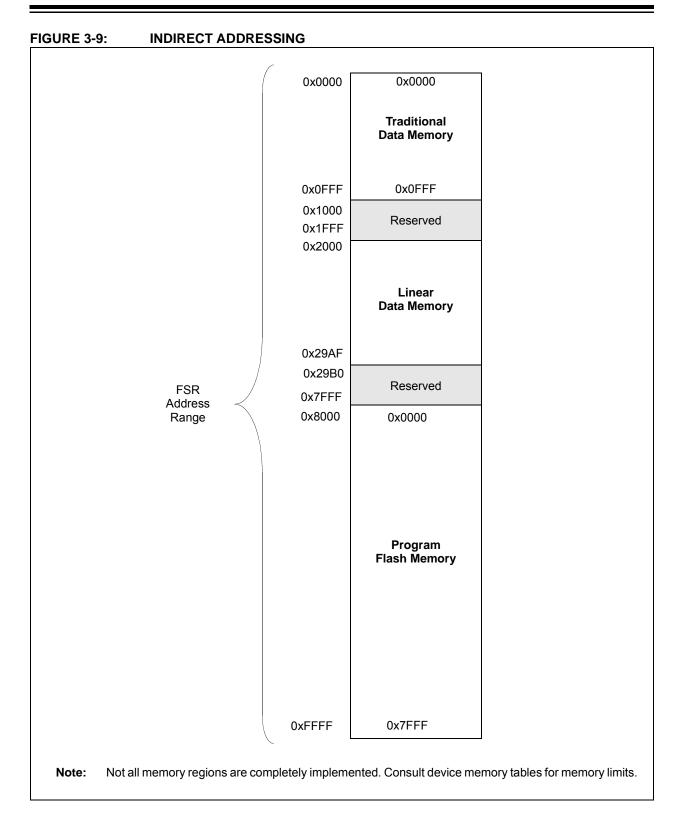

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants   |               |         |      |

|-------------|---------------|---------|------|

| RETLW       | DATA0         | ;Index0 | data |

| RETLW       | DATA1         | ;Index1 | data |

| RETLW       | DATA2         |         |      |

| RETLW       | DATA3         |         |      |

| my_function | on            |         |      |

| ; LOI       | IS OF CODE    |         |      |

| MOVLW       | LOW constan   | ts      |      |

| MOVWF       | FSR1L         |         |      |

| MOVLW       | HIGH consta   | nts     |      |

| MOVWF       | FSR1H         |         |      |

| MOVIW       | 0[FSR1]       |         |      |

| ; THE PROG  | RAM MEMORY IS | IN W    |      |

#### 5.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation<br>upon release of POR | Device Operation<br>upon wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|-----------------------------------------|-------------------------------------------------|--|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready                     |                                                 |  |

| 10         | Х      | Sleep       | Disabled |                                         |                                                 |  |

| 0.1        | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |

| 01         | 0      | х           | Disabled | Begins immediately                      |                                                 |  |

| 00         | х      | х           | Disabled | Begins immediately                      |                                                 |  |

#### TABLE 5-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## 6.4 Oscillator Control Registers

## REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0            | R/W-0/0                              | R/W-1/1              | R/W-1/1      | R/W-1/1         | U-0            | R/W-0/0         | R/W-0/0      |

|----------------|--------------------------------------|----------------------|--------------|-----------------|----------------|-----------------|--------------|

| _              |                                      | IRCF                 | <3:0>        |                 | _              | SCS             | <1:0>        |

| oit 7          |                                      |                      |              |                 |                |                 | bit C        |

| egend:         |                                      |                      |              |                 |                |                 |              |

| R = Readabl    | le hit                               | W = Writable         | bit          | U = Unimplem    | nented bit rea | d as '0'        |              |

| i = Bit is und |                                      | x = Bit is unkr      |              | •               |                | DR/Value at all | other Resets |

| 1' = Bit is se | •                                    | '0' = Bit is clea    |              |                 |                |                 |              |

|                |                                      |                      |              |                 |                |                 |              |

| oit 7          | Unimplem                             | nented: Read as '    | 0'           |                 |                |                 |              |

| oit 6-3        | IRCF<3:0                             | Internal Oscillat    | or Frequency | Select bits     |                |                 |              |

|                | 000x = 31                            | kHz LF               |              |                 |                |                 |              |

|                | 001x = 31                            | .25 kHz              |              |                 |                |                 |              |

|                | 0100 <b>= 62</b>                     | -                    |              |                 |                |                 |              |

|                | 0101 <b>= 12</b>                     | • · · · · =          |              |                 |                |                 |              |

|                | 0110 = 25                            |                      |              |                 |                |                 |              |

|                |                                      | 0 kHz (default upo   | on Reset)    |                 |                |                 |              |

|                | 1000 = 12                            |                      |              |                 |                |                 |              |

|                | 1001 <b>= 25</b><br>1010 <b>= 50</b> |                      |              |                 |                |                 |              |

|                | 1010 <b>= 50</b><br>1011 <b>= 1</b>  |                      |              |                 |                |                 |              |

|                | 1100 <b>= 2</b>                      |                      |              |                 |                |                 |              |

|                | 1101 = 4                             |                      |              |                 |                |                 |              |

|                | 1110 = 8                             |                      |              |                 |                |                 |              |

|                | 1111 = 16                            |                      |              |                 |                |                 |              |

| oit 2          | Unimplem                             | nented: Read as '    | 0'           |                 |                |                 |              |

| oit 1-0        | SCS<1:0>                             | : System Clock S     | elect bits   |                 |                |                 |              |

|                | 1x = Interr                          | nal oscillator block | Ĩ            |                 |                |                 |              |

|                | 01 = Seco                            | ndary oscillator     |              |                 |                |                 |              |

|                | 00 = Clock                           | k determined by F    | OSC<1:0> in  | Configuration W | ord 1.         |                 |              |

| Note 1: D      | unligato fragu                       | ency derived from    |              |                 |                |                 |              |

**FLASH PROGRAM**

**FIGURE 10-7:**

### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

# MEMORY MODIFY FLOWCHART Start Modify Operation Read Operation Figure 10-1 An image of the entire row read must be stored in RAM Modify Image The words to be modified are changed in the RAM image Erase Operation Figure 10-4 Write Operation use RAM image Figure 10-5

End Modify Operation

| R/W-1/1        | R/W-1/1                   | R/W-1/1                             | R/W-1/1         | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|----------------|---------------------------|-------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| WPUEN          | INTEDG                    | TMR0CS                              | TMR0SE          | PSA            |                  | PS<2:0>          |              |

| oit 7          |                           |                                     |                 |                |                  |                  | bit (        |

|                |                           |                                     |                 |                |                  |                  |              |

| Legend:        |                           |                                     |                 |                |                  |                  |              |

| R = Readat     |                           | W = Writable                        |                 |                | mented bit, read |                  |              |

| u = Bit is un  | <b>U</b>                  | x = Bit is unk                      |                 | -n/n = Value a | at POR and BC    | R/Value at all c | other Resets |

| '1' = Bit is s | et                        | '0' = Bit is cle                    | ared            |                |                  |                  |              |

| bit 7          |                           | ok Dull un Eng                      | bla bit         |                |                  |                  |              |

|                |                           | eak Pull-up Ena<br>pull-ups are dis |                 | MCLP if it is  | onablod)         |                  |              |

|                |                           | ll-ups are enab                     | · · ·           |                | ,                |                  |              |

| bit 6          | INTEDG: Inte              | errupt Edge Se                      | lect bit        |                |                  |                  |              |

|                |                           | on rising edge                      |                 |                |                  |                  |              |

|                | 0 = Interrupt             | on falling edge                     | of INT pin      |                |                  |                  |              |

| bit 5          | TMR0CS: Tir               | mer0 Clock So                       | urce Select bit |                |                  |                  |              |

|                |                           | n on T0CKI pin                      |                 |                |                  |                  |              |

| L:1 4          |                           | nstruction cycle                    |                 | 4)             |                  |                  |              |

| bit 4          |                           | mer0 Source E<br>nt on high-to-lov  | •               | TOCKLoin       |                  |                  |              |

|                |                           | nt on low-to-hig                    |                 |                |                  |                  |              |

| bit 3          |                           | ller Assignmen                      |                 | ľ              |                  |                  |              |

|                |                           | r is not assigne                    |                 | 0 module       |                  |                  |              |

|                | 0 = Prescale              | r is assigned to                    | the Timer0 m    | odule          |                  |                  |              |

| bit 2-0        | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate S                      | elect bits      |                |                  |                  |              |

|                | Bit                       | Value Timer0                        | Rate            |                |                  |                  |              |

|                |                           | 000 1:2                             |                 |                |                  |                  |              |

|                |                           | 001 1:4<br>010 1:8                  |                 |                |                  |                  |              |

|                |                           | 010 1.6                             |                 |                |                  |                  |              |

|                | :                         | 100 1:3                             | 32              |                |                  |                  |              |

## REGISTER 16-1: OPTION\_REG: OPTION REGISTER

1:64

1:128

1:256

101

110 111

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|------------------------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 65                  |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> | -      | 130                 |

| TMR0       | Timer0 Module Register |        |        |        | 128*   |        |         |        |                     |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 95                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

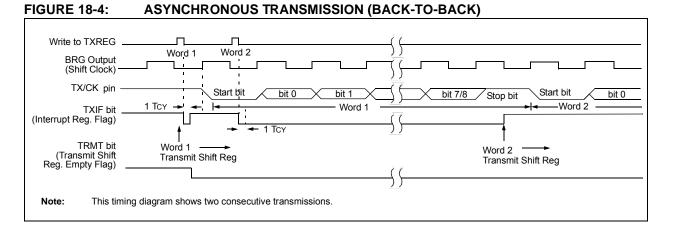

#### TABLE 18-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7                                 | Bit 6 | Bit 5               | Bit 4               | Bit 3        | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|----------|---------------------------------------|-------|---------------------|---------------------|--------------|---------|-------|--------|---------------------|

| BAUD1CON | ABDOVF                                | RCIDL | —                   | SCKP                | BRG16        | —       | WUE   | ABDEN  | 153                 |

| BAUD2CON | ABDOVF                                | RCIDL | —                   | SCKP                | BRG16        | —       | WUE   | ABDEN  | 153                 |

| INTCON   | GIE                                   | PEIE  | TMR0IE              | INTE                | IOCIE        | TMR0IF  | INTF  | IOCIF  | 65                  |

| PIE1     | TMR1GIE                               | ADIE  | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | —            | —       | _     | TMR1IE | 66                  |

| PIR1     | TMR1GIF                               | ADIF  | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —            | —       | _     | TMR1IF | 68                  |

| RCSTA    | SPEN                                  | RX9   | SREN                | CREN                | ADDEN        | FERR    | OERR  | RX9D   | 152                 |

| SPBRGL   |                                       |       | EUSART              | Baud Rate           | Generator, L | ow Byte |       |        | 154*                |

| SPBRGH   | EUSART Baud Rate Generator, High Byte |       |                     |                     |              | 154*    |       |        |                     |

| TXREG    | EUSART Transmit Register              |       |                     |                     |              |         | 144*  |        |                     |

| TXSTA    | CSRC                                  | TX9   | TXEN                | SYNC                | SENDB        | BRGH    | TRMT  | TX9D   | 151                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous transmission.

\* Page provides register information.

Note 1: PIC16LF1904/7 only.

#### 18.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH:SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- 3. Enable the serial port by setting the SPEN bit and the RX/DT pin TRIS bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE interrupt enable bit and set the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

#### 18.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an asynchronous reception with address detect enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE interrupt enable bit and set the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                | Start<br>bit bit 0 / bit 1 / j / bit 7/8 / Stop<br>bit bit / bit 0 / j / bit 7/8 / Stop<br>bit / bit / bit 7/8 / Stop<br>bit / bit / bit 7/8 / Stop |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg►        |                                                                                                                                                     |

| Rcv Buffer Reg           | Word 1 Word 2 A A A A A A A A A A A A A A A A A A                                                                                                   |

| RCIDL                    |                                                                                                                                                     |

| Read Rcv<br>Buffer Reg   |                                                                                                                                                     |

| RCREG                    |                                                                                                                                                     |

| RCIF<br>(Interrupt Flag) | <u></u> <u></u>                                                                                                                                     |

| OERR bit                 |                                                                                                                                                     |

| CREN                     |                                                                                                                                                     |

|                          | timing diagram shows three words appearing on the RX/DT input. The RCREG (receive buffer) is read after the third word,                             |

| caus                     | ing the OERR (overrun) bit to be set.                                                                                                               |

**FIGURE 18-5:**

#### 18.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 18.4.2). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRGL begins counting up using the BRG counter clock as shown in Table 18-6. The fifth rising edge will occur on the RX/ DT pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH:SPBRGL register pair, the ABDEN bit is automatically cleared, and the RCIF interrupt flag is set. A read operation on the RCREG needs to be performed to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 18-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 18.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

#### TABLE 18-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### XXXXh 0000h **BRG** Value 001Ch - Edge #1 - Edge #2 - Edge #3 - Edge #4 Edge #5 RX/DT pin bit 2 bit 3 bit 6 bit 7 Start bit 0 bit 1 bit 4 bit 5 Stop bit Auto Cleared Set by User ABDEN bit RCIDL RCIF bit (Interrupt) Read RCREG XXh SPBRGL 1Ch SPBRGH XXh 00h Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode

#### FIGURE 18-6: AUTOMATIC BAUD RATE CALIBRATION

## 18.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 18.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

The TRIS bits corresponding to the RX/DT and TX/CK pins should be set.

#### 18.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 18.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock and is sampled on the rising edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock and is sampled on the falling edge of each clock.

#### 18.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

# 18.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RX/DT and TX/ CK I/O pins.

- 4. Disable Receive mode by clearing bits SREN and CREN.

- 5. Enable Transmit mode by setting the TXEN bit.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXIE, GIE and PEIE interrupt enable bits.

- 8. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 9. Start transmission by loading data to the TXREG register.

#### 18.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

RX/DT and TX/CK pin output drivers must be disabled by setting the corresponding TRIS bits.

#### 18.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 18.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 18.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- 3. Clear the CREN and SREN bits.

- If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

#### 18.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 18.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 18.5.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the RCIE bit.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name     | Bit 7                                 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on Page |

|----------|---------------------------------------|-------|--------|-------|-------|---------|-------|--------|---------------------|

| BAUD1CON | ABDOVF                                | RCIDL | —      | SCKP  | BRG16 | BRG16 — |       | ABDEN  | 153                 |

| BAUD2CON | ABDOVF                                | RCIDL | —      | SCKP  | BRG16 | _       | WUE   | ABDEN  | 153                 |

| INTCON   | GIE                                   | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF  | INTF  | IOCIF  | 65                  |

| PIE1     | TMR1GIE                               | ADIE  | RCIE   | TXIE  | —     | _       | _     | TMR1IE | 66                  |

| PIR1     | TMR1GIF                               | ADIF  | RCIF   | TXIF  | _     | _       | _     | TMR1IF | 68                  |

| RCREG    | EUSART Receive Register               |       |        |       |       |         |       | 147*   |                     |

| RCSTA    | SPEN                                  | RX9   | SREN   | CREN  | ADDEN | FERR    | OERR  | RX9D   | 152                 |

| SPBRGL   | EUSART Baud Rate Generator, Low Byte  |       |        |       |       |         |       | 154*   |                     |

| SPBRGH   | EUSART Baud Rate Generator, High Byte |       |        |       |       |         |       | 154*   |                     |

| TXSTA    | CSRC                                  | TX9   | TXEN   | SYNC  | SENDB | BRGH    | TRMT  | TX9D   | 151                 |

### TABLE 18-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous slave reception.

\* Page provides register information.

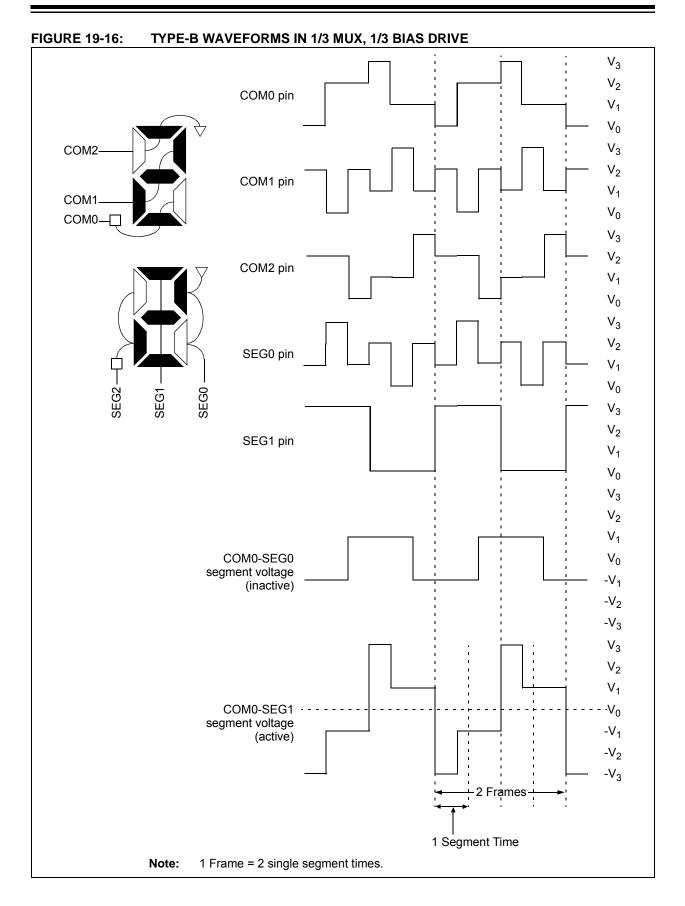

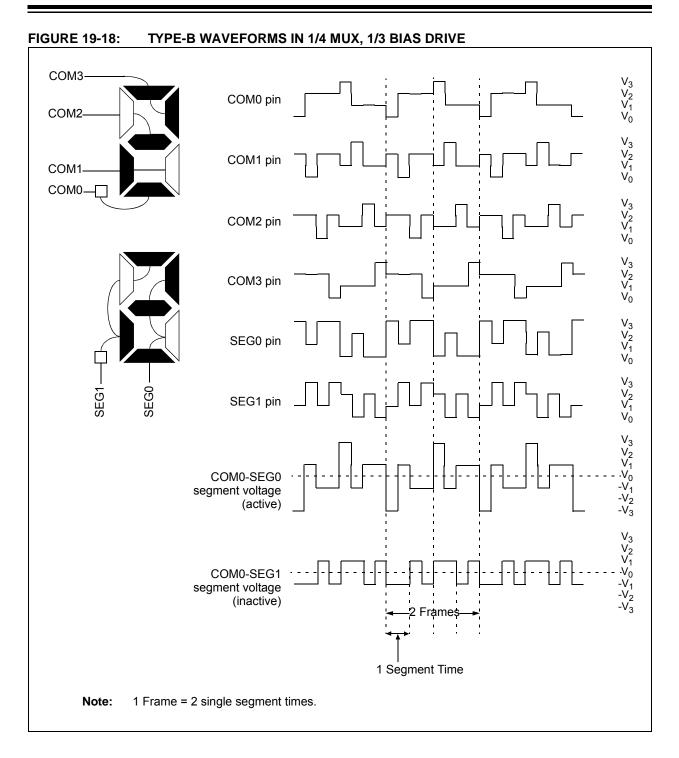

## 19.12 Configuring the LCD Module

The following is the sequence of steps to configure the LCD module.

- 1. Select the frame clock prescale using bits LP<3:0> of the LCDPS register.

- 2. Configure the appropriate pins to function as segment drivers using the LCDSEn registers.

- 3. Configure the LCD module for the following using the LCDCON register:

- Multiplex and Bias mode, bits LMUX<1:0>

- Timing source, bits CS<1:0>

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCD-DATA0 through LCDDATA21.

- 5. Clear LCD Interrupt Flag, LCDIF bit of the PIR2 register and if desired, enable the interrupt by setting bit LCDIE of the PIE2 register.

- Configure bias voltages by setting the LCDRL, LCDREF and the associated ANSELx registers as needed.

- 7. Enable the LCD module by setting bit LCDEN of the LCDCON register.

### 19.13 Disabling the LCD Module

To disable the LCD module, write all '0's to the LCDCON register.

## 19.14 LCD Current Consumption

When using the LCD module the current consumption consists of the following three factors:

- Oscillator Selection

- · LCD Bias Source

- Capacitance of the LCD segments

The current consumption of just the LCD module can be considered negligible compared to these other factors.

#### 19.14.1 OSCILLATOR SELECTION

The current consumed by the clock source selected must be considered when using the LCD module. See **Section 22.0 "Electrical Specifications"** for oscillator current consumption information.

#### 19.14.2 LCD BIAS SOURCE

The LCD bias source, internal or external, can contribute significantly to the current consumption. Use the highest possible resistor values while maintaining contrast to minimize current.

# 19.14.3 CAPACITANCE OF THE LCD SEGMENTS

The LCD segments which can be modeled as capacitors which must be both charged and discharged every frame. The size of the LCD segment and its technology determines the segment's capacitance.

### TABLE 22-6: THERMAL CONSIDERATIONS

| Standard Operating Conditions (unless otherwise | stated) |

|-------------------------------------------------|---------|

|-------------------------------------------------|---------|

| Standard Operating Conditions (unless otherwise stated) |           |                                        |      |       |                                                          |  |  |

|---------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|

| Param<br>No.                                            | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |

| TH01                                                    | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                         |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                         |           |                                        | 27.5 | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                         |           |                                        | 47.2 | °C/W  | 40-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 41.0 | °C/W  | 40-pin UQFN 5x5mm package                                |  |  |

|                                                         |           |                                        | 46.0 | °C/W  | 44-pin TQFP package                                      |  |  |

| TH02 θJC                                                | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                         |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                         |           |                                        | 24   | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                         |           |                                        | 24.7 | °C/W  | 40-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 50.5 | °C/W  | 40-pin UQFN 5x5mm package                                |  |  |

|                                                         |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |  |  |

| TH03                                                    | Тјмах     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |

| TH04                                                    | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                    | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                    | Pı/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                    | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Τj - Τa)/θja <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

# 23.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

Graphs and charts are not available at this time.

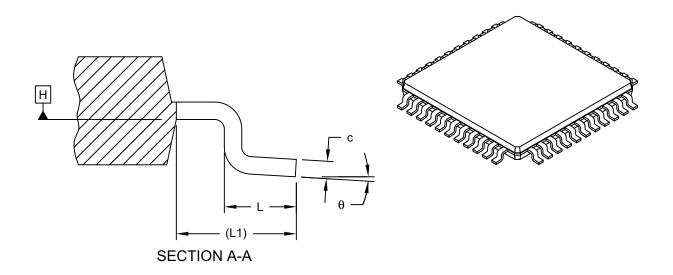

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |  |

|--------------------------|-------------|-----------|------|------|--|--|

| Dimension                | MIN         | NOM       | MAX  |      |  |  |

| Number of Leads          | Ν           | 44        |      |      |  |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |  |

| Overall Height           | A           | -         | -    | 1.20 |  |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |  |

| Lead Length              | L           | 0.45      | 0.60 | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF  |      |      |  |  |

| Foot Angle               | θ           | 0°        | 3.5° | 7°   |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0545-0