Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1907-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Dedicated low-power 32 kHz oscillator driver

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- Auto-wake-up on start

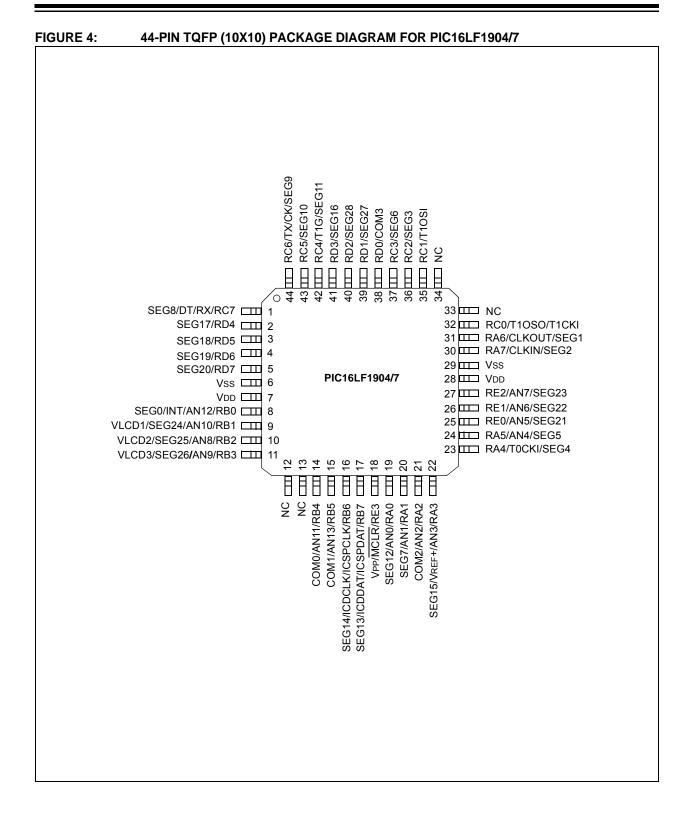

# PIC16LF190X Family Types

|             | ×                | >                               |                      | Flash                        |                      |                 |                      |        |             | LCD          |                   |                      |     |

|-------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|-----------------|----------------------|--------|-------------|--------------|-------------------|----------------------|-----|

| Device      | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Fl<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | Timers<br>(8/16-bit) | EUSART | Common Pins | Segment Pins | Total Segments    | Debug <sup>(1)</sup> | ХГР |

| PIC16LF1902 | (1)              | 2048                            | 128                  | 128                          | 25                   | 11              | 1/1                  |        | 4           | 19           | 72 <sup>(3)</sup> | Н                    | Y   |

| PIC16LF1903 | (1)              | 4096                            | 256                  | 128                          | 25                   | 11              | 1/1                  | _      | 4           | 19           | 72 <sup>(3)</sup> | Н                    | Y   |

| PIC16LF1904 | (2)              | 4096                            | 256                  | 128                          | 36                   | 14              | 1/1                  | 1      | 4           | 29           | 116               | I/H                  | Y   |

| PIC16LF1906 | (2)              | 8192                            | 512                  | 128                          | 25                   | 11              | 1/1                  | 1      | 4           | 19           | 72 <sup>(3)</sup> | I/H                  | Y   |

| PIC16LF1907 | (2)              | 8192                            | 512                  | 128                          | 36                   | 14              | 1/1                  | 1      | 4           | 29           | 116               | I/H                  | Y   |

Note 1: Debugging Methods: (I) – Integrated on Chip; (H) – using Debug Header; (E) – using Emulation Header.

2: One pin is input-only.

3: COM3 and SEG15 share a pin, so the total segments are limited to 72 for 28-pin devices.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS40001455 PIC16LF1902/3 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001569 PIC16LF1904/6/7 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

### **Table of Contents**

| 1.0   | Device Overview                                                           |       |

|-------|---------------------------------------------------------------------------|-------|

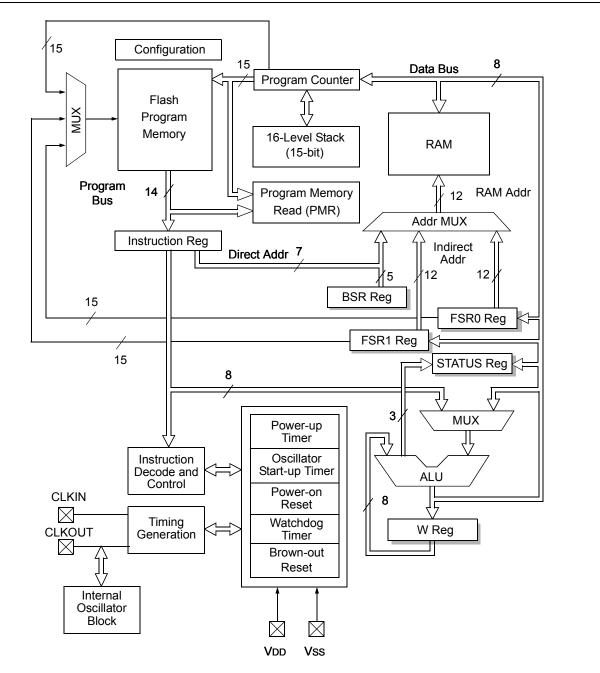

| 2.0   | Enhanced Mid-range CPU                                                    | 15    |

| 3.0   | Memory Organization                                                       | 16    |

| 4.0   | Device Configuration                                                      | 38    |

| 5.0   | Resets                                                                    | 43    |

| 6.0   | Oscillator Module                                                         | 51    |

| 7.0   | Interrupts                                                                | 60    |

| 8.0   | Power-Down Mode (Sleep)                                                   | 71    |

| 9.0   | Watchdog Timer                                                            | 73    |

| 10.0  | Flash Program Memory Control                                              | 77    |

| 11.0  | I/O Ports                                                                 | 93    |

| 12.0  | Interrupt-On-Change                                                       | . 109 |

| 13.0  | Fixed Voltage Reference (FVR)                                             | . 112 |

| 14.0  | Temperature Indicator Module                                              | . 114 |

| 15.0  | Analog-to-Digital Converter (ADC) Module                                  | . 115 |

| 16.0  | Timer0 Module                                                             | . 128 |

| 17.0  | Timer1 Module with Gate Control                                           |       |

| 18.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 142 |

| 19.0  | Liquid Crystal Display (LCD) Driver Module                                | . 171 |

| 20.0  | In-Circuit Serial Programming™ (ICSP™)                                    | . 205 |

| 21.0  | Instruction Set Summary                                                   | . 207 |

| 22.0  | Electrical Specifications                                                 | . 221 |

| 23.0  | DC and AC Characteristics Graphs and Charts                               | . 238 |

| 24.0  | Development Support                                                       | . 239 |

| 25.0  | Packaging Information                                                     | . 243 |

| Appe  | ndix A: Data Sheet Revision History                                       | . 261 |

| The N | /icrochip WebSite                                                         | . 262 |

| Custo | omer Change Notification Service                                          | . 262 |

| Custo | mer Support                                                               | . 262 |

| Produ | uct Identification System                                                 | . 263 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| Name                                | Function  | Input<br>Type | Output<br>Type | Description                                          |  |  |  |

|-------------------------------------|-----------|---------------|----------------|------------------------------------------------------|--|--|--|

| RB3 <sup>(1)</sup> /AN9/SEG26/VLCD3 | RB3       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | AN9       | AN            | —              | A/D Channel 9 input.                                 |  |  |  |

|                                     | • SEG26   |               | AN             | LCD Analog output.                                   |  |  |  |

|                                     | VLCD3     | AN            | —              | LCD analog input.                                    |  |  |  |

| RB4 <sup>(1)</sup> /AN11/COM0       | RB4       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | AN11      | AN            | —              | A/D Channel 11 input.                                |  |  |  |

|                                     | COM0      |               | AN             | LCD Analog output.                                   |  |  |  |

| RB5 <sup>(1)</sup> /AN13/COM1       | RB5       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | AN13      | AN            | —              | A/D Channel 13 input.                                |  |  |  |

|                                     | COM1      | _             | AN             | LCD Analog output.                                   |  |  |  |

| RB6 <sup>(1)</sup> /ICSPCLK/ICDCLK/ | RB6       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

| SEG14                               | ICSPCLK   | ST            | —              | Serial Programming Clock.                            |  |  |  |

|                                     | ICDCLK    | ST            | —              | In-Circuit Debug Clock.                              |  |  |  |

|                                     | SEG14     | _             | AN             | LCD Analog output.                                   |  |  |  |

| RB7 <sup>(1)</sup> /ICSPDAT/ICDDAT/ | RB7       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

| SEG13                               | ICSPDAT   | ST            | _              | Serial Programming Clock.                            |  |  |  |

|                                     | ICDDAT    | ST            | CMOS           | In-Circuit Data I/O.                                 |  |  |  |

|                                     | SEG13     |               | AN             | LCD Analog output.                                   |  |  |  |

| RC0/T1OSO/T1CKI                     | RC0       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | T10S0     | XTAL          | XTAL           | Timer1 oscillator connection.                        |  |  |  |

|                                     | T1CKI     | ST            | —              | Timer1 clock input.                                  |  |  |  |

| RC1/T10SI                           | RC1       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | T10SI     | XTAL          | XTAL           | Timer1 oscillator connection.                        |  |  |  |

| RC2/SEG3                            | RC2       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | SEG3      | _             | AN             | LCD Analog output.                                   |  |  |  |

| RC3/SEG6                            | RC3       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | SEG6      |               | AN             | LCD Analog output.                                   |  |  |  |

| RC4/T1G/SEG11                       | RC4       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | T1G       | XTAL          | XTAL           | Timer1 oscillator connection.                        |  |  |  |

|                                     | SEG11     |               | AN             | LCD Analog output.                                   |  |  |  |

| RC5/SEG10                           | RC5       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | SEG10     |               | AN             | LCD Analog output.                                   |  |  |  |

| RC6/TX/CK/SEG9                      | RC6       | TTL           | CMOS           | General purpose I/O.                                 |  |  |  |

| RC0/17/CR/3EG9                      | TX        | 116           | CMOS           | USART asynchronous transmit.                         |  |  |  |

|                                     | СК        | ST            | CMOS           | USART synchronous clock.                             |  |  |  |

|                                     | SEG9      |               | AN             | LCD Analog output.                                   |  |  |  |

|                                     |           |               |                |                                                      |  |  |  |

| RC7/RX/DT/SEG8                      | RC7<br>RX | TTL<br>ST     | CMOS           | General purpose I/O.                                 |  |  |  |

|                                     | DT        | ST            | - CMOS         | USART asynchronous input.<br>USART synchronous data. |  |  |  |

|                                     | SEG8      | 31            | AN             | LCD Analog output.                                   |  |  |  |

PIC16LF1904/6/7 PINOUT DESCRIPTION (CONTINUED) **TABLE 1-2:**

XTAL = Crystal HV = High Voltage

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ levels

Note 1: These pins have interrupt-on-change functionality.

2: PIC16LF1906/7 only.

#### 5.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00-1 110x        |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu-u Ouuu        |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu-u Ouuu        |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu-0 uuuu        |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu-u uuuu        |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00-1 11u0        |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu-u uuuu        |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu-u u0uu        |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu-u uuuu        |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul-u uuuu        |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

## 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate interrupt enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 8.0** "**Power-Down Mode (Sleep)**" for more details.

## 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

## 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- · BSR register

- · FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

### 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1ms. See **Section 22.0 "Electrical Specifications"** for the LFINTOSC tolerances.

### 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word 1. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word 1 are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word 1 are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word 1 are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |

|-----------|--------|----------------|-------------|--|

| 11        | х      | Х              | Active      |  |

| 10        | 37     | Awake          | Active      |  |

| 10        | х      | Sleep          | Disabled    |  |

| 01        | 1      | х              | Active      |  |

| 01        | 0      | ~              | Disabled    |  |

| 00        | х      | Х              | Disabled    |  |

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT        |

|----------------------------------------------------------|------------|

| WDTE<1:0> = 00                                           |            |

| WDTE<1:0> = 01 and SWDTEN = 0                            |            |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared    |

| CLRWDT Command                                           | Cleared    |

| Oscillator Fail Detected                                 |            |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK | 7          |

| Change INTOSC divider (IRCF bits)                        | Unaffected |

#### 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail event

- WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 9-2 for more information.

#### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the <u>device</u> wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0 "Memory Organization"** and STATUS register (**Register 3-1**) for more information.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | Register<br>on Page |

|--------|-------|-------|-------|-------|--------|-------|----------|-------|---------------------|

| OSCCON | —     |       | IRCF  | <3:0> |        | _     | SCS<1:0> |       | 58                  |

| STATUS | —     | _     | —     | TO    | PD     | Z     | DC       | С     | 21                  |

| WDTCON | —     | _     |       |       | SWDTEN | 75    |          |       |                     |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

## TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       | _       | _        | _         | CLKOUTEN | BORE     | N<1:0>    | _       | 20                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | —        | FOSC<1:0> |         | 39                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash Program Memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash Program Memory can be protected in two ways; by code protection (CP bit in Configuration Word 1) and write protection (WRT<1:0> bits in Configuration Word 2).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash Program Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash Program Memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash Program Memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash Program Memory array is enabled by clearing the CP bit of Configuration Word 1.

# **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash Program Memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash Program Memory.

# 10.2 Flash Program Memory Overview

It is important to understand the Flash Program Memory structure for erase and programming operations. Flash Program Memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

**Note:** If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash Program Memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

## 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2.

When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

| TABLE 10-2: | USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1) |

|-------------|-------------------------------------------------------------|

|-------------|-------------------------------------------------------------|

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

\* PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables;

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | PMADRL       | ; | Select correct Bank        |

|---------|--------------|---|----------------------------|

| MOVLW   | PROG_ADDR_LO | ; |                            |

| MOVWF   | PMADRL       | ; | Store LSB of address       |

| CLRF    | PMADRH       | ; | Clear MSB of address       |

|         |              |   |                            |

| BSF     | PMCON1,CFGS  | ; | Select Configuration Space |

| BCF     | INTCON,GIE   | ; | Disable interrupts         |

| BSF     | PMCON1,RD    | ; | Initiate read              |

| NOP     |              | ; | Executed (See Figure 10-1) |

| NOP     |              | ; | Ignored (See Figure 10-1)  |

| BSF     | INTCON,GIE   | ; | Restore interrupts         |

|         |              |   |                            |

| MOVF    | PMDATL,W     | ; | Get LSB of word            |

| MOVWF   | PROG_DATA_LO | ; | Store in user location     |

| MOVF    | PMDATH,W     | ; | Get MSB of word            |

| MOVWF   | PROG_DATA_HI | ; | Store in user location     |

|         |              |   |                            |

| W-0/0            | W-0/0    | W-0/0             | W-0/0       | W-0/0            | W-0/0            | W-0/0            | W-0/0        |

|------------------|----------|-------------------|-------------|------------------|------------------|------------------|--------------|

|                  |          | Prog              | gram Memory | / Control Regist | ter 2            |                  |              |

| bit 7            |          |                   |             |                  |                  |                  | bit 0        |

|                  |          |                   |             |                  |                  |                  |              |

| Legend:          |          |                   |             |                  |                  |                  |              |

| R = Readable I   | bit      | W = Writable      | bit         | U = Unimpler     | mented bit, read | l as '0'         |              |

| S = Bit can only | y be set | x = Bit is unkn   | iown        | -n/n = Value a   | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared        |                  |                  |                  |              |

## REGISTER 10-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7       | Bit 6 | Bit 5         | Bit 4      | Bit 3         | Bit 2  | Bit 1 | Bit 0 | Register on<br>Page |

|--------|-------------|-------|---------------|------------|---------------|--------|-------|-------|---------------------|

| PMCON1 | (1)         | CFGS  | LWLO          | FREE       | WRERR         | WREN   | WR    | RD    | 91                  |

| PMCON2 |             |       | Prog          | ram Memory | Control Regis | ster 2 |       |       | 92                  |

| PMADRL | PMADRL<7:0> |       |               |            |               |        |       | 90    |                     |

| PMADRH | (1)         |       |               | F          | MADRH<6:0     | >      |       |       | 90                  |

| PMDATL |             |       |               | PMDA       | ۲L<7:0>       |        |       |       | 90                  |

| PMDATH | _           | _     | – PMDATH<5:0> |            |               |        |       | 90    |                     |

| INTCON | GIE         | PEIE  | TMR0IE        | INTE       | IOCIE         | TMR0IF | INTF  | IOCIF | 65                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Flash Program Memory module. Note 1: Unimplemented, read as '1'.

### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         |          | _        | CLKOUTEN | BORE     | N<1:0>  | _       | 20                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   |          | FOSC    | <1:0>   | 39                  |

|         | 13:8 | _       | _       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | —       | 40                  |

| CONFIG2 | 7:0  |         |         |          | 1        | _        |          | WRT     | <1:0>   | 40                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Flash Program Memory.

# REGISTER 11-5: PORTB: PORTB REGISTER

| R/W-x/u          | R/W-x/u                             | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|-------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| RB7              | RB6                                 | RB5               | RB4                                                   | RB3                                | RB2     | RB1     | RB0     |  |

| bit 7            |                                     |                   |                                                       |                                    |         |         | bit 0   |  |

|                  |                                     |                   |                                                       |                                    |         |         |         |  |

| Legend:          |                                     |                   |                                                       |                                    |         |         |         |  |

| R = Readable     | bit                                 | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set |                                     | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to the corresponding LATB register. Reads from the PORTB register is return of actual I/O pin values.

# REGISTER 11-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

# REGISTER 11-7: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

# bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to the corresponding LATB register. Reads from the PORTB register is return of actual I/O pin values.

## 11.4 PORTD Registers (PIC16LF1904/7 only)

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 11-14). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTD register (Register 11-13) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATD).

The TRISD register (Register 11-14) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.4.1 PORTD FUNCTIONS AND OUTPUT PRIORITIES

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-9.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 11-9.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RD0      | RD0                              |

| RD1      | RD1                              |

| RD2      | RD2                              |

| RD3      | RD3                              |

| RD4      | RD4                              |

| RD5      | RD5                              |

| RD6      | RD6                              |

| RD7      | RD7                              |

|          |                                  |

TABLE 11-9: PORTD OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

| Name   | Bit 7                    | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|--------------------------|--------|--------|--------|--------|--------|---------|---------|---------------------|

| ADCON0 | —                        | CHS4   | CHS3   | CHS2   | CHS1   | CHS0   | GO/DONE | ADON    | 121                 |

| ADCON1 | ADFM                     | ADCS2  | ADCS1  | ADCS0  | —      | —      | ADPREF1 | ADPREF0 | 122                 |

| ADRESH | A/D Result Register High |        |        |        |        |        |         |         | 123, 124            |

| ADRESL | A/D Result Register Low  |        |        |        |        |        |         |         | 123, 124            |

| ANSELA | —                        | —      | ANSA5  | —      | ANSA3  | ANSA2  | ANSA1   | ANSA0   | 96                  |

| ANSELB | —                        | _      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1   | ANSB0   | 99                  |

| INTCON | GIE                      | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF   | 65                  |

| PIE1   | TMR1GIE                  | ADIE   | RCIE   | TXIE   | _      | —      | —       | TMR1IE  | 66                  |

| PIR1   | TMR1GIF                  | ADIF   | RCIF   | TXIF   | _      | —      | —       | TMR1IF  | 68                  |

| TRISA  | TRISA7                   | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0  | 95                  |

| TRISB  | TRISB7                   | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1  | TRISB0  | 98                  |

| FVRCON | FVREN                    | FVRRDY | TSEN   | TSRNG  | _      | —      | ADFVR1  | ADFVR0  | 113                 |

TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

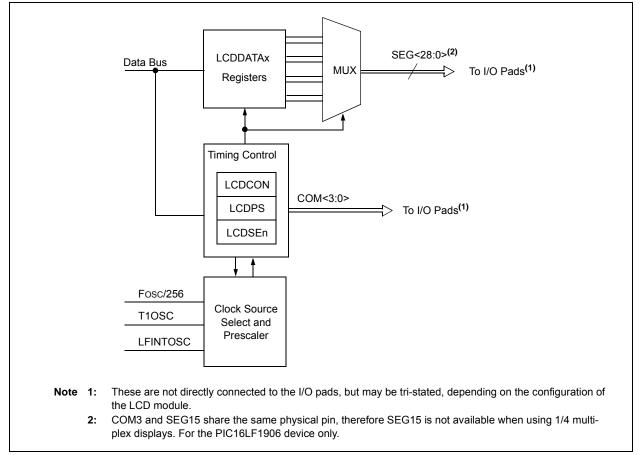

# 19.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16LF1904/6/7 device, the module drives the panels of up to four commons and up to 116 total segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- · Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- 19 Segment pins (PIC16LF1906 only)

- 29 Segment pins (PIC16LF1904/7 only)

• Static, 1/2 or 1/3 LCD Bias

Note: COM3 and SEG15 share the same physical pin on the PIC16LF1906, therefore SEG15 is not available when using 1/4 multiplex displays.

# 19.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 4 LCD Segment Enable registers (LCDSEn)

- Up to 16 LCD data registers (LCDDATAn)

#### FIGURE 19-1: LCD DRIVER MODULE BLOCK DIAGRAM

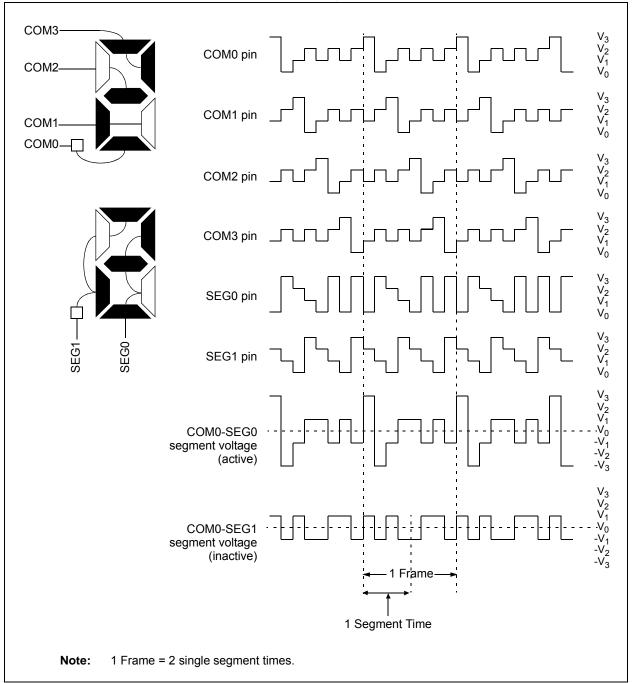

## FIGURE 19-17: TYPE-A WAVEFORMS IN 1/4 MUX, 1/3 BIAS DRIVE

# TABLE 22-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

| PIC16LF1904/6/7 |                                     |      | Standard Operating Conditions (unless otherwise stated) |      |       |            |                                         |  |  |

|-----------------|-------------------------------------|------|---------------------------------------------------------|------|-------|------------|-----------------------------------------|--|--|

| Param           | Device                              | Min. | Тур†                                                    | Max. | Units | Conditions |                                         |  |  |

| No.             | Characteristics                     |      |                                                         |      |       | Vdd        | Note                                    |  |  |

|                 | Supply Current (IDD) <sup>(1,</sup> | 2)   |                                                         |      |       |            |                                         |  |  |

| D010            |                                     | —    | 58                                                      | 75   | μA    | 1.8        | Fosc = 1 MHz                            |  |  |

|                 |                                     | _    | 115                                                     | 140  | μA    | 3.0        | EC Oscillator mode                      |  |  |

|                 |                                     | —    | 133                                                     | 176  | μA    | 3.6        | High Power mode                         |  |  |

| D011            |                                     | —    | 130                                                     | 200  | μA    | 1.8        | Fosc = 4 MHz                            |  |  |

|                 |                                     | —    | 245                                                     | 300  | μA    | 3.0        | EC Oscillator mode<br>High Power mode   |  |  |

|                 |                                     | —    | 290                                                     | 350  | μA    | 3.6        |                                         |  |  |

| D012            |                                     | —    | 218                                                     | 275  | μA    | 1.8        | Fosc = 500 kHz                          |  |  |

|                 |                                     | —    | 283                                                     | 375  | μA    | 3.0        | HFINTOSC mode                           |  |  |

|                 |                                     | —    | 314                                                     | 395  | μA    | 3.6        |                                         |  |  |

| D013            |                                     | —    | 233                                                     | 325  | μA    | 1.8        | Fosc = 1 MHz                            |  |  |

|                 |                                     | _    | 309                                                     | 425  | μA    | 3.0        | HFINTOSC mode                           |  |  |

|                 |                                     | _    | 347                                                     | 475  | μA    | 3.6        |                                         |  |  |

| D014            |                                     | _    | 305                                                     | 360  | μA    | 1.8        | Fosc = 4 MHz                            |  |  |

|                 |                                     | _    | 433                                                     | 520  | μA    | 3.0        | HFINTOSC mode                           |  |  |

|                 |                                     | _    | 500                                                     | 600  | μA    | 3.6        | -                                       |  |  |

| D015            |                                     | _    | 395                                                     | 480  | μA    | 1.8        | Fosc = 8 MHz                            |  |  |

|                 |                                     | _    | 600                                                     | 720  | μA    | 3.0        | HFINTOSC mode                           |  |  |

|                 |                                     |      | 700                                                     | 850  | μA    | 3.6        | -                                       |  |  |

| D016            |                                     | _    | 567                                                     | 670  | μA    | 1.8        | Fosc = 16 MHz                           |  |  |

|                 |                                     |      | 915                                                     | 1100 | μA    | 3.0        | HFINTOSC mode                           |  |  |

|                 |                                     | _    | 1087                                                    | 1300 | μA    | 3.6        | -                                       |  |  |

| D017            |                                     | _    | 2.7                                                     | 7.2  | μA    | 1.8        | Fosc = 31 kHz                           |  |  |

|                 |                                     | _    | 4.5                                                     | 9.7  | μA    | 3.0        | LFINTOSC mode                           |  |  |

|                 |                                     | _    | 5.2                                                     | 12.0 | μA    | 3.6        | $-40^{\circ}C \le TA \le +125^{\circ}C$ |  |  |

| D017A           |                                     | _    | 2.7                                                     | 6.5  | μA    | 1.8        | Fosc = 31 kHz                           |  |  |

|                 |                                     | _    | 4.5                                                     | 9.0  | μA    | 3.0        | LFINTOSC mode                           |  |  |

|                 |                                     | _    | 5.2                                                     | 11.0 | μΑ    | 3.6        | $-40^{\circ}C \le TA \le +85^{\circ}C$  |  |  |

| D018            |                                     | _    | 2.4                                                     | 6.7  | μΑ    | 1.8        | Fosc = 32 kHz                           |  |  |

|                 |                                     | _    | 4.2                                                     | 9.2  | μΑ    | 3.0        | EC Oscillator mode, Low-Power mode      |  |  |

|                 |                                     | _    | 4.8                                                     | 11.5 | μA    | 3.6        | $-$ -40°C $\leq$ TA $\leq$ +125°C       |  |  |

| D018A           |                                     | _    | 2.4                                                     | 6.0  | μA    | 1.8        | Fosc = 32 kHz                           |  |  |

|                 |                                     | _    | 4.2                                                     | 8.5  | μΑ    | 3.0        | EC Oscillator mode, Low-Power mode      |  |  |

|                 |                                     |      | 4.8                                                     | 10.5 | μA    | 3.6        | $-40^{\circ}C \le TA \le +85^{\circ}C$  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: FVR and BOR are disabled.

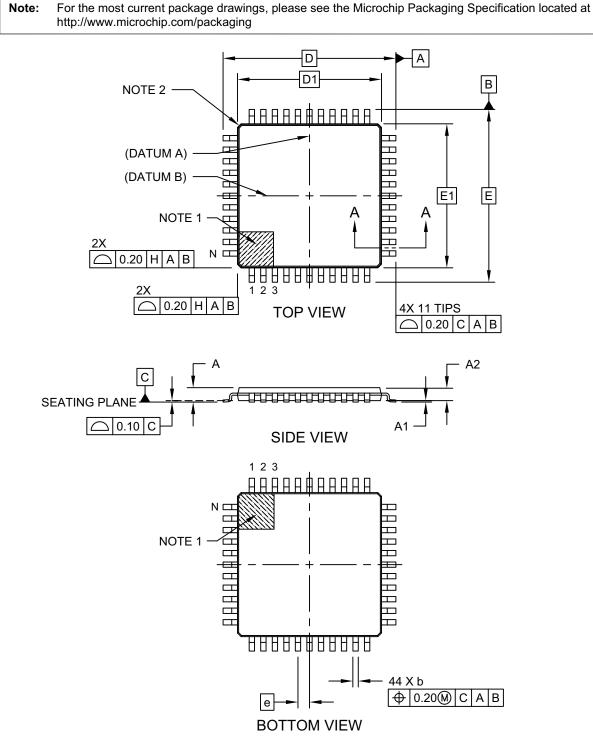

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

Microchip Technology Drawing C04-076C Sheet 1 of 2

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256 ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15