Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1907-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC16LF1904/6/7 are described within this data sheet. They are available in 28, 40 and 44-pin packages. Figure 1-1 shows a block diagram of the PIC16LF1904/6/7 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral              | PIC16LF1906 | PIC16LF1904/7 |   |

|-------------------------|-------------|---------------|---|

| ADC                     | ٠           | •             |   |

| EUSART                  | •           | •             |   |

| Fixed Voltage Reference | e (FVR)     | ٠             | • |

| LCD                     |             | •             | • |

| Temperature Indicator   | •           | •             |   |

| Timers                  |             |               |   |

|                         | Timer0      | ٠             | • |

|                         | Timer1      | •             | • |

### 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "**Indirect Addressing**" for more information.

Data memory uses a 12-bit address. The upper seven bits of the address define the Bank Address and the lower five bits select the registers/RAM in that bank.

### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-4.

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

TABLE 3-2: CORE REGISTERS

# PIC16LF1904/6/7

|            |            | 0x0F                                                                                                 |                                                                                        |                                                                                                                                                                                                                      |

|------------|------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |            | 0x0E                                                                                                 |                                                                                        |                                                                                                                                                                                                                      |

|            |            | 0x0D                                                                                                 |                                                                                        | -                                                                                                                                                                                                                    |

|            |            | 0x0C                                                                                                 |                                                                                        | -                                                                                                                                                                                                                    |

|            |            | 0x0B                                                                                                 |                                                                                        | _                                                                                                                                                                                                                    |

|            |            | 0x0A                                                                                                 |                                                                                        | _                                                                                                                                                                                                                    |

|            |            | 0x09                                                                                                 |                                                                                        | This figure shows the stack configuration                                                                                                                                                                            |

|            |            | 0x08                                                                                                 |                                                                                        | after the first CALL or a single interrupt.<br>If a RETURN instruction is executed, the                                                                                                                              |

|            |            | 0x07                                                                                                 |                                                                                        | return address will be placed in the<br>Program Counter and the Stack Pointer                                                                                                                                        |

|            |            | 0x06                                                                                                 |                                                                                        | decremented to the empty state (0x1F).                                                                                                                                                                               |

|            |            | 0x05                                                                                                 |                                                                                        | _                                                                                                                                                                                                                    |

|            |            | 0x04                                                                                                 |                                                                                        | _                                                                                                                                                                                                                    |

|            |            | 0x03                                                                                                 |                                                                                        | -                                                                                                                                                                                                                    |

|            |            | 0x02                                                                                                 |                                                                                        | -                                                                                                                                                                                                                    |

|            |            | 0x01                                                                                                 |                                                                                        |                                                                                                                                                                                                                      |

| TOSH:TOSL  |            | 0x00                                                                                                 | Return Address                                                                         | STKPTR = 0x00                                                                                                                                                                                                        |

| : 3-7: ACC |            | E STA                                                                                                | CK EXAMPLE                                                                             | 3                                                                                                                                                                                                                    |

| E 3-7: ACC | ESSING THE | <u>=</u> STA                                                                                         | CK EXAMPLE                                                                             | 3                                                                                                                                                                                                                    |

| : 3-7: ACC |            | 0x0F                                                                                                 | CK EXAMPLE                                                                             | <u>3</u>                                                                                                                                                                                                             |

| : 3-7: ACC |            | 0x0F [<br>0x0E [                                                                                     | CK EXAMPLE                                                                             | 3                                                                                                                                                                                                                    |

| : 3-7: ACC |            | 0x0F<br>0x0E<br>0x0D                                                                                 | CK EXAMPLE                                                                             | 3                                                                                                                                                                                                                    |

| 3-7: ACC   |            | 0x0F<br>0x0E<br>0x0D<br>0x0D                                                                         |                                                                                        | After seven CALLS or six CALLS and an                                                                                                                                                                                |

| : 3-7: ACC |            | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0C                                                                 | SCK EXAMPLE                                                                            | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions                                                                                        |

| 3-7: ACC   |            | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A                                                         |                                                                                        | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

| 3-7: ACC   |            | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0B<br>0x0A<br>0x09                                         |                                                                                        | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

| : 3-7: ACC |            | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x0A<br>0x09<br>0x08                                 |                                                                                        | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses                                             |

|            |            | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07                                 |                                                                                        | After seven CALLS or six CALLS and an<br>interrupt, the stack looks like the figure<br>on the left. A series of RETURN instructions<br>will repeatedly place the return addresses                                    |

| 3-7: ACC   |            | 0x0F<br>0x0D<br>0x0D<br>0x0B<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x08                         | Return Address                                                                         | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

|            |            | 0x0F<br>0x0D<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05                 | Return Address<br>Return Address                                                       | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

|            |            | 0x0F<br>0x0D<br>0x0D<br>0x0B<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x08                         | Return Address                                                                         | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

|            |            | 0x0F<br>0x0D<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x04<br>0x07<br>0x06<br>0x05<br>0x04                 | Return Address<br>Return Address<br>Return Address                                     | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

|            |            | 0x0F<br>0x0D<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x03<br>0x07<br>0x06<br>0x05<br>0x04<br>0x04<br>0x03 | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

$\ensuremath{\textcircled{}^{\odot}}$  2011-2016 Microchip Technology Inc.

### 5.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation<br>upon release of POR | Device Operation<br>upon wake- up from<br>Sleep |  |  |

|------------|--------|-------------|----------|-----------------------------------------|-------------------------------------------------|--|--|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |  |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready                     |                                                 |  |  |

| 10         | Х      | Sleep       | Disabled |                                         |                                                 |  |  |

| 0.1        | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |  |

| 01         | 0      | х           | Disabled | Begins immediately                      |                                                 |  |  |

| 00         | х      | х           | Disabled | Begins in                               | nmediately                                      |  |  |

### TABLE 5-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 and PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | e set, |

|---------|-------------|------|-------|-------|------|-------|--------|

|         | regardless  | of   | the   | state | of   | any   | other  |

|         | enable bits | -    |       |       |      |       |        |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7.3 for more details.

## 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash Program Memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash Program Memory can be protected in two ways; by code protection (CP bit in Configuration Word 1) and write protection (WRT<1:0> bits in Configuration Word 2).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash Program Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash Program Memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash Program Memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash Program Memory array is enabled by clearing the CP bit of Configuration Word 1.

## **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash Program Memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash Program Memory.

# 10.2 Flash Program Memory Overview

It is important to understand the Flash Program Memory structure for erase and programming operations. Flash Program Memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

**Note:** If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash Program Memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

## 11.3 PORTC Registers

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 11-6). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-5) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 11-6) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

# 11.3.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 11-7.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RC0      | T10S0                            |

|          | T1CKI<br>RC0                     |

| RC1      | T10SI                            |

|          | RC1                              |

| RC2      | SEG2                             |

|          | RC2                              |

| RC3      | SEG6                             |

|          | RC3                              |

| RC4      | SEG11                            |

|          | T1G                              |

|          | RC4                              |

| RC5      | SEG10                            |

|          | RC5                              |

| RC6      | SEG9                             |

|          | RC6                              |

|          | TX/CK                            |

| RC7      | SEG8                             |

|          | RC7                              |

|          | RX/DT                            |

### TABLE 11-7: PORTC OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

# PIC16LF1904/6/7

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| LATC  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 98                  |

| PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 98                  |

| TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 98                  |

### TABLE 11-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### REGISTER 11-20: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0              | U-0   | U-0               | U-0  | R/W-1/1                                               | U-0 | U-0 | U-0   |  |

|------------------|-------|-------------------|------|-------------------------------------------------------|-----|-----|-------|--|

| _                | —     | —                 | —    | WPUE3                                                 | —   | —   | —     |  |

| bit 7            |       |                   |      |                                                       |     |     | bit 0 |  |

|                  |       |                   |      |                                                       |     |     |       |  |

| Legend:          |       |                   |      |                                                       |     |     |       |  |

| R = Readable b   | bit   | W = Writable I    | bit  | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is uncha | inged | x = Bit is unkn   | own  | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                                                       |     |     |       |  |

|                  |       |                   |      |                                                       |     |     |       |  |

| bit 7-4 | Unimplemented: Read as '0'       |

|---------|----------------------------------|

| bit 3   | WPUE3: Weak Pull-up Register bit |

|         | 1 = Pull-up enabled              |

|         | 0 = Pull-up disabled             |

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| TABLE 11-11: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3 | Bit 2                | Bit 1                 | Bit 0                 | Register<br>on Page |

|--------|-------|-------|-------|----------|-------|----------------------|-----------------------|-----------------------|---------------------|

| ADCON0 | —     |       |       | CHS<4:0> |       |                      | GO/DONE               | ADON                  | 121                 |

| ANSELE | _     |       | _     | _        | _     | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup>  | ANSE0 <sup>(2)</sup>  | 99                  |

| LATE   | _     | _     | _     | —        | —     | LATE2 <sup>(2)</sup> | LATE1 <sup>(2)</sup>  | LATE0 <sup>(2)</sup>  | 106                 |

| PORTE  | _     | _     | _     | —        | RE3   | RE2 <sup>(2)</sup>   | RE1 <sup>(2)</sup>    | RE0 <sup>(2)</sup>    | 106                 |

| TRISE  | _     | _     | _     | _        | _(1)  | TRISE2(2)            | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 106                 |

| WPUE   | _     |       |       | _        | WPUE3 | _                    | _                     | _                     | 108                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

2: PIC16LF1904/7 only.

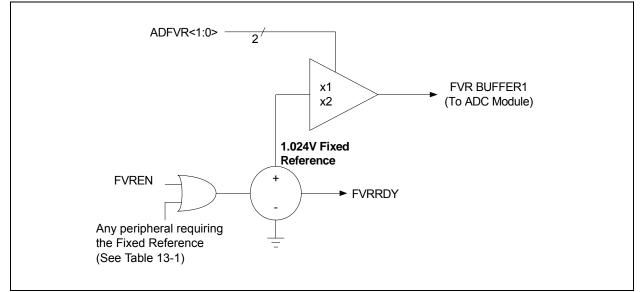

## 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with 1.024V or 2.048V selectable output levels. The output of the FVR can be configured as the FVR input channel on the ADC.

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

### 13.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC is routed through two independent programmable gain amplifiers. Each amplifier can be configured to amplify the reference voltage by 1x or 2x, to produce the two possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

## 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 22.0** "**Electrical Specifications**" for the minimum delay requirement.

### FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

| TABLE 13-1: | PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| Peripheral | Conditions                              | Description                                         |

|------------|-----------------------------------------|-----------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> = 000x | INTOSC is active and device is not in Sleep.        |

|            | BOREN<1:0> = 11                         | BOR always enabled.                                 |

| BOR        | BOREN<1:0> = 10 and BORFS = 1           | BOR disabled in Sleep mode, BOR Fast Start enabled. |

|            | BOREN<1:0> = 01 and BORFS = 1           | BOR under software control, BOR Fast Start enabled. |

| R/W-0/0          | R/W-0/0                                | R/W-0/0                                                        | R/W-0/0        | U-0            | U-0             | R/W-0/0         | R/W-0/0      |

|------------------|----------------------------------------|----------------------------------------------------------------|----------------|----------------|-----------------|-----------------|--------------|

| ADFM             |                                        | ADCS<2:0>                                                      |                |                | —               | ADPRE           | EF<1:0>      |

| bit 7            |                                        |                                                                |                |                | •               |                 | bit (        |

| Legend:          |                                        |                                                                |                |                |                 |                 |              |

| R = Readable     | bit                                    | W = Writable                                                   | bit            | U = Unimpler   | nented bit, rea | ad as '0'       |              |

| u = Bit is unch  | nanged                                 | x = Bit is unkr                                                | nown           | -n/n = Value a | at POR and BO   | OR/Value at all | other Resets |

| '1' = Bit is set |                                        | '0' = Bit is cle                                               | ared           |                |                 |                 |              |

| bit 6-4          | loaded.<br>0 = Left jus<br>loaded.     | tified. Six Least                                              | Significant bi | ts of ADRESL a |                 |                 |              |

|                  | 100 = Fosc<br>101 = Fosc<br>110 = Fosc | :/8<br>:/32<br>(clock supplied fi<br>:/4<br>:/16               |                |                |                 |                 |              |

| bit 3-2          | Unimpleme                              | ented: Read as '                                               | 0'             |                |                 |                 |              |

| bit 1-0          | 00 = VREF+<br>01 = Reser               | :0>: A/D Positive<br>is connected to<br>ved<br>is connected to | VDD            | -              | ation bits      |                 |              |

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 22.0 "Electrical Specifications"** for details.

### 18.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH:SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- 3. Enable the serial port by setting the SPEN bit and the RX/DT pin TRIS bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE interrupt enable bit and set the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

#### 18.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an asynchronous reception with address detect enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 18.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RX/DT and TX/CK TRIS controls to '1'.

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE interrupt enable bit and set the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin<br>Rcv Shift<br>Reg<br>Rcv Buffer Reg | Start       Start       Start       Start       Start       Start       Start       bit       bit |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCIDL                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Read Rcv<br>Buffer Reg<br>RCREG                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RCIF<br>(Interrupt Flag)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OERR bit                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CREN                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                 | timing diagram shows three words appearing on the RX/DT input. The RCREG (receive buffer) is read after the third word,<br>sing the OERR (overrun) bit to be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**FIGURE 18-5:**

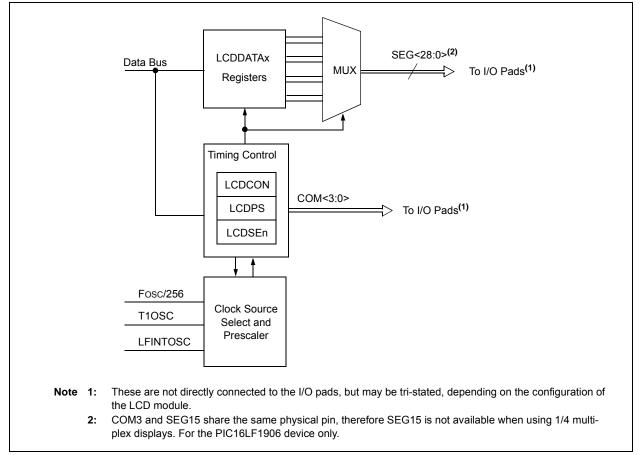

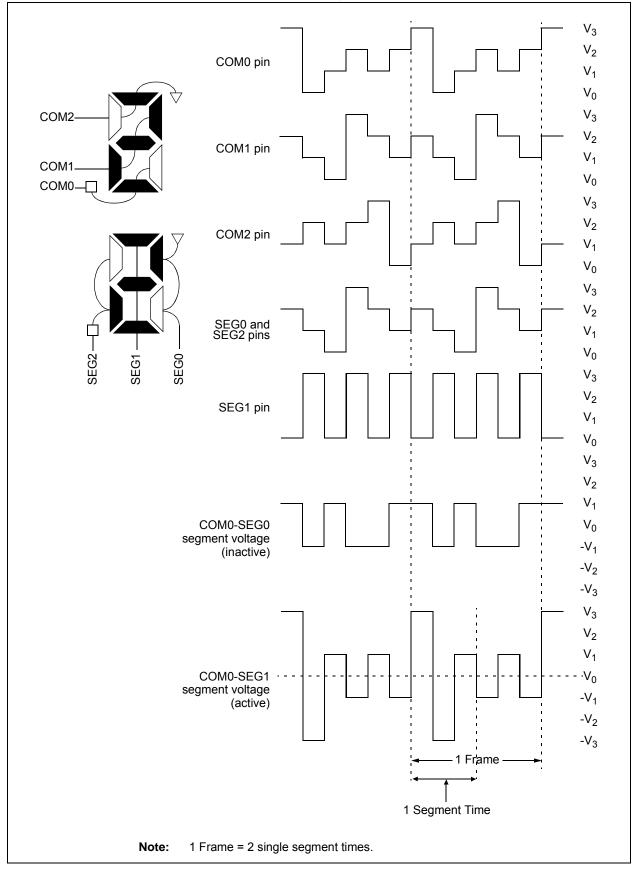

# 19.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16LF1904/6/7 device, the module drives the panels of up to four commons and up to 116 total segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- · Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- 19 Segment pins (PIC16LF1906 only)

- 29 Segment pins (PIC16LF1904/7 only)

• Static, 1/2 or 1/3 LCD Bias

Note: COM3 and SEG15 share the same physical pin on the PIC16LF1906, therefore SEG15 is not available when using 1/4 multiplex displays.

## 19.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to 4 LCD Segment Enable registers (LCDSEn)

- Up to 16 LCD data registers (LCDDATAn)

### FIGURE 19-1: LCD DRIVER MODULE BLOCK DIAGRAM

# 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification" (DS41397).

### 20.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 20.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 5.4 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

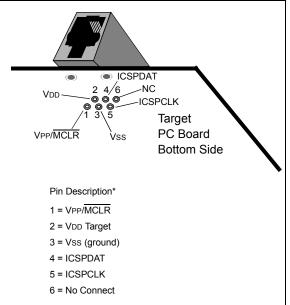

### 20.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 20-1.

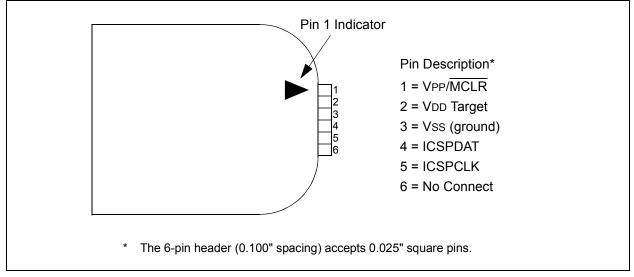

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 20-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

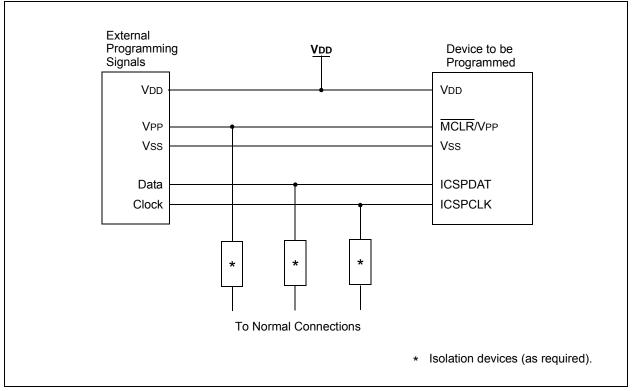

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 20-3 for more information.

| Mnemonic,<br>Operands |      |                                     |              | 14-Bit Opcode |      |      |      | Status   |       |

|-----------------------|------|-------------------------------------|--------------|---------------|------|------|------|----------|-------|

|                       |      | Description                         | Cycles       | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE I                | REGISTER OPE | RATIC         | NS   |      |      |          |       |

| ADDWF                 | f, d | Add W and f                         | 1            | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                | f, d | Add with Carry W and f              | 1            | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                 | f, d | AND W with f                        | 1            | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                  | f, d | Arithmetic Right Shift              | 1            | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                  | f, d | Logical Left Shift                  | 1            | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                  | f, d | Logical Right Shift                 | 1            | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                  | f    | Clear f                             | 1            | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | _    | Clear W                             | 1            | 00            | 0001 | 0000 | 00xx | z        |       |

| COMF                  | f. d | Complement f                        | 1            | 00            | 1001 | dfff | ffff | z        | 2     |

| DECF                  | f. d | Decrement f                         | 1            | 0.0           | 0011 | dfff | ffff | z        | 2     |

| INCF                  | f. d | Increment f                         | 1            | 00            |      | dfff |      | z        | 2     |

| IORWF                 | f, d | Inclusive OR W with f               | 1            | 00            | 0100 |      | ffff | Z        | 2     |

| MOVF                  | f. d | Move f                              | 1            | 00            |      | dfff |      | Z        | 2     |

| MOVWF                 | f, G | Move W to f                         | 1            | 00            | 0000 | 1fff |      | 2        | 2     |

| RLF                   | f. d | Rotate Left f through Carry         | 1            | 00            |      | dfff |      | с        | 2     |

| RRF                   | f, d | Rotate Right f through Carry        | 1            | 00            |      | dfff |      | c        | 2     |

| SUBWF                 | f, d | Subtract W from f                   | 1            |               |      | dfff |      | -        | 2     |

| SUBWFB                | f, d | Subtract with Borrow W from f       | 1            | 00<br>11      |      |      |      |          | 2     |

|                       | ,    |                                     | 1            |               |      | dfff |      | C, DC, Z | 2     |

| SWAPF                 | f, d | Swap nibbles in f                   | 1            | 00            |      | dfff |      | 7        | 2     |

| XORWF                 | f, d | Exclusive OR W with f BYTE ORIENTED |              | 00            | 0110 | aiii | ffff | Z        | 2     |

|                       |      | -                                   |              |               |      |      |      |          | 4.0   |

| DECFSZ                | f, d | Decrement f, Skip if 0              | 1(2)         | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ                | f, d | Increment f, Skip if 0              | 1(2)         | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                       |      | BIT-ORIENTED FILE R                 | EGISTER OPER | ATION         | IS   |      |      |          |       |

| BCF                   | f, b | Bit Clear f                         | 1            | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                   | f, b | Bit Set f                           | 1            | 01            | 01bb | bfff | ffff |          | 2     |

|                       |      | BIT-ORIENTED S                      | KIP OPERATIO | NS            |      |      |      |          |       |

| BTFSC                 | f, b | Bit Test f, Skip if Clear           | 1 (2)        | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                 | f, b | Bit Test f, Skip if Set             | 1 (2)        | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL               |      |                                     |              |               |      |      |      |          |       |

| ADDLW                 | k    | Add literal and W                   | 1            | 11            | 1110 | kkkk | kkkk | C, DC, Z |       |

| ANDLW                 | k    | AND literal with W                  | 1            | 11            | 1001 | kkkk | kkkk | Z        |       |

| IORLW                 | k    | Inclusive OR literal with W         | 1            | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLB                 | k    | Move literal to BSR                 | 1            | 00            | 0000 | 001k | kkkk |          |       |

| MOVLP                 | k    | Move literal to PCLATH              | 1            | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW                 | k    | Move literal to W                   | 1            | 11            | 0000 | kkkk | kkkk |          |       |

| SUBLW                 | k    | Subtract W from literal             | 1            | 11            | 1100 | kkkk | kkkk | C, DC, Z |       |

| CODL                  |      |                                     |              |               |      |      |      |          |       |

## TABLE 21-3: PIC16LF1904/6/7 ENHANCED INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                         |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                            |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                   |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                              |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

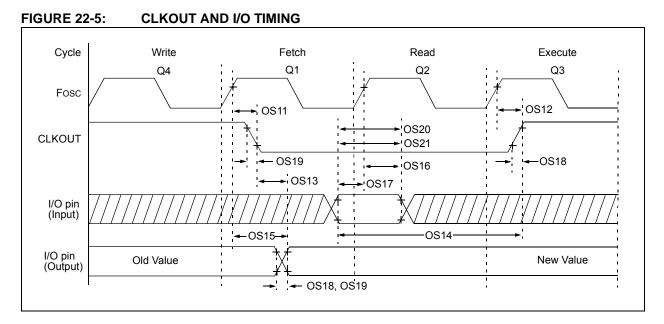

| TABLE 22-9: CLKOUT AND I/O TIMING PARAMETERS | TABLE 22-9: | CLKOUT AND I/O TIMING PARAMETERS |

|----------------------------------------------|-------------|----------------------------------|

|----------------------------------------------|-------------|----------------------------------|

| Standa       | rd Operating | g Conditions (unless otherwise stated)                       |               |          |          |       |                              |

|--------------|--------------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|

| Param<br>No. | Sym.         | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |

| OS11         | TosH2ckL     | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | _             | _        | 70       | ns    | VDD = 3.3-5.0V               |

| OS12         | TosH2ckH     | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             | _        | 72       | ns    | VDD = 3.3-5.0V               |

| OS13         | TckL2ioV     | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _        | 20       | ns    |                              |

| OS14         | TioV2ckH     | Port input valid before CLKOUT↑ <sup>(1)</sup>               | Tosc + 200 ns | _        | —        | ns    |                              |

| OS15         | TosH2ioV     | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |

| OS16         | TosH2iol     | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            |          | —        | ns    | VDD = 3.3-5.0V               |

| OS17         | TioV2osH     | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | _        | —        | ns    |                              |

| OS18         | TioR         | Port output rise time                                        | _             | 40<br>15 | 72<br>32 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS19         | TioF         | Port output fall time                                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS20*        | Tinp         | INT pin input high or low time                               | 25            | _        | —        | ns    |                              |

| OS21*        | Tioc         | Interrupt-on-change new input level time                     | 25            | _        | _        | ns    |                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EC mode where CLKOUT output is 4 x Tosc.

# 24.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 24.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker