Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1907t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FIGURE 5: | 40-PIN UQFN (5X5) PACKAGE DIAGRAM FOR PIC16LF1904/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | RC6/TX/CK/SEG9<br>RC6/TX/CK/SEG9<br>RC4/T1G/SEG11<br>RD3/SEG16<br>RD2/SEG28<br>RD1/SEG27<br>RD0/COM3<br>RC1/T10S1<br>RC2/SEG3<br>RC1/T10S1                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|           | SEG8/DT/RX/RC7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|           | SEG17/RD42301RC0/T1OSO/T1CKISEG18/RD53291RA6/CLKOUT/SEG1SEG19/RD64281RA7/CLKIN/SEG2SEG20/RD75271VssVss6PIC16LF1904/7261VDD7251RE2/AN7/SEG23SEG0/INT/AN12/RB08241RE1/AN6/SEG22VLCD1/SEG24/AN10/RB19231RE0/AN5/SEG21DA5/AN4/SEC5231RA5/SEC5                                                                                                                                                                                                                                                                                                                                                                 |  |

|           | VLCD2/SEG25/AN8/RB2 10 221 RA4/T0CKI/SEG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|           | VLCD3/SEG26/AN9/RB3<br>COM0/AN11/RB4<br>COM1/AN13/RB5<br>SEG14/ICDCLK/ICSPCLK/RB6<br>SEG13/ICDDAT/ICSPCLK/RB6<br>SEG13/ICDDAT/ICSPCLK/RB6<br>SEG13/ICDDAT/ICSPCLK/RB6<br>SEG13/ICDDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6<br>SEG13/ICCDAT/ICSPCLK/RB6 |  |

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 21.0 "Instruction Set Summary").

| Note: | The C  | and DC  | bits | opera | te as Borrow a | nd |

|-------|--------|---------|------|-------|----------------|----|

|       | Digit  | Borrow  | out  | bits, | respectively,  | in |

|       | subtra | action. |      |       |                |    |

#### REGISTER 3-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                                                                     |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                           |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

| TABI               | LE 3-5:               | SPECIAL   | FUNCTI       | ON REG         | SISTER S       | UMMAR        | Y (CON1     | INUED) |        |                      |                                 |

|--------------------|-----------------------|-----------|--------------|----------------|----------------|--------------|-------------|--------|--------|----------------------|---------------------------------|

| Addr               | Name                  | Bit 7     | Bit 6        | Bit 5          | Bit 4          | Bit 3        | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Ban                | k 2                   |           |              |                |                |              |             |        |        |                      |                                 |

| 10Ch               | LATA                  | PORTA Dat | ta Latch     |                |                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 10Dh               | LATB                  | PORTB Da  | ta Latch     |                |                |              |             |        |        | XXXX XXXX            | uuuu uuuu                       |

| 10Eh               | LATC                  | PORTC Da  | ta Latch     |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATD <sup>(3)</sup>   | PORTD Da  | ta Latch     |                |                |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATE <sup>(3)</sup>   | -         | _            | _              | _              | _            | LATE2       | LATE1  | LATE0  | xxx                  | uuu                             |

| 111h<br>to<br>115h | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 116h               | BORCON                | SBOREN    | BORFS        | _              | _              | _            |             | _      | BORRDY | 10q                  | uuu                             |

| 117h               | FVRCON                | FVREN     | FVRRDY       | TSEN           | TSRNG          | _            | _           | ADFVR1 | ADFVR0 | 0q0000               | 0q0000                          |

| 118h<br>to<br>11Fh | _                     | Unimpleme | nted         |                |                |              | •           | •      |        | _                    | _                               |

| Ban                | k 3                   |           |              |                |                |              |             |        |        |                      |                                 |

| 18Ch               | ANSELA                | _         | —            | ANSA5          | —              | ANSA3        | ANSA2       | ANSA1  | ANSA0  | 1- 1111              | 11 1111                         |

| 18Dh               | ANSELB                | _         | —            | ANSB5          | ANSB4          | ANSB3        | ANSB2       | ANSB1  | ANSB0  | 11 1111              | 11 1111                         |

| 18Eh               | —                     | Unimpleme | nted         |                | •              |              |             | •      |        | _                    | _                               |

| 18Fh               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 190h               | ANSELE <sup>(3)</sup> | _         | _            | _              | _              | _            | ANSE2       | ANSE1  | ANSE0  | 111                  | 111                             |

| 191h               | PMADRL                | Program M | emory Addre  | ess Register   | Low Byte       |              |             |        |        | 0000 0000            | 0000 0000                       |

| 192h               | PMADRH                | (2)       |              |                | ess Register I | High Byte    |             |        |        | 1000 0000            | 1000 0000                       |

| 193h               | PMDATL                | Program M | emory Read   | I Data Regist  | ter Low Byte   |              |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| 194h               | PMDATH                | _         | _            | Program M      | emory Read     | Data Registe | r High Byte |        |        | xx xxxx              | uu uuuu                         |

| 195h               | PMCON1                | (2)       | CFGS         | LWLO           | FREE           | WRERR        | WREN        | WR     | RD     | 1000 x000            | 1000 q000                       |

| 196h               | PMCON2                | Program M | emory Conti  | rol Register 2 | 2              |              |             |        |        | 0000 0000            | 0000 0000                       |

| 197h               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    |                                 |

| 198h               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

| 199h               | RCREG                 | USART Re  | ceive Data F | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |

| 19Ah               | TXREG                 | USART Tra | Insmit Data  | Register       |                |              |             |        |        | 0000 0000            | 0000 0000                       |

| 19Bh               | SPBRG                 |           |              |                | BRG            | <7:0>        |             |        |        | 0000 0000            | 0000 0000                       |

| 19Ch               | SPBRGH                |           |              |                | BRG<           | <15:8>       |             |        |        | 0000 0000            | 0000 0000                       |

| 19Dh               | RCSTA                 | SPEN      | RX9          | SREN           | CREN           | ADDEN        | FERR        | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| 19Eh               | TXSTA                 | CSRC      | TX9          | TXEN           | SYNC           | SENDB        | BRGH        | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| 19Fh               | BAUD1CON              | ABDOVF    | RCIDL        | _              | SCKP           | BRG16        | _           | WUE    | ABDEN  | 01-0 0-00            |                                 |

| Ban                |                       | 1         | 1            |                |                | 1            | 1           |        | L      |                      | 1                               |

| 20Ch               | _                     | Unimpleme | nted         |                |                |              |             |        |        | _                    | _                               |

|                    | WPUB                  | WPUB7     | WPUB6        | WPUB5          | WPUB4          | WPUB3        | WPUB2       | WPUB1  | WPUB0  | 1111 1111            | 1111 1111                       |

| 20Eh               | _                     | Unimpleme |              |                |                |              |             |        |        | _                    | _                               |

| 20Fh               | _                     | Unimpleme |              |                |                |              |             |        |        | _                    | _                               |

| 210h               | WPUE                  |           | _            | _              | _              | WPUE3        |             | _      | _      | 1                    | 1                               |

|                    |                       |           |              |                |                |              |             |        |        | ±                    | 1                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-5

Bank 5

211h to 21Fh

29Fh

28Ch

\_ \_

Bank 6

| Бап      | ĸo |                                                                                                                                            |   |   |

|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------|---|---|

| 30Ch     | _  | Unimplemented                                                                                                                              | - | _ |

| <br>31Fh |    |                                                                                                                                            |   |   |

| Legen    |    | vn, u = unchanged, $q$ = value depends on condition, - = unimplemented, read as '0', r = reserved. cations are unimplemented, read as '0'. |   |   |

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16LF1904/7 only. Note 1:

Unimplemented

Unimplemented

2:

3:

#### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 and PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | e set, |

|---------|-------------|------|-------|-------|------|-------|--------|

|         | regardless  | of   | the   | state | of   | any   | other  |

|         | enable bits | -    |       |       |      |       |        |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

#### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7.3 for more details.

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| CLKIN <sup>(1)</sup>        |                  | Q1 Q2 Q3  Q4       | Q1             |          | Q1 Q2 Q3 Q4          | Q1 Q2 Q3 Q4        | Q1 Q2 Q3 Q4         | Q1 Q2 Q3 Q4   |

|-----------------------------|------------------|--------------------|----------------|----------|----------------------|--------------------|---------------------|---------------|

| CLKOUT <sup>(2)</sup>       | \/<br> <br>      | /                  | \              |          | ·/                   | \/<br>!            |                     |               |

| Interrupt flag              | l                |                    | /              | _        | Interrupt Laten      | cy <sup>(1)</sup>  | 1                   | i             |

|                             | 1                |                    |                |          | 1                    | 1                  | ·P,                 | ļ             |

| GIE bit                     | I                |                    | Processor in   |          | 1                    | <u> </u>           |                     | 1             |

| (INTCON reg.)               | !— — — — !       |                    | Sleep          |          | ;<br>!               | ;;<br>;            | '                   |               |

| Instruction Flow            | i i              |                    | ;              |          | I                    |                    | i i                 | i             |

| PC                          | X PC             | PC + 1             | X PC           | + 2      | χ <u>PC + 2</u>      | X PC + 2           | X 0004h             | ( 0005h       |

| Instruction {<br>Fetched    | Inst(PC) = Sleep | Inst(PC + 1)       | 1<br>1<br>1    |          | Inst(PC + 2)         | I I I              | Inst(0004h)         | Inst(0005h)   |

| Instruction {<br>Executed { | Inst(PC - 1)     | Sleep              | 1<br>1<br>1    |          | Inst(PC + 1)         | Dummy Cycle        | Dummy Cycle         | Inst(0004h)   |

| Note 1: 0                   | GIE = 1 assumed. | In this case after | wake-up, the p | orocesso | r calls the ISR at ( | 0004h. If GIE = 0, | execution will cont | inue in-line. |

### FIGURE 8-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 65                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 110                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 110                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 110                 |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE   | —          | _      | _      | TMR1IE | 66                  |

| PIE2   | —       | _      | _      | _      | —          | LCDIE  | _      | —      | 67                  |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF   | —          | _      | _      | TMR1IF | 68                  |

| PIR2   | _       | _      | _      | _      | —          | LCDIF  | _      | —      | 69                  |

| STATUS | —       |        |        | TO     | PD         | Z      | DC     | С      | 21                  |

| WDTCON | _       |        |        | ١      | NDTPS<4:0> | >      |        | SWDTEN | 75                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-down mode.

#### EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, stored in little endian format ; ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) INTCON,GIE BCF ; Disable ints so required sequences will execute properly PMADRH ; Bank 3 BANKSEL MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWE PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSROH ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1.WREN ; Enable writes BSF PMCON1,LWLO ; Only Load Write Latches LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWE PMDATT. ; MOVIW FSR0++ ; Load second data byte into upper MOVWF PMDATH ; Check if lower bits of address are '00000' MOVF PMADRL,W 0x1F ; Check if we're on the last of 32 addresses XORLW ANDLW 0x1F STATUS, Z ; Exit if last of 32 words, BTFSC GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh ; Set WR bit to begin write BSF PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction BCF PMCON1,WREN ; Disable writes BSF INTCON, GIE ; Enable interrupts

#### REGISTER 11-5: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u          | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|---------|---------|--|

| RB7                                     | RB6     | RB5               | RB4     | RB3                                                   | RB2              | RB1     | RB0     |  |

| bit 7                                   |         |                   |         |                                                       |                  |         | bit 0   |  |

|                                         |         |                   |         |                                                       |                  |         |         |  |

| Legend:                                 |         |                   |         |                                                       |                  |         |         |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimpler                                          | mented bit, read | as '0'  |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |                  |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to the corresponding LATB register. Reads from the PORTB register is return of actual I/O pin values.

#### REGISTER 11-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 11-7: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to the corresponding LATB register. Reads from the PORTB register is return of actual I/O pin values.

#### **REGISTER 11-18: LATE: PORTE DATA LATCH REGISTER**

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-x/u              | R/W-x/u              | R/W-x/u              |

|---------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

|         | —   |     | —   | —   | LATE2 <sup>(2)</sup> | LATE1 <sup>(2)</sup> | LATE0 <sup>(2)</sup> |

| bit 7   |     |     |     |     |                      |                      | bit 0                |

|         |     |     |     |     |                      |                      |                      |

| Logond: |     |     |     |     |                      |                      |                      |

| Le | g | e | r | 1 | d | - |

|----|---|---|---|---|---|---|

|    |   |   |   |   |   |   |

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(1)</sup>

- Note 1: Writes to PORTE are actually written to the corresponding LATE register. Reads from the PORTE register is return of actual I/O pin values.

- 2: LATE<2:0> are not implemented on the PIC16LF1906. Read as '0'.

#### **REGISTER 11-19: ANSELE: PORTE ANALOG SELECT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1              | R/W-1/1              | R/W-1/1              |

|-------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

| —     | —   | —   | —   | —   | ANSE2 <sup>(2)</sup> | ANSE1 <sup>(2)</sup> | ANSE0 <sup>(2)</sup> |

| bit 7 |     |     |     |     |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on pins RE<2:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSE<2:0> are not implemented on the PIC16LF1906. Read as '0'.

#### 15.2.5 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 15.3 "A/D Acquisition Requirements".

#### EXAMPLE 15-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, Frc ;clock and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, Frc MOVLW ;clock MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL ADCON0 B'00000001' ;Select channel ANO MOVLW ;Turn ADC On MOVWE ADCON0 SampleTime ; Acquisiton delay CALL ADCON0, ADGO ; Start conversion BSF BTFSC ADCON0, ADGO ; Is conversion done? GOTO \$-1 ;No, test again ADRESH ; BANKSEL ADRESH,W ;Read upper 2 bits MOVF MOVWF RESULTHI ;store in GPR space BANKSEL ADRESL ; ADRESL,W MOVF ;Read lower 8 bits MOVWE RESULTLO ;Store in GPR space

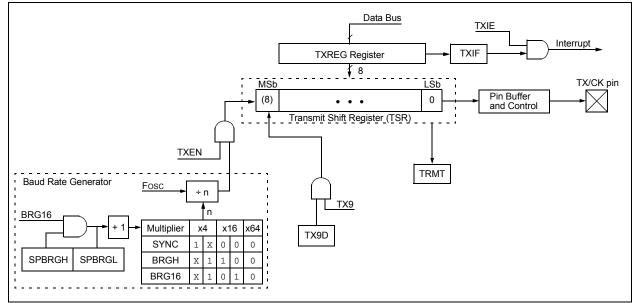

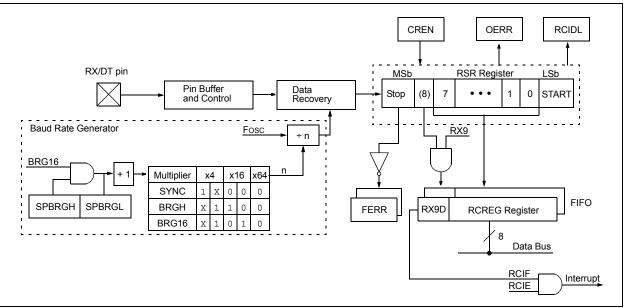

#### 18.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- · Programmable clock and data polarity

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 18-1 and Figure 18-2.

#### FIGURE 18-1: EUSART TRANSMIT BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 18-1, Register 18-2 and Register 18-3, respectively.

For all modes of EUSART operation, the TRIS control bits corresponding to the RX/DT and TX/CK pins should be set to '1'. The EUSART control will automatically reconfigure the pin from input to output, as needed.

When the receiver or transmitter section is not enabled then the corresponding RX/DT or TX/CK pin may be used for general purpose input and output.

| Name     | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3       | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------|--------|---------------------|---------------------|-------------|-----------|--------|--------|---------------------|

| BAUD1CON | ABDOVF  | RCIDL  | —                   | SCKP                | BRG16       | _         | WUE    | ABDEN  | 153                 |

| BAUD2CON | ABDOVF  | RCIDL  | —                   | SCKP                | BRG16       | _         | WUE    | ABDEN  | 153                 |

| INTCON   | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE       | TMR0IF    | INTF   | IOCIF  | 65                  |

| PIE1     | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | —           | _         |        | TMR1IE | 66                  |

| PIR1     | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —           | _         | _      | TMR1IF | 68                  |

| RCREG    |         |        | El                  | JSART Rec           | eive Regist | er        |        |        | 147*                |

| RCSTA    | SPEN    | RX9    | SREN                | CREN                | ADDEN       | FERR      | OERR   | RX9D   | 152                 |

| SPBRGL   |         |        | EUSART              | Baud Rate           | Generator,  | Low Byte  |        |        | 154*                |

| SPBRGH   |         |        | EUSART              | Baud Rate           | Generator,  | High Byte |        |        | 154*                |

| TRISC    | TRISC7  | TRISC6 | TRISC5              | TRISC4              | TRISC3      | TRISC2    | TRISC1 | TRISC0 | 101                 |

| TXSTA    | CSRC    | TX9    | TXEN                | SYNC                | SENDB       | BRGH      | TRMT   | TX9D   | 151                 |

#### TABLE 18-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous reception.

\* Page provides register information.

Note 1: PIC16LF1904/7 only.

| R/W-0/0                   | R/W-0/0                                                                                                                                             | R/C-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                        | R/W-0/0                                | R/W-0/0                                        | R/W-1/1          | R/W-1/1      |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|------------------------------------------------|------------------|--------------|--|--|--|--|

| LCDEN                     | SLPEN                                                                                                                                               | WERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                          | (                                      | CS<1:0>                                        | LMU>             | <1:0>        |  |  |  |  |

| bit 7                     | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                                |                  | bit          |  |  |  |  |

|                           |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                                        |                                                |                  |              |  |  |  |  |

| Legend:                   | . <b>L</b> :4                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            | II — I heirer                          | lowented bit read                              | aa (0)           |              |  |  |  |  |

| R = Readable              |                                                                                                                                                     | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | •                                      | lemented bit, read                             |                  |              |  |  |  |  |

| u = Bit is unch           | •                                                                                                                                                   | x = Bit is unknow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |                                        | e at POR and BOF                               | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is set          |                                                                                                                                                     | '0' = Bit is cleare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ed                                                                         | C = Only c                             | learable bit                                   |                  |              |  |  |  |  |

| bit 7                     | LCDEN: LCD                                                                                                                                          | Driver Enable bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t                                                                          |                                        |                                                |                  |              |  |  |  |  |

|                           |                                                                                                                                                     | er module is enab<br>er module is disat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                        |                                                |                  |              |  |  |  |  |