# E·XFL

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are applicated to

#### Details

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                    |

| Applications            | HB LED Controller                                                           |

| Core Processor          | M8C                                                                         |

| Program Memory Type     | FLASH (16KB)                                                                |

| Controller Series       | CY8CLED                                                                     |

| RAM Size                | 1K x 8                                                                      |

| Interface               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Number of I/O           | 56                                                                          |

| Voltage - Supply        | 3V ~ 5.25V                                                                  |

| Operating Temperature   | -40°C ~ 85°C                                                                |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 68-VFQFN Exposed Pad                                                        |

| Supplier Device Package | 68-QFN (8x8)                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8cled04-68lfxi |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CY8CLED04

# Contents

| EZ-Color™ Functional Overview     | . 4 |

|-----------------------------------|-----|

| Target Applications               | 4   |

| The PSoC Core                     | . 4 |

| The Digital System                | 4   |

| The Analog System                 |     |

| The Analog Multiplexer System     | . 6 |

| Additional System Resources       |     |

| EZ-Color Device Characteristics   | . 6 |

| Getting Started                   | 7   |

| Application Notes                 | 7   |

| Development Kits                  | 7   |

| Training                          |     |

| CYPros Consultants                | 7   |

| Solutions Library                 | 7   |

| Technical Support                 | 7   |

| Development Tools                 |     |

| PSoC Designer Software Subsystems |     |

| Designing with PSoC Designer      |     |

| Select User Modules               |     |

| Configure User Modules            |     |

| Organize and Connect              |     |

| Generate, Verify, and Debug       | .9  |

| Pin Information                   |     |

| 68-Pin Part Pinout                |     |

| Register Conventions              |     |

| Abbreviations Used                |     |

| Register Mapping Tables           |     |

| Electrical Specifications         |     |

| Absolute Maximum Ratings          |     |

| Operating Temperature             |     |

| DC Electrical Characteristics     |     |

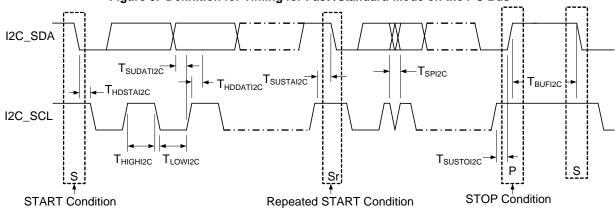

| AC Electrical Characteristics     | 29  |

|                                   |     |

| 37 |

|----|

| 38 |

| 38 |

| 39 |

| 39 |

| 39 |

| 40 |

| 40 |

| 40 |

| 40 |

| 41 |

| 41 |

| 41 |

| 42 |

| 42 |

| 42 |

| 43 |

| 43 |

| 43 |

| 43 |

| 48 |

| 49 |

| 49 |

| 49 |

| 49 |

|    |

# **Getting Started**

The quickest way to understand PSoC silicon is to read this data sheet and then use the PSoC Designer integrated development environment (IDE). This data sheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications.

For in depth information, along with detailed programming details, see the *PSoC® Programmable System-on-Chip Technical Reference Manual*.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device data sheets on the web at http://www.cypress.com/ez-color.

#### **Application Notes**

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

#### **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

## Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

## **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

## **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

## **Technical Support**

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

# **Development Tools**

PSoC Designer<sup>™</sup> is the revolutionary integrated design environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- □ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

## **PSoC Designer Software Subsystems**

#### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this lets you to use more than 100 percent of PSoC's resources for an application.

#### Table 3. Register Map Bank 0 Table: User Space (continued)

| Name     | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access | Name           | Addr (0,Hex) | Access | Name         | Addr (0,Hex) | Access |

|----------|--------------|--------|----------|--------------|--------|----------------|--------------|--------|--------------|--------------|--------|

| DBB00DR2 | 22           | RW     |          | 62           |        |                | A2           |        | INT_VC       | E2           | RC     |

| DBB00CR0 | 23           | #      | ARF_CR   | 63           | RW     |                | A3           |        | RES_WDT      | E3           | W      |

| DBB01DR0 | 24           | #      | CMP_CR0  | 64           | #      |                | A4           |        | DEC_DH       | E4           | RC     |

| DBB01DR1 | 25           | W      | ASY_CR   | 65           | #      |                | A5           |        | DEC_DL       | E5           | RC     |

| DBB01DR2 | 26           | RW     | CMP_CR1  | 66           | RW     |                | A6           |        | DEC_CR0      | E6           | RW     |

| DBB01CR0 | 27           | #      |          | 67           |        |                | A7           |        | DEC_CR1      | E7           | RW     |

| DCB02DR0 | 28           | #      |          | 68           |        | MUL1_X         | A8           | W      | MUL0_X       | E8           | W      |

| DCB02DR1 | 29           | W      |          | 69           |        | MUL1_Y         | A9           | W      | MUL0_Y       | E9           | W      |

| DCB02DR2 | 2A           | RW     |          | 6A           |        | MUL1_DH        | AA           | R      | MUL0_DH      | EA           | R      |

| DCB02CR0 | 2B           | #      |          | 6B           |        | MUL1_DL        | AB           | R      | MUL0_DL      | EB           | R      |

| DCB03DR0 | 2C           | #      | TMP_DR0  | 6C           | RW     | ACC1_DR1       | AC           | RW     | ACC0_DR<br>1 | EC           | RW     |

| DCB03DR1 | 2D           | W      | TMP_DR1  | 6D           | RW     | ACC1_DR0       | AD           | RW     | ACC0_DR<br>0 | ED           | RW     |

| DCB03DR2 | 2E           | RW     | TMP_DR2  | 6E           | RW     | ACC1_DR3       | AE           | RW     | ACC0_DR<br>3 | EE           | RW     |

| DCB03CR0 | 2F           | #      | TMP_DR3  | 6F           | RW     | ACC1_DR2       | AF           | RW     | ACC0_DR<br>2 | EF           | RW     |

|          | 30           |        | ACB00CR3 | 70           | RW     | RDIORI         | B0           | RW     |              | F0           |        |

|          | 31           |        | ACB00CR0 | 71           | RW     | <b>RDI0SYN</b> | B1           | RW     |              | F1           |        |

|          | 32           |        | ACB00CR1 | 72           | RW     | RDI0IS         | B2           | RW     |              | F2           |        |

|          | 33           |        | ACB00CR2 | 73           | RW     | RDI0LT0        | B3           | RW     |              | F3           |        |

|          | 34           |        | ACB01CR3 | 74           | RW     | RDI0LT1        | B4           | RW     |              | F4           |        |

|          | 35           |        | ACB01CR0 | 75           | RW     | RDI0RO0        | B5           | RW     |              | F5           |        |

|          | 36           |        | ACB01CR1 | 76           | RW     | RDI0RO1        | B6           | RW     |              | F6           |        |

|          | 37           |        | ACB01CR2 | 77           | RW     |                | B7           |        | CPU_F        | F7           | RL     |

|          | 38           |        |          | 78           |        |                | B8           |        |              | F8           |        |

|          | 39           |        |          | 79           |        |                | B9           |        |              | F9           |        |

|          | 3A           |        |          | 7A           |        |                | BA           |        |              | FA           |        |

|          | 3B           |        |          | 7B           |        |                | BB           |        |              | FB           |        |

|          | 3C           |        |          | 7C           |        |                | BC           |        |              | FC           |        |

|          | 3D           |        |          | 7D           |        |                | BD           |        | DAC_D        | FD           | RW     |

|          | 3E           |        |          | 7E           |        |                | BE           |        | CPU_SCR<br>1 | FE           | #      |

|          | 3F           |        |          | 7F           |        |                | BF           |        | CPU_SCR      | FF           | #      |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

# Table 4. Register Map Bank 1 Table: Configuration Space

| Name    | Addr (1,Hex) | Access | Name    | Addr (1,Hex) | Access | Name         | Addr (1,Hex) | Access | Name       | Addr (1,Hex) | Access |

|---------|--------------|--------|---------|--------------|--------|--------------|--------------|--------|------------|--------------|--------|

| PRT0DM0 | 00           | RW     | PMA0_WA | 40           | RW     | ASC10CR<br>0 | 80           | RW     | USBI/O_CR2 | CO           | RW     |

| PRT0DM1 | 01           | RW     | PMA1_WA | 41           | RW     | ASC10CR<br>1 | 81           | RW     | USB_CR1    | C1           | #      |

| PRT0IC0 | 02           | RW     | PMA2_WA | 42           | RW     | ASC10CR<br>2 | 82           | RW     |            |              |        |

| PRT0IC1 | 03           | RW     | PMA3_WA | 43           | RW     | ASC10CR<br>3 | 83           | RW     |            |              |        |

| PRT1DM0 | 04           | RW     | PMA4_WA | 44           | RW     | ASD11CR<br>0 | 84           | RW     | EP1_CR0    | C4           | #      |

| PRT1DM1 | 05           | RW     | PMA5_WA | 45           | RW     | ASD11CR<br>1 | 85           | RW     | EP2_CR0    | C5           | #      |

| PRT1IC0 | 06           | RW     | PMA6_WA | 46           | RW     | ASD11CR<br>2 | 86           | RW     | EP3_CR0    | C6           | #      |

| PRT1IC1 | 07           | RW     | PMA7_WA | 47           | RW     | ASD11CR<br>3 | 87           | RW     | EP4_CR0    | C7           | #      |

| PRT2DM0 | 08           | RW     |         | 48           |        |              | 88           |        |            | C8           |        |

| PRT2DM1 | 09           | RW     |         | 49           |        |              | 89           |        |            | C9           |        |

| PRT2IC0 | 0A           | RW     |         | 4A           |        |              | 8A           |        |            | CA           |        |

| PRT2IC1 | 0B           | RW     |         | 4B           |        |              | 8B           |        |            | СВ           |        |

| PRT3DM0 | 0C           | RW     |         | 4C           |        |              | 8C           |        |            | CC           |        |

| PRT3DM1 | 0D           | RW     |         | 4D           |        |              | 8D           |        |            | CD           |        |

| PRT3IC0 | 0E           | RW     |         | 4E           | 1      |              | 8E           |        |            | CE           |        |

| PRT3IC1 | 0F           | RW     |         | 4F           |        |              | 8F           |        |            | CF           |        |

| PRT4DM0 | 10           | RW     | PMA0_RA | 50           | RW     |              | 90           |        | GDI_O_IN   | D0           | RW     |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8CLED04 EZ-Color device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at <a href="http://www.cypress.com/ez-color">http://www.cypress.com/ez-color</a>.

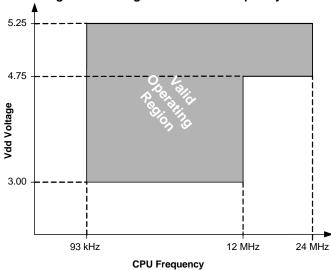

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications for devices running at greater than 12 MHz are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C and T<sub>J</sub>  $\leq$  82 °C.

# Figure 4. Voltage versus CPU Frequency

# Absolute Maximum Ratings

| Symbol             | Description                                                   | Min                      | Тур | Max                      | Units | Notes                                                                                                                                                                                                          |

|--------------------|---------------------------------------------------------------|--------------------------|-----|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>   | Storage temperature                                           | -55                      | 25  | +100                     | °C    | Higher storage temperatures will<br>reduce data retention time.<br>Recommended storage<br>temperature is +25 °C ± 25 °C.<br>Extended duration storage<br>temperatures above 65 °C will<br>degrade reliability. |

| T <sub>A</sub>     | Ambient temperature with power applied                        | -40                      | -   | +85                      | °C    |                                                                                                                                                                                                                |

| V <sub>DD</sub>    | Supply voltage on V <sub>DD</sub> relative to V <sub>SS</sub> | -0.5                     | -   | +6.0                     | V     |                                                                                                                                                                                                                |

| V <sub>I/O</sub>   | DC input voltage                                              | V <sub>SS</sub> -<br>0.5 | -   | V <sub>DD</sub> +<br>0.5 | V     |                                                                                                                                                                                                                |

| V <sub>I/O2</sub>  | DC voltage applied to tri-state                               | V <sub>SS</sub> -<br>0.5 | -   | V <sub>DD</sub> +<br>0.5 | V     |                                                                                                                                                                                                                |

| I <sub>MI/O</sub>  | Maximum current into any port pin                             | -25                      | -   | +50                      | mA    |                                                                                                                                                                                                                |

| I <sub>MAI/O</sub> | Maximum current into any port pin configured as analog driver | -50                      | -   | +50                      | mA    |                                                                                                                                                                                                                |

| ESD                | Electrostatic discharge voltage                               | 2000                     | -   | -                        | V     | Human Body Model ESD.                                                                                                                                                                                          |

| LU                 | Latch-up current                                              | -                        | -   | 200                      | mA    |                                                                                                                                                                                                                |

# **Operating Temperature**

| Symbol            | Description                   | Min | Тур | Max  | Units | Notes                                                                                                                                                                                            |

|-------------------|-------------------------------|-----|-----|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub>    | Ambient temperature           | -40 | -   | +85  | °C    |                                                                                                                                                                                                  |

| T <sub>AUSB</sub> | Ambient temperature using USB | -10 | -   | +85  | °C    |                                                                                                                                                                                                  |

| Т                 | Junction temperature          | -40 | _   | +100 | °C    | The temperature rise from ambient<br>to junction is package specific. See<br>"Thermal Impedance" on page 38.<br>The user must limit the power<br>consumption to comply with this<br>requirement. |

## DC Low Power Comparator Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V at 25 °C and are for design guidance only.

#### Table 9. DC Low Power Comparator Specifications

| Symbol              | Description                                        | Min | Тур | Max                 | Units | Notes |

|---------------------|----------------------------------------------------|-----|-----|---------------------|-------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | -   | V <sub>DD</sub> - 1 | V     |       |

| I <sub>SLPC</sub>   | LPC supply current                                 | -   | 10  | 40                  | μA    |       |

| V <sub>OSLPC</sub>  | LPC voltage offset                                 | -   | 2.5 | 30                  | mV    |       |

#### DC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 10. 5-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                                        | Min                                                        | Тур        | Max                                                        | Units    | Notes                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| CL                   | Load capacitance                                                                                   | _                                                          | Ι          | 200                                                        | pF       | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                              | _                                                          | 3          | 12                                                         | mV       |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                 | -                                                          | +6         | -                                                          | µV/°C    |                                                                                                      |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                    | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                      | V        |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                   |                                                            | 0.6<br>0.6 |                                                            | W<br>W   |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing<br>(Load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high | 0.5 × V <sub>DD</sub> + 1.1<br>0.5 × V <sub>DD</sub> + 1.1 | -          |                                                            | V<br>V   |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(Load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high  |                                                            |            | 0.5 × V <sub>DD</sub> – 1.3<br>0.5 × V <sub>DD</sub> – 1.3 | V<br>V   |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including opamp bias<br>cell<br>(No Load)<br>Power = low<br>Power = high            |                                                            | 1.1<br>2.6 | 5.1<br>8.8                                                 | mA<br>mA |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                     | 53                                                         | 64         | -                                                          | dB       | $(0.5 \times V_{DD} - 1.3) \pm V_{OUT} \pm (V_{DD} - 2.3).$                                          |

# Table 13. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reference Power<br>Settings            | Symbol             | Reference | Description                                                | Min                        | Тур                        | Max                        | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|-----------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.200 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.365 | V     |

| ARF_CR         Image: Second seco | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.030$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.034$         | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 - 1.346 | V <sub>DD</sub> /2 - 1.292 | V <sub>DD</sub> /2 - 1.208 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.196 | $V_{DD}/2 + 1.292$         | V <sub>DD</sub> /2 + 1.374 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.029$         | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.031 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 - 1.349 | V <sub>DD</sub> /2 - 1.295 | V <sub>DD</sub> /2 – 1.227 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.204 | $V_{DD}/2 + 1.293$         | V <sub>DD</sub> /2 + 1.369 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 - 0.030 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.030$         | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 - 1.351 | V <sub>DD</sub> /2 - 1.297 | V <sub>DD</sub> /2 - 1.229 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.189 | $V_{DD}/2 + 1.294$         | V <sub>DD</sub> /2 + 1.384 | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.032$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.029$         | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 - 1.353 | V <sub>DD</sub> /2 - 1.297 | V <sub>DD</sub> /2 - 1.230 | V     |

| 0b001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.105   | P2[4]+P2[6]-<br>0.008      | P2[4]+P2[6]+<br>0.095      | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.035   | P2[4]-P2[6]+<br>0.006      | P2[4]-P2[6]+<br>0.053      | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.094   | P2[4]+P2[6]-<br>0.005      | P2[4]+P2[6]+<br>0.073      | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.033   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.042      | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.094   | P2[4]+P2[6]-<br>0.003      | P2[4]+P2[6]+<br>0.075      | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.035   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.038      | V     |