Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 20MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 12                                                          |

| Program Memory Size        | 4KB (4K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 256 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                             |

| Supplier Device Package    | 16-TSSOP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qg44cdte |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT1 enabling the COP watchdog (see Section 5.8.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

The COPCLKS bit in SOPT2 (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there is an associated short and long time-out controlled by COPT in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the associated long time-out ( $2^8$  cycles).

| Control Bits |      | Clock Source | COP Overflow Count                          |  |

|--------------|------|--------------|---------------------------------------------|--|

| COPCLKS      | СОРТ | Clock Source |                                             |  |

| 0            | 0    | ~1 kHz       | 2 <sup>5</sup> cycles (32 ms) <sup>1</sup>  |  |

| 0            | 1    | ~1 kHz       | 2 <sup>8</sup> cycles (256 ms) <sup>1</sup> |  |

| 1            | 0    | Bus          | 2 <sup>13</sup> cycles                      |  |

| 1            | 1    | Bus          | 2 <sup>18</sup> cycles                      |  |

| Table 5-1. COP Configuration Option |

|-------------------------------------|

|-------------------------------------|

<sup>1</sup> Values are shown in this column based on  $t_{RTI} = 1$  ms. See  $t_{RTI}$  in the appendix Section A.8.1, "Control Timing," for the tolerance of this value.

Even if the application will use the reset default settings of COPE, COPCLKS, and COPT, the user must write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost. The initial writes to SOPT1 and SOPT2 will reset the COP counter.

The write to SRS that services (clears) the COP counter must not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

In background debug mode, the COP counter will not increment.

When the bus clock source is selected, the COP counter does not increment while the system is in stop mode. The COP counter resumes as soon as the MCU exits stop mode.

# 5.8.8 System Power Management Status and Control 1 Register (SPMSC1)

This high page register contains status and control bits to support the low voltage detect function and to enable the bandgap voltage reference for use by the ADC module. To configure the low voltage detect trip voltage, see Table 5-14 for the LVDV bit description in SPMSC3.

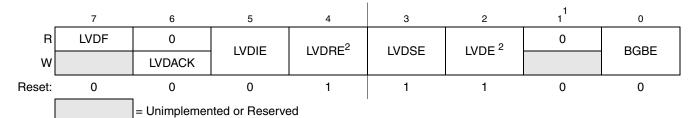

Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

<sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Table 5-12. SPMSC1 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                           |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                                          |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This write-once bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

| 0<br>BGBE   | <ul> <li>Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels or as a voltage reference for ACMP module.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>          |

Chapter 6 Parallel Input/Output Control

\_\_\_\_\_

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode<br>Qpj                              | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                            | Affect<br>on CCR |                                                |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|------------------|------------------------------------------------|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    | βά<br>Μ                                             |                                                                                  | ර                               | Dotano                                           | VH               | INZC                                           |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓-               | -:::                                           |

| SWI                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + \$0001<br>Push (PCL); SP $\leftarrow$ (SP) - \$0001<br>Push (PCH); SP $\leftarrow$ (SP) - \$0001<br>Push (X); SP $\leftarrow$ (SP) - \$0001<br>Push (A); SP $\leftarrow$ (SP) - \$0001<br>Push (CCR); SP $\leftarrow$ (SP) - \$0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | ssssvvfppp                                       |                  | 1                                              |

| ТАР                                                                                                             | Transfer Accumulator to CCR $CCR \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | p                                                | ¢¢               | $\uparrow \uparrow \uparrow \uparrow \uparrow$ |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low) $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 97                                                                               | 1                               | р                                                |                  |                                                |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                |                  |                                                |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | Test for Negative or Zero (M) - \$00<br>(A) - \$00<br>(X) - \$00<br>(M) - \$00<br>(M) - \$00<br>(M) - \$00                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                | 0 —              | - \$ \$ -                                      |

| тѕх                                                                                                             | Transfer SP to Index Reg.<br>H:X $\leftarrow$ (SP) + \$0001                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 95                                                                               | 2                               | fp                                               |                  |                                                |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator A $\leftarrow$ (X)                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | p                                                |                  |                                                |

| Table 7-2 Instrue | ction Set Summary | (Sheet 8 of 9) |

|-------------------|-------------------|----------------|

|-------------------|-------------------|----------------|

Inter-Integrated Circuit (S08IICV1)

### 11.4.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 11-8, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 11.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 11-8).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

### 11.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 11-8. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

#### Chapter 12 Keyboard Interrupt (S08KBIV2)

#### NOTES:

- <sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

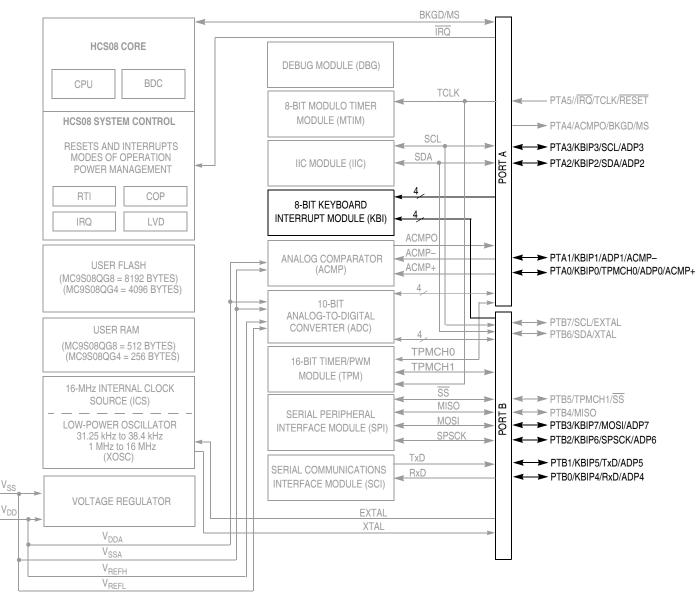

#### Figure 12-1. MC9S08QG8/4 Block Diagram Highlighting KBI Block and Pins

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

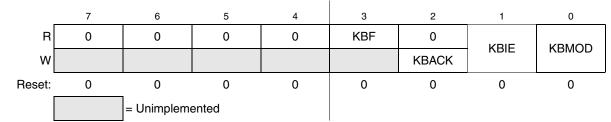

#### Figure 12-3. KBI Status and Control Register

#### Table 12-2. KBISC Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                 |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:4        | Unused register bits, always read 0.                                                                                                                                                                                        |  |  |

| 3<br>KBF   | <ul> <li>Keyboard Interrupt Flag — KBF indicates when a keyboard interrupt is detected. Writes have no effect on KBF.</li> <li>0 No keyboard interrupt detected.</li> <li>1 Keyboard interrupt detected.</li> </ul>         |  |  |

| 2<br>KBACK | <b>Keyboard Acknowledge</b> — Writing a 1 to KBACK is part of the flag clearing mechanism. KBACK always reads as 0.                                                                                                         |  |  |

| 1<br>KBIE  | <ul> <li>Keyboard Interrupt Enable — KBIE determines whether a keyboard interrupt is requested.</li> <li>Keyboard interrupt request not enabled.</li> <li>Keyboard interrupt request enabled.</li> </ul>                    |  |  |

| 0<br>KBMOD | <ul> <li>Keyboard Detection Mode — KBMOD (along with the KBEDG bits) controls the detection mode of the keyboard interrupt pins.0Keyboard detects edges only.</li> <li>1 Keyboard detects both edges and levels.</li> </ul> |  |  |

### 12.3.2 KBI Pin Enable Register (KBIPE)

KBIPE contains the pin enable control bits.

| Figure 12-4 | KBI Pin | Enable | Register |

|-------------|---------|--------|----------|

|-------------|---------|--------|----------|

### Table 12-3. KBIPE Register Field Descriptions

| Field | Description                                                                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Keyboard Pin Enables — Each of the KBIPEn bits enable the corresponding keyboard interrupt pin.</li> <li>0 Pin not enabled as keyboard interrupt.</li> <li>1 Pin enabled as keyboard interrupt.</li> </ul> |

### 12.3.3 KBI Edge Select Register (KBIES)

KBIES contains the edge select control bits.

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

KBISC provided all enabled keyboard inputs are at their deasserted levels. KBF will remain set if any enabled KBI pin is asserted while attempting to clear by writing a 1 to KBACK.

### 12.4.3 KBI Pullup/Pulldown Resistors

The KBI pins can be configured to use an internal pullup/pulldown resistor using the associated I/O port pullup enable register. If an internal resistor is enabled, the KBIES register is used to select whether the resistor is a pullup (KBEDGn = 0) or a pulldown (KBEDGn = 1).

### 12.4.4 KBI Initialization

When a keyboard interrupt pin is first enabled it is possible to get a false keyboard interrupt flag. To prevent a false interrupt request during keyboard initialization, the user should do the following:

- 1. Mask keyboard interrupts by clearing KBIE in KBISC.

- 2. Enable the KBI polarity by setting the appropriate KBEDGn bits in KBIES.

- 3. If using internal pullup/pulldown device, configure the associated pullup enable bits in PTxPE.

- 4. Enable the KBI pins by setting the appropriate KBIPEn bits in KBIPE.

- 5. Write to KBACK in KBISC to clear any false interrupts.

- 6. Set KBIE in KBISC to enable interrupts.

Modulo Timer (S08MTIMV1)

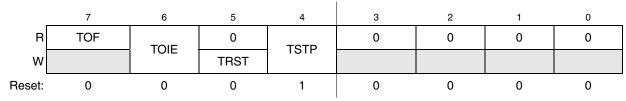

# 13.3.1 MTIM Status and Control Register (MTIMSC)

MTIMSC contains the overflow status flag and control bits which are used to configure the interrupt enable, reset the counter, and stop the counter.

### Figure 13-4. MTIM Status and Control Register

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF  | <ul> <li>MTIM Overflow Flag — This read-only bit is set when the MTIM counter register overflows to \$00 after reaching the value in the MTIM modulo register. Clear TOF by reading the MTIMSC register while TOF is set, then writing a 0 to TOF. TOF is also cleared when TRST is written to a 1 or when any value is written to the MTIMMOD register.</li> <li>0 MTIM counter has not reached the overflow value in the MTIM modulo register.</li> <li>1 MTIM counter has reached the overflow value in the MTIM modulo register.</li> </ul> |

| 6<br>TOIE | <ul> <li>MTIM Overflow Interrupt Enable — This read/write bit enables MTIM overflow interrupts. If TOIE is set, then an interrupt is generated when TOF = 1. Reset clears TOIE. Do not set TOIE if TOF = 1. Clear TOF first, then set TOIE.</li> <li>0 TOF interrupts are disabled. Use software polling.</li> <li>1 TOF interrupts are enabled.</li> </ul>                                                                                                                                                                                     |

| 5<br>TRST | <ul> <li>MTIM Counter Reset — When a 1 is written to this write-only bit, the MTIM counter register resets to \$00 and TOF is cleared. Reading this bit always returns 0.</li> <li>0 No effect. MTIM counter remains at current state.</li> <li>1 MTIM counter is reset to \$00.</li> </ul>                                                                                                                                                                                                                                                     |

| 4<br>TSTP | <ul> <li>MTIM Counter Stop — When set, this read/write bit stops the MTIM counter at its current value. Counting resumes from the current value when TSTP is cleared. Reset sets TSTP to prevent the MTIM from counting.</li> <li>0 MTIM counter is active.</li> <li>1 MTIM counter is stopped.</li> </ul>                                                                                                                                                                                                                                      |

| 3:0       | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

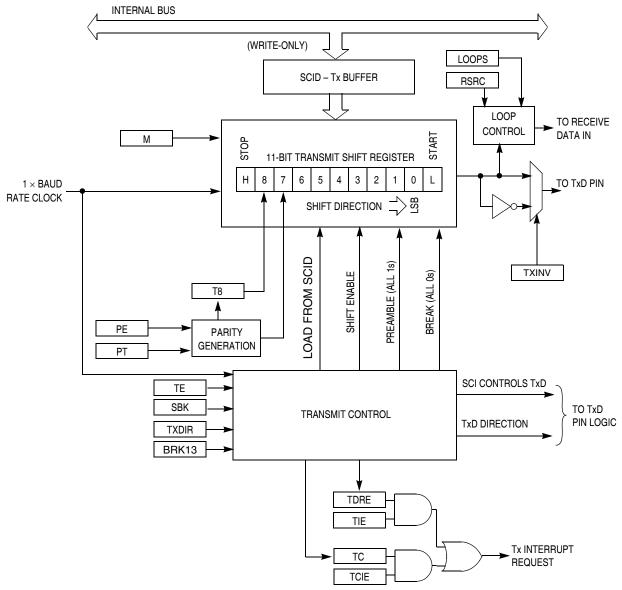

### 14.1.3 Block Diagram

Figure 14-3 shows the transmitter portion of the SCI. (Figure 14-4 shows the receiver portion of the SCI.)

Figure 14-3. SCI Transmitter Block Diagram

| Field    | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0      | Baud Rate Modulo Divisor — These 13 bits are referred to collectively as BR, and they set the modulo divide                                                                                                             |

| SBR[7:0] | rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = $BUSCLK/(16 \times BR)$ . See also BR bits in Table 14-1. |

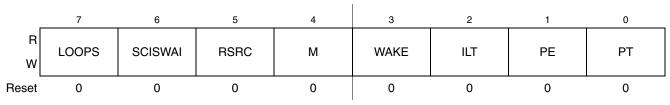

# 14.2.2 SCI Control Register 1 (SCIC1)

This read/write register is used to control various optional features of the SCI system.

Figure 14-7. SCI Control Register 1 (SCIC1)

### Table 14-3. SCIC1 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                 |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                    |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters<br/>start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                      |

| 3<br>WAKE    | <ul> <li>Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.</li> <li>0 Idle-line wakeup.</li> <li>1 Address-mark wakeup.</li> </ul>                                                                                                                                                                                                                                                                                            |

| 2<br>ILT     | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of the logic high level by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit.                                                           |

selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in the transmit data register is transferred to the shift register (synchronized with the baud rate clock) and the transmit data register empty (TDRE) status flag is set to indicate another character may be written to the transmit data buffer at SCID.

If no new character is waiting in the transmit data buffer after a stop bit is shifted out the TxD1 pin, the transmitter sets the transmit complete flag and enters an idle mode, with TxD1 high, waiting for more characters to transmit.

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

### 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD1 pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD1 is an output driving a logic 1. This ensures that the TxD1 line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М | Break Character Length |

|-------|---|------------------------|

| 0     | 0 | 10 bit times           |

| 0     | 1 | 11 bit times           |

| 1     | 0 | 13 bit times           |

| 1     | 1 | 14 bit times           |

| Table <sup>•</sup> | 14-8. | Break | Character | Length |

|--------------------|-------|-------|-----------|--------|

|--------------------|-------|-------|-----------|--------|

Timer/Pulse-Width Modulator (S08TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

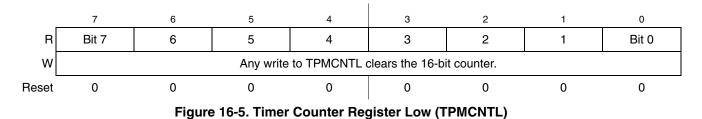

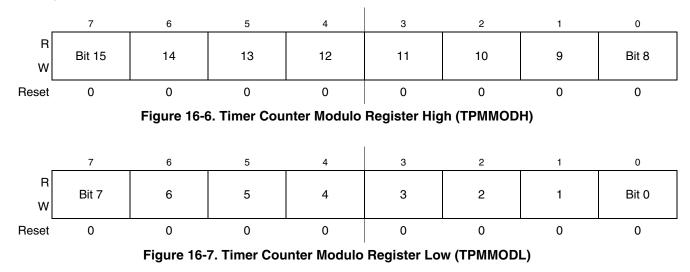

# 16.3.3 Timer Counter Modulo Registers (TPMMODH:TPMMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMMODH or TPMMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

# Chapter 17 Development Support

# 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins. Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 17.1.1 Module Configuration

The alternate BDC clock source is the ICSLCLK. This clock source is selected by clearing the CLKSW bit in the BDCSCR register. For details on ICSLCLK, see Section 10.4, "Functional Description" of the ICS chapter.

#### Development Support

driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a debug pod is connected to BKGD it is possible to force the MCU into active background mode after reset. The specific conditions for forcing active background depend upon the HCS08 derivative (refer to the introduction to this Development Support section). It is not necessary to reset the target MCU to communicate with it through the background debug interface.

### 17.2.2 Communication Details

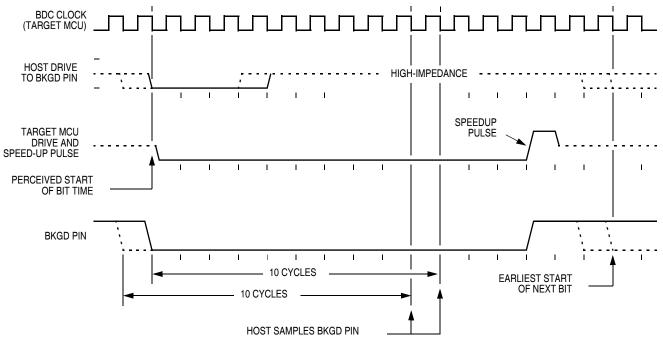

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Figure 17-2 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target HCS08 MCU. The host is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin during the host-to-target transmission period, there is no need to treat the line as an open-drain signal during this period.

#### Development Support

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

### 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

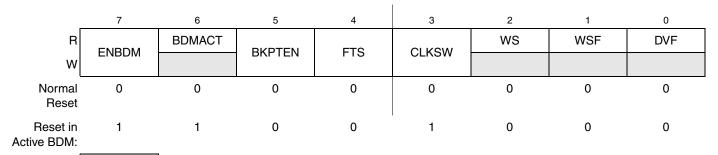

### 17.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

#### Figure 17-5. BDC Status and Control Register (BDCSCR)

#### Table 17-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.</li> <li>0 BDM cannot be made active (non-intrusive commands still allowed)</li> <li>1 BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                |

| 6<br>BDMACT | <ul> <li>Background Mode Active Status — This is a read-only status bit.</li> <li>0 BDM not active (user application program running)</li> <li>1 BDM active and waiting for serial commands</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |

| 3<br>CLKSW  | <ul> <li>Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.</li> <li>0 Alternate BDC clock source</li> <li>1 MCU bus clock</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parameter                                          | Symbol | V <sub>DD</sub> (V) <sup>1</sup> | Typical <sup>2</sup> | Max | T (°C) |

|----------------------------------------------------|--------|----------------------------------|----------------------|-----|--------|

| RTI adder to stop1, stop2 or stop3 <sup>4</sup>    | _      | 3                                | 300 nA               | _   | 85     |

| RTT adder to stop 1, stop2 of stop3                |        | 2                                | 300 nA               | _   | 85     |

| LVD adder to stop3 (LVDE = LVDSE = 1)              |        | 3                                | 70 μA                | _   | 85     |

|                                                    |        | 2                                | 60 μA                | -   | 85     |

| Adder to stop3 for oscillator enabled <sup>5</sup> | _      | 3                                | 5 μΑ                 | _   | 85     |

| (EREFSTEN =1)                                      |        | 2                                | 4 μΑ                 |     | 85     |

#### Table A-7. Supply Current Characteristics

<sup>1</sup> 3-V values are 100% tested; 2-V values are characterized but not tested.

<sup>2</sup> Typicals are measured at 25°C.

<sup>3</sup> Does not include any DC loads on port pins.

- <sup>4</sup> Most customers are expected to find that auto-wakeup from a stop mode can be used instead of the higher current wait mode.

- <sup>5</sup> Values given under the following conditions: low range operation (RANGE = 0), Loss-of-clock disabled (LOCD = 1), low-power oscillator (HGO = 0).

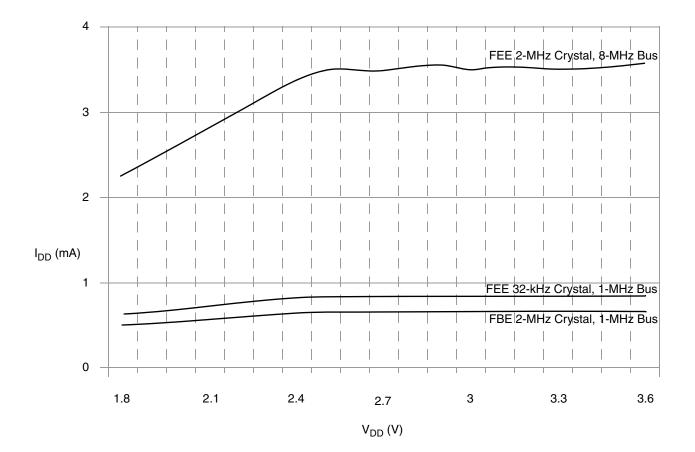

Figure A-6. Typical Run I<sub>DD</sub> for FBE and FEE, I<sub>DD</sub> vs. V<sub>DD</sub> (ACMP and ADC off, All Other Modules Enabled)

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

Appendix A Electrical Characteristics

# A.7 External Oscillator (XOSC) and Internal Clock Source (ICS) Characteristics

Reference Figure A-7 for crystal or resonator circuit.

| Symbol                                                                   | Min                                                                                                                                                                                                                                                                                                                   | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unit                                                   |  |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| f <sub>int_ft</sub>                                                      | _                                                                                                                                                                                                                                                                                                                     | 31.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | kHz                                                    |  |  |  |  |

| f <sub>lo</sub><br>f <sub>hi</sub><br>f <sub>hi</sub><br>f <sub>hi</sub> | 32<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                     | <br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38.4<br>5<br>16<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | kHz<br>MHz<br>MHz<br>MHz                               |  |  |  |  |

| C <sub>1</sub><br>C <sub>2</sub>                                         | See Note <sup>2</sup>                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |  |  |  |  |