Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | -                                                                      |

| Core Size                  | -                                                                      |

| Speed                      | -                                                                      |

| Connectivity               | -                                                                      |

| Peripherals                | -                                                                      |

| Number of I/O              | -                                                                      |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | -                                                                      |

| EEPROM Size                | -                                                                      |

| RAM Size                   | -                                                                      |

| Voltage - Supply (Vcc/Vdd) | -                                                                      |

| Data Converters            | -                                                                      |

| Oscillator Type            | -                                                                      |

| Operating Temperature      | -                                                                      |

| Mounting Type              | -                                                                      |

| Package / Case             | -                                                                      |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg4cdter |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This product incorporates SuperFlash<sup>®</sup> Technology licensed from SST.

**Section Number**

### Title

Page

## Chapter 14 Serial Communications Interface (S08SCIV3)

| 14.1 | 1 Introduction                                  |  |

|------|-------------------------------------------------|--|

|      | 14.1.1 Features                                 |  |

|      | 14.1.2 Modes of Operation                       |  |

|      | 14.1.3 Block Diagram                            |  |

| 14.2 | 2 Register Definition                           |  |

|      | 14.2.1 SCI Baud Rate Registers (SCIBDH, SCIBHL) |  |

|      | 14.2.2 SCI Control Register 1 (SCIC1)           |  |

|      | 14.2.3 SCI Control Register 2 (SCIC2)           |  |

|      | 14.2.4 SCI Status Register 1 (SCIS1)            |  |

|      | 14.2.5 SCI Status Register 2 (SCIS2)            |  |

|      | 14.2.6 SCI Control Register 3 (SCIC3)           |  |

|      | 14.2.7 SCI Data Register (SCID)                 |  |

| 14.3 | 3 Functional Description                        |  |

|      | 14.3.1 Baud Rate Generation                     |  |

|      | 14.3.2 Transmitter Functional Description       |  |

|      | 14.3.3 Receiver Functional Description          |  |

|      | 14.3.4 Interrupts and Status Flags              |  |

| 14.4 | 4 Additional SCI Functions                      |  |

|      | 14.4.1 8- and 9-Bit Data Modes                  |  |

|      | 14.4.2 Stop Mode Operation                      |  |

|      | 14.4.3 Loop Mode                                |  |

|      | 14.4.4 Single-Wire Operation                    |  |

## Chapter 15 Serial Peripheral Interface (S08SPIV3)

| Introduction                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1.2 Block Diagrams                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1.3 SPI Baud Rate Generation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| External Signal Description                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.1 SPSCK — SPI Serial Clock              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.2 MOSI — Master Data Out, Slave Data In |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.3 MISO — Master Data In, Slave Data Out |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.4 $\overline{\text{SS}}$ — Slave Select |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Modes of Operation                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3.1 SPI in Stop Modes                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Register Definition                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.1 SPI Control Register 1 (SPIC1)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.2 SPI Control Register 2 (SPIC2)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.3 SPI Baud Rate Register (SPIBR)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | <ul> <li>15.1.1 Features.</li> <li>15.1.2 Block Diagrams</li> <li>15.1.3 SPI Baud Rate Generation</li> <li>External Signal Description</li> <li>15.2.1 SPSCK — SPI Serial Clock.</li> <li>15.2.2 MOSI — Master Data Out, Slave Data In</li> <li>15.2.3 MISO — Master Data In, Slave Data Out</li> <li>15.2.4 SS — Slave Select</li> <li>Modes of Operation.</li> <li>15.3.1 SPI in Stop Modes</li> <li>Register Definition</li> <li>15.4.1 SPI Control Register 1 (SPIC1)</li> <li>15.4.2 SPI Control Register 2 (SPIC2)</li> </ul> |

#### Chapter 4 Memory Map and Register Definition

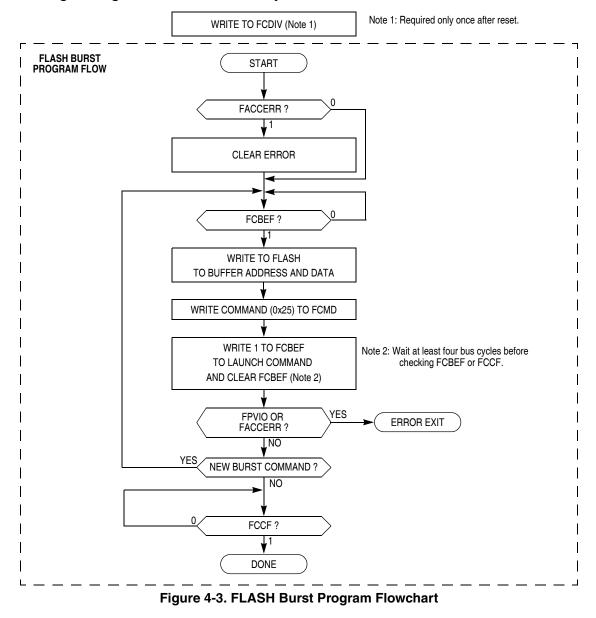

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

### Table 4-11. FPROT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>FPS | <b>FLASH Protect Select Bits</b> — When FPDIS = 0, this 7-bit field determines the ending address of unprotected FLASH locations at the high address end of the FLASH. Protected FLASH locations cannot be erased or programmed. |

| 0<br>FPDIS | <ul> <li>FLASH Protection Disable</li> <li>0 FLASH block specified by FPS7:FPS1 is block protected (program or erase not allowed).</li> <li>1 No FLASH block is protected.</li> </ul>                                            |

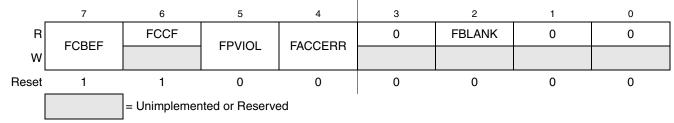

### 4.7.5 FLASH Status Register (FSTAT)

### Figure 4-9. FLASH Status Register (FSTAT)

### Table 4-12. FSTAT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF  | <ul> <li>FLASH Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a 1 to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.</li> <li>0 Command buffer is full (not ready for additional commands).</li> <li>1 A new burst program command can be written to the command buffer.</li> </ul> |

| 6<br>FCCF   | <ul> <li>FLASH Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.</li> <li>0 Command in progress</li> <li>1 All commands complete</li> </ul>                                                                                                                                                                                             |

| 5<br>FPVIOL | <ul> <li>Protection Violation Flag — FPVIOL is set automatically when FCBEF is cleared to register a command that attempts to erase or program a location in a protected block (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.</li> <li>0 No protection violation.</li> <li>1 An attempt was made to erase or program a protected location.</li> </ul>                                                                                                                                                                           |

| Table 4-12. FSTAT Register Field Descriptions (continu | Jed) |

|--------------------------------------------------------|------|

|--------------------------------------------------------|------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred. |

| 2<br>FBLANK  | <ul> <li>FLASH Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>0 After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>     |

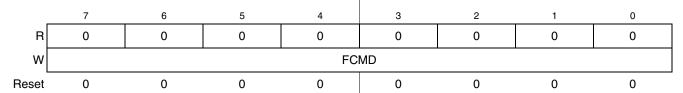

### 4.7.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-13. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of FLASH programming and erase operations.

Figure 4-10. FLASH Command Register (FCMD)

| Command                     | FCMD | Equate File Label |

|-----------------------------|------|-------------------|

| Blank check                 | 0x05 | mBlank            |

| Byte program                | 0x20 | mByteProg         |

| Byte program — burst mode   | 0x25 | mBurstProg        |

| Page erase (512 bytes/page) | 0x40 | mPageErase        |

| Mass erase (all FLASH)      | 0x41 | mMassErase        |

Table 4-13. FLASH Commands

All other command codes are illegal and generate an access error.

It is not necessary to perform a blank check command after a mass erase operation. The blank check command is only required as part of the security unlocking mechanism.

# Chapter 5 Resets, Interrupts, and General System Control

## 5.1 Introduction

This section discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts in the MC9S08QG8/4. Some interrupt sources from peripheral modules are discussed in greater detail within other sections of this data sheet. This section gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog and real-time interrupt (RTI), are not part of on-chip peripheral systems with their own chapters but are part of the system control logic.

## 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vectors for each module (reduces polling overhead) (see Table 5-2)

## 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose, high-impedance inputs with pullup devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The MC9S08QG8/4 has the following sources for reset:

- External pin reset (PIN) enabled using RSTPE in SOPT1

- Power-on reset (POR)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Illegal address detect (ILAD)

- Background debug force reset

Each of these sources, with the exception of the background debug force reset, has an associated bit in the system reset status register.

## 5.6 Low-Voltage Detect (LVD) System

The MC9S08QG8/4 includes a system to protect against low voltage conditions to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC3. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop1 or stop2, and the current consumption in stop3 with the LVD enabled will be greater.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured using SPMSC1 for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF in SPMSC1 will be set and an LVD interrupt request will occur.

### 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, but is above, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC3.

### 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1-kHz internal clock or an external clock if available. External clock input requires the XOSC module; consult Table 1-1 to see if your MCU contains this module. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Either RTI clock source can be used when the MCU is in run, wait or stop3 mode. When using the external oscillator in stop3, it must be enabled in stop (EREFSTEN = 1) and configured for low frequency operation

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Table 7-2 | Instruction | Set Summary | (Sheet 9 of 9) |

|-----------|-------------|-------------|----------------|

|-----------|-------------|-------------|----------------|

| Source<br>Form | Operation                                                            | ddress<br>Mode<br>IqO | Object Code | ycles | Cyc-by-Cyc<br>Details | Affect<br>on CCR |      |

|----------------|----------------------------------------------------------------------|-----------------------|-------------|-------|-----------------------|------------------|------|

|                |                                                                      | Ac                    |             | S     |                       | VH               | INZC |

| TXS            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – \$0001             | INH                   | 94          | 2     | fp                    |                  |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH                   | 8 F         | 2+    | fp                    |                  | 0    |

**Source Form:** Everything in the source forms columns, *except expressions in italic characters*, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (# , () and +) are always a literal characters.

*n* Any label or expression that evaluates to a single integer in the range 0-7.

*opr8i* Any label or expression that evaluates to an 8-bit immediate value.

*opr16i* Any label or expression that evaluates to a 16-bit immediate value.

opr8a Any label or expression that evaluates to an 8-bit direct-page address (\$00xx).

opr16a Any label or expression that evaluates to a 16-bit address.

oprx8 Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing.

oprx16 Any label or expression that evaluates to a 16-bit value, used for indexed addressing.

rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

#### **Operation Symbols:**

| Α | Accumulator |

|---|-------------|

|   |             |

- CCR Condition code register

- H Index register high byte

- M Memory location

- n Any bit

- opr Operand (one or two bytes)

- PC Program counter

- PCH Program counter high byte

- PCL Program counter low byte

- rel Relative program counter offset byte

- SP Stack pointer

- SPL Stack pointer low byte

- X Index register low byte

- & Logical AND

- Logical OR

- Logical EXCLUSIVE OR

- () Contents of

- + Add

- Subtract, Negation (two's complement)

- × Multiply

- ÷ Divide

- # Immediate value

- $\leftarrow \qquad \text{Loaded with} \qquad$

- : Concatenated with

#### CCR Bits:

- V Overflow bit

- H Half-carry bit

- I Interrupt mask

- N Negative bit

- Z Zero bit

- C Carry/borrow bit

#### Addressing Modes:

- DIR Direct addressing mode

- EXT Extended addressing mode

- IMM Immediate addressing mode

- INH Inherent addressing mode

- IX Indexed, no offset addressing mode

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- IX+ Indexed, no offset, post increment addressing mode

- IX1+ Indexed, 8-bit offset, post increment addressing mode

- REL Relative addressing mode

- SP1 Stack pointer, 8-bit offset addressing mode

- SP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

- f Free cycle. This indicates a cycle where the CPU does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- p Progryam fetch; read from next consecutive location in program memory

- r Read 8-bit operand

- s Push (write) one byte onto stack

- u Pop (read) one byte from stack

- v Read vector from \$FFxx (high byte first)

- w Write 8-bit operand

#### CCR Effects:

- \$\$ Set or cleared

- Not affected

- U Undefined

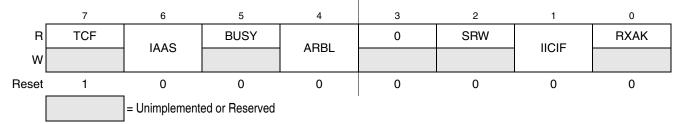

## 11.3.4 IIC Status Register (IICS)

Figure 11-6. IIC Status Register (IICS)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TCF   | <ul> <li>Transfer Complete Flag — This bit is set on the completion of a byte transfer. Note that this bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress.</li> <li>1 Transfer complete.</li> </ul>                 |  |  |  |  |  |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave — The IAAS bit is set when the calling address matches the programmed slave address.</li> <li>Writing the IICC register clears this bit.</li> <li>0 Not addressed.</li> <li>1 Addressed as a slave.</li> </ul>                                                                                                                                                                         |  |  |  |  |  |

| 5<br>BUSY  | <ul> <li>Bus Busy — The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a START signal is detected and cleared when a STOP signal is detected.</li> <li>0 Bus is idle.</li> <li>1 Bus is busy.</li> </ul>                                                                                                                                                      |  |  |  |  |  |

| 4<br>ARBL  | <ul> <li>Arbitration Lost — This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software, by writing a one to it.</li> <li>0 Standard bus operation.</li> <li>1 Loss of arbitration.</li> </ul>                                                                                                                                                                      |  |  |  |  |  |

| 2<br>SRW   | <ul> <li>Slave Read/Write — When addressed as a slave the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>O Slave receive, master writing to slave.</li> <li>1 Slave transmit, master reading from slave.</li> </ul>                                                                                                                                          |  |  |  |  |  |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag — The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a one to it in the interrupt routine. One of the following events can set the IICIF bit:</li> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> <li>No interrupt pending.</li> <li>1 Interrupt pending.</li> </ul> |  |  |  |  |  |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge — When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received.</li> <li>1 No acknowledge received.</li> </ul>                                                                             |  |  |  |  |  |

KBISC provided all enabled keyboard inputs are at their deasserted levels. KBF will remain set if any enabled KBI pin is asserted while attempting to clear by writing a 1 to KBACK.

### 12.4.3 KBI Pullup/Pulldown Resistors

The KBI pins can be configured to use an internal pullup/pulldown resistor using the associated I/O port pullup enable register. If an internal resistor is enabled, the KBIES register is used to select whether the resistor is a pullup (KBEDGn = 0) or a pulldown (KBEDGn = 1).

### 12.4.4 KBI Initialization

When a keyboard interrupt pin is first enabled it is possible to get a false keyboard interrupt flag. To prevent a false interrupt request during keyboard initialization, the user should do the following:

- 1. Mask keyboard interrupts by clearing KBIE in KBISC.

- 2. Enable the KBI polarity by setting the appropriate KBEDGn bits in KBIES.

- 3. If using internal pullup/pulldown device, configure the associated pullup enable bits in PTxPE.

- 4. Enable the KBI pins by setting the appropriate KBIPEn bits in KBIPE.

- 5. Write to KBACK in KBISC to clear any false interrupts.

- 6. Set KBIE in KBISC to enable interrupts.

### 13.3.2 MTIM Clock Configuration Register (MTIMCLK)

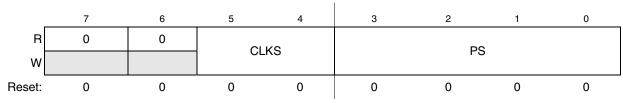

MTIMCLK contains the clock select bits (CLKS) and the prescaler select bits (PS).

Figure 13-5. MTIM Clock Configuration Register

### Table 13-3. MTIM Clock Configuration Register Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6         | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:4<br>CLKS | Clock Source Select — These two read/write bits select one of four different clock sources as the input to the MTIM prescaler. Changing the clock source while the counter is active does not clear the counter. The count continues with the new clock source. Reset clears CLKS to 000.         00       Encoding 0. Bus clock (BUSCLK)         01       Encoding 1. Fixed-frequency clock (XCLK)         10       Encoding 3. External source (TCLK pin), falling edge         11       Encoding 4. External source (TCLK pin), rising edge         All other encodings default to the bus clock (BUSCLK).                                                                                                                              |

| 3:0<br>PS   | Clock Source Prescaler — These four read/write bits select one of nine outputs from the 8-bit prescaler. Changing<br>the prescaler value while the counter is active does not clear the counter. The count continues with the new<br>prescaler value. Reset clears PS to 0000.<br>0000 Encoding 0. MTIM clock source ÷ 1<br>0001 Encoding 1. MTIM clock source ÷ 2<br>0010 Encoding 2. MTIM clock source ÷ 4<br>0011 Encoding 3. MTIM clock source ÷ 8<br>0100 Encoding 4. MTIM clock source ÷ 16<br>0101 Encoding 5. MTIM clock source ÷ 32<br>0110 Encoding 6. MTIM clock source ÷ 64<br>0111 Encoding 7. MTIM clock source ÷ 128<br>1000 Encoding 8. MTIM clock source ÷ 256<br>All other encodings default to MTIM clock source ÷ 256. |

| Field    | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0      | Baud Rate Modulo Divisor — These 13 bits are referred to collectively as BR, and they set the modulo divide                                                                                                             |

| SBR[7:0] | rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = $BUSCLK/(16 \times BR)$ . See also BR bits in Table 14-1. |

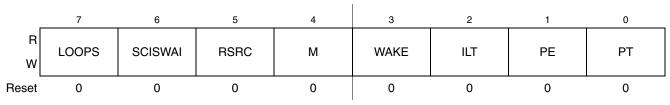

## 14.2.2 SCI Control Register 1 (SCIC1)

This read/write register is used to control various optional features of the SCI system.

Figure 14-7. SCI Control Register 1 (SCIC1)

### Table 14-3. SCIC1 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                 |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                    |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters<br/>start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                      |

| 3<br>WAKE    | <ul> <li>Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.</li> <li>0 Idle-line wakeup.</li> <li>1 Address-mark wakeup.</li> </ul>                                                                                                                                                                                                                                                                                            |

| 2<br>ILT     | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of the logic high level by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit.                                                           |

### 15.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

### 15.1.2 Block Diagrams

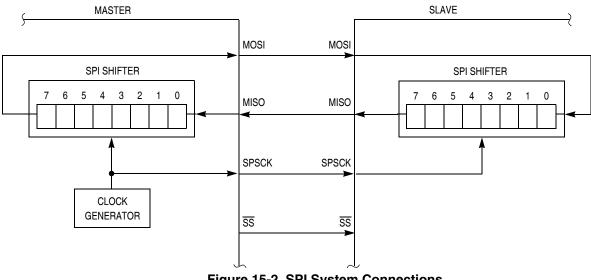

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 15.1.2.1 SPI System Block Diagram

Figure 15-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 15-2. SPI System Connections

### 16.1.3 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

### 16.1.4 Block Diagram

Figure 16-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

#### Timer/Pulse-Width Modulator (S08TPMV2)

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMMODH:TPMMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMCNTH or TPMCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMCNTH or TPMCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

### 16.4.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

### 16.4.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMCnVH:TPMCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

Timer/Pulse-Width Modulator (S08TPMV2)

### 16.5.3 Channel Event Interrupt Description

The meaning of channel interrupts depends on the current mode of the channel (input capture, output compare, edge-aligned PWM, or center-aligned PWM).

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select rising edges, falling edges, any edge, or no edge (off) as the edge that triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the 2-step sequence described in Section 16.5.1, "Clearing Timer Interrupt Flags."

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the 2-step sequence described in Section 16.5.1, "Clearing Timer Interrupt Flags."

### 16.5.4 PWM End-of-Duty-Cycle Events

For channels that are configured for PWM operation, there are two possibilities:

- When the channel is configured for edge-aligned PWM, the channel flag is set when the timer counter matches the channel value register that marks the end of the active duty cycle period.

- When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle, which are the times when the timer counter matches the channel value register.

The flag is cleared by the 2-step sequence described in Section 16.5.1, "Clearing Timer Interrupt Flags."

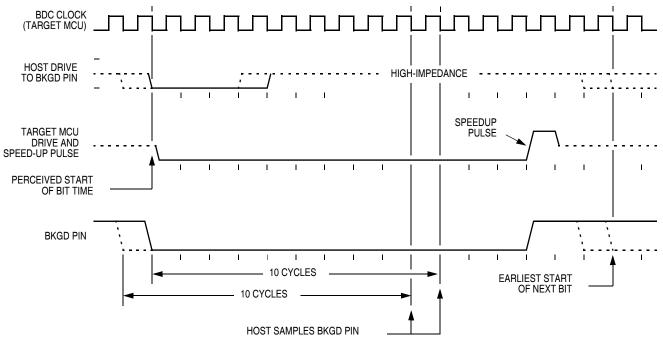

#### Development Support

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

### 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Development Support

# 17.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 17.3.6, "Hardware Breakpoints."

## 17.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

## 17.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

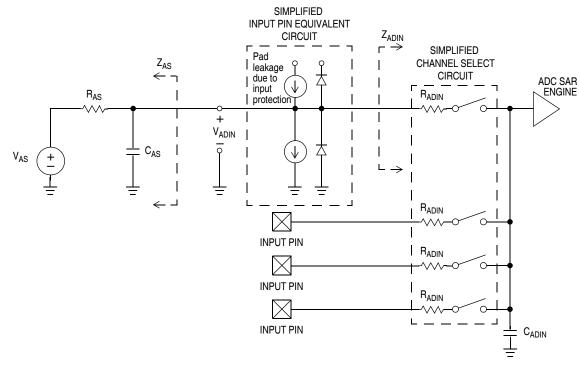

Figure A-17. ADC Input Impedance Equivalency Diagram

| Characteristic                                  | Conditions           | Symb               | Min  | Typ <sup>1</sup> | Max | Unit | Comment                                      |

|-------------------------------------------------|----------------------|--------------------|------|------------------|-----|------|----------------------------------------------|

| Supply current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 120              | _   | μA   |                                              |

| Supply current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 202              | _   | μA   |                                              |

| Supply current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 288              |     | μA   |                                              |

| Supply current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 532              | 646 | μA   |                                              |

| ADC asynchronous                                | High speed (ADLPC=0) | f <sub>ADACK</sub> | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub> |

| clock source                                    | Low power (ADLPC=1)  |                    | 1.25 | 2                | 3.3 |      |                                              |

| Table A-14. 3 Volt 10-bit ADC Characteristics | 3 |

|-----------------------------------------------|---|

|-----------------------------------------------|---|