## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 12                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-VQFN Exposed Pad                                                   |

| Supplier Device Package    | 16-QFN-EP (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg4cffe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MC9S08QG8 Data Sheet

Covers MC9S08QG8 MC9S08QG4

> MC9S08QG8 Rev. 5 11/2009

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2007-2009. All rights reserved.

## **Section Number**

Title

#### Page

|     | 4.5.2    | Program and Erase Times                      | 47 |

|-----|----------|----------------------------------------------|----|

|     | 4.5.3    | Program and Erase Command Execution          | 48 |

|     | 4.5.4    | Burst Program Execution                      | 49 |

|     | 4.5.5    | Access Errors                                | 51 |

|     | 4.5.6    | FLASH Block Protection                       | 51 |

|     | 4.5.7    | Vector Redirection                           | 52 |

| 4.6 | Security | Ι                                            | 52 |

| 4.7 | FLASH    | Registers and Control Bits                   | 54 |

|     | 4.7.1    | FLASH Clock Divider Register (FCDIV)         | 54 |

|     | 4.7.2    | FLASH Options Register (FOPT and NVOPT)      | 55 |

|     | 4.7.3    | FLASH Configuration Register (FCNFG)         | 56 |

|     | 4.7.4    | FLASH Protection Register (FPROT and NVPROT) | 56 |

|     | 4.7.5    | FLASH Status Register (FSTAT)                | 57 |

|     | 4.7.6    | FLASH Command Register (FCMD)                | 58 |

|     |          |                                              |    |

# Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introduc  | ction                                                           | 59 |

|-----|-----------|-----------------------------------------------------------------|----|

| 5.2 | Features  | 5                                                               | 59 |

| 5.3 | MCU R     | eset                                                            | 59 |

| 5.4 | Comput    | er Operating Properly (COP) Watchdog                            | 60 |

| 5.5 |           | ts                                                              |    |

|     | 5.5.1     | Interrupt Stack Frame                                           | 62 |

|     | 5.5.2     | External Interrupt Request Pin (IRQ)                            | 62 |

|     | 5.5.3     | Interrupt Vectors, Sources, and Local Masks                     | 63 |

| 5.6 | Low-Vo    | ltage Detect (LVD) System                                       | 65 |

|     | 5.6.1     | Power-On Reset Operation                                        | 65 |

|     | 5.6.2     | LVD Reset Operation                                             | 65 |

|     | 5.6.3     | LVD Interrupt Operation                                         | 65 |

|     | 5.6.4     | Low-Voltage Warning (LVW)                                       | 65 |

| 5.7 | Real-Ti   | me Interrupt (RTI)                                              | 65 |

| 5.8 | Reset, In | nterrupt, and System Control Registers and Control Bits         | 66 |

|     | 5.8.1     | Interrupt Pin Request Status and Control Register (IRQSC)       | 67 |

|     | 5.8.2     | System Reset Status Register (SRS)                              | 68 |

|     | 5.8.3     | System Background Debug Force Reset Register (SBDFR)            | 69 |

|     | 5.8.4     | System Options Register 1 (SOPT1)                               | 70 |

|     | 5.8.5     | System Options Register 2 (SOPT2)                               | 71 |

|     | 5.8.6     | System Device Identification Register (SDIDH, SDIDL)            | 72 |

|     | 5.8.7     | System Real-Time Interrupt Status and Control Register (SRTISC) | 73 |

|     | 5.8.8     | System Power Management Status and Control 1 Register (SPMSC1)  | 74 |

|     | 5.8.9     | System Power Management Status and Control 2 Register (SPMSC2)  | 75 |

|     | 5.8.10    | System Power Management Status and Control 3 Register (SPMSC3)  | 76 |

|     |           |                                                                 |    |

#### **Section Number**

Title

#### Page

| 17.2.4 BDC Hardware Breakpoint                              |     |

|-------------------------------------------------------------|-----|

| 17.3 On-Chip Debug System (DBG)                             |     |

| 17.3.1 Comparators A and B                                  |     |

| 17.3.2 Bus Capture Information and FIFO Operation           |     |

| 17.3.3 Change-of-Flow Information                           |     |

| 17.3.4 Tag vs. Force Breakpoints and Triggers               |     |

| 17.3.5 Trigger Modes                                        |     |

| 17.3.6 Hardware Breakpoints                                 |     |

| 17.4 Register Definition                                    | 256 |

| 17.4.1 BDC Registers and Control Bits                       |     |

| 17.4.2 System Background Debug Force Reset Register (SBDFR) |     |

| 17.4.3 DBG Registers and Control Bits                       |     |

#### Appendix A Electrical Characteristics

| A.1  | Introduction                                                               |  |

|------|----------------------------------------------------------------------------|--|

| A.2  | Absolute Maximum Ratings                                                   |  |

| A.3  | Thermal Characteristics                                                    |  |

| A.4  | ESD Protection and Latch-Up Immunity                                       |  |

| A.5  | DC Characteristics.                                                        |  |

| A.6  | Supply Current Characteristics                                             |  |

| A.7  | External Oscillator (XOSC) and Internal Clock Source (ICS) Characteristics |  |

| A.8  | AC Characteristics                                                         |  |

|      | A.8.1 Control Timing                                                       |  |

|      | A.8.2 TPM/MTIM Module Timing                                               |  |

|      | A.8.3 SPI Timing                                                           |  |

| A.9  | Analog Comparator (ACMP) Electricals                                       |  |

| A.10 | ADC Characteristics                                                        |  |

| A.11 | FLASH Specifications.                                                      |  |

| A.12 | EMC Performance                                                            |  |

|      | A.12.1 Radiated Emissions                                                  |  |

|      | A.12.2 Conducted Transient Susceptibility                                  |  |

|      |                                                                            |  |

## Appendix B

## **Ordering Information and Mechanical Drawings**

| <b>B</b> .1 | Orderin | g Information           | 289 |

|-------------|---------|-------------------------|-----|

|             | B.1.1   | Device Numbering Scheme | 289 |

| B.2         |         | nical Drawings          |     |

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

| Source<br>Form                                                                                                  | Operation                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR |            |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|------------------|------------|

| FOIII                                                                                                           |                                                                                         | Pdd<br>Md                                           |                                                                                  | S                               | Details                                                  | VH               | INZC       |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry<br>A $\leftarrow$ (A) + (M) + (C)                                        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A9 ii<br>B9 dd<br>C9 hh ll<br>D9 ee ff<br>E9 ff<br>F9<br>9E D9 ee ff<br>9E E9 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ¢¢               | - \$ \$ \$ |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry<br>A $\leftarrow$ (A) + (M)                                           | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB ii<br>BB dd<br>CB hh 11<br>DB ee ff<br>EB ff<br>FB<br>9E DB ee ff<br>9E EB ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ¢¢               | - \$ \$ \$ |

| AIS # <i>opr8i</i>                                                                                              | Add Immediate Value (Signed) to Stack Pointer $SP \leftarrow (SP) + (M)$                | ІММ                                                 | A7 ii                                                                            | 2                               | qq                                                       |                  |            |

| AIX #opr8i                                                                                                      | Add Immediate Value (Signed) to<br>Index Register (H:X)<br>H:X $\leftarrow$ (H:X) + (M) | ІММ                                                 | AF ii                                                                            | 2                               | qq                                                       |                  |            |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND<br>A ← (A) & (M)                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | 0 —              | - ‡ ‡ -    |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL oprx8,SP                                              | Arithmetic Shift Left                                                                   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                    | \$−              | - \$ \$ \$ |

| ASR <i>opr8a</i><br>ASRA<br>ASRX<br>ASR <i>oprx8</i> ,X<br>ASR ,X<br>ASR <i>oprx8</i> ,SP                       | Arithmetic Shift Right                                                                  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwp                     | \$-              | - \$ \$ \$ |

| BCC rel                                                                                                         | Branch if Carry Bit Clear<br>(if C = 0)                                                 | REL                                                 | 24 rr                                                                            | 3                               | qqq                                                      |                  |            |

Table 7-2. . Instruction Set Summary (Sheet 1 of 9)

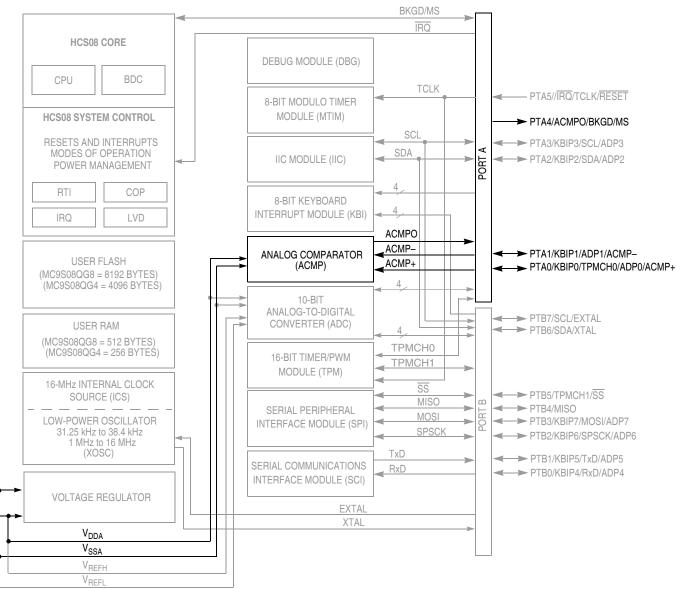

#### Chapter 8 Analog Comparator (S08ACMPV2)

#### NOTES:

V<sub>SS</sub>

$V_{DD}$

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 8-1. MC9S08QG8/4 Block Diagram Highlighting ACMP Block and Pins

## 8.2 External Signal Description

The ACMP has two analog input pins, ACMP+ and ACMP– and one digital output pin ACMPO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 8-2, the ACMP– pin is connected to the inverting input of the comparator, and the ACMP+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 8-2, the ACMPO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 8-1.

| Signal | Function                                                    | I/O |

|--------|-------------------------------------------------------------|-----|

| ACMP-  | Inverting analog input to the ACMP.<br>(Minus input)        | I   |

| ACMP+  | Non-inverting analog input to the ACMP.<br>(Positive input) | I   |

| ACMPO  | Digital output of the ACMP.                                 | 0   |

Table 8-1. Signal Properties

## 8.3 Register Definition

The ACMP includes one register:

• An 8-bit status and control register

Refer to the direct-page register summary in the memory section of this data sheet for the absolute address assignments for all ACMP registers. This section refers to registers and control bits only by their names and relative address offsets.

Some MCUs may have more than one ACMP, so register names include placeholder characters to identify which ACMP is being referenced.

111

Analog Comparator (S08ACMPV2)

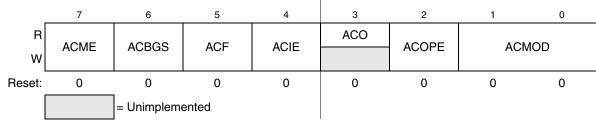

#### 8.3.1 ACMP Status and Control Register (ACMPSC)

ACMPSC contains the status flag and control bits which are used to enable and configure the ACMP.

Figure 8-3. ACMP Status and Control Register

#### Table 8-2. ACMP Status and Control Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACME    | <ul> <li>Analog Comparator Module Enable — ACME enables the ACMP module.</li> <li>0 ACMP not enabled</li> <li>1 ACMP is enabled</li> </ul>                                                                                                                                                                                                                     |

| 6<br>ACBGS   | <ul> <li>Analog Comparator Bandgap Select — ACBGS is used to select between the bandgap reference voltage or the ACMP+ pin as the input to the non-inverting input of the analog comparatorr.</li> <li>0 External pin ACMP+ selected as non-inverting input to comparator</li> <li>1 Internal reference select as non-inverting input to comparator</li> </ul> |

| 5<br>ACF     | <ul> <li>Analog Comparator Flag — ACF is set when a compare event occurs. Compare events are defined by ACMOD.</li> <li>ACF is cleared by writing a one to ACF.</li> <li>0 Compare event has not occurred</li> <li>1 Compare event has occurred</li> </ul>                                                                                                     |

| 4<br>ACIE    | Analog Comparator Interrupt Enable — ACIE enables the interrupt from the ACMP. When ACIE is set, an interrupt will be asserted when ACF is set.<br>0 Interrupt disabled<br>1 Interrupt enabled                                                                                                                                                                 |

| 3<br>ACO     | Analog Comparator Output — Reading ACO will return the current value of the analog comparator output. ACO is reset to a 0 and will read as a 0 when the ACMP is disabled (ACME = 0).                                                                                                                                                                           |

| 2<br>ACOPE   | <ul> <li>Analog Comparator Output Pin Enable — ACOPE is used to enable the comparator output to be placed onto the external pin, ACMPO.</li> <li>0 Analog comparator output not available on ACMPO</li> <li>1 Analog comparator output is driven out on ACMPO</li> </ul>                                                                                       |

| 1:0<br>ACMOD | Analog Comparator Mode — ACMOD selects the type of compare event which sets ACF.<br>00 Encoding 0 — Comparator output falling edge<br>01 Encoding 1 — Comparator output rising edge<br>10 Encoding 2 — Comparator output falling edge<br>11 Encoding 3 — Comparator output rising or falling edge                                                              |

Analog-to-Digital Converter (S08ADC10V1)

Inter-Integrated Circuit (S08IICV1)

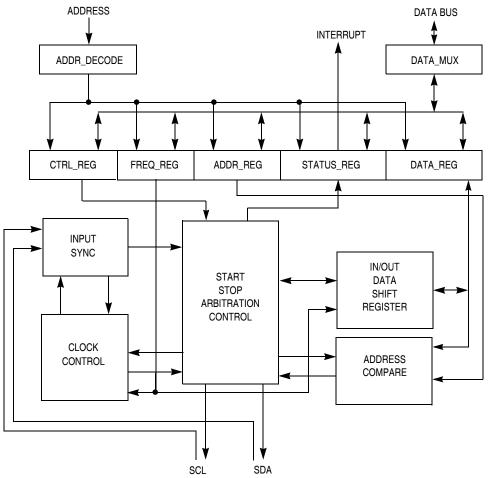

## 11.1.4 Block Diagram

Figure 11-2 is a block diagram of the IIC.

Figure 11-2. IIC Functional Block Diagram

## 11.2 External Signal Description

This section describes each user-accessible pin signal.

### 11.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

#### 11.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

### **11.3 Register Definition**

This section consists of the IIC register descriptions in address order.

Keyboard Interrupts (S08KBIV2)

Modulo Timer (S08MTIMV1)

#### 13.4.1 MTIM Operation Example

This section shows an example of the MTIM operation as the counter reaches a matching value from the modulo register.

| selected<br>clock source |      | nnn  | nnn      | nnn  | JUUU | uuu  |

|--------------------------|------|------|----------|------|------|------|

| MTIM clock<br>(PS=%0010) |      |      | <u> </u> |      |      |      |

| MTIMCNT                  | \$A7 | \$A8 | \$A9     | \$AA | \$00 | \$01 |

| TOF                      |      |      |          |      |      |      |

| MTIMMOD:                 |      |      | \$A      | A    |      |      |

#### Figure 13-8. MTIM counter overflow example

In the example of Figure 13-8, the selected clock source could be any of the five possible choices. The prescaler is set to PS = %0010 or divide-by-4. The modulo value in the MTIMMOD register is set to \$AA. When the counter, MTIMCNT, reaches the modulo value of \$AA, the counter overflows to \$00 and continues counting. The timer overflow flag, TOF, sets when the counter value changes from \$AA to \$00. An MTIM overflow interrupt is generated when TOF is set, if TOIE = 1.

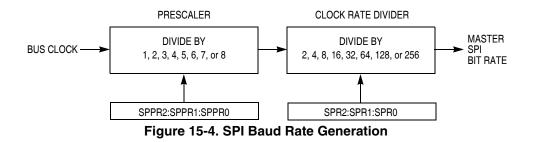

Serial Peripheral Interface (S08SPIV3)

## 15.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

#### 15.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

#### 15.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

### 15.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 15.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

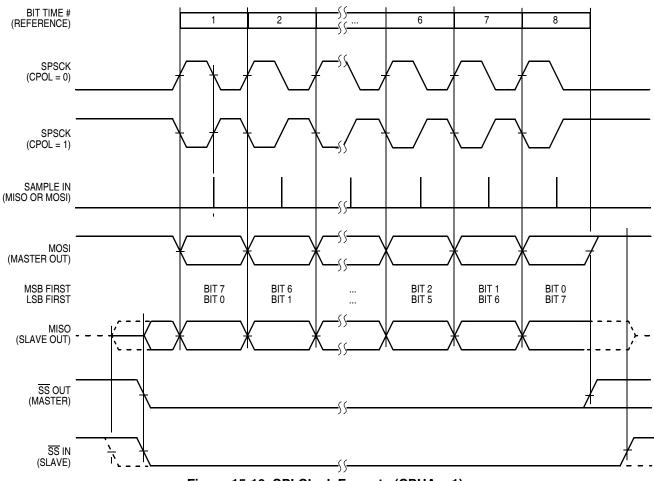

MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 15-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

#### Development Support

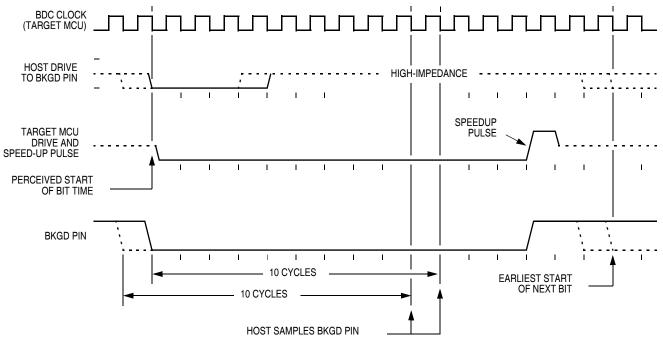

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

#### 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

#### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

| ned reference pulse to determine<br>ommunication speed<br>owledge protocol. Refer to<br>cument order no. HCS08RMv1/D.<br>owledge protocol. Refer to<br>cument order no. HCS08RMv1/D.<br>oackground mode if enabled<br>3DM bit equals 0)<br>atus from BDCSCR<br>ontrols in BDCSCR<br>from target memory<br>and report status<br>from address just read and report<br>to target memory |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cument order no. HCS08RMv1/D.<br>owledge protocol. Refer to<br>cument order no. HCS08RMv1/D.<br>oackground mode if enabled<br>3DM bit equals 0)<br>atus from BDCSCR<br>ontrols in BDCSCR<br>from target memory<br>and report status<br>from address just read and report<br>to target memory                                                                                         |

| cument order no. HCS08RMv1/D.<br>background mode if enabled<br>3DM bit equals 0)<br>atus from BDCSCR<br>from target memory<br>and report status<br>from address just read and report<br>to target memory                                                                                                                                                                             |

| BDM bit equals 0)<br>atus from BDCSCR<br>ontrols in BDCSCR<br>from target memory<br>and report status<br>from address just read and report<br>to target memory                                                                                                                                                                                                                       |

| ontrols in BDCSCR<br>from target memory<br>and report status<br>from address just read and report<br>to target memory                                                                                                                                                                                                                                                                |

| from target memory<br>and report status<br>from address just read and report<br>to target memory                                                                                                                                                                                                                                                                                     |

| and report status<br>from address just read and report<br>to target memory                                                                                                                                                                                                                                                                                                           |

| from address just read and report<br>to target memory                                                                                                                                                                                                                                                                                                                                |

| to target memory                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                      |

| and report status                                                                                                                                                                                                                                                                                                                                                                    |

| KPT breakpoint register                                                                                                                                                                                                                                                                                                                                                              |

| (PT breakpoint register                                                                                                                                                                                                                                                                                                                                                              |

| e the user application program                                                                                                                                                                                                                                                                                                                                                       |

| instruction at the address in the<br>rn to active background mode                                                                                                                                                                                                                                                                                                                    |

| but enable external tagging<br>ces have no external tagging pin)                                                                                                                                                                                                                                                                                                                     |

| ulator (A)                                                                                                                                                                                                                                                                                                                                                                           |

| on code register (CCR)                                                                                                                                                                                                                                                                                                                                                               |

| n counter (PC)                                                                                                                                                                                                                                                                                                                                                                       |

| X register pair (H:X)                                                                                                                                                                                                                                                                                                                                                                |

| ointer (SP)                                                                                                                                                                                                                                                                                                                                                                          |

| X by one then read memory byte<br>X                                                                                                                                                                                                                                                                                                                                                  |

| X by one then read memory byte<br>X. Report status and data.                                                                                                                                                                                                                                                                                                                         |

| ulator (A)                                                                                                                                                                                                                                                                                                                                                                           |

| on code register (CCR)                                                                                                                                                                                                                                                                                                                                                               |

| n counter (PC)                                                                                                                                                                                                                                                                                                                                                                       |

| X register pair (H:X)                                                                                                                                                                                                                                                                                                                                                                |

| ointer (SP)                                                                                                                                                                                                                                                                                                                                                                          |

| X by one, then write memory byte                                                                                                                                                                                                                                                                                                                                                     |

| X by one, then write memory byte<br>X. Also report status.                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 17-1. BDC Command Summary

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

| Parameter                                                                                | Symbol | V <sub>DD</sub> (V) <sup>1</sup> | Typical <sup>2</sup> | Max | T (°C) |

|------------------------------------------------------------------------------------------|--------|----------------------------------|----------------------|-----|--------|

| DTL adder to step1 step2 er step2 4                                                      |        |                                  | 300 nA               | _   | 85     |

| RTI adder to stop1, stop2 or stop3 <sup>4</sup><br>LVD adder to stop3 (LVDE = LVDSE = 1) |        | 2                                | 300 nA               | _   | 85     |

| IVD adder to stop3 (IVDE – IVDSE – 1)                                                    |        | 3                                | 70 μ <b>A</b>        | _   | 85     |

|                                                                                          |        | 2                                | 60 μA                | -   | 85     |

| Adder to stop3 for oscillator enabled <sup>5</sup>                                       | _      | 3                                | 5 μΑ                 | _   | 85     |

| (EREFSTEN =1)                                                                            |        | 2                                | 4 μΑ                 |     | 85     |

#### Table A-7. Supply Current Characteristics

<sup>1</sup> 3-V values are 100% tested; 2-V values are characterized but not tested.

<sup>2</sup> Typicals are measured at 25°C.

<sup>3</sup> Does not include any DC loads on port pins.

- <sup>4</sup> Most customers are expected to find that auto-wakeup from a stop mode can be used instead of the higher current wait mode.

- <sup>5</sup> Values given under the following conditions: low range operation (RANGE = 0), Loss-of-clock disabled (LOCD = 1), low-power oscillator (HGO = 0).

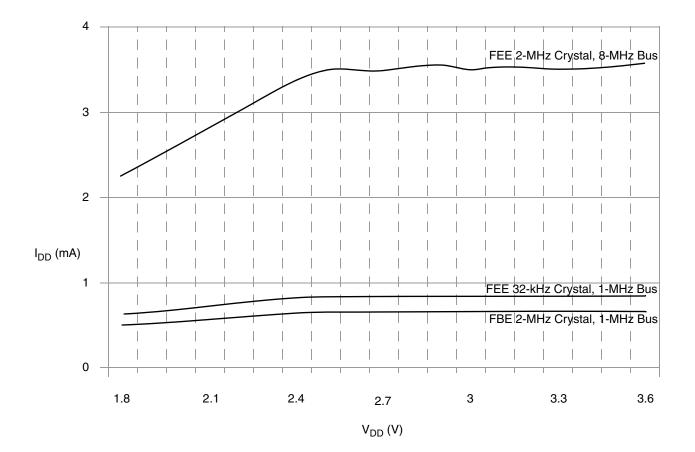

Figure A-6. Typical Run I<sub>DD</sub> for FBE and FEE, I<sub>DD</sub> vs. V<sub>DD</sub> (ACMP and ADC off, All Other Modules Enabled)

## A.11 FLASH Specifications

This section provides details about program/erase times and program-erase endurance for the FLASH memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

| Characteristic                                                                                        | Symbol                  | Min    | Typical     | Max               | Unit              |

|-------------------------------------------------------------------------------------------------------|-------------------------|--------|-------------|-------------------|-------------------|

| Supply voltage for program/erase:                                                                     |                         |        |             |                   |                   |

| T ≤ 85°C                                                                                              | V <sub>prog/erase</sub> | 1.8    | —           | 3.6               | V                 |

| T > 85 °C                                                                                             |                         | 2.1    | _           | 3.6               |                   |

| Supply voltage for read operation                                                                     | V <sub>Read</sub>       | 1.8    | —           | 3.6               | V                 |

| Internal FCLK frequency <sup>1</sup>                                                                  | f <sub>FCLK</sub>       | 150    | —           | 200               | kHz               |

| Internal FCLK period (1/FCLK)                                                                         | t <sub>Fcyc</sub>       | 5      | —           | 6.67              | μs                |

| Byte program time (random location) <sup>(2)</sup>                                                    | t <sub>prog</sub>       |        | 9           | I                 | t <sub>Fcyc</sub> |

| Byte program time (burst mode) <sup>(2)</sup>                                                         | t <sub>Burst</sub>      |        | 4           |                   | t <sub>Fcyc</sub> |

| Page erase time <sup>2</sup>                                                                          | t <sub>Page</sub>       |        | 4000        |                   | t <sub>Fcyc</sub> |

| Mass erase time <sup>(2)</sup>                                                                        | t <sub>Mass</sub>       | 20,000 |             | t <sub>Fcyc</sub> |                   |

| Program/erase endurance <sup>3</sup><br>$T_L$ to $T_H = -40^{\circ}C$ to + 125°C<br>$T = 25^{\circ}C$ | •                       | 10,000 | <br>100,000 |                   | cycles            |

| Data retention <sup>4</sup>                                                                           | t <sub>D_ret</sub>      | 15     | 100         | —                 | years             |

| Table | A-15. | FLASH   | Characteristics |

|-------|-------|---------|-----------------|

| Table | A-13. | I LAUII | onaracteristics |

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance for FLASH** was evaluated for this product family on the 9S12Dx64. For additional information on how Motorola defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory*.

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Motorola defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*

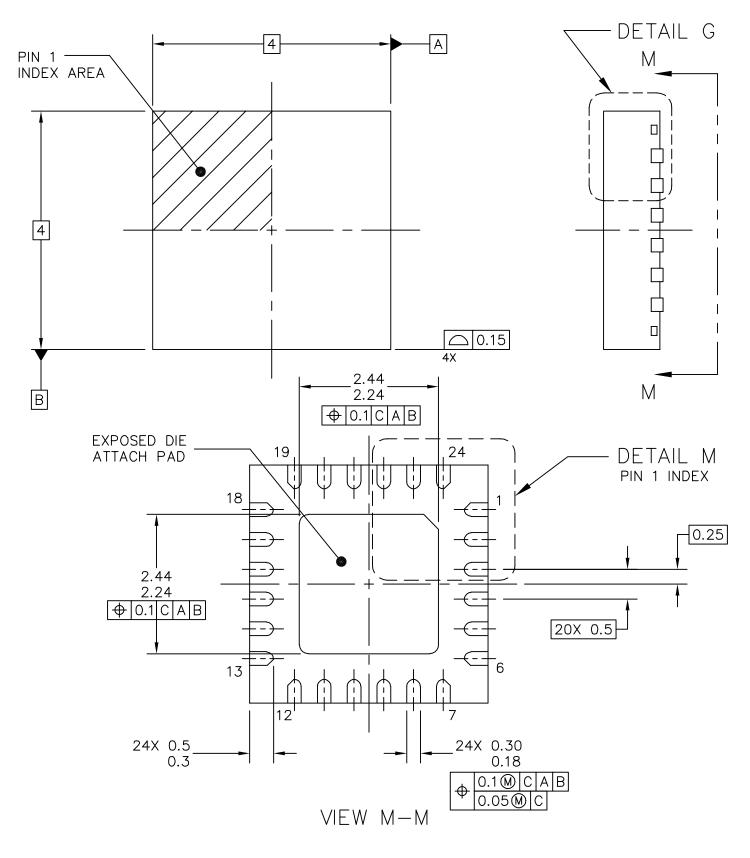

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA                     | LOUTLINE    | PRINT VERSION NO         | T TO SCALE |

|---------------------------------------------------------|-------------------------------|-------------|--------------------------|------------|

| TITLE: THERMALLY ENHANCED                               | QUAD                          | DOCUMENT NO | : 98ARL10605D            | REV: O     |

| FLAT NON-LEADED PACKAGE (QFN)                           |                               | CASE NUMBER | BER: 1897-01 08 SEP 2006 |            |

| 24 TERMINAL, 0.5 PITCH (4                               | STANDARD: JEDEC M0-220 VGGD-8 |             |                          |            |

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED.                                               | MECHANICAL OUTLINE |                                  | PRINT VERSION NOT TO SCALE |             |

|-------------------------------------------------------------------------------------------------------|--------------------|----------------------------------|----------------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>24 TERMINAL, 0.5 PITCH (4 X 4 X 1) |                    | DOCUMENT NO                      | ): 98ARL10605D             | REV: O      |

|                                                                                                       |                    | CASE NUMBER: 1897-01 08 SEP 2004 |                            | 08 SEP 2006 |

|                                                                                                       |                    | STANDARD: JEDEC M0-220 VGGD-8    |                            |             |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- $\triangle$  DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS). STYLE 1:

| PIN | 1. | AC | ΙN   |  |

|-----|----|----|------|--|

|     | 2. | DC | + IN |  |

|     | З. | DC | — IN |  |

|     | 4. | AC | ΙN   |  |

- 5. GROUND

- OUTPUT

AUXILIARY

- 8. VCC

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |  | L OUTLINE           | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|--|---------------------|------------------|-------------|

| TITLE:                                                  |  | DOCUMENT NO         | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               |  | CASE NUMBER: 626-06 |                  | 19 MAY 2005 |

|                                                         |  | STANDARD: NO        | N-JEDEC          |             |