# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-VQFN Exposed Pad                                                    |

| Supplier Device Package    | 16-QFN-EP (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg4cffer |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |

| MC9S08AC16    |                     |                                                 |                                                  |

| MC9S908AC60   |                     |                                                 |                                                  |

| MC9S08AC128   |                     |                                                 |                                                  |

| MC9S08AW60    |                     |                                                 |                                                  |

| MC9S08GB60A   |                     |                                                 |                                                  |

| MC9S08GT16A   |                     |                                                 |                                                  |

| MC9S08JM16    |                     |                                                 |                                                  |

| MC9S08JM60    |                     |                                                 |                                                  |

| MC9S08LL16    |                     |                                                 |                                                  |

| MC9S08QE128   |                     |                                                 |                                                  |

| MC9S08QE32    |                     |                                                 |                                                  |

| MC9S08RG60    |                     |                                                 |                                                  |

| MCF51CN128    |                     |                                                 |                                                  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |

| MC9S08QB8     |                     |                                                 |                                                  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |

| MC9S08QG8     |                     |                                                 |                                                  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program must either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

When using the 8-pin devices, the user must either enable on-chip pullup devices or change the direction of non-bonded out port B pins to outputs so the pins do not float.

### 2.2.5.1 Pin Control Registers

To select drive strength or enable slew rate control or pullup devices, the user writes to the appropriate pin control register located in the high page register block of the memory map. The pin control registers operate independently of the parallel I/O registers and allow control of a port on an individual pin basis.

### 2.2.5.1.1 Internal Pullup Enable

An internal pullup device can be enabled for each port pin by setting the corresponding bit in one of the pullup enable registers (PTxPEn). The pullup device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function, regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function.

The KBI module, when enabled for rising edge detection, causes an enabled internal pull device to be configured as a pulldown.

### 2.2.5.2 Output Slew Rate Control

Slew rate control can be enabled for each port pin by setting the corresponding bit in one of the slew rate control registers (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins that are configured as inputs.

### 2.2.5.3 Output Drive Strength Select

An output pin can be selected to have high output drive strength by setting the corresponding bit in one of the drive strength select registers (PTxDSn). When high drive is selected, a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this, the EMC emissions may be affected by enabling pins as high drive.

Chapter 3 Modes of Operation

| Poriphoral        | Mode  |             |                            |  |  |  |  |

|-------------------|-------|-------------|----------------------------|--|--|--|--|

| Peripheral        | Stop1 | Stop2       | Stop3                      |  |  |  |  |

| MTIM              | Off   | Off         | Standby                    |  |  |  |  |

| SCI               | Off   | Off         | Standby                    |  |  |  |  |

| SPI               | Off   | Off         | Standby                    |  |  |  |  |

| ТРМ               | Off   | Off         | Standby                    |  |  |  |  |

| Voltage Regulator | Off   | Standby     | Standby                    |  |  |  |  |

| XOSC              | Off   | Off         | Optionally On <sup>3</sup> |  |  |  |  |

| I/O Pins          | Hi-Z  | States Held | States Held                |  |  |  |  |

#### Table 3-2. Stop Mode Behavior (continued)

<sup>1</sup> Requires the asynchronous ADC clock and LVD to be enabled, else in standby.

<sup>2</sup> IRCLKEN and IREFSTEN set in ICSC1, else in standby.

<sup>3</sup> ERCLKEN and EREFSTEN set in ICSC2, else in standby. For high frequency range (RANGE in ICSC2 set) requires the LVD to also be enabled in stop3.

| Address                            | Register Name | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

|------------------------------------|---------------|--------|-------|-------|-------|-------|-------|-----|-------|

| 0x00 <b>3F</b>                     | MTIMMOD       |        | MOD   |       |       |       |       |     |       |

| 0x00 <b>40</b>                     | TPMSC         | TOF    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1 | PS0   |

| 0x00 <b>41</b>                     | TPMCNTH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>42</b>                     | TPMCNTL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>43</b>                     | TPMMODH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>44</b>                     | TPMMODL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>45</b>                     | TPMC0SC       | CH0F   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0   | 0     |

| 0x00 <b>46</b>                     | TPMC0VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>47</b>                     | TPMC0VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>48</b>                     | TPMC1SC       | CH1F   | CH1IE | MS1B  | MS1A  | ELS1B | ELS1A | 0   | 0     |

| 0x00 <b>49</b>                     | TPMC1VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>4A</b>                     | TPMC1VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>4B</b> –<br>0x00 <b>5F</b> | Reserved      |        | _     | _     |       |       |       |     | _     |

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| Address           | Register Name | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

|-------------------|---------------|---------|--------|---------|-------|-------|--------|--------|-------|

| 0x1800            | SRS           | POR     | PIN    | COP     | ILOP  | ILAD  | 0      | LVD    | 0     |

| 0x1801            | SBDFR         | 0       | 0      | 0       | 0     | 0     | 0      | 0      | BDFR  |

| 0x1802            | SOPT1         | COPE    | COPT   | STOPE   | _     | 0     | 0      | BKGDPE | RSTPE |

| 0x1803            | SOPT2         | COPCLKS | 0      | 0       | 0     | 0     | 0      | IICPS  | ACIC  |

| 0x <b>1804</b>    | Reserved      | —       | _      | _       | _     | _     | —      | —      | —     |

| 0x1805            | Reserved      | —       | -      | _       | -     | -     | —      | —      | —     |

| 0x1806            | SDIDH         | _       | _      | _       | _     | ID11  | ID10   | ID9    | ID8   |

| 0x1807            | SDIDL         | ID7     | ID6    | ID5     | ID4   | ID3   | ID2    | ID1    | ID0   |

| 0x1808            | SRTISC        | RTIF    | RTIACK | RTICLKS | RTIE  | 0     |        | RTIS   |       |

| 0x1809            | SPMSC1        | LVDF    | LVDACK | LVDIE   | LVDRE | LVDSE | LVDE   | 0      | BGBE  |

| 0x180A            | SPMSC2        | 0       | 0      | 0       | PDF   | PPDF  | PPDACK | PDC    | PPDC  |

| 0x180B            | Reserved      | —       | —      | -       | _     | -     | —      | _      | -     |

| 0x180C            | SPMSC3        | LVWF    | LVWACK | LVDV    | LVWV  | -     | —      | _      | -     |

| 0x180D–<br>0x180F | Reserved      |         |        |         |       |       | _      |        | _     |

| 0x1810            | DBGCAH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1811            | DBGCAL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1812            | DBGCBH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1813            | DBGCBL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1814            | DBGFH         | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1815            | DBGFL         | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

#### Table 4-3. High-Page Register Summary

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

### 4.5.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased.

### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte that is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag, which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized before using any FLASH commands. This must be done only once following a reset.

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.4 System Options Register 1 (SOPT1)

This high page register is a write-once register so only the first write after reset is honored. It can be read at any time. Any subsequent attempt to write to SOPT1 (intentionally or unintentionally) is ignored to avoid accidental changes to these sensitive settings. SOPT1 must be written during the user reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

|        | 7    | 6                           | 5     | 4 <sup>1</sup> | 3 | 2 | 1      | 0                |  |  |  |

|--------|------|-----------------------------|-------|----------------|---|---|--------|------------------|--|--|--|

| R      | COPE | COPT                        | STOPE |                | 0 | 0 | BKGDPE | RSTPE            |  |  |  |

| w      | COPE | COPT                        | SIOPE |                |   |   | DKGDFE | NOIFE            |  |  |  |

| Reset: | 1    | 1                           | 0     | 1              | 0 | 0 | 1      | u <sup>(2)</sup> |  |  |  |

| POR:   | 1    | 1                           | 0     | 1              | 0 | 0 | 1      | 0                |  |  |  |

| LVD:   | 1    | 1                           | 0     | 1              | 0 | 0 | 1      | 0                |  |  |  |

| Γ      |      | = Unimplemented or Reserved |       |                |   |   |        |                  |  |  |  |

Figure 5-5. System Options Register 1 (SOPT1)

<sup>1</sup> Bit 4 is reserved; writes will change the value but will have no effect on this MCU.

<sup>2</sup> u = unaffected

| Table 5-6. SOPT1 Register Field Descriptions | 5 |

|----------------------------------------------|---|

|----------------------------------------------|---|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPE   | <ul> <li>COP Watchdog Enable — This write-once bit selects whether the COP watchdog is enabled.</li> <li>0 COP watchdog timer disabled.</li> <li>1 COP watchdog timer enabled (force reset on timeout).</li> </ul>                                                                                                                                                                                                                                                     |

| 6<br>COPT   | <ul> <li>COP Watchdog Timeout — This write-once bit selects the timeout period of the COP. COPT along with COPCLKS in SOPT2 defines the COP timeout period.</li> <li>0 Short timeout period selected.</li> <li>1 Long timeout period selected.</li> </ul>                                                                                                                                                                                                              |

| 5<br>STOPE  | <ul> <li>Stop Mode Enable — This write-once bit is used to enable stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>O Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul>                                                                                                                                                                                            |

| 1<br>BKGDPE | <ul> <li>Background Debug Mode Pin Enable — This write-once bit when set enables the PTA4/ACMPO/BKGD/MS pin to function as BKGD/MS. When clear, the pin functions as one of its output only alternative functions. This pin defaults to the BKGD/MS function following any MCU reset.</li> <li>0 PTA4/ACMPO/BKGD/MS pin functions as PTA4 or ACMPO.</li> <li>1 PTA4/ACMPO/BKGD/MS pin functions as BKGD/MS.</li> </ul>                                                 |

| 0<br>RSTPE  | RESET Pin Enable — This write-once bit when set enables the PTA5/IRQ/TCLK/RESET pin to function as RESET. When clear, the pin functions as one of its input only alternative functions. This pin defaults to its input-only port function following an MCU POR. When RSTPE is set, an internal pullup device is enabled on RESET.         0       PTA5/IRQ/TCLK/RESET pin functions as PTA5, IRQ, or TCLK.         1       PTA5/IRQ/TCLK/RESET pin functions as RESET. |

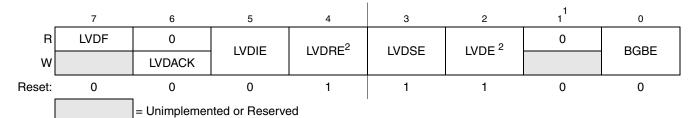

# 5.8.8 System Power Management Status and Control 1 Register (SPMSC1)

This high page register contains status and control bits to support the low voltage detect function and to enable the bandgap voltage reference for use by the ADC module. To configure the low voltage detect trip voltage, see Table 5-14 for the LVDV bit description in SPMSC3.

Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

<sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Table 5-12. SPMSC1 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                           |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                                          |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This write-once bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

| 0<br>BGBE   | <ul> <li>Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels or as a voltage reference for ACMP module.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>          |

Chapter 6 Parallel Input/Output Control

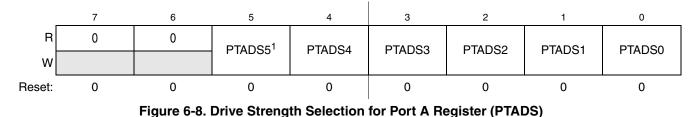

### 6.4.2.3 Port A Drive Strength Select (PTADS)

An output pin can be selected to have high output drive strength by setting the corresponding bit in the drive strength select register (PTADS). When high drive is selected, a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive.

### 6.4.2.4 Port A Drive Strength Select (PTADS)

<sup>1</sup> PTADS5 has no effect on the input-only PTA5 pin.

#### Table 6-5. PTADS Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.3.5 Extended Addressing Mode (EXT)

In extended addressing mode, the full 16-bit address of the operand is located in the next two bytes of program memory after the opcode (high byte first).

### 7.3.6 Indexed Addressing Mode

Indexed addressing mode has seven variations including five that use the 16-bit H:X index register pair and two that use the stack pointer as the base reference.

### 7.3.6.1 Indexed, No Offset (IX)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction.

### 7.3.6.2 Indexed, No Offset with Post Increment (IX+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is only used for MOV and CBEQ instructions.

### 7.3.6.3 Indexed, 8-Bit Offset (IX1)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

### 7.3.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is used only for the CBEQ instruction.

### 7.3.6.5 Indexed, 16-Bit Offset (IX2)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

### 7.3.6.6 SP-Relative, 8-Bit Offset (SP1)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                   | Operation                                                                                                                                                                                                                                                           | Address<br>Mode                                                                                          | Object Code                                                                                  | Cycles                                         | Cyc-by-Cyc<br>Details                                                         | Affect<br>on CCR |         |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------|------------------|---------|--|

| Form                                                                                                             |                                                                                                                                                                                                                                                                     | Ado                                                                                                      | -                                                                                            | S                                              | Details                                                                       | VH               | INZC    |  |

| BRA rel                                                                                                          | Branch Always (if I = 1)                                                                                                                                                                                                                                            | REL                                                                                                      | 20 rr                                                                                        | 3                                              | ppp                                                                           |                  |         |  |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit $n$ in Memory Clear (if (Mn) = 0)                                                                                                                                                                                                                     | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          |                  | \$      |  |

| BRN <i>rel</i>                                                                                                   | Branch Never (if I = 0)                                                                                                                                                                                                                                             | REL                                                                                                      | 21 rr                                                                                        | 3                                              | ppp                                                                           |                  |         |  |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                                                                                                                  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5           | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          |                  | \$      |  |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory (Mn ← 1)                                                                                                                                                                                                                                 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp |                  |         |  |

| BSR rel                                                                                                          | $\begin{array}{l} \text{Branch to Subroutine} \\ \text{PC} \leftarrow (\text{PC}) + \$0002 \\ \text{push (PCL); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{push (PCH); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{PC} \leftarrow (\text{PC}) + rel \end{array}$ | REL                                                                                                      | AD rr                                                                                        | 5                                              | gaggg                                                                         |                  |         |  |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                      | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                                  | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>5<br>5<br>6                          | rpppp<br>pppp<br>pppp<br>rpppp<br>rfppp<br>prpppp                             |                  |         |  |

| CLC                                                                                                              | Clear Carry Bit (C $\leftarrow$ 0)                                                                                                                                                                                                                                  | INH                                                                                                      | 98                                                                                           | 1                                              | р                                                                             |                  | 0       |  |

| CLI                                                                                                              | Clear Interrupt Mask Bit (I ← 0)                                                                                                                                                                                                                                    | INH                                                                                                      | 9A                                                                                           | 1                                              | р                                                                             |                  | 0       |  |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear $M \leftarrow \$00$<br>$A \leftarrow \$00$<br>$X \leftarrow \$00$<br>$H \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$                                                                                                 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F dd<br>4F<br>5F<br>8C<br>6F ff<br>7F<br>9E 6F ff                                           | 5<br>1<br>1<br>5<br>4<br>6                     | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                                    | 0 —              | - 0 1 - |  |

Table 7-2. . Instruction Set Summary (Sheet 3 of 9)

| Bit-Manipulation Branch Read-Modify-Write |                        |                      |                       |                       | Control Register/Memory |                      |                       |                        |              |                      |                      |                      |                      |                      |                     |

|-------------------------------------------|------------------------|----------------------|-----------------------|-----------------------|-------------------------|----------------------|-----------------------|------------------------|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

|                                           |                        |                      | 20 5                  | 40 1                  |                         |                      | 70 4                  |                        |              | 40 0                 | B0 3                 |                      |                      | E0 3                 | F0 3                |

| BRSET0<br>3 DIR                           | BSET0<br>2 DIR         | BRA<br>2 REL         | 30 5<br>NEG<br>2 DIR  | NEGA<br>1 INH         | NEGX                    | 60 5<br>NEG<br>2 IX1 | NEG<br>1 IX           | 80 9<br>RTI<br>1 INH   | BGE<br>2 REL | A0 2<br>SUB<br>2 IMM | SUB<br>2 DIR         | SUB<br>3 EXT         | D0 4<br>SUB<br>3 IX2 | SUB<br>2 IX1         | SUB<br>1 IX         |

| 01 5                                      | 11 5                   | 21 3                 | 31 5                  | 41 4                  | 51 4                    | 61 5                 | 71 5                  | 81 6                   | 91 3         | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                                    | BCLR0                  | BRN                  | CBEQ                  | CBEQA                 | CBEQX                   | CBEQ                 | CBEQ                  | RTS                    | BLT          | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 3 DIR                 | 3 IMM                 | 3 IMM                   | 3 IX1+               | 2 IX+                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5<br>BRSET1<br>3 DIR                   | 12 5<br>BSET1<br>2 DIR | 22 3<br>BHI<br>2 REL | 32 5<br>LDHX<br>3 EXT | 42 5<br>MUL<br>1 INH  | 52 6<br>DIV<br>1 INH    | -                    | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH |              | A2 2<br>SBC<br>2 IMM |                      | C2 4<br>SBC<br>3 EXT | D2 4<br>SBC          | E2 3<br>SBC<br>2 IX1 | F2 3<br>SBC<br>1 IX |

| 03 5<br>BRCLR1<br>3 DIR                   | 13 5<br>BCLR1<br>2 DIR | 23 3<br>BLS<br>2 REL | 33 5<br>COM<br>2 DIR  | 43 1<br>COMA<br>1 INH | 53 1<br>COMX<br>1 INH   | 63 5<br>COM<br>2 IX1 | 73 4<br>COM<br>1 IX   | 83 11<br>SWI<br>1 INH  |              | A3 2<br>CPX<br>2 IMM |                      | C3 4<br>CPX<br>3 EXT |                      | E3 3<br>CPX<br>2 IX1 | F3 3<br>CPX<br>1 IX |

| 04 5<br>BRSET2<br>3 DIR                   | 14 5                   | 24 3<br>BCC<br>2 REL | 34 5<br>LSR<br>2 DIR  | 44 1<br>LSRA<br>1 INH |                         |                      | 74 4<br>LSR<br>1 IX   | 84 1<br>TAP<br>1 INH   |              | A4 2<br>AND          |                      | C4 4<br>AND<br>3 EXT |                      | E4 3<br>AND<br>2 IX1 | F4 3<br>AND<br>1 IX |

| 05 5                                      | 15 5                   | 25 3                 | 35 4                  | 45 3                  | 55 4                    | 65 3                 | 75 5                  | 85 1                   | 95 2         | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                                    | BCLR2                  | BCS                  | STHX                  | LDHX                  | LDHX                    | CPHX                 | CPHX                  | TPA                    | TSX          | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 3 IMM                 | 2 DIR                   | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                                      | 16 5                   | 26 3                 | 36 5                  | 46 1                  | 56 1                    | 66 5                 | 76 4                  | 86 3                   | 96 5         | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                                    | BSET3                  | BNE                  | ROR                   | RORA                  | RORX                    | ROR                  | ROR                   | PULA                   | STHX         | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                                      | 17 5                   | 27 3                 | 37 5                  | 47 1                  | 57 1                    | 67 5                 | 77 4                  | 87 2                   | 97 1         | A7 2                 | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                                    | BCLR3                  | BEQ                  | ASR                   | ASRA                  | ASRX                    | ASR                  | ASR                   | PSHA                   | TAX          | AIS                  | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                                      | 18 5                   | 28 3                 | 38 5                  | 48 1                  | 58 1                    | 68 5                 | 78 4                  | 88 3                   | 98 1         | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                                    | BSET4                  | BHCC                 | LSL                   | LSLA                  | LSLX                    | LSL                  | LSL                   | PULX                   | CLC          | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5                                      | 19 5                   | 29 3                 | 39 5                  | 49 1                  | 59 1                    | 69 5                 | 79 4                  | 89 2                   | 99 1         | A9 2                 |                      | C9 4                 | D9 4                 | E9 3                 | F9 3                |

| BRCLR4                                    | BCLR4                  | BHCS                 | ROL                   | ROLA                  | ROLX                    | ROL                  | ROL                   | PSHX                   | SEC          | ADC                  |                      | ADC                  | ADC                  | ADC                  | ADC                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                |                      | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0A 5                                      | 1A 5                   | 2A 3                 | 3A 5                  | 4A 1                  | 5A 1                    | 6A 5                 | 7A 4                  | 8A 3                   | 9A 1         | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                                    | BSET5                  | BPL                  | DEC                   | DECA                  | DECX                    | DEC                  | DEC                   | PULH                   | CLI          | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                                      | 1B 5                   | 2B 3                 | 3B 7                  | 4B 4                  | 5B 4                    | DBNZ                 | 7B 6                  | 8B 2                   | 9B 1         | AB 2                 | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                                    | BCLR5                  | BMI                  | DBNZ                  | DBNZA                 | DBNZX                   |                      | DBNZ                  | PSHH                   | SEI          | ADD                  | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 3 DIR                 | 2 INH                 | 2 INH                   |                      | 2 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                                      | 1C 5                   | 2C 3                 | 3C 5                  | 4C 1                  | 5C 1                    | 6C 5                 | 7C 4                  | 8C 1                   | 9C 1         |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                                    | BSET6                  | BMC                  | INC                   | INCA                  | INCX                    | INC                  | INC                   | CLRH                   | RSP          |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5<br>BRCLR6<br>3 DIR                   | 1D 5<br>BCLR6<br>2 DIR | 2D 3<br>BMS<br>2 REL | 3D 4<br>TST<br>2 DIR  | 4D 1<br>TSTA<br>1 INH | 5D 1<br>TSTX<br>1 INH   | 6D 4<br>TST<br>2 IX1 | 7D 3<br>TST<br>1 IX   |                        | NOP          | AD 5<br>BSR<br>2 REL | JSR<br>2 DIR         | CD 6<br>JSR<br>3 EXT | DD 6<br>JSR<br>3 IX2 | ED 5<br>JSR<br>2 IX1 | FD 5<br>JSR<br>1 IX |

| 0E 5<br>BRSET7<br>3 DIR                   | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+   | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2 | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                                      | 1F 5                   | 2F 3                 | 3F 5                  | 4F 1                  | 5F 1                    | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1         | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                                    | BCLR7                  | BIH                  | CLR                   | CLRA                  | CLRX                    | CLR                  | CLR                   | WAIT                   | TXA          | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                   | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

#### Table 7-3, Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

Opcode in Hexadecimal F0 3 SUB Instruction Mnemonic 1 IX Addressing Mode Number of Bytes

| Field       | Description                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC17 | <ul> <li>ADC Pin Control 17 — ADPC17 is used to control the pin associated with channel AD17.</li> <li>0 AD17 pin I/O control enabled</li> <li>1 AD17 pin I/O control disabled</li> </ul> |

| 0<br>ADPC16 | <ul> <li>ADC Pin Control 16 — ADPC16 is used to control the pin associated with channel AD16.</li> <li>0 AD16 pin I/O control enabled</li> <li>1 AD16 pin I/O control disabled</li> </ul> |

#### Table 9-11. APCTL3 Register Field Descriptions (continued)

# 9.4 Functional Description

The ADC module is disabled during reset or when the ADCH bits are all high. The module is idle when a conversion has completed and another conversion has not been initiated. When idle, the module is in its lowest power state.

The ADC can perform an analog-to-digital conversion on any of the software selectable channels. The selected channel voltage is converted by a successive approximation algorithm into an 11-bit digital result. In 8-bit mode, the selected channel voltage is converted by a successive approximation algorithm into a 9-bit digital result.

When the conversion is completed, the result is placed in the data registers (ADCRH and ADCRL).In 10-bit mode, the result is rounded to 10 bits and placed in ADCRH and ADCRL. In 8-bit mode, the result is rounded to 8 bits and placed in ADCRL. The conversion complete flag (COCO) is then set and an interrupt is generated if the conversion complete interrupt has been enabled (AIEN = 1).

The ADC module has the capability of automatically comparing the result of a conversion with the contents of its compare registers. The compare function is enabled by setting the ACFE bit and operates in conjunction with any of the conversion modes and configurations.

### 9.4.1 Clock Select and Divide Control

One of four clock sources can be selected as the clock source for the ADC module. This clock source is then divided by a configurable value to generate the input clock to the converter (ADCK). The clock is selected from one of the following sources by means of the ADICLK bits.

- The bus clock, which is equal to the frequency at which software is executed. This is the default selection following reset.

- The bus clock divided by 2. For higher bus clock rates, this allows a maximum divide by 16 of the bus clock.

- ALTCLK, as defined for this MCU (See module section introduction).

- The asynchronous clock (ADACK) This clock is generated from a clock source within the ADC module. When selected as the clock source this clock remains active while the MCU is in wait or stop3 mode and allows conversions in these modes for lower noise operation.

Whichever clock is selected, its frequency must fall within the specified frequency range for ADCK. If the available clocks are too slow, the ADC will not perform according to specifications. If the available clocks

## 10.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

### 10.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

### 10.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN is set and the ERCLKEN bit is written to 1, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

# 10.4.7 Fixed Frequency Clock

The ICS provides the divided FLL reference clock as ICSFFCLK for use as an additional clock source for peripheral modules. The ICS provides an output signal (ICSFFE) which indicates when the ICS is providing ICSOUT frequencies four times or greater than the divided FLL reference clock (ICSFFCLK). In FLL engaged mode (FEI and FEE), this is always true and ICSFFE is always high. In ICS Bypass modes, ICSFFE will get asserted for the following combinations of BDIV and RDIV values:

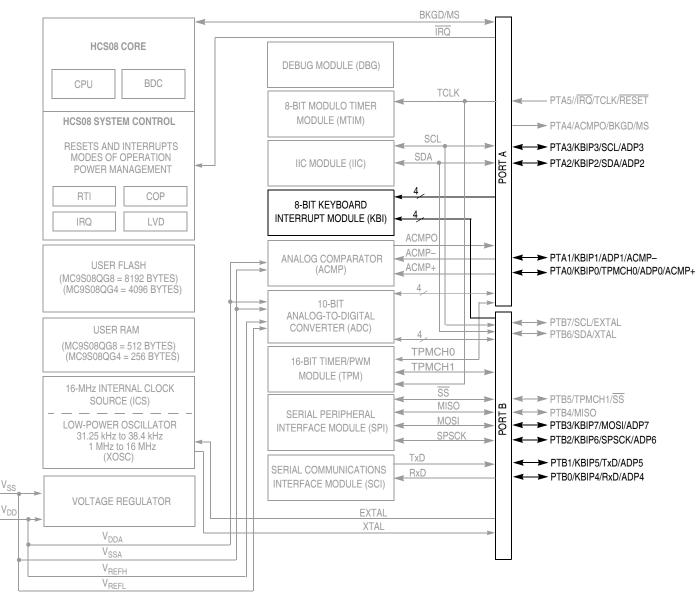

#### Chapter 12 Keyboard Interrupt (S08KBIV2)

#### NOTES:

- <sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 12-1. MC9S08QG8/4 Block Diagram Highlighting KBI Block and Pins

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

Keyboard Interrupts (S08KBIV2)

### 13.1.2 Features

Timer system features include:

- 8-bit up-counter

- Free-running or 8-bit modulo limit

- Software controllable interrupt on overflow

- Counter reset bit (TRST)

- Counter stop bit (TSTP)

- Four software selectable clock sources for input to prescaler:

- System bus clock rising edge

- Fixed frequency clock (XCLK) rising edge

- External clock source on the TCLK pin rising edge

- External clock source on the TCLK pin falling edge

- Nine selectable clock prescale values:

- Clock source divide by 1, 2, 4, 8, 16, 32, 64, 128, or 256

### 13.1.3 Modes of Operation

This section defines the MTIM's operation in stop, wait and background debug modes.

### 13.1.3.1 MTIM in Wait Mode

The MTIM continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the MTIM can be used to bring the MCU out of wait mode if the timer overflow interrupt is enabled. For lowest possible current consumption, the MTIM should be stopped by software if not needed as an interrupt source during wait mode.

### 13.1.3.2 MTIM in Stop Modes

The MTIM is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the MTIM cannot be used as a wake up source from stop modes.

Waking from stop1 and stop2 modes, the MTIM will be put into its reset state. If stop3 is exited with a reset, the MTIM will be put into its reset state. If stop3 is exited with an interrupt, the MTIM continues from the state it was in when stop3 was entered. If the counter was active upon entering stop3, the count will resume from the current value.

### 13.1.3.3 MTIM in Active Background Mode

The MTIM suspends all counting until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as an MTIM reset did not occur (TRST written to a 1 or MTIMMOD written).

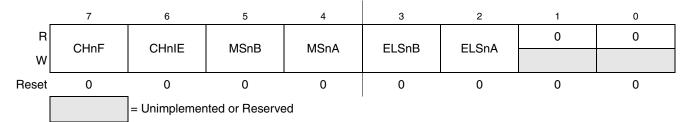

### 16.3.4 Timer Channel n Status and Control Register (TPMCnSC)

TPMCnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

#### Figure 16-8. Timer Channel n Status and Control Register (TPMCnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | <ul> <li>Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.</li> <li>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.</li> <li>No input capture or output compare event occurred on channel n</li> </ul> |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>0 Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 16-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 16-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 16-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin.                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 16-4. TPMCnSC Register Field Descriptions

**Development Support**

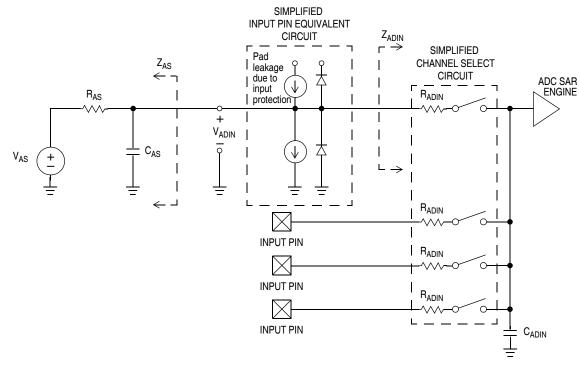

Figure A-17. ADC Input Impedance Equivalency Diagram

| Characteristic                                  | Conditions           | Symb               | Min  | Typ <sup>1</sup> | Max | Unit | Comment              |

|-------------------------------------------------|----------------------|--------------------|------|------------------|-----|------|----------------------|

| Supply current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 120              | _   | μA   |                      |

| Supply current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 202              | _   | μA   |                      |

| Supply current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 288              |     | μA   |                      |

| Supply current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDAD</sub>  | _    | 532              | 646 | μA   |                      |

| ADC asynchronous                                | High speed (ADLPC=0) | f <sub>ADACK</sub> | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> = |

| clock source                                    | Low power (ADLPC=1)  |                    | 1.25 | 2                | 3.3 |      | 1/f <sub>ADACK</sub> |

| Table A-14. 3 Volt 10-bit ADC Characteristics | 3 |

|-----------------------------------------------|---|

|-----------------------------------------------|---|

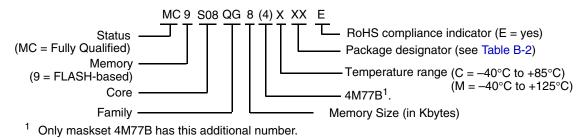

# Appendix B Ordering Information and Mechanical Drawings

# B.1 Ordering Information

This section contains ordering information for MC9S08QG8 and MC9S08QG4 devices.

| Device Number <sup>1</sup> | Men   | nory | Available Packages <sup>2</sup> |                               |                              |  |

|----------------------------|-------|------|---------------------------------|-------------------------------|------------------------------|--|

| Device Nulliber            | FLASH | RAM  | 24-Pin                          | 16-Pin                        | 8-Pin                        |  |

| MC9S08QG8                  | 8K    | 512  | 24 QFN                          | 16 PDIP<br>16 QFN<br>16 TSSOP | 8 DFN<br>8 NB SOIC           |  |

| MC9S08QG4                  | 4K    | 256  | 24 QFN                          | 16 QFN<br>16 TSSOP            | 8 DFN<br>8 PDIP<br>8 NB SOIC |  |

Table B-1. Device Numbering System

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-2 for package information.

# B.1.1 Device Numbering Scheme

# **B.2** Mechanical Drawings

The following pages are mechanical specifications for MC9S08QG8/4 package options. See Table B-2 for the document number for each package type.

| Pin Count | Туре  | Designator | Document No. |  |  |

|-----------|-------|------------|--------------|--|--|

| 24        | QFN   | FK         | 98ARL10605D  |  |  |

| 16        | PDIP  | PB         | 98ASB42431B  |  |  |

| 16        | QFN   | FF         | 98ARE10614D  |  |  |

| 16        | TSSOP | DT         | 98ASH70247A  |  |  |

#### Table B-2. Package Information

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5