# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 20MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 4                                                          |

| Program Memory Size        | 4KB (4K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 256 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | A/D 4x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                     |

| Supplier Device Package    | 8-PDIP                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qg4mpae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

Title

### Page

| 11.4 | Functional Description                 |  |

|------|----------------------------------------|--|

|      | 11.4.1 IIC Protocol                    |  |

| 11.5 | Resets                                 |  |

| 11.6 | Interrupts                             |  |

|      | 11.6.1 Byte Transfer Interrupt         |  |

|      | 11.6.2 Address Detect Interrupt        |  |

|      | 11.6.3 Arbitration Lost Interrupt      |  |

| 11.7 | Initialization/Application Information |  |

# Chapter 12 Keyboard Interrupt (S08KBIV2)

| 12.1 | Introduction                                   | 173 |

|------|------------------------------------------------|-----|

|      | 12.1.1 Features                                | 175 |

|      | 12.1.2 Modes of Operation                      | 175 |

|      | 12.1.3 Block Diagram                           | 175 |

| 12.2 | External Signal Description                    | 176 |

| 12.3 | Register Definition                            | 176 |

|      | 12.3.1 KBI Status and Control Register (KBISC) | 176 |

|      | 12.3.2 KBI Pin Enable Register (KBIPE)         | 177 |

|      | 12.3.3 KBI Edge Select Register (KBIES)        | 177 |

| 12.4 | Functional Description                         | 178 |

|      | 12.4.1 Edge Only Sensitivity                   | 178 |

|      | 12.4.2 Edge and Level Sensitivity              | 178 |

|      | 12.4.3 KBI Pullup/Pulldown Resistors           |     |

|      | 12.4.4 KBI Initialization                      | 179 |

|      |                                                |     |

# Chapter 13 Modulo Timer (S08MTIMV1)

| Introduction                                       |                                                              |

|----------------------------------------------------|--------------------------------------------------------------|

| 13.1.1 MTIM/TPM Configuration Information          |                                                              |

| 13.1.2 Features                                    |                                                              |

| 13.1.3 Modes of Operation                          |                                                              |

| 13.1.4 Block Diagram                               |                                                              |

| External Signal Description                        |                                                              |

| Register Definition                                |                                                              |

| 13.3.1 MTIM Status and Control Register (MTIMSC)   |                                                              |

| 13.3.2 MTIM Clock Configuration Register (MTIMCLK) |                                                              |

| 13.3.3 MTIM Counter Register (MTIMCNT)             |                                                              |

| 13.3.4 MTIM Modulo Register (MTIMMOD)              |                                                              |

| Functional Description                             |                                                              |

| 13.4.1 MTIM Operation Example                      | 190                                                          |

|                                                    | <ul> <li>13.1.1 MTIM/TPM Configuration Information</li></ul> |

# **Chapter 1 Device Overview**

#### 1.1 Introduction

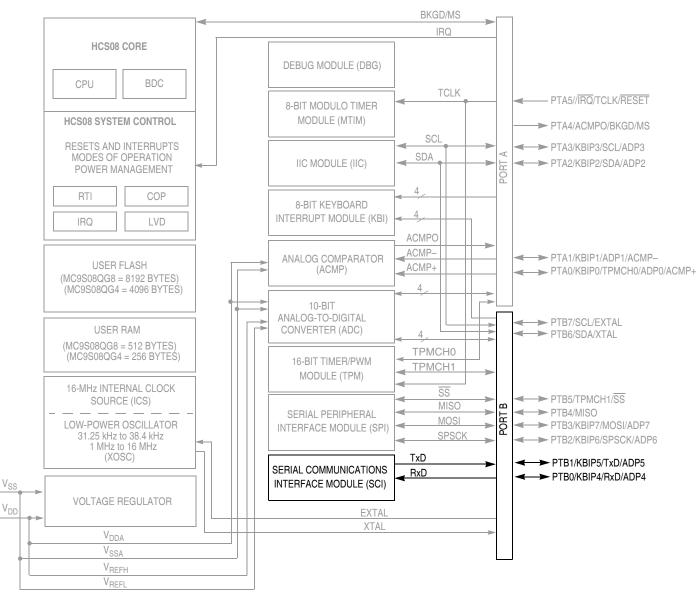

The MC9S08QG8 is a member of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types. Refer to Table 1-1 for features associated with each device in this series.

#### 1.1.1 Devices in the MC9S08QG8/4 Series

Table 1-1 summarizes the features available in the MC9S08QG8/4 series of MCUs.

|                  | Device                                                                          |                               |                                                                                                           |           |                                         |                                         |                                        |  |

|------------------|---------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------------------------|----------------------------------------|--|

| Feature          |                                                                                 | MC9S08QG                      | 8                                                                                                         | MC9S08QG4 |                                         |                                         |                                        |  |

| Package          | 24-Pin 16-Pin 8-Pin                                                             |                               |                                                                                                           | 24-Pin    | 16-Pin                                  | 8-Pin                                   |                                        |  |

| FLASH            |                                                                                 | 8K                            |                                                                                                           |           | 4K                                      |                                         |                                        |  |

| RAM              |                                                                                 | 512                           |                                                                                                           |           | 256                                     |                                         |                                        |  |

| XOSC             | yes                                                                             | yes                           | no                                                                                                        | yes       | yes                                     | no                                      |                                        |  |

| ICS              |                                                                                 | yes                           |                                                                                                           |           | yes                                     |                                         |                                        |  |

| ACMP             |                                                                                 | yes                           |                                                                                                           |           | yes                                     |                                         |                                        |  |

| ADC              | 8-ch                                                                            | 8-ch                          | 4-ch                                                                                                      | 8-ch      | 8-ch                                    | 4-ch                                    |                                        |  |

| DBG              |                                                                                 | yes                           |                                                                                                           | yes       | yes                                     | yes                                     |                                        |  |

| IIC              |                                                                                 | yes                           |                                                                                                           | yes       |                                         |                                         |                                        |  |

| IRQ              |                                                                                 | yes                           |                                                                                                           | yes       |                                         |                                         |                                        |  |

| KBI              | 8-pin 8-pin                                                                     |                               | 4-pin                                                                                                     | 8-pin     | 8-pin                                   | 4-pin                                   |                                        |  |

| MTIM             |                                                                                 | yes                           |                                                                                                           | yes       |                                         |                                         |                                        |  |

| SCI              | yes                                                                             | yes                           | no                                                                                                        | yes       | yes                                     | no                                      |                                        |  |

| SPI              | yes                                                                             | yes                           | no                                                                                                        | yes       | yes                                     | no                                      |                                        |  |

| TPM              | 2-ch                                                                            | 2-ch                          | 1-ch                                                                                                      | 2-ch      | 2-ch                                    | 1-ch                                    |                                        |  |

| I/O pins         | 12 I/O 12 I/O<br>1 Output 1 Output only<br>only 1 Input only<br>1 Input<br>only |                               | pins 1 Output 1 Output only 1 Output only 1 Output<br>only 1 Input only 1 Input only 1 Input only 1 Input |           | 12 I/O<br>1 Output only<br>1 Input only | 12 I/O<br>1 Output only<br>1 Input only | 4 I/O<br>1 Output only<br>1 Input only |  |

| Package<br>Types | 24 QFN                                                                          | 16 PDIP<br>16 QFN<br>16 TSSOP | 8 DFN<br>8 SOIC                                                                                           | 24 QFN    | 16 QFN<br>16 TSSOP                      | 8 DFN<br>8 PDIP<br>8 SOIC               |                                        |  |

Table 1-1. Devices in the MC9S08QG8/4 Series

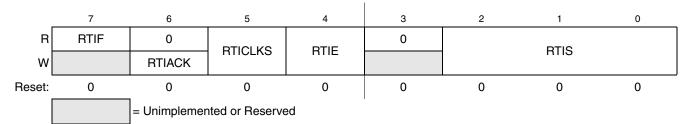

# 5.8.7 System Real-Time Interrupt Status and Control Register (SRTISC)

This high page register contains status and control bits for the RTI.

### Figure 5-9. System RTI Status and Control Register (SRTISC)

### Table 5-10. SRTISC Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF    | <ul> <li>Real-Time Interrupt Flag — This read-only status bit indicates the periodic wakeup timer has timed out.</li> <li>0 Periodic wakeup timer not timed out.</li> <li>1 Periodic wakeup timer timed out.</li> </ul>                                                                   |

| 6<br>RTIACK  | <b>Real-Time Interrupt Acknowledge</b> — This write-only bit is used to acknowledge real-time interrupt request (write 1 to clear RTIF). Writing 0 has no meaning or effect. Reads always return 0.                                                                                       |

| 5<br>RTICLKS | <ul> <li>Real-Time Interrupt Clock Select — This read/write bit selects the clock source for the real-time interrupt.</li> <li>0 Real-time interrupt request clock source is internal 1-kHz oscillator.</li> <li>1 Real-time interrupt request clock source is external clock.</li> </ul> |

| 4<br>RTIE    | Real-Time Interrupt Enable — This read-write bit enables real-time interrupts.         0 Real-time interrupts disabled.         1 Real-time interrupts enabled.                                                                                                                           |

| 2:0<br>RTIS  | <b>Real-Time Interrupt Delay Selects</b> — These read/write bits select the period for the RTI. See Table 5-11.                                                                                                                                                                           |

### Table 5-11. Real-Time Interrupt Period

| RTIS2:RTIS1:RTIS0 | Using Internal 1-kHz Clock Source <sup>1 2</sup> | Using External Clock Source<br>Period = t <sub>ext</sub> <sup>3</sup> |

|-------------------|--------------------------------------------------|-----------------------------------------------------------------------|

| 0:0:0             | Disable RTI                                      | Disable RTI                                                           |

| 0:0:1             | 8 ms                                             | t <sub>ext</sub> x 256                                                |

| 0:1:0             | 32 ms                                            | t <sub>ext</sub> x 1024                                               |

| 0:1:1             | 64 ms                                            | t <sub>ext</sub> x 2048                                               |

| 1:0:0             | 128 ms                                           | t <sub>ext</sub> x 4096                                               |

| 1:0:1             | 256 ms                                           | t <sub>ext</sub> x 8192                                               |

| 1:1:0             | 512 ms                                           | t <sub>ext</sub> x 16384                                              |

| 1:1:1             | 1.024 s                                          | t <sub>ext</sub> x 32768                                              |

<sup>1</sup> Values are shown in this column based on t<sub>RTI</sub> = 1 ms. See t<sub>RTI</sub> in the appendix Section A.8.1, "Control Timing," for the tolerance of this value.

<sup>2</sup> The initial RTI timeout period will be up to one 1-kHz clock period less than the time specified.

<sup>3</sup> t<sub>ext</sub> is the period of the external crystal frequency.

Chapter 6 Parallel Input/Output Control

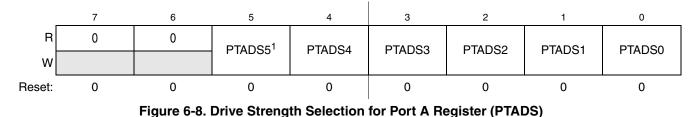

### 6.4.2.3 Port A Drive Strength Select (PTADS)

An output pin can be selected to have high output drive strength by setting the corresponding bit in the drive strength select register (PTADS). When high drive is selected, a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive.

### 6.4.2.4 Port A Drive Strength Select (PTADS)

<sup>1</sup> PTADS5 has no effect on the input-only PTA5 pin.

### Table 6-5. PTADS Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

### 9.1.1.3 Alternate Clock

The ADC is capable of performing conversions using the MCU bus clock, the bus clock divided by two, or the local asynchronous clock (ADACK) within the module. The alternate clock, ALTCLK, input for the MC9S08QG8/4 MCU devices is not implemented.

### 9.1.1.4 Hardware Trigger

The ADC hardware trigger, ADHWT, is output from the real-time interrupt (RTI) counter. The RTI counter can be clocked by either ICSERCLK or a nominal 1-kHz clock source within the RTI block.

The period of the RTI is determined by the input clock frequency and the RTIS bits. The RTI counter is a free running counter that generates an overflow at the RTI rate determined by the RTIS bits. When the ADC hardware trigger is enabled, a conversion is initiated upon an RTI counter overflow.

The RTI can be configured to cause a hardware trigger in MCU run, wait, and stop3.

### 9.1.1.5 Analog Pin Enables

The ADC on MC9S08QG8 devices contains only one analog pin enable register, APCTL1.

### 9.1.1.6 Temperature Sensor

The ADC module includes a temperature sensor whose output is connected to one of the ADC analog channel inputs. Equation 9-1 provides an approximate transfer function of the temperature sensor.

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- V<sub>TEMP25</sub> is the voltage of the temperature sensor channel at 25°C.

— m is the hot or cold voltage versus temperature slope in  $V/^{\circ}C$ .

For temperature calculations, use the V<sub>TEMP25</sub> and m values from Section A.10, "ADC Characteristics," in Appendix A, "Electrical Characteristics."

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$ , the cold slope value is applied in Equation 9-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 9-1.

### 9.1.1.7 Low-Power Mode Operation

The ADC is capable of running in stop3 mode but requires LVDSE and LVDE in SPMSC1 to be set.

Analog-to-Digital Converter (S08ADC10V1)

### 9.4.4.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADCRH and ADCRL. This is indicated by the setting of COCO. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADCRH and ADCRL if the previous data is in the process of being read while in 10-bit MODE (the ADCRH register has been read but the ADCRL register has not). When blocking is active, the data transfer is blocked, COCO is not set, and the new result is lost. In the case of single conversions with the compare function enabled and the compare condition false, blocking has no effect and ADC operation is terminated. In all other cases of operation, when a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled).

If single conversions are enabled, the blocking mechanism could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

### 9.4.4.3 Aborting Conversions

Any conversion in progress will be aborted when:

- A write to ADCSC1 occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCSC2, ADCCFG, ADCCVH, or ADCCVL occurs. This indicates a mode of operation change has occurred and the current conversion is therefore invalid.

- The MCU is reset.

- The MCU enters stop mode with ADACK not enabled.

When a conversion is aborted, the contents of the data registers, ADCRH and ADCRL, are not altered but continue to be the values transferred after the completion of the last successful conversion. In the case that the conversion was aborted by a reset, ADCRH and ADCRL return to their reset states.

### 9.4.4.4 Power Control

The ADC module remains in its idle state until a conversion is initiated. If ADACK is selected as the conversion clock source, the ADACK clock generator is also enabled.

Power consumption when active can be reduced by setting ADLPC. This results in a lower maximum value for  $f_{ADCK}$  (see the electrical specifications).

# 9.4.4.5 Total Conversion Time

The total conversion time depends on the sample time (as determined by ADLSMP), the MCU bus frequency, the conversion mode (8-bit or 10-bit), and the frequency of the conversion clock ( $f_{ADCK}$ ). After the module becomes active, sampling of the input begins. ADLSMP is used to select between short and long sample times. When sampling is complete, the converter is isolated from the input channel and a successive approximation algorithm is performed to determine the digital value of the analog signal. The

# 9.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

### 9.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source (R<sub>AS</sub>) is kept below 5 kΩ.

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

### 9.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit mode or 10 in 10-bit mode).

### 9.6.2.3 Noise-Induced Errors

System noise which occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>REFH</sub> to V<sub>REFL</sub>.

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- If inductive isolation is used from the primary supply, an additional 1  $\mu$ F capacitor is placed from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- $V_{SSAD}$  (and  $V_{REFL}$ , if connected) is connected to  $V_{SS}$  at a quiet point in the ground plane.

- Operate the MCU in wait or stop3 mode before initiating (hardware triggered conversions) or immediately after initiating (hardware or software triggered conversions) the ADC conversion.

- For software triggered conversions, immediately follow the write to the ADCSC1 with a WAIT instruction or STOP instruction.

- For stop3 mode operation, select ADACK as the clock source. Operation in stop3 reduces  $V_{DD}$  noise but increases effective conversion time due to stop recovery.

- There is no I/O switching, input or output, on the MCU during the conversion.

There are some situations where external system activity causes radiated or conducted noise emissions or excessive  $V_{DD}$  noise is coupled into the ADC. In these situations, or when the MCU cannot be placed in wait or stop3 or I/O activity cannot be halted, these recommended actions may reduce the effect of noise on the accuracy:

• Place a 0.01  $\mu$ F capacitor (C<sub>AS</sub>) on the selected input channel to V<sub>REFL</sub> or V<sub>SSAD</sub> (this will improve noise issues but will affect sample rate based on the external analog source resistance).

#### Chapter 11 Inter-Integrated Circuit (S08IICV1)

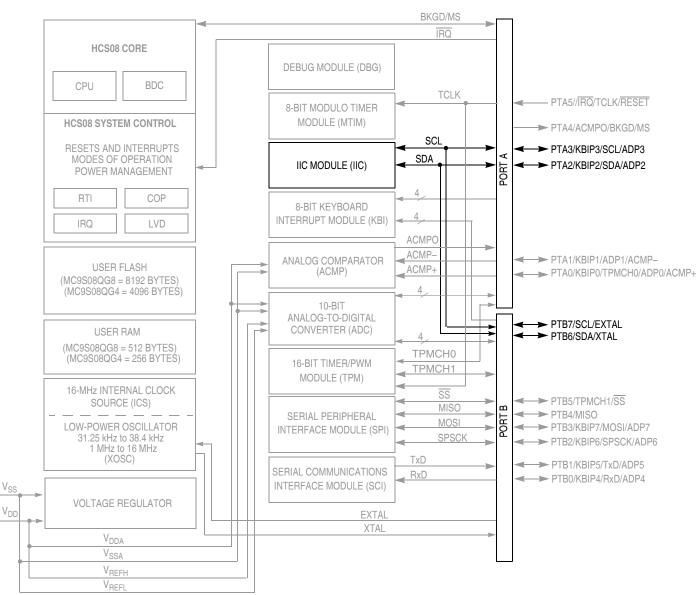

#### NOTES:

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

### Figure 11-1. MC9S08QG8/4 Block Diagram Highlighting IIC Block and Pins

Inter-Integrated Circuit (S08IICV1)

### 11.4.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 11-8, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 11.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 11-8).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

### 11.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 11-8. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

#### Chapter 14 Serial Communications Interface (S08SCIV3)

#### NOTES:

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup/pulldown device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

### Figure 14-1. MC9S08QG8/4 Block Diagram Highlighting SCI Block and Pins

|                              |                       |              |              | Mod                                              | ule Initiali           | zation:                     |               |                             |                |

|------------------------------|-----------------------|--------------|--------------|--------------------------------------------------|------------------------|-----------------------------|---------------|-----------------------------|----------------|

| Write:                       | SCIE                  | BDH:SCIBD    | L to s       | et                                               | ba                     | ud rate                     |               |                             |                |

| Write:                       | SCFC1                 |              | to c         | onfigure                                         | 1-v                    | vire/2-wire, 9              | 9/8-bit data, | wakeup, an                  | d parity, if u |

| Write;                       | SCIC                  | 2            | to c         | onfigure                                         |                        | errupts, ena<br>able Rx wak |               | Tx, RWU<br>ends break       | character      |

| Write:                       | SCIC                  | 3            | to e         | enable                                           |                        |                             |               | Also contro<br>only used in |                |

|                              |                       |              |              |                                                  | Module Us              | e:                          |               |                             |                |

| Wait for RI                  | DRF, thei<br>umber of | application  | from SCID    |                                                  | age automat            | ic receiver v               | vakeup, SBł   | K to send br                | eak charac     |

| S                            | CIBDH                 |              |              | 1                                                | SBR12                  | SBR11                       | SBR10         | SBR9                        | SBR8           |

| S                            | CIBDL                 | SBR7         | SBR6         | SBR5                                             | SBR4                   | SBR3                        | SBR2          | SBR1                        | SBR0           |

|                              |                       | Baud rate    | = BUSCLK     | / (16 x SBR                                      | 12:SBR0)               |                             |               |                             | ·              |

| 5                            | SCIC1                 | LOOPS        | SCISWAI      | RSRC                                             | М                      | WAKE                        | ILT           | PE                          | PT             |

|                              |                       | Module co    | onfiguration |                                                  |                        |                             |               |                             |                |

| S                            | SCIC2                 | TIE          | TCIE         | RIE                                              | ILIE                   | TE                          | RE            | RWU                         | SBK            |

| Local interrupt enables Tx a |                       |              |              | s Tx and Rx                                      | ( enable               |                             |               | Rx wakeup                   | and send b     |

| S                            | SCIS1                 | TDRE         | тс           | RDRF                                             | IDLE                   | OR                          | NF            | FE                          | PF             |

|                              |                       | Interrupt fl | ags          | 1                                                | •                      | Rx error                    | flags         | •                           | ·              |

| S                            | SCIS2                 |              |              | l<br>I                                           | 1                      |                             | BRK13         |                             | RAF            |

|                              |                       | Configure    | LIN suppor   | t options an                                     | d monitor re           | ceiver activi               | ty            |                             |                |

| S                            | SCIS3                 | R8           | T8           | TXDIR                                            | TXINV                  | ORIE                        | NEIE          | FEIE                        | PEIE           |

|                              |                       | 9th data b   |              | Rx/Tx pin<br>direction in<br>single-wire<br>mode | Tx data pa<br>polarity |                             | errupt enable | es                          |                |

|                              |                       |              |              |                                                  |                        |                             |               |                             | 1              |

| S                            | CIID                  | R7/T7        | R6/T6        | R5/T5                                            | R4/T4                  | R3/T3                       | R2/T2         | R1/T1                       | R0/T0          |

Figure 14-2. SCI Module Quick Start

### 14.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character

- Selectable transmitter output polarity

### 14.1.2 Modes of Operation

See Section 14.3, "Functional Description," for a detailed description of SCI operation in the different modes.

- 8- and 9- bit data modes

- Stop modes SCI is halted during all stop modes

- Loop mode

- Single-wire mode

### 15.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

### 15.1.2 Block Diagrams

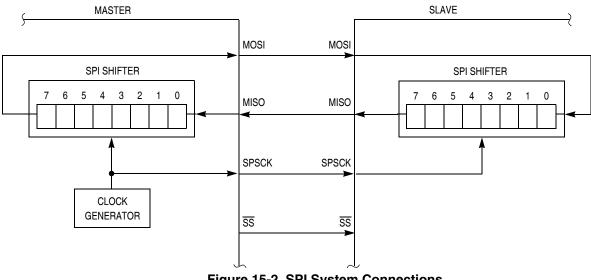

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 15.1.2.1 SPI System Block Diagram

Figure 15-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 15-2. SPI System Connections

#### Timer/Pulse-Width Modulator (S08TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

# 16.3.1 Timer Status and Control Register (TPMSC)

TPMSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

|       | 7                           | 6    | 5     | 4     | 3     | 2    | 1   | 0   |

|-------|-----------------------------|------|-------|-------|-------|------|-----|-----|

| R     | TOF                         | TOIE | CPWMS | CLKSB | CLKSA | PS2  | PS1 | PS0 |

| W     |                             | IOIE |       | ULKOD | ULKOA | F 32 | F31 | FOU |

| Reset | 0                           | 0    | 0     | 0     | 0     | 0    | 0   | 0   |

|       | = Unimplemented or Reserved |      |       |       |       |      |     |     |

### Figure 16-3. Timer Status and Control Register (TPMSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.         0       TOF interrupts inhibited (use software polling)         1       TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>O All TPM channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPM channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                                |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table 16-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 16-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Development Support

# 17.1.2 Features

Features of the BDC module include:

- Single pin for mode selection and background communications

- BDC registers are not located in the memory map

- SYNC command to determine target communications rate

- Non-intrusive commands for memory access

- Active background mode commands for CPU register access

- GO and TRACE1 commands

- BACKGROUND command can wake CPU from stop or wait modes

- One hardware address breakpoint built into BDC

- Oscillator runs in stop mode, if BDC enabled

- COP watchdog disabled while in active background mode

Features of the ICE system include:

- Two trigger comparators: Two address + read/write (R/W) or one full address + data + R/W

- Flexible 8-word by 16-bit FIFO (first-in, first-out) buffer for capture information:

- Change-of-flow addresses or

- Event-only data

- Two types of breakpoints:

- Tag breakpoints for instruction opcodes

- Force breakpoints for any address access

- Nine trigger modes:

- Basic: A-only, A OR B

- Sequence: A then B

- Full: A AND B data, A AND NOT B data

- Event (store data): Event-only B, A then event-only B

- Range: Inside range (A  $\leq$  address  $\leq$  B), outside range (address < A or address > B)

# 17.2 Background Debug Controller (BDC)

All MCUs in the HCS08 Family contain a single-wire background debug interface that supports in-circuit programming of on-chip nonvolatile memory and sophisticated non-intrusive debug capabilities. Unlike debug interfaces on earlier 8-bit MCUs, this system does not interfere with normal application resources. It does not use any user memory or locations in the memory map and does not share any on-chip peripherals.

BDC commands are divided into two groups:

• Active background mode commands require that the target MCU is in active background mode (the user program is not running). Active background mode commands allow the CPU registers to be

**Development Support**

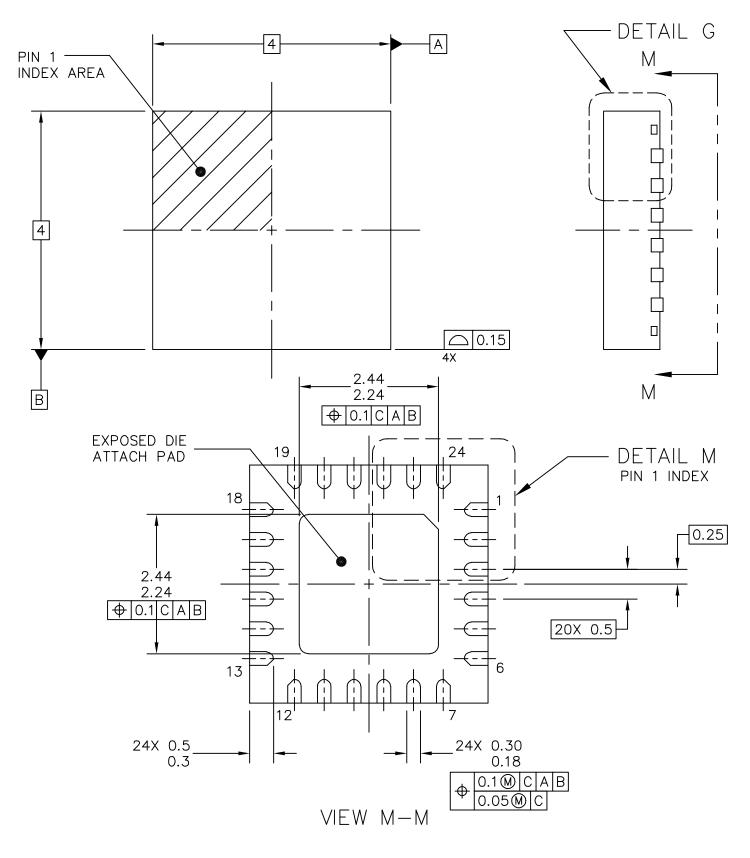

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA  | LOUTLINE                      | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|------------|-------------------------------|------------------|-------------|

|                                                         |            | DOCUMENT NO                   | : 98ARL10605D    | REV: O      |

|                                                         |            | CASE NUMBER                   | : 1897–01        | 08 SEP 2006 |

| 24 TERMINAL, 0.5 PITCH (4                               | 4 X 4 X 1) | STANDARD: JEDEC M0-220 VGGD-8 |                  |             |

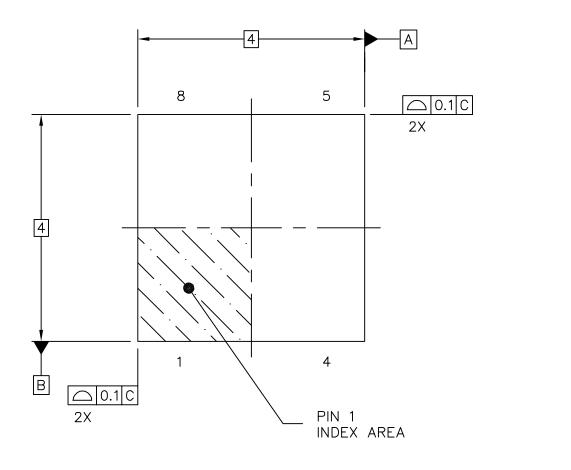

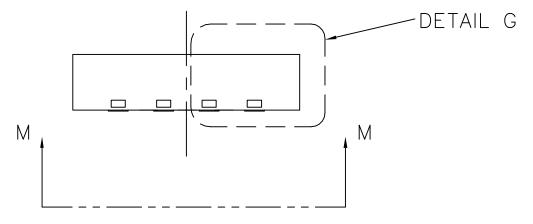

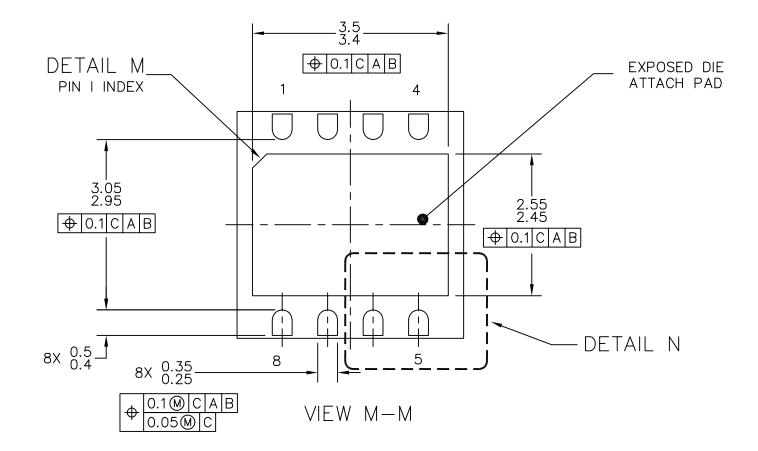

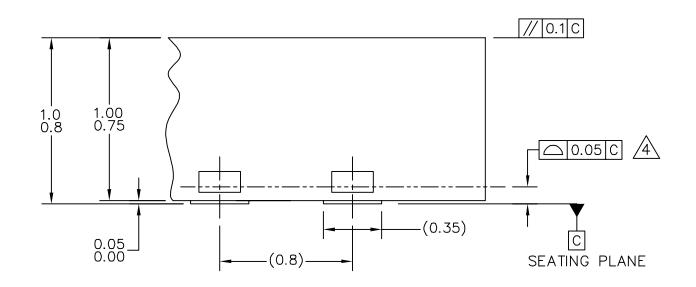

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved.      | MECHANICA | LOUTLINE            | PRINT VERSION NO | T TO SCALE  |

|--------------------------------------------------------------|-----------|---------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED DUAL<br>FLAT NO LEAD PACKAGE (DFN) |           | DOCUMENT NO         | ): 98ARL10557D   | REV: B      |

|                                                              |           | CASE NUMBER         | : 1452–02        | 28 DEC 2005 |

| 8 TERMINAL, 0.8 PITCH (4                                     | X 4 X I)  | STANDARD: NON-JEDEC |                  |             |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.      | DECHANICA | LOUTLINE     | PRINT VERSION NO | T TO SCALE  |

|--------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED DUAL<br>FLAT NO LEAD PACKAGE (DFN) |           | DOCUMENT NO  | ): 98ARL10557D   | REV: B      |

|                                                              |           | CASE NUMBER  | : 1452–02        | 28 DEC 2005 |

| 8 TERMINAL, 0.8 PITCH (4                                     | X 4 X 1)  | STANDARD: NO | N-JEDEC          |             |

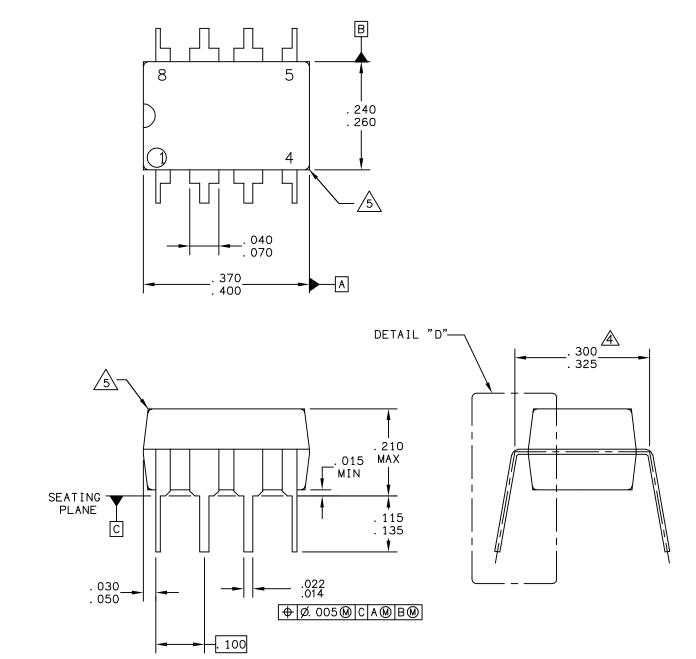

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO    | DT TO SCALE |

|---------------------------------------------------------|--------------------|---------------------|-------------|

| TITLE:                                                  | DOCUMENT N         | D: 98ASB42420B      | REV: N      |

| 8 LD PDIP                                               | CASE NUMBE         | R: 626–06           | 19 MAY 2005 |

|                                                         | STANDARD: N        | STANDARD: NON-JEDEC |             |