Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 4                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 4x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-VDFN Exposed Pad                                                     |

| Supplier Device Package    | 8-DFN-EP (4x4)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg84cfqe |

# MC9S08QG8 Data Sheet

Covers MC9S08QG8 MC9S08QG4

> MC9S08QG8 Rev. 5 11/2009

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2007-2009. All rights reserved.

Section Number Title Page

#### **Chapter 2 External Signal Description**

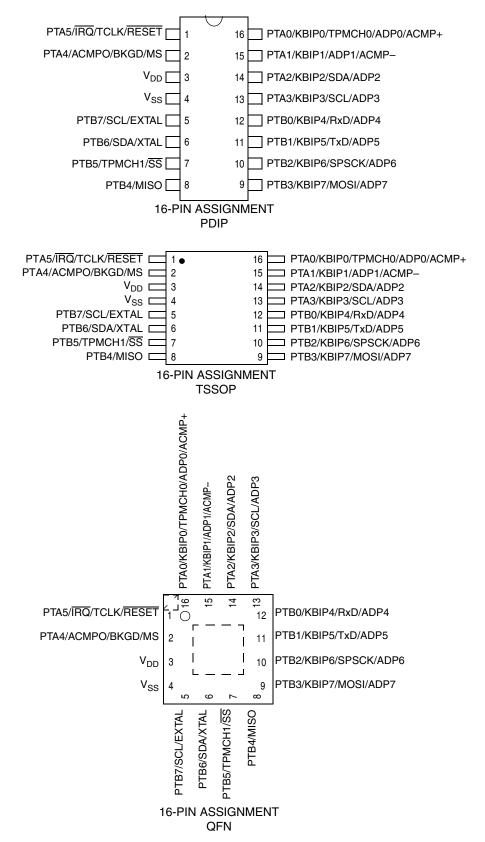

Figure 2-2. 16-Pin Packages

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

## 2.2.2 Oscillator (XOSC)

Out of reset, the MCU uses an internally generated clock provided by the internal clock source (ICS) module. The internal frequency is nominally 16-MHz and the default ICS settings will provide for a 8-MHz bus out of reset. For more information on the ICS, see Chapter 10, "Internal Clock Source (S08ICSV1)."

The oscillator module (XOSC) in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator in either of two frequency ranges selected by the RANGE bit in ICSC2. Rather than a crystal or ceramic resonator, an external clock source can be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion. R<sub>S</sub> (when used) and R<sub>F</sub> should be low-inductance resistors such as carbon composition resistors. Wire-wound resistors, and some metal film resistors, have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup, and its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity, and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2, which are usually the same size. As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

# 2.2.3 Reset (Input Only)

After a power-on reset (POR), the PTA5/ $\overline{IRQ}$ /TCLK/ $\overline{RESET}$  pin defaults to a general-purpose input port pin, PTA5. Setting RSTPE in SOPT1 configures the pin to be the  $\overline{RESET}$  input pin. After configured as  $\overline{RESET}$ , the pin will remain  $\overline{RESET}$  until the next POR. The  $\overline{RESET}$  pin can be used to reset the MCU from an external source when the pin is driven low. When enabled as the  $\overline{RESET}$  pin (RSTPE = 1), an internal pullup device is automatically enabled.

### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ .

The voltage measured on the internally pulled-up RESET pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . The  $\overline{RESET}$  pullup should not be used to pull up components external to the MCU.

## **NOTE**

<u>In EMC</u>-sensitive applications, an external RC filter is recommended on the <u>RESET</u> pin, if enabled. See Figure 2-4 for an example.

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

## **Chapter 2 External Signal Description**

**Table 2-1. Pin Sharing Priority**

|        | Pin Number |       |                   | Priority |                  |                   |                 |  |  |

|--------|------------|-------|-------------------|----------|------------------|-------------------|-----------------|--|--|

| P      | ın Numb    | er    | Lowest            | Highes   |                  |                   |                 |  |  |

| 24-pin | 16-pin     | 8-pin | Port Pin          | Alt 1    | Alt 2            | Alt 3             | Alt 4           |  |  |

| 24     | 1          | 1     | PTA5 <sup>1</sup> | ĪRQ      | TCLK             |                   | RESET           |  |  |

| 1      | 2          | 2     | PTA4              |          | ACMPO            | BKGD              | MS              |  |  |

| 2      | 3          | 3     |                   |          |                  |                   | $V_{DD}$        |  |  |

| 3      | 4          | 4     |                   |          |                  |                   | V <sub>SS</sub> |  |  |

| 4      | 5          | _     | PTB7              |          | SCL <sup>2</sup> | EXTAL             |                 |  |  |

| 5      | 6          | _     | PTB6              |          | SDA <sup>2</sup> | XTAL              |                 |  |  |

| 6      | 7          | _     | PTB5              |          | TPMCH1           | SS                |                 |  |  |

| 10     | 8          | _     | PTB4              |          | MISO             |                   |                 |  |  |

| 12     | 9          | _     | PTB3              | KBIP7    | MOSI             | ADP7              |                 |  |  |

| 13     | 10         | 1     | PTB2              | KBIP6    | SPSCK            | ADP6              |                 |  |  |

| 14     | 11         | 1     | PTB1              | KBIP5    | TxD              | ADP5              |                 |  |  |

| 15     | 12         | _     | PTB0              | KBIP4    | RxD              | ADP4              |                 |  |  |

| 16     | 13         | 5     | PTA3              | KBIP3    | SCL <sup>2</sup> | ADP3              |                 |  |  |

| 17     | 14         | 6     | PTA2              | KBIP2    | SDA <sup>2</sup> | ADP2              |                 |  |  |

| 18     | 15         | 7     | PTA1              | KBIP1    |                  | ADP1 <sup>3</sup> | ACMP-3          |  |  |

| 20     | 16         | 8     | PTA0              | KBIP0    | TPMCH0           | ADP0 <sup>3</sup> | ACMP+3          |  |  |

Pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ . The voltage measured on the internally pulled-up  $\overline{RESET}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ .

Table 2-2. Pin Function Reference

| Signal Function                 | Example(s)                                 | Reference                                                   |

|---------------------------------|--------------------------------------------|-------------------------------------------------------------|

| Port Pins                       | PTAx, PTBx                                 | Chapter 6, "Parallel Input/Output Control"                  |

| Analog comparator               | ACMPO, ACMP-, ACMP+                        | Chapter 8, "Analog Comparator (S08ACMPV2)"                  |

| Serial peripheral interface     | SS, MISO, MOSI, SPSCK                      | Chapter 15, "Serial Peripheral Interface (S08SPIV3)         |

| Keyboard interrupts             | KBIPx                                      | Chapter 12, "Keyboard Interrupt (S08KBIV2)"                 |

| Timer/PWM                       | TCLK, TPMCHx                               | Chapter 16, "Timer/Pulse-Width Modulator (S08TPMV2)"        |

| Inter-integrated circuit        | SCL, SDA                                   | Chapter 11, "Inter-Integrated Circuit (S08IICV1)"           |

| Serial communications interface | TxD, RxD                                   | Chapter 14, "Serial Communications Interface (S08SCIV3)     |

| Oscillator/clocking             | EXTAL, XTAL                                | Chapter 10, "Internal Clock Source (S08ICSV1)"              |

| Analog-to-digital               | ADPx                                       | Chapter 9, "Analog-to-Digital Converter (S08ADC10V1)"       |

| Power/core                      | BKGD/MS, V <sub>DD</sub> , V <sub>SS</sub> | Chapter 2, "External Signal Description"                    |

| Reset and interrupts            | RESET, IRQ                                 | Chapter 5, "Resets, Interrupts, and General System Control" |

## MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

<sup>&</sup>lt;sup>2</sup> IIC pins can be repositioned using IICPS in SOPT2; default reset locations are on PTA2 and PTA3

<sup>&</sup>lt;sup>3</sup> If ACMP and ADC are both enabled, both will have access to the pin.

**Table 4-2. Direct-Page Register Summary (continued)**

| Address                            | Register Name | Bit 7  | 6      | 5     | 4     | 3      | 2      | 1      | Bit 0  |  |  |

|------------------------------------|---------------|--------|--------|-------|-------|--------|--------|--------|--------|--|--|

| 0x00 <b>3F</b>                     | MTIMMOD       |        | MOD    |       |       |        |        |        |        |  |  |

| 0x00 <b>40</b>                     | TPMSC         | TOF    | TOIE   | CPWMS | CLKSB | CLKSA  | PS2    | PS1    | PS0    |  |  |

| 0x00 <b>41</b>                     | TPMCNTH       | Bit 15 | 14     | 13    | 12    | 11     | 10     | 9      | Bit 8  |  |  |

| 0x00 <b>42</b>                     | TPMCNTL       | Bit 7  | 6      | 5     | 4     | 3      | 2      | 1      | Bit 0  |  |  |

| 0x00 <b>43</b>                     | TPMMODH       | Bit 15 | 14     | 13    | 12    | 11     | 10     | 9      | Bit 8  |  |  |

| 0x00 <b>44</b>                     | TPMMODL       | Bit 7  | 6      | 5     | 4     | 3      | 2      | 1      | Bit 0  |  |  |

| 0x00 <b>45</b>                     | TPMC0SC       | CH0F   | CH0IE  | MS0B  | MS0A  | ELS0B  | ELS0A  | 0      | 0      |  |  |

| 0x00 <b>46</b>                     | TPMC0VH       | Bit 15 | 14     | 13    | 12    | 11     | 10     | 9      | Bit 8  |  |  |

| 0x00 <b>47</b>                     | TPMC0VL       | Bit 7  | 6      | 5     | 4     | 3      | 2      | 1      | Bit 0  |  |  |

| 0x00 <b>48</b>                     | TPMC1SC       | CH1F   | CH1IE  | MS1B  | MS1A  | ELS1B  | ELS1A  | 0      | 0      |  |  |

| 0x00 <b>49</b>                     | TPMC1VH       | Bit 15 | 14     | 13    | 12    | 11     | 10     | 9      | Bit 8  |  |  |

| 0x00 <b>4A</b>                     | TPMC1VL       | Bit 7  | 6      | 5     | 4     | 3      | 2      | 1      | Bit 0  |  |  |

| 0x00 <b>4B</b> -<br>0x00 <b>5F</b> | Reserved      | _<br>_ | _<br>_ |       |       | _<br>_ | _<br>_ | _<br>_ | _<br>_ |  |  |

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

**Table 4-3. High-Page Register Summary**

| Address        | Register Name | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

|----------------|---------------|---------|--------|---------|-------|-------|--------|--------|-------|

| 0x1800         | SRS           | POR     | PIN    | COP     | ILOP  | ILAD  | 0      | LVD    | 0     |

|                |               |         |        |         |       |       |        |        | •     |

| 0x1801         | SBDFR         | 0       | 0      | 0       | 0     | 0     | 0      | 0      | BDFR  |

| 0x1802         | SOPT1         | COPE    | COPT   | STOPE   | _     | 0     | 0      | BKGDPE | RSTPE |

| 0x1803         | SOPT2         | COPCLKS | 0      | 0       | 0     | 0     | 0      | IICPS  | ACIC  |

| 0x <b>1804</b> | Reserved      | _       | -      | ı       | -     | ı     | ı      | 1      | _     |

| 0x1805         | Reserved      | _       | -      | ı       | -     | ı     | ı      | 1      | _     |

| 0x1806         | SDIDH         | _       | -      | ı       | -     | ID11  | ID10   | ID9    | ID8   |

| 0x1807         | SDIDL         | ID7     | ID6    | ID5     | ID4   | ID3   | ID2    | ID1    | ID0   |

| 0x1808         | SRTISC        | RTIF    | RTIACK | RTICLKS | RTIE  | 0     |        | RTIS   |       |

| 0x1809         | SPMSC1        | LVDF    | LVDACK | LVDIE   | LVDRE | LVDSE | LVDE   | 0      | BGBE  |

| 0x180A         | SPMSC2        | 0       | 0      | 0       | PDF   | PPDF  | PPDACK | PDC    | PPDC  |

| 0x180B         | Reserved      | _       | _      | _       | _     | _     | _      | _      | _     |

| 0x180C         | SPMSC3        | LVWF    | LVWACK | LVDV    | LVWV  | _     | _      | _      | _     |

| 0x180D-        | Reserved      | _       | _      | _       | _     | _     | _      | _      | _     |

| 0x180F         | 110001100     | _       | _      | 1       | _     | 1     | 1      | 1      | _     |

| 0x1810         | DBGCAH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1811         | DBGCAL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1812         | DBGCBH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1813         | DBGCBL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1814         | DBGFH         | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1815         | DBGFL         | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

**Chapter 4 Memory Map and Register Definition**

**Table 4-3. High-Page Register Summary (continued)**

| Address           | Register Name | Bit 7  | 6      | 5      | 4       | 3      | 2      | 1         | Bit 0  |

|-------------------|---------------|--------|--------|--------|---------|--------|--------|-----------|--------|

| 0x1816            | DBGC          | DBGEN  | ARM    | TAG    | BRKEN   | RWA    | RWAEN  | RWB       | RWBEN  |

| 0x1817            | DBGT          | TRGSEL | BEGIN  | 0      | 0       | TRG3   | TRG2   | TRG2 TRG1 |        |

| 0x1818            | DBGS          | AF     | BF     | ARMF   | 0       | CNT3   | CNT2   | CNT1      | CNT0   |

| 0x1819–<br>0x181F | Reserved      | _      |        | _<br>_ |         | -      | _      | -         | _<br>_ |

| 0x1820            | FCDIV         | DIVLD  | PRDIV8 |        |         | D      | V      |           |        |

| 0x1821            | FOPT          | KEYEN  | FNORED | 0      | 0       | 0      | 0      | SEC01     | SEC00  |

| 0x1822            | Reserved      | _      | _      | _      | _       | _      | _      | _         | _      |

| 0x1823            | FCNFG         | 0      | 0      | KEYACC | 0       | 0      | 0      | 0         | 0      |

| 0x1824            | FPROT         |        |        |        | FPS     |        |        |           | FPDIS  |

| 0x1825            | FSTAT         | FCBEF  | FCCF   | FPVIOL | FACCERR | 0      | FBLANK | 0         | 0      |

| 0x1826            | FCMD          |        |        |        | FC      | MD     |        |           |        |

| 0x1827-<br>0x183F | Reserved      | _      | _      | _<br>_ | _       | _      | _<br>_ | _         | _      |

| 0x1840            | PTAPE         | 0      | 0      | PTAPE5 | PTAPE4  | PTAPE3 | PTAPE2 | PTAPE1    | PTAPE0 |

| 0x1841            | PTASE         | 0      | 0      | PTASE5 | PTASE4  | PTASE3 | PTASE2 | PTASE1    | PTASE0 |

| 0x1842            | PTADS         | 0      | 0      | PTADS5 | PTADS4  | PTADS3 | PTADS2 | PTADS1    | PTADS0 |

| 0x1843            | Reserved      | _      | _      | _      | _       | _      | _      | _         | _      |

| 0x1844            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4  | PTBPE3 | PTBPE2 | PTBPE1    | PTBPE0 |

| 0x1845            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4  | PTBSE3 | PTBSE2 | PTBSE1    | PTBSE0 |

| 0x1846            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4  | PTBDS3 | PTBDS2 | PTBDS1    | PTBDS0 |

| 0x1847            | Reserved      | _      | _      | _      | _       | _      | _      | _         | _      |

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key that optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5 44 Freescale Semiconductor

#### **Chapter 4 Memory Map and Register Definition**

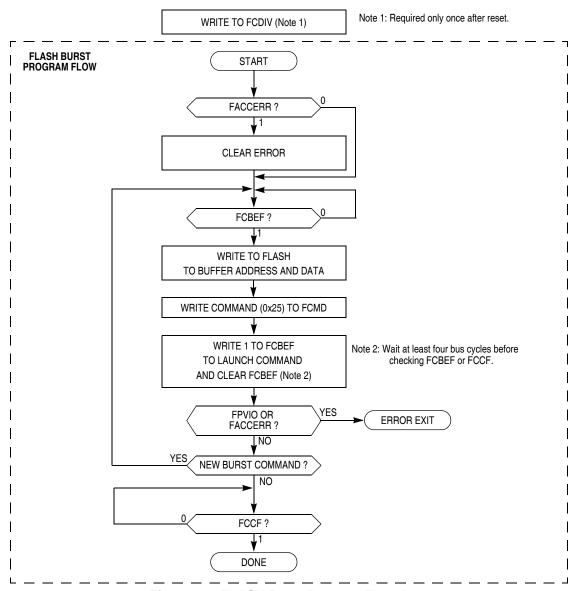

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

Figure 4-3. FLASH Burst Program Flowchart

**Chapter 4 Memory Map and Register Definition**

**Table 4-12. FSTAT Register Field Descriptions (continued)**

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.  O No access error.  1 An access error has occurred. |

| 2<br>FBLANK  | <ul> <li>FLASH Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>O After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>   |

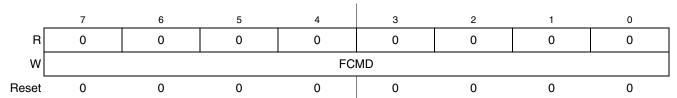

## 4.7.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-13. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of FLASH programming and erase operations.

Figure 4-10. FLASH Command Register (FCMD)

**Table 4-13. FLASH Commands**

| Command                     | FCMD | Equate File Label |

|-----------------------------|------|-------------------|

| Blank check                 | 0x05 | mBlank            |

| Byte program                | 0x20 | mByteProg         |

| Byte program — burst mode   | 0x25 | mBurstProg        |

| Page erase (512 bytes/page) | 0x40 | mPageErase        |

| Mass erase (all FLASH)      | 0x41 | mMassErase        |

All other command codes are illegal and generate an access error.

It is not necessary to perform a blank check command after a mass erase operation. The blank check command is only required as part of the security unlocking mechanism.

Chapter 5 Resets, Interrupts, and General System Control

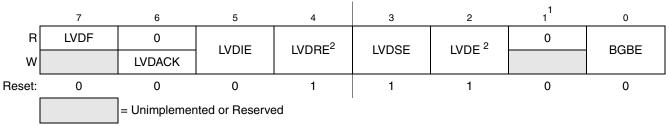

# 5.8.8 System Power Management Status and Control 1 Register (SPMSC1)

This high page register contains status and control bits to support the low voltage detect function and to enable the bandgap voltage reference for use by the ADC module. To configure the low voltage detect trip voltage, see Table 5-14 for the LVDV bit description in SPMSC3.

Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

Table 5-12. SPMSC1 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                       |

| 6<br>LVDACK | Low-Voltage Detect Acknowledge — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                           |

| 5<br>LVDIE  | Low-Voltage Detect Interrupt Enable — This bit enables hardware interrupt requests for LVDF.  0 Hardware interrupt disabled (use polling).  1 Request a hardware interrupt when LVDF = 1.                                                                          |

| 4<br>LVDRE  | Low-Voltage Detect Reset Enable — This write-once bit enables LVDF events to generate a hardware reset (provided LVDE = 1).  0 LVDF does not generate hardware resets.  1 Force an MCU reset when LVDF = 1.                                                        |

| 3<br>LVDSE  | Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.  0 Low-voltage detect disabled during stop mode.  1 Low-voltage detect enabled during stop mode. |

| 2<br>LVDE   | Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.  0 LVD logic disabled.  1 LVD logic enabled.                                                                          |

| 0<br>BGBE   | Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels or as a voltage reference for ACMP module.  0 Bandgap buffer disabled.  1 Bandgap buffer enabled.          |

<sup>&</sup>lt;sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>&</sup>lt;sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

Table 7-2. . Instruction Set Summary (Sheet 1 of 9)

| Source<br>Form                                                                                                  | Operation                                                                | Address<br>Mode                       | Object Code                                                                      | Cycles                               | Cyc-by-Cyc<br>Details                      | Affect on CCR |         |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|---------------|---------|

| 1 01111                                                                                                         |                                                                          | PA                                    |                                                                                  | Q                                    | Dotano                                     | VH            | INZC    |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry $A \leftarrow (A) + (M) + (C)$                            | IMM DIR EXT IX2 IX1 IX SP2 SP1        | A9 ii B9 dd C9 hh ll D9 ee ff E9 ff F9 9E D9 ee ff 9E E9 ff                      | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp prpp rfp pprpp prpp            | <b>1</b>      | - 1 1 1 |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry A ← (A) + (M)                                          | IMM DIR EXT IX2 IX1 IX SP2 SP1        | AB ii BB dd CB hh ll DB ee ff EB ff FB 9E DB ee ff 9E EB ff                      | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp rpp rfp pprpp prpp prpp        | <b>‡</b> ‡    | - 1 1 1 |

| AIS #opr8i                                                                                                      | Add Immediate Value (Signed) to Stack Pointer $SP \leftarrow (SP) + (M)$ | IMM                                   | A7 ii                                                                            | 2                                    | pp                                         |               |         |

| AIX #opr8i                                                                                                      | Add Immediate Value (Signed) to Index Register (H:X) H:X ← (H:X) + (M)   | IMM                                   | AF ii                                                                            | 2                                    | pp                                         |               |         |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND<br>A ← (A) & (M)                                             | IMM DIR EXT IX2 IX1 IX SP2 SP1        | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp rpp rfp pprpp prpp prpp        | 0 –           | - ↑ ↑ - |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL oprx8,SP                                              | Arithmetic Shift Left  Color bo bo bo (Same as LSL)                      | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp | <b>1</b> –    | - 1 1 1 |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                              | Arithmetic Shift Right  b7 b0                                            | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp | <b>1</b> –    | - 1 1 1 |

| BCC rel                                                                                                         | Branch if Carry Bit Clear (if C = 0)                                     | REL                                   | 24 rr                                                                            | 3                                    | ppp                                        |               |         |

Table 7-2. . Instruction Set Summary (Sheet 6 of 9)

| Source<br>Form                                                                                                  | Operation                                                                                                  | Address<br>Mode                          | Object Code                                                 | Cycles                               | Cyc-by-Cyc<br>Details                      |            | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------|--------------------------------------|--------------------------------------------|------------|-----------------|

| 1 01111                                                                                                         |                                                                                                            | ĀĀ                                       |                                                             | Q                                    | Details                                    | VH         | INZC            |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                            | Move (M) <sub>destination</sub> ← (M) <sub>source</sub> In IX+/DIR and DIR/IX+ Modes, H:X ← (H:X) + \$0001 | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR | 4E dd dd<br>5E dd<br>6E ii dd<br>7E dd                      | 5<br>5<br>4<br>5                     | rpwpp<br>rfwpp<br>pwpp<br>rfwpp            | 0 –        | - \$ \$-        |

| MUL                                                                                                             | Unsigned multiply $X:A \leftarrow (X) \times (A)$                                                          | INH                                      | 42                                                          | 5                                    | ffffp                                      | - 0        | 0               |

| NEG opr8a<br>NEGA<br>NEGX<br>NEG oprx8,X<br>NEG ,X<br>NEG oprx8,SP                                              | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                      | IX                                       | 30 dd<br>40<br>50<br>60 ff<br>70<br>9E 60 ff                | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp p p rfwpp rfwp prfwpp                | <b>1</b> – | - 🕽 🕽 🕽         |

| NOP                                                                                                             | No Operation — Uses 1 Bus Cycle                                                                            | INH                                      | 9D                                                          | 1                                    | р                                          |            |                 |

| NSA                                                                                                             | Nibble Swap Accumulator<br>A ← (A[3:0]:A[7:4])                                                             | INH                                      | 62                                                          | 1                                    | р                                          |            |                 |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator and Memory $A \leftarrow (A) \mid (M)$                                            | IMM DIR EXT IX2 IX1 IX SP2 SP1           | AA ii BA dd CA hh 11 DA ee ff EA ff FA 9E DA ee ff 9E EA ff | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp rfp pprpp pprpp pprpp prpp     | 0 –        | - 1 1 -         |

| PSHA                                                                                                            | Push Accumulator onto Stack<br>Push (A); SP ← (SP) – \$0001                                                | INH                                      | 87                                                          | 2                                    | sp                                         |            |                 |

| PSHH                                                                                                            | Push H (Index Register High) onto Stack<br>Push (H); SP ← (SP) – \$0001                                    | INH                                      | 8B                                                          | 2                                    | sp                                         |            |                 |

| PSHX                                                                                                            | Push X (Index Register Low) onto Stack Push (X); SP ← (SP) – \$0001                                        | INH                                      | 89                                                          | 2                                    | sp                                         |            |                 |

| PULA                                                                                                            | Pull Accumulator from Stack SP ← (SP + \$0001); Pull (A)                                                   | INH                                      | 86                                                          | 3                                    | ufp                                        |            |                 |

| PULH                                                                                                            | Pull H (Index Register High) from Stack SP ← (SP + \$0001); Pull (H)                                       | INH                                      | 8A                                                          | 3                                    | ufp                                        |            |                 |

| PULX                                                                                                            | Pull X (Index Register Low) from Stack $SP \leftarrow (SP + \$0001)$ ; Pull (X)                            | INH                                      | 88                                                          | 3                                    | ufp                                        |            |                 |

| ROL opr8a<br>ROLA<br>ROLX<br>ROL oprx8,X<br>ROL ,X<br>ROL oprx8,SP                                              | Rotate Left through Carry  b7 b0                                                                           | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1    | 39 dd<br>49<br>59<br>69 ff<br>79<br>9E 69 ff                | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp p rfwpp rfwp prfwpp                  | <b>1</b> – | - ↑ ↑ ↑         |

| ROR opr8a<br>RORA<br>RORX<br>ROR oprx8,X<br>ROR ,X<br>ROR oprx8,SP                                              | Rotate Right through Carry  b7 b0                                                                          | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1    | 36 dd<br>46<br>56<br>66 ff<br>76<br>9E 66 ff                | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp | <b>1</b> - | - 🕽 🕽 🕽         |

#### Chapter 7 Central Processor Unit (S08CPUV2)

## Table 7-2. . Instruction Set Summary (Sheet 9 of 9)

| Source<br>Form | Operation                                                 | ddress<br>Mode | Object Code | ycles | Cyc-by-Cyc<br>Details | Affect on CCR |      |

|----------------|-----------------------------------------------------------|----------------|-------------|-------|-----------------------|---------------|------|

|                |                                                           | Ad<br>≥        |             | Ö.    | 2000                  | VH            | INZC |

| TXS            | Transfer Index Reg. to SP<br>SP ← (H:X) – \$0001          | INH            | 94          | 2     | fp                    |               |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit ← 0; Halt CPU | INH            | 8F          | 2+    | fp                    |               | 0    |

**Source Form:** Everything in the source forms columns, *except expressions in italic characters*, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (# , ( ) and +) are always a literal characters.

Any label or expression that evaluates to a single integer in the range 0-7.

opr8i Any label or expression that evaluates to an 8-bit immediate value.opr16i Any label or expression that evaluates to a 16-bit immediate value.

opr8a Any label or expression that evaluates to an 8-bit direct-page address (\$00xx).

opr16a Any label or expression that evaluates to a 16-bit address.

oprx8 Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing.

oprx16 Any label or expression that evaluates to a 16-bit value, used for indexed addressing.

rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

### **Operation Symbols:**

A Accumulator

CCR Condition code register

H Index register high byte

M Memory location

n Any bit

opr Operand (one or two bytes)

PC Program counter

PCH Program counter high byte

PCL Program counter low byte

rel Relative program counter offset byte

SP Stack pointer

SPL Stack pointer low byte X Index register low byte

& Logical ANDI Logical OR

⊕ Logical EXCLUSIVE OR

() Contents of

+ Add

Subtract, Negation (two's complement)

× Multiply

Divide

# Immediate value

← Loaded with

: Concatenated with

#### **CCR Bits:**

V Overflow bit

H Half-carry bit

I Interrupt mask

N Negative bit

Z Zero bit

C Carry/borrow bit

### Addressing Modes:

DIR Direct addressing mode

EXT Extended addressing mode

IMM Immediate addressing mode

INH Inherent addressing mode

IX Indexed, no offset addressing mode

IX1 Indexed, 8-bit offset addressing modeIX2 Indexed, 16-bit offset addressing mode

IX+ Indexed, no offset, post increment addressing mode

IX1+ Indexed, 8-bit offset, post increment addressing mode

REL Relative addressing mode

SP1 Stack pointer, 8-bit offset addressing modeSP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

Free cycle. This indicates a cycle where the CPU does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

p Progryam fetch; read from next consecutive location in program memory

r Read 8-bit operand

s Push (write) one byte onto stack

u Pop (read) one byte from stack

v Read vector from \$FFxx (high byte first)

w Write 8-bit operand

### **CCR Effects:**

\$\ \tag{Set}\$ or clearedNot affectedU Undefined

#### Internal Clock Source (S08ICSV1)

times the filter frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

## 10.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

## 10.4.1.7 Stop

ICS stop mode is entered whenever the MCU enters stop. In this mode, all ICS clock signals are stopped except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

## 10.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency.

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

# 10.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

# **Chapter 11 Inter-Integrated Circuit (S08IICV1)**

## 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

## 11.1.1 Module Configuration

The IIC module pins, SDA and SCL can be repositioned under software control using IICPS in SOPT2 as as shown in Table 11-1. IICPS in SOPT2 selects which general-purpose I/O ports are associated with IIC operation.

**Table 11-1. IIC Position Options**

| IICPS in SOPT2 | Port Pin for SDA | Port Pin for SCL |

|----------------|------------------|------------------|

| 0 (default)    | PTA2             | PTA3             |

| 1              | PTB6             | PTB7             |

Figure 11-1 is the MC9S08QG8/4 block diagram with the IIC block highlighted.

## Serial Communications Interface (S08SCIV3)

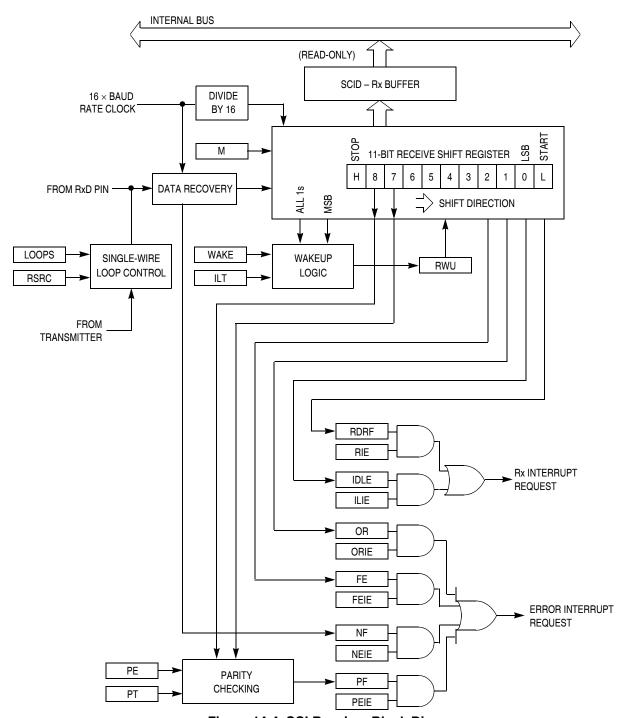

Figure 14-4 shows the receiver portion of the SCI.

Figure 14-4. SCI Receiver Block Diagram

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPRF  | SPI Read Buffer Full Flag — SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPID). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.  0 No data available in the receive data buffer  1 Data available in the receive data buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5<br>SPTEF | SPI Transmit Buffer Empty Flag — This bit is set when there is room in the transmit data buffer. It is cleared by reading SPIS with SPTEF set, followed by writing a data value to the transmit buffer at SPID. SPIS must be read with SPTEF = 1 before writing data to SPID or the SPID write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPIC1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPID is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter.  O SPI transmit buffer not empty  1 SPI transmit buffer empty |

| 4<br>MODF  | Master Mode Fault Flag — MODF is set if the SPI is configured as a master and the slave select input goes low, indicating some other SPI device is also configured as a master. The SS pin acts as a mode fault error input only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by reading MODF while it is 1, then writing to SPI control register 1 (SPIC1).  O No mode fault error  Mode fault error detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 15.4.5 SPI Data Register (SPID)

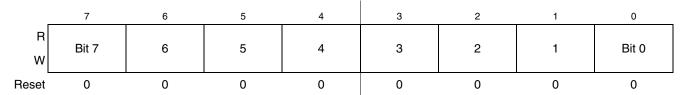

Figure 15-9. SPI Data Register (SPID)

Reads of this register return the data read from the receive data buffer. Writes to this register write data to the transmit data buffer. When the SPI is configured as a master, writing data to the transmit data buffer initiates an SPI transfer.

Data should not be written to the transmit data buffer unless the SPI transmit buffer empty flag (SPTEF) is set, indicating there is room in the transmit buffer to queue a new transmit byte.

Data may be read from SPID any time after SPRF is set and before another transfer is finished. Failure to read the data out of the receive data buffer before a new transfer ends causes a receive overrun condition and the data from the new transfer is lost.

## **Appendix A Electrical Characteristics**

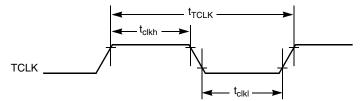

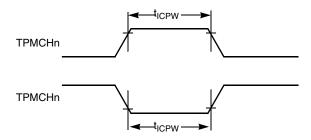

Table A-10. TPM/MTIM Input Timing

| Function                  | Symbol            | Min | Max                 | Unit             |

|---------------------------|-------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TCLK</sub> | 0   | f <sub>Bus</sub> /4 | Hz               |

| External clock period     | t <sub>TCLK</sub> | 4   | _                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub> | 1.5 | _                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>clkl</sub> | 1.5 | _                   | t <sub>cyc</sub> |

| Input capture pulse width | t <sub>ICPW</sub> | 1.5 | _                   | t <sub>cyc</sub> |

Figure A-11. Timer External Clock

Figure A-12. Timer Input Capture Pulse

# A.8.3 SPI Timing

Table A-11 and Figure A-13 through Figure A-16 describe the timing requirements for the SPI system.

Table A-11. SPI Timing

| No. | Function                         | Symbol             | Min                         | Max                                        | Unit                                   |

|-----|----------------------------------|--------------------|-----------------------------|--------------------------------------------|----------------------------------------|

|     | Operating frequency Master Slave | f <sub>op</sub>    | f <sub>Bus</sub> /2048<br>0 | f <sub>Bus</sub> /2<br>f <sub>Bus</sub> /4 | Hz                                     |

| 1   | SPSCK period<br>Master<br>Slave  | t <sub>SPSCK</sub> | 2<br>4                      | 2048<br>—                                  | t <sub>cyc</sub><br>t <sub>cyc</sub>   |

| 2   | Enable lead time Master Slave    | t <sub>Lead</sub>  | 1/2<br>1                    |                                            | t <sub>SPSCK</sub><br>t <sub>cyc</sub> |

| 3   | Enable lag time Master Slave     | t <sub>Lag</sub>   | 1/2<br>1                    |                                            | t <sub>SPSCK</sub><br>t <sub>cyc</sub> |

## MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

# Appendix B Ordering Information and Mechanical Drawings

# **B.1** Ordering Information

This section contains ordering information for MC9S08QG8 and MC9S08QG4 devices.

Available Packages<sup>2</sup> Memory Device Number<sup>1</sup> **FLASH** 24-Pin **RAM** 16-Pin 8-Pin 16 PDIP 8 DFN MC9S08QG8 8K 512 **24 QFN** 16 QFN 8 NB SOIC 16 TSSOP 8 DFN 16 QFN MC9S08QG4 4K 256 24 QFN 8 PDIP 16 TSSOP 8 NB SOIC

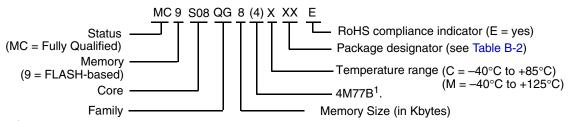

**Table B-1. Device Numbering System**

## **B.1.1** Device Numbering Scheme

Only maskset 4M77B has this additional number.

## **B.2** Mechanical Drawings

The following pages are mechanical specifications for MC9S08QG8/4 package options. See Table B-2 for the document number for each package type.

| Pin Count | Туре  | Designator | Document No. |

|-----------|-------|------------|--------------|

| 24        | QFN   | FK         | 98ARL10605D  |

| 16        | PDIP  | PB         | 98ASB42431B  |

| 16        | QFN   | FF         | 98ARE10614D  |

| 16        | TSSOP | DT         | 98ASH70247A  |

**Table B-2. Package Information**

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

See Table 1-1 for a complete description of modules included on each device.

<sup>&</sup>lt;sup>2</sup> See Table B-2 for package information.

## NOTES:

TITLE:

16 LD PDIP

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- A DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|                                                         | MILLIM | IETERS |           | INCHES    |       | MILL | LIMETERS  | INCHES   |          |

|---------------------------------------------------------|--------|--------|-----------|-----------|-------|------|-----------|----------|----------|

| DIM                                                     | MIN    | MAX    | MIN       | MAX       | DIM   | MIN  | MAX       | MIN      | MAX      |

| А                                                       | 18.80  | 19.55  | 0.740     | 0.770     |       |      |           |          |          |

| В                                                       | 6.35   | 6.85   | 0.250     | 0.270     |       |      |           |          |          |

| С                                                       | 3.69   | 4.44   | 0.145     | 0.175     |       |      |           |          |          |

| D                                                       | 0.39   | 0.53   | 0.015     | 0.021     |       |      |           |          |          |

| F                                                       | 1.02   | 1.77   | 0.040     | 0.070     |       |      |           |          |          |

| G                                                       | 2.54   | BSC    | 0.100 BSC |           |       |      |           |          |          |

| Н                                                       | 1.27   | BSC    | 0.0       | 50 BSC    |       |      |           |          |          |

| J                                                       | 0.21   | 0.38   | 0.008     | 0.015     |       |      |           |          |          |

| K                                                       | 2.80   | 3.30   | 0.110     | 0.130     |       |      |           |          |          |

| L                                                       | 7.50   | 7.74   | 0.295     | 0.305     |       |      |           |          |          |

| M                                                       | 0.     | 10°    | 0.        | 10°       |       |      |           |          |          |

| S                                                       | 0.51   | 1.01   | 0.020     | 0.040     |       |      |           |          |          |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |        |        | INC.      | MECHANICA | L OUT | LINE | PRINT VER | SION NOT | TO SCALE |

DOCUMENT NO: 98ASB42431B

CASE NUMBER: 648-08

STANDARD: NON-JEDEC

REV: T

19 MAY 2005