Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 4                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 4x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 8-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg8cdne |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# NP

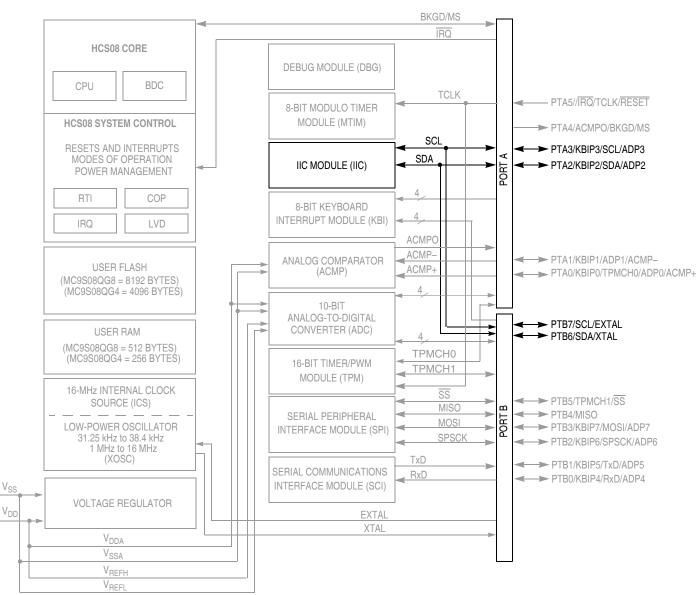

# MC9S08QG8/4 Features

## 8-Bit HCS08 Central Processor Unit (CPU)

- 20-MHz HCS08 CPU (central processor unit)

- HC08 instruction set with added BGND instruction

- Background debugging system

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- Debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing change-of-flow addresses and event-only data Debug module supports both tag and force breakpoints

- Support for up to 32 interrupt/reset sources

### **Memory Options**

- FLASH read/program/erase over full operating voltage and temperature

- MC9S08QG8 8 Kbytes FLASH, 512 bytes RAM MC9S08QG4 — 4 Kbytes FLASH, 256 bytes RAM

#### **Power-Saving Modes**

• Wait plus three stops

### **Clock Source Options**

- ICS Internal clock source module containing a frequency-locked-loop (FLL) controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage; supports bus frequencies from 1 MHz to 10 MHz

- XOSC Low-power oscillator module with software selectable crystal or ceramic resonator range, 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz, and supports external clock source input up to 20 MHz

### **System Protection**

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

- FLASH block protect

#### Peripherals

- ADC 8-channel, 10-bit analog-to-digital converter with automatic compare function, asynchronous clock source, temperature sensor, and internal bandgap reference channel; ADC is hardware triggerable using the RTI counter

- ACMP Analog comparator module with option to compare to internal reference; output can be optionally routed to TPM module

- SCI Serial communications interface module with option for 13-bit break capabilities

- SPI Serial peripheral interface module

- IIC Inter-integrated circuit bus module

- **TPM** 2-channel timer/pulse-width modulator; each channel can be used for input capture, output compare, buffered edge-aligned PWM, or buffered center-aligned PWM

- MTIM 8-bit modulo timer module with 8-bit prescaler

- **KBI**—8-pin keyboard interrupt module with software selectable polarity on edge or edge/level modes

## Input/Output

- 12 general-purpose input/output (I/O) pins, one input-only pin and one output-only pin; outputs 10 mA each, 60 mA max for package

- Software selectable pullups on ports when used as input

- Software selectable slew rate control and drive strength on ports when used as output

- Internal pullup on RESET and IRQ pins to reduce customer system cost

### **Development Support**

- Single-wire background debug interface

- On-chip, in-circuit emulation (ICE) with real-time bus capture

## **Package Options**

- 24-pin quad flat no lead (QFN) package

- 16-pin plastic dual in-line package (PDIP) MC9S08QG8 only

- 16-pin quad flat no lead (QFN) package

- 16-pin thin shrink small outline package (TSSOP)

- 8-pin dual flat no lead (DFN) package

- 8-pin PDIP MC9S08QG4 only

- 8-pin narrow body small outline integrated circuit (SOIC) package

**Section Number**

Title

Page

## NOTE

When an alternative function is first enabled, it is possible to get a spurious edge to the module. User software should clear out any associated flags before interrupts are enabled. Table 2-1 shows the priority if multiple modules are enabled. The highest priority module will have control over the pin. Selecting a higher priority pin function with a lower priority function already enabled can cause spurious edges to the lower priority module. It is recommended that all modules that share a pin be disabled before enabling anther module.

#### **Chapter 4 Memory Map and Register Definition**

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

| Table | 4-9. | Security | States <sup>1</sup> |

|-------|------|----------|---------------------|

|-------|------|----------|---------------------|

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

## 4.7.3 FLASH Configuration Register (FCNFG)

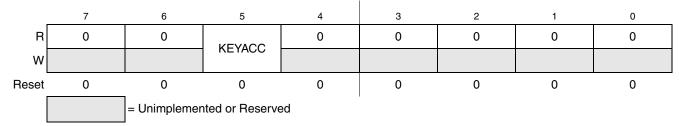

#### Figure 4-7. FLASH Configuration Register (FCNFG)

#### Table 4-10. FCNFG Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

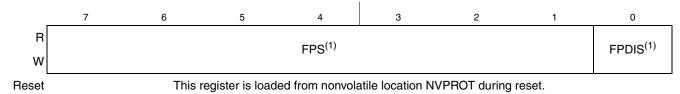

# 4.7.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT are copied from FLASH into FPROT. This register can be read at any time. If FPDIS = 0, protection can be increased, i.e., a smaller value of FPS can be written. If FPDIS = 1, writes do not change protection.

Background commands can be used to change the contents of these bits in FPROT.

Figure 4-8. FLASH Protection Register (FPROT)

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

1

1

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.10 System Power Management Status and Control 3 Register (SPMSC3)

This high page register is used to report the status of the low voltage warning function and to select the low voltage detect trip voltage.

|                  | 7              | 6            | 5               | 4    | 3                      | 2 | 1 | 0 |

|------------------|----------------|--------------|-----------------|------|------------------------|---|---|---|

| R                | LVWF           | 0            |                 |      | 0                      | 0 | 0 | 0 |

| W                |                | LVWACK       | LVDV            | LVWV |                        |   |   |   |

| POR:             | 0 <sup>1</sup> | 0            | 0               | 0    | 0                      | 0 | 0 | 0 |

| LVD:             | 0 <sup>1</sup> | 0            | U               | U    | 0                      | 0 | 0 | 0 |

| Any other reset: | 01             | 0            | U               | U    | 0                      | 0 | 0 | 0 |

|                  |                | = Unimplemer | ited or Reserve | ed   | U= Unaffected by reset |   |   |   |

Figure 5-12. System Power Management Status and Control 3 Register (SPMSC3)

LVWF will be set in the case when V<sub>Supply</sub> transitions below the trip point or after reset and V<sub>Supply</sub> is already below V<sub>LVW</sub>.

| Field       | Description                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>LVWF   | <ul> <li>Low-Voltage Warning Flag — The LVWF bit indicates the low voltage warning status.</li> <li>0 Low voltage warning not present.</li> <li>1 Low voltage warning is present or was present.</li> </ul>                                                                   |  |  |  |  |  |

| 6<br>LVWACK | <b>Low-Voltage Warning Acknowledge</b> — The LVWF bit indicates the low voltage warning status. Writing a 1 to LVWACK clears LVWF to a 0 if a low voltage warning is not present.                                                                                             |  |  |  |  |  |

| 5<br>LVDV   | <ul> <li>Low-Voltage Detect Voltage Select — The LVDV bit selects the LVD trip point voltage (V<sub>LVD</sub>).</li> <li>0 Low trip point selected (V<sub>LVD</sub> = V<sub>LVDL</sub>).</li> <li>1 High trip point selected (V<sub>LVD</sub> = V<sub>LVDH</sub>).</li> </ul> |  |  |  |  |  |

| 4<br>LVWV   | Low-Voltage Warning Voltage Select — The LVWV bit selects the LVW trip point voltage (V <sub>LVW</sub> ).         0 Low trip point selected (V <sub>LVW</sub> = V <sub>LVWL</sub> ).         1 High trip point selected (V <sub>LVW</sub> = V <sub>LVWH</sub> ).              |  |  |  |  |  |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

# 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

## 9.1.2 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 10 bits resolution.

- Up to 28 analog inputs.

- Output formatted in 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop3 modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Selectable asynchronous hardware conversion trigger.

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

## 9.1.3 Block Diagram

Figure 9-2 provides a block diagram of the ADC module

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

# 9.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

## 9.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

# 9.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

## 9.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

#### Chapter 11 Inter-Integrated Circuit (S08IICV1)

#### NOTES:

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 11-1. MC9S08QG8/4 Block Diagram Highlighting IIC Block and Pins

## 11.4.1.4 STOP Signal

The master can terminate the communication by generating a STOP signal to free the bus. However, the master may generate a START signal followed by a calling command without generating a STOP signal first. This is called repeated START. A STOP signal is defined as a low-to-high transition of SDA while SCL at logical 1 (see Figure 11-8).

The master can generate a STOP even if the slave has generated an acknowledge at which point the slave must release the bus.

## 11.4.1.5 Repeated START Signal

As shown in Figure 11-8, a repeated START signal is a START signal generated without first generating a STOP signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

## 11.4.1.6 Arbitration Procedure

The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a STOP condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

## 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-9). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

# Chapter 14 Serial Communications Interface (S08SCIV3)

# 14.1 Introduction

Figure 14-1 shows the MC9S08QG8/4 block diagram with the SCI highlighted.

# 14.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

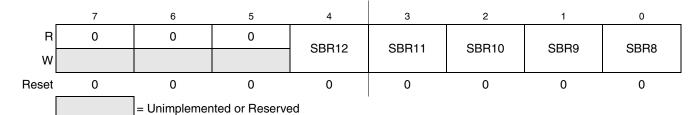

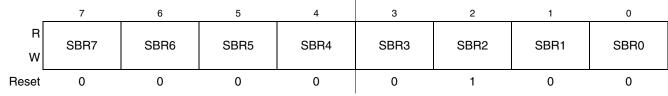

# 14.2.1 SCI Baud Rate Registers (SCIBDH, SCIBDL)

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCIBDH to buffer the high half of the new value and then write to SCIBDL. The working value in SCIBDH does not change until SCIBDL is written.

SCIBDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCIC2 are written to 1).

## Figure 14-5. SCI Baud Rate Register (SCIBDH)

Table 14-1. SCIBDH Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — These 13 bits are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/( $16 \times BR$ ). See also BR bits in Table 14-2. |

Figure 14-6. SCI Baud Rate Register (SCIBDL)

Timer/Pulse-Width Modulator (S08TPMV2)

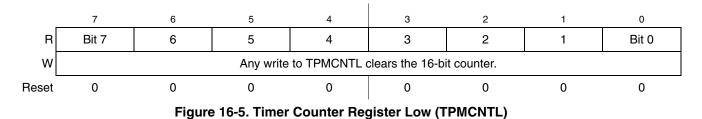

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

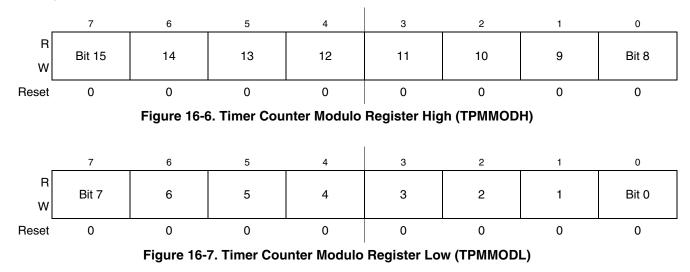

# 16.3.3 Timer Counter Modulo Registers (TPMMODH:TPMMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMMODH or TPMMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

#### Timer/Pulse-Width Modulator (S08TPMV2)

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMMODH:TPMMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMCNTH or TPMCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMCNTH or TPMCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

## 16.4.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

## 16.4.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMCnVH:TPMCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

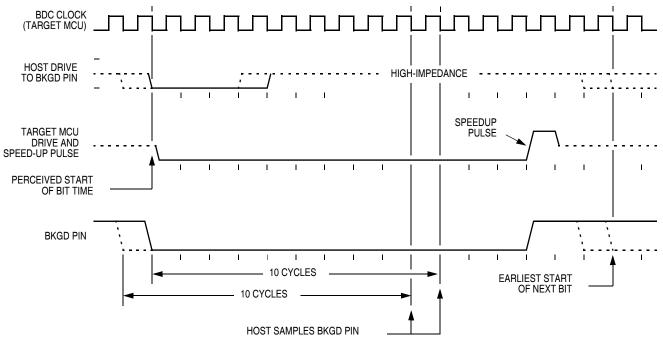

#### Development Support

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

# 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

## **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

NP

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

#### Development Support

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

# 17.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

**Appendix A Electrical Characteristics**

1. Not defined but normally MSB of character just received

1. Not defined but normally LSB of character just received

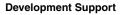

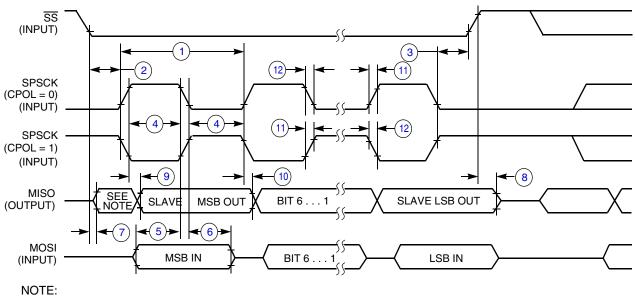

Figure A-16. SPI Slave Timing (CPHA = 1)

| Characteristic          | Conditions              | Symb                | Min | Typ <sup>1</sup> | Max  | Unit             | Comment                               |

|-------------------------|-------------------------|---------------------|-----|------------------|------|------------------|---------------------------------------|

| Conversion time         | Short sample (ADLSMP=0) | t <sub>ADC</sub>    |     | 20               |      | ADCK             | See                                   |

| (including sample time) | Long sample (ADLSMP=1)  |                     | _   | 40               | _    | cycles           | Table 9-12 for<br>conversion          |

| Sample time             | Short sample (ADLSMP=0) | t <sub>ADS</sub>    |     | 3.5              | —    | ADCK             | time variances                        |

|                         | Long sample (ADLSMP=1)  |                     | -   | 23.5             | —    | cycles           |                                       |

| Total unadjusted error  | 10 bit mode             | E <sub>TUE</sub>    | _   | ±1.5             | ±3.5 | LSB <sup>2</sup> | Includes                              |

|                         | 8 bit mode              |                     | _   | ±0.7             | ±1.5 |                  | quantization                          |

| Differential            | 10 bit mode             | DNL                 |     | ±0.5             | ±1.0 | LSB <sup>2</sup> | Monotonicity                          |

| non-linearity           | 8 bit mode              |                     | _   | ±0.3             | ±0.5 |                  | and no<br>missing codes<br>guaranteed |

| Integral non-linearity  | 10 bit mode             | INL                 | _   | ±0.5             | ±1.0 | LSB <sup>2</sup> |                                       |

|                         | 8 bit mode              |                     | _   | ±0.3             | ±0.5 |                  |                                       |

| Zero-scale error        | 10 bit mode             | E <sub>ZS</sub>     | _   | ±1.5             | ±2.1 | LSB <sup>2</sup> | $V_{ADIN} = V_{SS}$                   |

|                         | 8 bit mode              |                     |     | ±0.5             | ±0.7 |                  |                                       |

| Full-scale error        | 10 bit mode             | E <sub>FS</sub>     | 0   | ±1.0             | ±1.5 | LSB <sup>2</sup> | $V_{ADIN} = V_{DD}$                   |

|                         | 8 bit mode              |                     | 0   | ±0.5             | ±0.5 |                  |                                       |

| Quantization error      | 10 bit mode             | EQ                  |     | —                | ±0.5 | LSB <sup>2</sup> |                                       |

|                         | 8 bit mode              |                     | _   | —                | ±0.5 |                  |                                       |

| Input leakage error     | 10 bit mode             | E <sub>IL</sub>     | 0   | ±0.2             | ±4   | LSB <sup>2</sup> | Pad leakage <sup>3</sup> *            |

|                         | 8 bit mode              |                     | 0   | ±0.1             | ±1.2 |                  | R <sub>AS</sub>                       |

| Temp sensor<br>slope    | -40°C– 25°C             | m                   | _   | 1.646            | —    | mV/°C            |                                       |

|                         | 25°C– 85°C              |                     |     | 1.769            | —    |                  |                                       |

| Temp sensor<br>voltage  | 25°C                    | V <sub>TEMP25</sub> | _   | 701.2            | _    | mV               |                                       |

| Table A-14. 3 Volt 10-bit ADC Characteristics (c | continued) |

|--------------------------------------------------|------------|

|--------------------------------------------------|------------|

<sup>1</sup> Typical values assume V<sub>DD</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> 1 LSB = (V<sub>REFH</sub> - V<sub>REFL</sub>)/2<sup>N</sup>

<sup>3</sup> Based on input pad leakage current. Refer to pad electricals.