### NXP USA Inc. - MC9S08QG8CDTER Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg8cdter |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08QG8 Data Sheet

Covers MC9S08QG8 MC9S08QG4

> MC9S08QG8 Rev. 5 11/2009

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2007-2009. All rights reserved.

### PRELIMINARY

# **Section Number**

Title

### Page

| 11.4 | Functional Description                 |  |

|------|----------------------------------------|--|

|      | 11.4.1 IIC Protocol                    |  |

| 11.5 | Resets                                 |  |

| 11.6 | Interrupts                             |  |

|      | 11.6.1 Byte Transfer Interrupt         |  |

|      | 11.6.2 Address Detect Interrupt        |  |

|      | 11.6.3 Arbitration Lost Interrupt      |  |

| 11.7 | Initialization/Application Information |  |

# Chapter 12 Keyboard Interrupt (S08KBIV2)

| 12.1 | Introduction                                   | 173 |

|------|------------------------------------------------|-----|

|      | 12.1.1 Features                                | 175 |

|      | 12.1.2 Modes of Operation                      | 175 |

|      | 12.1.3 Block Diagram                           | 175 |

| 12.2 | External Signal Description                    | 176 |

| 12.3 | Register Definition                            | 176 |

|      | 12.3.1 KBI Status and Control Register (KBISC) | 176 |

|      | 12.3.2 KBI Pin Enable Register (KBIPE)         | 177 |

|      | 12.3.3 KBI Edge Select Register (KBIES)        | 177 |

| 12.4 | Functional Description                         | 178 |

|      | 12.4.1 Edge Only Sensitivity                   | 178 |

|      | 12.4.2 Edge and Level Sensitivity              | 178 |

|      | 12.4.3 KBI Pullup/Pulldown Resistors           |     |

|      | 12.4.4 KBI Initialization                      | 179 |

|      |                                                |     |

# Chapter 13 Modulo Timer (S08MTIMV1)

| Introduction                                       |                                                              |

|----------------------------------------------------|--------------------------------------------------------------|

| 13.1.1 MTIM/TPM Configuration Information          |                                                              |

| 13.1.2 Features                                    |                                                              |

| 13.1.3 Modes of Operation                          |                                                              |

| 13.1.4 Block Diagram                               |                                                              |

| External Signal Description                        |                                                              |

| Register Definition                                |                                                              |

| 13.3.1 MTIM Status and Control Register (MTIMSC)   |                                                              |

| 13.3.2 MTIM Clock Configuration Register (MTIMCLK) |                                                              |

| 13.3.3 MTIM Counter Register (MTIMCNT)             |                                                              |

| 13.3.4 MTIM Modulo Register (MTIMMOD)              |                                                              |

| Functional Description                             |                                                              |

| 13.4.1 MTIM Operation Example                      |                                                              |

|                                                    | <ul> <li>13.1.1 MTIM/TPM Configuration Information</li></ul> |

**Section Number**

### Title

Page

# Chapter 14 Serial Communications Interface (S08SCIV3)

| 14.1 | 1 Introduction                                  |  |

|------|-------------------------------------------------|--|

|      | 14.1.1 Features                                 |  |

|      | 14.1.2 Modes of Operation                       |  |

|      | 14.1.3 Block Diagram                            |  |

| 14.2 | 2 Register Definition                           |  |

|      | 14.2.1 SCI Baud Rate Registers (SCIBDH, SCIBHL) |  |

|      | 14.2.2 SCI Control Register 1 (SCIC1)           |  |

|      | 14.2.3 SCI Control Register 2 (SCIC2)           |  |

|      | 14.2.4 SCI Status Register 1 (SCIS1)            |  |

|      | 14.2.5 SCI Status Register 2 (SCIS2)            |  |

|      | 14.2.6 SCI Control Register 3 (SCIC3)           |  |

|      | 14.2.7 SCI Data Register (SCID)                 |  |

| 14.3 | 3 Functional Description                        |  |

|      | 14.3.1 Baud Rate Generation                     |  |

|      | 14.3.2 Transmitter Functional Description       |  |

|      | 14.3.3 Receiver Functional Description          |  |

|      | 14.3.4 Interrupts and Status Flags              |  |

| 14.4 | 4 Additional SCI Functions                      |  |

|      | 14.4.1 8- and 9-Bit Data Modes                  |  |

|      | 14.4.2 Stop Mode Operation                      |  |

|      | 14.4.3 Loop Mode                                |  |

|      | 14.4.4 Single-Wire Operation                    |  |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| Introduction                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1.2 Block Diagrams                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

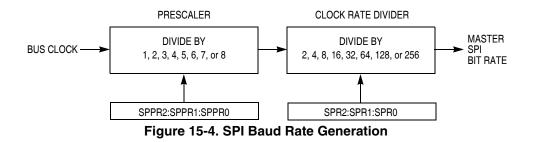

| 15.1.3 SPI Baud Rate Generation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| External Signal Description                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.1 SPSCK — SPI Serial Clock              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.2 MOSI — Master Data Out, Slave Data In |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.3 MISO — Master Data In, Slave Data Out |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.4 $\overline{\text{SS}}$ — Slave Select |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Modes of Operation                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3.1 SPI in Stop Modes                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Register Definition                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.1 SPI Control Register 1 (SPIC1)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.2 SPI Control Register 2 (SPIC2)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.3 SPI Baud Rate Register (SPIBR)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | <ul> <li>15.1.1 Features.</li> <li>15.1.2 Block Diagrams</li> <li>15.1.3 SPI Baud Rate Generation</li> <li>External Signal Description</li> <li>15.2.1 SPSCK — SPI Serial Clock.</li> <li>15.2.2 MOSI — Master Data Out, Slave Data In</li> <li>15.2.3 MISO — Master Data In, Slave Data Out</li> <li>15.2.4 SS — Slave Select</li> <li>Modes of Operation.</li> <li>15.3.1 SPI in Stop Modes</li> <li>Register Definition</li> <li>15.4.1 SPI Control Register 1 (SPIC1)</li> <li>15.4.2 SPI Control Register 2 (SPIC2)</li> </ul> |

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08QG8/4 are described in this section. Entry into each mode, exit from each mode, and functionality while in each mode are described.

# 3.2 Features

- Active background mode for code development

- Wait mode:

- CPU halts operation to conserve power

- System clocks running

- Full voltage regulation is maintained

- Stop modes: CPU and bus clocks stopped

- Stop1: Full powerdown of internal circuits for maximum power savings

- Stop2: Partial powerdown of internal circuits; RAM contents retained

- Stop3: All internal circuits powered for fast recovery; RAM and register contents are retained

# 3.3 Run Mode

Run is the normal operating mode for the MC9S08QG8/4. This mode is selected upon the MCU exiting reset if the BKGD/MS pin is high. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE:0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip debug module (DBG), provides the means for analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

- When the BKGD/MS pin is low during POR or immediately after issuing a background debug force reset (see 5.8.3, "System Background Debug Force Reset Register (SBDFR)")

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

Chapter 4 Memory Map and Register Definition

# 4.2 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the Freescale Semiconductor-provided equate file for the MC9S08QG8/4.

| Address<br>(High:Low) | Vector                       | Vector Name |

|-----------------------|------------------------------|-------------|

| 0xFFC0:FFC1           | Unused Vector Space          |             |

| <b>\$</b>             | (available for user program) |             |

| 0xFFCE:FFCF           |                              |             |

| 0xFFD0:FFD1           | RTI                          | Vrti        |

| 0xFFD2:FFD3           | Reserved                     | —           |

| 0xFFD4:FFD5           | Reserved                     | —           |

| 0xFFD6:FFD7           | ACMP                         | Vacmp       |

| 0xFFD8:FFD9           | ADC Conversion               | Vadc        |

| 0xFFDA:FFDB           | KBI Interrupt                | Vkeyboard   |

| 0xFFDC:FFDD           | IIC                          | Viic        |

| 0xFFDE:FFDF           | SCI Transmit                 | Vscitx      |

| 0xFFE0:FFE1           | SCI Receive                  | Vscirx      |

| 0xFFE2:FFE3           | SCI Error                    | Vscierr     |

| 0xFFE4:FFE5           | SPI                          | Vspi        |

| 0xFFE6:FFE7           | MTIM Overflow                | Vmtim       |

| 0xFFE8:FFE9           | Reserved                     | _           |

| 0xFFEA:FFEB           | Reserved                     | _           |

| 0xFFEC:FFED           | Reserved                     | _           |

| 0xFFEE:FFEF           | Reserved                     | _           |

| 0xFFF0:FFF1           | TPM Overflow                 | Vtpmovf     |

| 0xFFF2:FFF3           | TPM Channel 1                | Vtpmch1     |

| 0xFFF4:FFF5           | TPM Channel 0                | Vtpmch0     |

| 0xFFF6:FFF7           | Reserved                     | —           |

| 0xFFF8:FFF9           | Low Voltage Detect           | Vlvd        |

| 0xFFFA:FFFB           | IRQ                          | Virq        |

| 0xFFFC:FFFD           | SWI                          | Vswi        |

| 0xFFFE:FFFF           | Reset                        | Vreset      |

### Table 4-1. Reset and Interrupt Vectors

# 6.3 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- In stop1 mode, all internal registers including parallel I/O control and data registers are powered off. Each of the pins assumes its default reset state (output buffer and internal pullup disabled). Upon exit from stop1, all pins must be re-configured the same as if the MCU had been reset by POR.

- Stop2 mode is a partial power-down mode, whereby latches maintain the pin state as before the STOP instruction was executed. CPU register status and the state of I/O registers must be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user must examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, and peripherals previously enabled will require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access of pins is now permitted again in the user application program.

- In stop3 mode, all pin states are maintained because internal logic stays powered up. Upon recovery, all pin functions are the same as before entering stop3.

# 6.4 Parallel I/O Registers

### 6.4.1 Port A Registers

This section provides information about the registers associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory Map and Register Definition," for the absolute address assignments for all parallel I/O. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

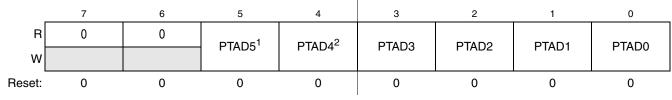

### 6.4.1.1 Port A Data (PTAD)

### Figure 6-2. Port A Data Register (PTAD)

<sup>1</sup> Reads of bit PTAD5 always return the pin value of PTA5, regardless of the value stored in bit PTADD5.

<sup>2</sup> Reads of bit PTAD4 always return the contents of PTAD4, regardless of the value stored in bit PTADD4.

\_\_\_\_

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                            | Affect<br>on CCR |                                                |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|------------------|------------------------------------------------|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    | βά<br>Μ                                             |                                                                                  | ර                               | Dotano                                           | VH               | INZC                                           |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓-               | -:::                                           |

| SWI                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + \$0001<br>Push (PCL); SP $\leftarrow$ (SP) - \$0001<br>Push (PCH); SP $\leftarrow$ (SP) - \$0001<br>Push (X); SP $\leftarrow$ (SP) - \$0001<br>Push (A); SP $\leftarrow$ (SP) - \$0001<br>Push (CCR); SP $\leftarrow$ (SP) - \$0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | sssssvvfppp                                      |                  | 1                                              |

| ТАР                                                                                                             | Transfer Accumulator to CCR $CCR \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | p                                                | ¢¢               | $\uparrow \uparrow \uparrow \uparrow \uparrow$ |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low) $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 97                                                                               | 1                               | р                                                |                  |                                                |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                |                  |                                                |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | Test for Negative or Zero (M) - \$00<br>(A) - \$00<br>(X) - \$00<br>(M) - \$00<br>(M) - \$00<br>(M) - \$00                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                | 0 —              | - \$ \$ -                                      |

| тѕх                                                                                                             | Transfer SP to Index Reg.<br>H:X $\leftarrow$ (SP) + \$0001                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 95                                                                               | 2                               | fp                                               |                  |                                                |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | p                                                |                  |                                                |

| Table 7-2 Instrue | ction Set Summary | (Sheet 8 of 9) |

|-------------------|-------------------|----------------|

|-------------------|-------------------|----------------|

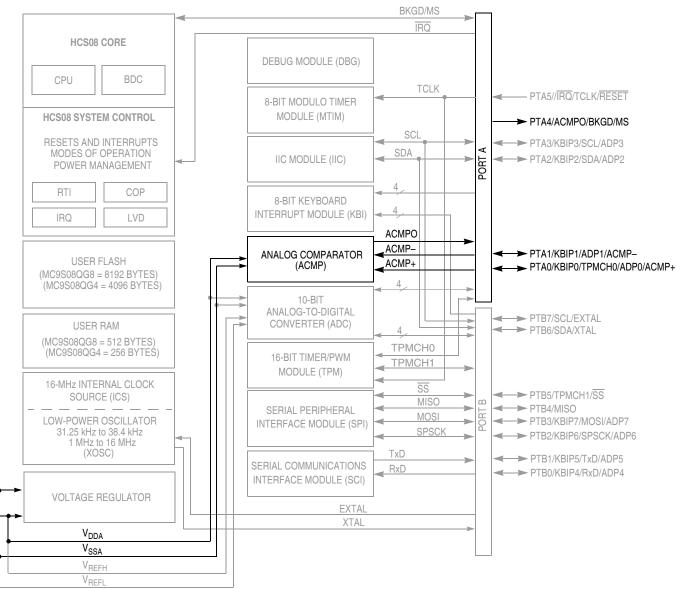

#### Chapter 8 Analog Comparator (S08ACMPV2)

#### NOTES:

V<sub>SS</sub>

$V_{DD}$

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

### Figure 8-1. MC9S08QG8/4 Block Diagram Highlighting ACMP Block and Pins

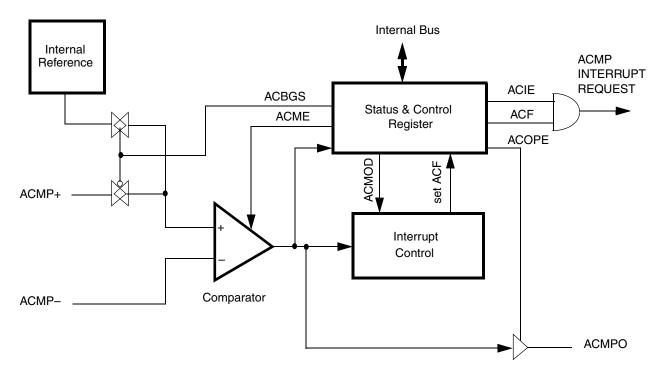

Analog Comparator (S08ACMPV2)

Figure 8-2. Analog Comparator (ACMP) Block Diagram

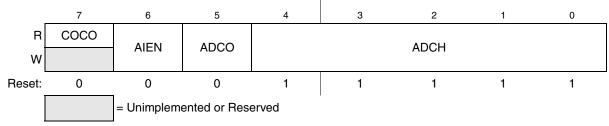

| Figure 9-3. Status | and Control | Register | (ADCSC1) |

|--------------------|-------------|----------|----------|

|--------------------|-------------|----------|----------|

| Table 9-3. | ADCSC1 | Register | Field | Descriptions |

|------------|--------|----------|-------|--------------|

|------------|--------|----------|-------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                           |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while       AIEN is high, an interrupt is asserted.         0       Conversion complete interrupt disabled         1       Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                   |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 9-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversion are not enabled because the module automatically enters a low-power state when a conversion completes. |

### Figure 9-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

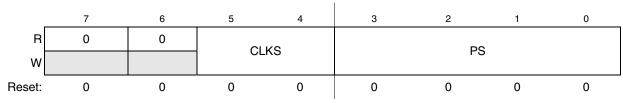

### 13.3.2 MTIM Clock Configuration Register (MTIMCLK)

MTIMCLK contains the clock select bits (CLKS) and the prescaler select bits (PS).

Figure 13-5. MTIM Clock Configuration Register

### Table 13-3. MTIM Clock Configuration Register Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6         | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:4<br>CLKS | Clock Source Select — These two read/write bits select one of four different clock sources as the input to the MTIM prescaler. Changing the clock source while the counter is active does not clear the counter. The count continues with the new clock source. Reset clears CLKS to 000.         00       Encoding 0. Bus clock (BUSCLK)         01       Encoding 1. Fixed-frequency clock (XCLK)         10       Encoding 3. External source (TCLK pin), falling edge         11       Encoding 4. External source (TCLK pin), rising edge         All other encodings default to the bus clock (BUSCLK).                                                                                                                              |

| 3:0<br>PS   | Clock Source Prescaler — These four read/write bits select one of nine outputs from the 8-bit prescaler. Changing<br>the prescaler value while the counter is active does not clear the counter. The count continues with the new<br>prescaler value. Reset clears PS to 0000.<br>0000 Encoding 0. MTIM clock source ÷ 1<br>0001 Encoding 1. MTIM clock source ÷ 2<br>0010 Encoding 2. MTIM clock source ÷ 4<br>0011 Encoding 3. MTIM clock source ÷ 8<br>0100 Encoding 4. MTIM clock source ÷ 16<br>0101 Encoding 5. MTIM clock source ÷ 32<br>0110 Encoding 6. MTIM clock source ÷ 64<br>0111 Encoding 7. MTIM clock source ÷ 128<br>1000 Encoding 8. MTIM clock source ÷ 256<br>All other encodings default to MTIM clock source ÷ 256. |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.1 Introduction

Figure 15-1 shows the MC9S08QG8/4 block diagram with the SPI highlighted.

Serial Peripheral Interface (S08SPIV3)

# 15.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

# 15.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

# 15.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 15.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 15.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

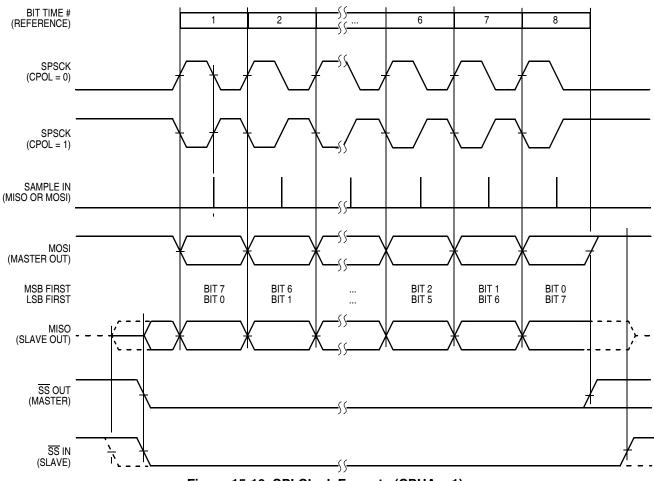

MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 15-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

Timer/Pulse-Width Modulator (S08TPMV2)

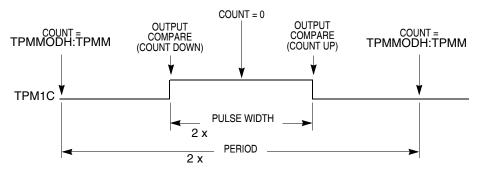

# 16.4.3 Center-Aligned PWM Mode

This type of PWM output uses the up-/down-counting mode of the timer counter (CPWMS = 1). The output compare value in TPMCnVH:TPMCnVL determines the pulse width (duty cycle) of the PWM signal and the period is determined by the value in TPMMODH:TPMMODL. TPMMODH:TPMMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

### period = 2 x (TPMMODH:TPMMODL); for TPMMODH:TPMMODL = 0x0001–0x7FFF Eqn. 16-2

If the channel value register TPMCnVH:TPMCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMCnVH:TPMCnVL is a positive value (bit 15 clear) and is greater than the (nonzero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if generation of 100% duty cycle is not necessary). This is not a significant limitation because the resulting period is much longer than required for normal applications.

TPMMODH: TPMMODL = 0x0000 is a special case that should not be used with center-aligned PWM mode. When CPWMS = 0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS = 1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

Figure 16-12 shows the output compare value in the TPM channel registers (multiplied by 2), which determines the pulse width (duty cycle) of the CPWM signal. If ELSnA = 0, the compare match while counting up forces the CPWM output signal low and a compare match while counting down forces the output high. The counter counts up until it reaches the modulo setting in TPMMODH:TPMMODL, then counts down until it reaches zero. This sets the period equal to two times TPMMODH:TPMMODL.

Figure 16-12. CPWM Period and Pulse Width (ELSnA = 0)

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin transitions are lined up at the same system clock edge. This type of PWM is also required for some types of motor drives.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMMODH, TPMMODL, TPMCnVH, and TPMCnVL, actually write to buffer registers. Values are

Development Support

# 17.1.2 Features

Features of the BDC module include:

- Single pin for mode selection and background communications

- BDC registers are not located in the memory map

- SYNC command to determine target communications rate

- Non-intrusive commands for memory access

- Active background mode commands for CPU register access

- GO and TRACE1 commands

- BACKGROUND command can wake CPU from stop or wait modes

- One hardware address breakpoint built into BDC

- Oscillator runs in stop mode, if BDC enabled

- COP watchdog disabled while in active background mode

Features of the ICE system include:

- Two trigger comparators: Two address + read/write (R/W) or one full address + data + R/W

- Flexible 8-word by 16-bit FIFO (first-in, first-out) buffer for capture information:

- Change-of-flow addresses or

- Event-only data

- Two types of breakpoints:

- Tag breakpoints for instruction opcodes

- Force breakpoints for any address access

- Nine trigger modes:

- Basic: A-only, A OR B

- Sequence: A then B

- Full: A AND B data, A AND NOT B data

- Event (store data): Event-only B, A then event-only B

- Range: Inside range (A  $\leq$  address  $\leq$  B), outside range (address < A or address > B)

# 17.2 Background Debug Controller (BDC)

All MCUs in the HCS08 Family contain a single-wire background debug interface that supports in-circuit programming of on-chip nonvolatile memory and sophisticated non-intrusive debug capabilities. Unlike debug interfaces on earlier 8-bit MCUs, this system does not interfere with normal application resources. It does not use any user memory or locations in the memory map and does not share any on-chip peripherals.

BDC commands are divided into two groups:

• Active background mode commands require that the target MCU is in active background mode (the user program is not running). Active background mode commands allow the CPU registers to be

#### Development Support

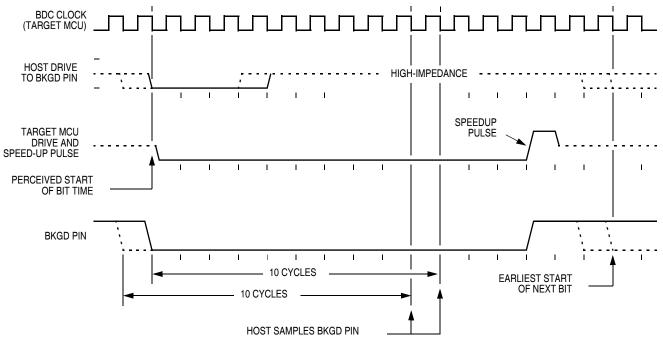

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

### 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- A DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|       | MILLIMETERS                               |       |       | INCHES                            |                           | MILLIMETERS |             |             | NCHES |

|-------|-------------------------------------------|-------|-------|-----------------------------------|---------------------------|-------------|-------------|-------------|-------|

| DIM   | MIN                                       | MAX   | MIN   | MAX                               | DIM                       | MIN         | MAX         | MIN         | MAX   |

| A     | 18.80                                     | 19.55 | 0.740 | 0.770                             |                           |             |             |             |       |

| В     | 6.35                                      | 6.85  | 0.250 | 0.270                             |                           |             |             |             |       |

| С     | 3.69                                      | 4.44  | 0.145 | 0.175                             |                           |             |             |             |       |

| D     | 0.39                                      | 0.53  | 0.015 | 0.021                             |                           |             |             |             |       |

| F     | 1.02                                      | 1.77  | 0.040 | 0.070                             |                           |             |             |             |       |

| G     | 2.54                                      | BSC   | 0.1   | IOO BSC                           |                           |             |             |             |       |

| Н     | 1.27 BSC 0.                               |       | 0.0   | )50 BSC                           |                           |             |             |             |       |

| J     | 0.21                                      | 0.38  | 0.008 | 0.015                             |                           |             |             |             |       |

| K     | 2.80                                      | 3.30  | 0.110 | 0.130                             |                           |             |             |             |       |

| L     | 7.50                                      | 7.74  | 0.295 | 0.305                             |                           |             |             |             |       |

| М     | 0.                                        | 10°   | 0.    | 10*                               |                           |             |             |             |       |

| S     | 0.51                                      | 1.01  | 0.020 | 0.040                             |                           |             |             |             |       |

| © FF  | © FREESCALE SEMICONDUCTOR, INC. MECHANICA |       |       | L OUTLINE PRINT VERSION NOT TO SC |                           |             | DT TO SCALE |             |       |

| TITLE | TITLE:                                    |       |       |                                   | DOCUMENT NO: 98ASB42431B  |             |             | REV: T      |       |

|       | 16 LD PDIP                                |       |       |                                   | CASE NUMBER: 648–08 19 MA |             |             | 19 MAY 2005 |       |

|       |                                           |       |       | STANDARD: NON-JEDEC               |                           |             |             |             |       |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- $\triangle$  DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS). STYLE 1:

| PIN | 1. | AC | ΙN   |  |

|-----|----|----|------|--|

|     | 2. | DC | + IN |  |

|     | З. | DC | — IN |  |

|     | 4. | AC | ΙN   |  |

- 5. GROUND

- OUTPUT

AUXILIARY

- 8. VCC

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |  | L OUTLINE           | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|--|---------------------|------------------|-------------|

| TITLE:                                                  |  | DOCUMENT NO         | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               |  | CASE NUMBER: 626-06 |                  | 19 MAY 2005 |

|                                                         |  | STANDARD: NON-JEDEC |                  |             |