Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | 508                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 20MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 4                                                          |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | A/D 4x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                              |

| Supplier Device Package    | 8-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qg8mdne |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                            | Register Name | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

|------------------------------------|---------------|--------|-------|-------|-------|-------|-------|-----|-------|

| 0x00 <b>3F</b>                     | MTIMMOD       |        |       |       | M     | DD    |       |     |       |

| 0x00 <b>40</b>                     | TPMSC         | TOF    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1 | PS0   |

| 0x00 <b>41</b>                     | TPMCNTH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>42</b>                     | TPMCNTL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>43</b>                     | TPMMODH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>44</b>                     | TPMMODL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>45</b>                     | TPMC0SC       | CH0F   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0   | 0     |

| 0x00 <b>46</b>                     | TPMC0VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>47</b>                     | TPMC0VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>48</b>                     | TPMC1SC       | CH1F   | CH1IE | MS1B  | MS1A  | ELS1B | ELS1A | 0   | 0     |

| 0x00 <b>49</b>                     | TPMC1VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9   | Bit 8 |

| 0x00 <b>4A</b>                     | TPMC1VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>4B</b> –<br>0x00 <b>5F</b> | Reserved      |        | _     | _     |       |       |       |     | _     |

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| Address           | Register Name | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

|-------------------|---------------|---------|--------|---------|-------|-------|--------|--------|-------|

| 0x1800            | SRS           | POR     | PIN    | COP     | ILOP  | ILAD  | 0      | LVD    | 0     |

| 0x1801            | SBDFR         | 0       | 0      | 0       | 0     | 0     | 0      | 0      | BDFR  |

| 0x1802            | SOPT1         | COPE    | COPT   | STOPE   | _     | 0     | 0      | BKGDPE | RSTPE |

| 0x1803            | SOPT2         | COPCLKS | 0      | 0       | 0     | 0     | 0      | IICPS  | ACIC  |

| 0x <b>1804</b>    | Reserved      | —       | _      | _       | _     | _     | —      | —      | —     |

| 0x1805            | Reserved      | _       | _      | _       | -     | -     | —      | —      | —     |

| 0x1806            | SDIDH         | _       | _      | _       | _     | ID11  | ID10   | ID9    | ID8   |

| 0x1807            | SDIDL         | ID7     | ID6    | ID5     | ID4   | ID3   | ID2    | ID1    | ID0   |

| 0x1808            | SRTISC        | RTIF    | RTIACK | RTICLKS | RTIE  | 0     | RTIS   |        |       |

| 0x1809            | SPMSC1        | LVDF    | LVDACK | LVDIE   | LVDRE | LVDSE | LVDE   | 0      | BGBE  |

| 0x180A            | SPMSC2        | 0       | 0      | 0       | PDF   | PPDF  | PPDACK | PDC    | PPDC  |

| 0x180B            | Reserved      | —       | —      | -       | _     | -     | —      | _      | -     |

| 0x180C            | SPMSC3        | LVWF    | LVWACK | LVDV    | LVWV  | -     | —      | _      | -     |

| 0x180D–<br>0x180F | Reserved      |         |        |         |       |       | _      |        | _     |

| 0x1810            | DBGCAH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1811            | DBGCAL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1812            | DBGCBH        | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1813            | DBGCBL        | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

| 0x1814            | DBGFH         | Bit 15  | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

| 0x1815            | DBGFL         | Bit 7   | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

### Table 4-3. High-Page Register Summary

**Chapter 4 Memory Map and Register Definition**

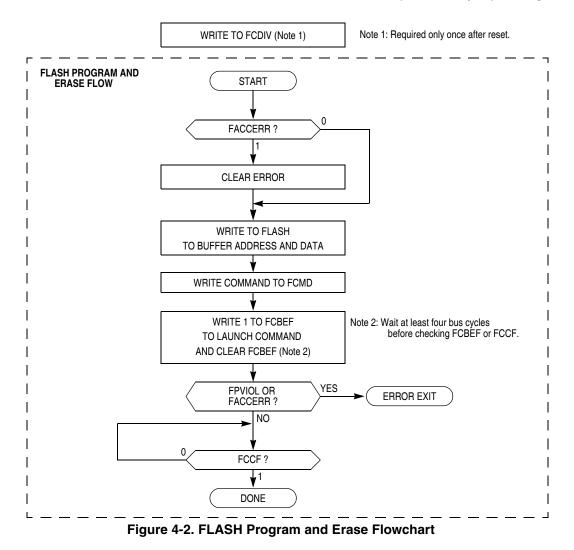

## 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08QG8/4 includes a system to protect against low voltage conditions to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC3. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop1 or stop2, and the current consumption in stop3 with the LVD enabled will be greater.

## 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

## 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured using SPMSC1 for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF in SPMSC1 will be set and an LVD interrupt request will occur.

## 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, but is above, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC3.

## 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1-kHz internal clock or an external clock if available. External clock input requires the XOSC module; consult Table 1-1 to see if your MCU contains this module. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Either RTI clock source can be used when the MCU is in run, wait or stop3 mode. When using the external oscillator in stop3, it must be enabled in stop (EREFSTEN = 1) and configured for low frequency operation

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | Cycles                               | Cyc-by-Cyc<br>Details                                                         |     | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------|-----|-----------------|

| 1 Onit                                                                                                          |                                                                                                          | Ad                                                                                                       |                                                                                  | G                                    |                                                                               | VH  | INZC            |

| BCLR n,opr8a                                                                                                    | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp |     |                 |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BEQ <i>rel</i>                                                                                                  | Branch if Equal (if Z = 1)                                                                               | REL                                                                                                      | 27 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BGE rel                                                                                                         | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                                   | fpppp                                                                         |     |                 |

| BGT <i>rel</i>                                                                                                  | Branch if Greater Than (if $Z   (N \oplus V) = 0$ ) (Signed)                                             | REL                                                                                                      | 92 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BHI <i>rel</i>                                                                                                  | Branch if Higher (if C   Z = 0)                                                                          | REL                                                                                                      | 22 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BIH <i>rel</i>                                                                                                  | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BIL <i>rel</i>                                                                                                  | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh ll<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4      | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp                      | 0 - | - \$ \$ -       |

| BLE rel                                                                                                         | Branch if Less Than or Equal To (if Z I (N $\oplus$ V) = 1) (Signed)                                     | REL                                                                                                      | 93 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BLO <i>rel</i>                                                                                                  | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                              | REL                                                                                                      | 25 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BLS <i>rel</i>                                                                                                  | Branch if Lower or Same (if $C \mid Z = 1$ )                                                             | REL                                                                                                      | 23 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BLT <i>rel</i>                                                                                                  | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BMI <i>rel</i>                                                                                                  | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BMS rel                                                                                                         | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| BNE <i>rel</i>                                                                                                  | Branch if Not Equal (if $Z = 0$ )                                                                        | REL                                                                                                      | 26 rr                                                                            | 3                                    | ppp                                                                           |     |                 |

| BPL <i>rel</i>                                                                                                  | Branch if Plus (if N = 0)                                                                                | REL                                                                                                      | 2A rr                                                                            | 3                                    | qqq                                                                           |     |                 |

| Table 7-2. | Instruction | Set | Summary | (Sheet 2 | of 9) |

|------------|-------------|-----|---------|----------|-------|

|------------|-------------|-----|---------|----------|-------|

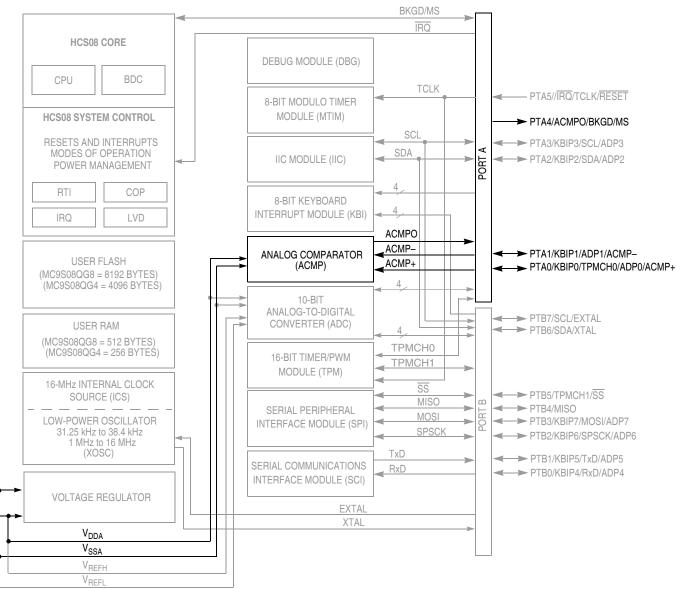

#### Chapter 8 Analog Comparator (S08ACMPV2)

#### NOTES:

V<sub>SS</sub>

$V_{DD}$

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 8-1. MC9S08QG8/4 Block Diagram Highlighting ACMP Block and Pins

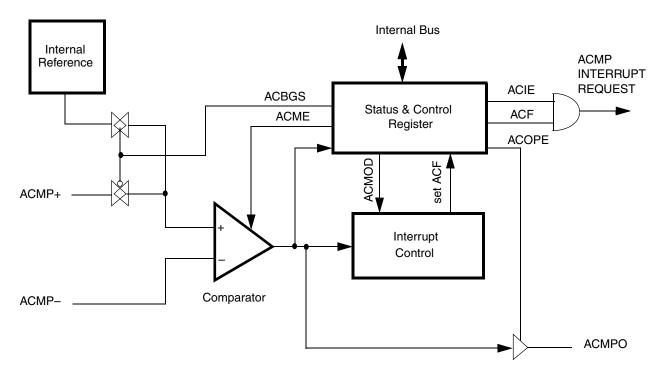

Analog Comparator (S08ACMPV2)

Figure 8-2. Analog Comparator (ACMP) Block Diagram

| Table 9-8. | Input | <b>Clock Select</b> |

|------------|-------|---------------------|

|------------|-------|---------------------|

| ADICLK | Selected Clock Source      |

|--------|----------------------------|

| 00     | Bus clock                  |

| 01     | Bus clock divided by 2     |

| 10     | Alternate clock (ALTCLK)   |

| 11     | Asynchronous clock (ADACK) |

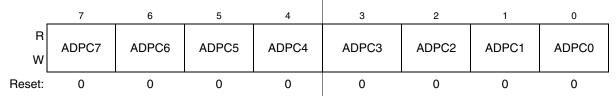

### 9.3.8 Pin Control 1 Register (APCTL1)

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.<br>0 AD7 pin I/O control enabled<br>1 AD7 pin I/O control disabled                                 |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

### Table 9-9. APCTL1 Register Field Descriptions

## 10.1.3 Features

Key features of the ICS module are:

- Frequency-locked loop (FLL) is trimmable for accuracy

- 0.2% resolution using internal 32 kHz reference

- 2% deviation over voltage and temperature using internal 32 kHz reference

- External reference clock up to 5 MHz can be used to control the FLL

- 3 bit select for reference divider is provided

- Internal reference clock has 9 trim bits available

- Internal or external reference clock can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2 bit select for clock divider is provided

- Allowable dividers are: 1, 2, 4, 8

- BDC clock is provided as a constant divide by 2 of the DCO output

- Control signals for a low power oscillator as the external reference clock are provided — HGO, RANGE, EREFS, ERCLKEN, EREFSTEN

- FLL engaged internal mode is automatically selected out of reset

### 10.1.4 Modes of Operation

The ICS features the following modes of operation: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

## 10.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

## 10.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

### 11.1.2 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

### 11.1.3 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop2 will reset the register contents.

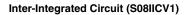

Keyboard Interrupts (S08KBIV2)

Figure 12-2. KBI Block Diagram

## 12.2 External Signal Description

The KBI input pins can be used to detect either falling edges, or both falling edge and low level interrupt requests. The KBI input pins can also be used to detect either rising edges, or both rising edge and high level interrupt requests.

The signal properties of KBI are shown in Table 12-1.

Table 12-1. Signal Properties

| Signal | Function                | I/O |

|--------|-------------------------|-----|

| KBIPn  | Keyboard interrupt pins | I   |

## 12.3 Register Definition

The KBI includes three registers:

- An 8-bit pin status and control register.

- An 8-bit pin enable register.

- An 8-bit edge select register.

Refer to the direct-page register summary in the Memory chapter for the absolute address assignments for all KBI registers. This section refers to registers and control bits only by their names.

Some MCUs may have more than one KBI, so register names include placeholder characters to identify which KBI is being referenced.

## 12.3.1 KBI Status and Control Register (KBISC)

KBISC contains the status flag and control bits, which are used to configure the KBI.

Modulo Timer (S08MTIMV1)

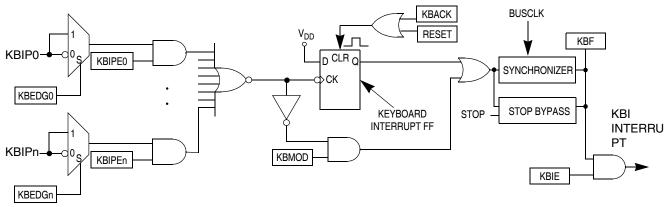

## 13.3.1 MTIM Status and Control Register (MTIMSC)

MTIMSC contains the overflow status flag and control bits which are used to configure the interrupt enable, reset the counter, and stop the counter.

### Figure 13-4. MTIM Status and Control Register

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF  | <ul> <li>MTIM Overflow Flag — This read-only bit is set when the MTIM counter register overflows to \$00 after reaching the value in the MTIM modulo register. Clear TOF by reading the MTIMSC register while TOF is set, then writing a 0 to TOF. TOF is also cleared when TRST is written to a 1 or when any value is written to the MTIMMOD register.</li> <li>0 MTIM counter has not reached the overflow value in the MTIM modulo register.</li> <li>1 MTIM counter has reached the overflow value in the MTIM modulo register.</li> </ul> |

| 6<br>TOIE | <ul> <li>MTIM Overflow Interrupt Enable — This read/write bit enables MTIM overflow interrupts. If TOIE is set, then an interrupt is generated when TOF = 1. Reset clears TOIE. Do not set TOIE if TOF = 1. Clear TOF first, then set TOIE.</li> <li>0 TOF interrupts are disabled. Use software polling.</li> <li>1 TOF interrupts are enabled.</li> </ul>                                                                                                                                                                                     |

| 5<br>TRST | <ul> <li>MTIM Counter Reset — When a 1 is written to this write-only bit, the MTIM counter register resets to \$00 and TOF is cleared. Reading this bit always returns 0.</li> <li>0 No effect. MTIM counter remains at current state.</li> <li>1 MTIM counter is reset to \$00.</li> </ul>                                                                                                                                                                                                                                                     |

| 4<br>TSTP | <ul> <li>MTIM Counter Stop — When set, this read/write bit stops the MTIM counter at its current value. Counting resumes from the current value when TSTP is cleared. Reset sets TSTP to prevent the MTIM from counting.</li> <li>0 MTIM counter is active.</li> <li>1 MTIM counter is stopped.</li> </ul>                                                                                                                                                                                                                                      |

| 3:0       | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

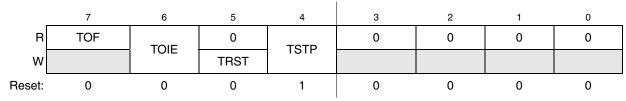

## 14.1.3 Block Diagram

Figure 14-3 shows the transmitter portion of the SCI. (Figure 14-4 shows the receiver portion of the SCI.)

Figure 14-3. SCI Transmitter Block Diagram

Serial Communications Interface (S08SCIV3)

# 14.3 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

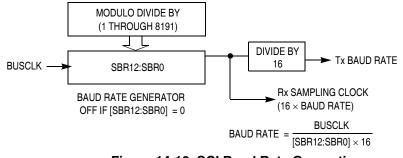

## 14.3.1 Baud Rate Generation

As shown in Figure 14-13, the clock source for the SCI baud rate generator is the bus-rate clock.

Figure 14-13. SCI Baud Rate Generation

SCI communications require the transmitter and receiver (which typically derive baud rates from independent clock sources) to use the same baud rate. Allowed tolerance on this baud frequency depends on the details of how the receiver synchronizes to the leading edge of the start bit and how bit sampling is performed.

The MCU resynchronizes to bit boundaries on every high-to-low transition, but in the worst case, there are no such transitions in the full 10- or 11-bit time character frame so any mismatch in baud rate is accumulated for the whole character time. For a Freescale Semiconductor SCI system whose bus frequency is driven by a crystal, the allowed baud rate mismatch is about  $\pm 4.5$  percent for 8-bit data format and about  $\pm 4$  percent for 9-bit data format. Although baud rate modulo divider settings do not always produce baud rates that exactly match standard rates, it is normally possible to get within a few percent, which is acceptable for reliable communications.

## 14.3.2 Transmitter Functional Description

This section describes the overall block diagram for the SCI transmitter, as well as specialized functions for sending break and idle characters. The transmitter block diagram is shown in Figure 14-3.

The transmitter output (TxD) idle state defaults to logic high (TXINV = 0 following reset). The transmitter output is inverted by setting TXINV = 1. The transmitter is enabled by setting the TE bit in SCIC2. This queues a preamble character that is one full character frame of the idle state. The transmitter then remains idle until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCID).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0,

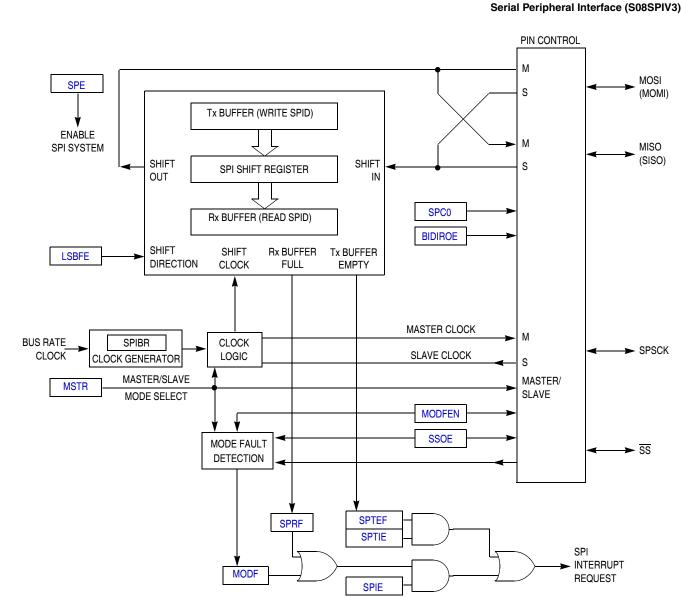

Figure 15-3. SPI Module Block Diagram

## 15.1.3 SPI Baud Rate Generation

As shown in Figure 15-4, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

# Chapter 16 Timer/Pulse-Width Modulator (S08TPMV2)

# 16.1 Introduction

Figure 16-1 shows the MC9S08QG8/4 block diagram with the TPM highlighted.

## 16.1.1 ACMP/TPM Configuration Information

The ACMP module can be configured to connect the output of the analog comparator to TPM input capture channel 0 by setting ACIC in SOPT2. With ACIC set, the TPMCH0 pin is not available externally regardless of the configuration of the TPM module.

## 16.1.2 MTIM/TPM Configuration Information

The external clock for the TPM module, TPMCLK, is selected by setting CLKS[B:A] = 1:1 in TPMSC, which selects the TCLK pin input. The TCLK input on PTA5 can be enabled as external clock inputs to both the MTIM and TPM modules simultaneously.

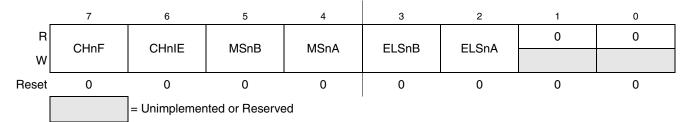

## 16.3.4 Timer Channel n Status and Control Register (TPMCnSC)

TPMCnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

### Figure 16-8. Timer Channel n Status and Control Register (TPMCnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | <ul> <li>Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.</li> <li>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.</li> <li>No input capture or output compare event occurred on channel n</li> </ul> |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>0 Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 16-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 16-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 16-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin.                                                                                                                                                                                                                                                                                                                                                                                              |

### Table 16-4. TPMCnSC Register Field Descriptions

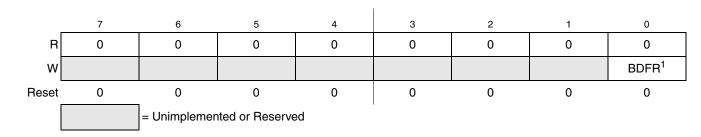

<sup>1</sup> BDFR is writable only through serial background mode debug commands, not from user programs.

#### Figure 17-6. System Background Debug Force Reset Register (SBDFR)

#### Table 17-3. SBDFR Register Field Description

| Field     | Description                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial active background mode command such as WRITE_BYTE allows an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

### 17.4.3 DBG Registers and Control Bits

The debug module includes nine bytes of register space for three 16-bit registers and three 8-bit control and status registers. These registers are located in the high register space of the normal memory map so they are accessible to normal application programs. These registers are rarely if ever accessed by normal user application programs with the possible exception of a ROM patching mechanism that uses the breakpoint logic.

### 17.4.3.1 Debug Comparator A High Register (DBGCAH)

This register contains compare value bits for the high-order eight bits of comparator A. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.2 Debug Comparator A Low Register (DBGCAL)

This register contains compare value bits for the low-order eight bits of comparator A. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.3 Debug Comparator B High Register (DBGCBH)

This register contains compare value bits for the high-order eight bits of comparator B. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.4 Debug Comparator B Low Register (DBGCBL)

This register contains compare value bits for the low-order eight bits of comparator B. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

Appendix A Electrical Characteristics

# A.12 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

# A.12.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter           | Symbol       | Conditions                                                             | Frequency      | f <sub>OSC</sub> /f <sub>BUS</sub> | Level <sup>1</sup><br>(Max) | Unit |

|---------------------|--------------|------------------------------------------------------------------------|----------------|------------------------------------|-----------------------------|------|

|                     | $V_{RE_TEM}$ | $V_{DD} = 3.3 V$<br>$T_{A} = +25^{\circ}C$<br>package type<br>16 TSSOP | 0.15 – 50 MHz  | 4-MHz crystal<br>10-MHz bus        | TBD                         | dBμV |

|                     |              |                                                                        | 50 – 150 MHz   |                                    | TBD                         |      |

| Radiated emissions, |              |                                                                        | 150 – 500 MHz  |                                    | TBD                         |      |

| electric field      |              |                                                                        | 500 – 1000 MHz |                                    | TBD                         |      |

|                     |              |                                                                        | IEC Level      |                                    | TBD                         | —    |

|                     |              |                                                                        | SAE Level      |                                    | TBD                         | _    |

Table A-16. Radiated Emissions, Electric Field

<sup>1</sup> Data based on qualification test results.

## A.12.2 Conducted Transient Susceptibility

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method. The conducted susceptibility is determined by injecting the transient susceptibility signal on each pin of the microcontroller. The transient waveform and injection methodology is based on IEC 61000-4-4 (EFT/B). The transient voltage required to cause performance degradation on any pin in the tested configuration is greater than or equal to the reported levels unless otherwise indicated by footnotes below Table A-17.

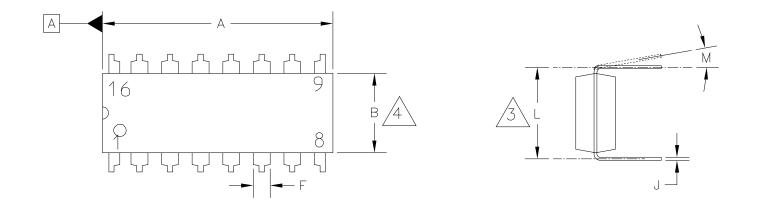

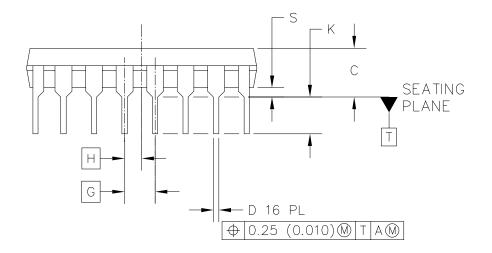

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. | MECHANICAL | OUTLINE             | PRINT VERSION NOT TO SCALE |             |  |

|---------------------------------------------------------|------------|---------------------|----------------------------|-------------|--|

| TITLE:                                                  | Γ          | DOCUMENT NO         | : 98ASB42431B              | RE∨: T      |  |

| 16 ID PDIP                                              | C          | CASE NUMBER: 648-08 |                            | 19 MAY 2005 |  |

|                                                         | 5          | STANDARD: NO        | N-JEDEC                    |             |  |