# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 12                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-VQFN Exposed Pad                                                   |

| Supplier Device Package    | 16-QFN-EP (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qg8mffe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

### Title

Page

### Chapter 6 Parallel Input/Output Control

| 6.1 | Port Data and Data Direction                        |  |

|-----|-----------------------------------------------------|--|

| 6.2 | Pin Control — Pullup, Slew Rate, and Drive Strength |  |

| 6.3 | Pin Behavior in Stop Modes                          |  |

| 6.4 | Parallel I/O Registers                              |  |

|     | 6.4.1 Port A Registers                              |  |

|     | 6.4.2 Port A Control Registers                      |  |

|     | 6.4.3 Port B Registers                              |  |

|     | 6.4.4 Port B Control Registers                      |  |

### Chapter 7 Central Processor Unit (S08CPUV2)

| 7.1 | Introdu | ction                           | 87 |

|-----|---------|---------------------------------|----|

|     | 7.1.1   | Features                        | 87 |

| 7.2 | Program | nmer's Model and CPU Registers  | 88 |

|     | 7.2.1   | Accumulator (A)                 | 88 |

|     | 7.2.2   | Index Register (H:X)            | 88 |

|     | 7.2.3   | Stack Pointer (SP)              | 89 |

|     | 7.2.4   | Program Counter (PC)            | 89 |

|     | 7.2.5   | Condition Code Register (CCR)   | 89 |

| 7.3 | Address | sing Modes                      | 91 |

|     | 7.3.1   | Inherent Addressing Mode (INH)  | 91 |

|     | 7.3.2   | Relative Addressing Mode (REL)  | 91 |

|     | 7.3.3   | Immediate Addressing Mode (IMM) | 91 |

|     | 7.3.4   | Direct Addressing Mode (DIR)    | 91 |

|     | 7.3.5   | Extended Addressing Mode (EXT)  | 92 |

|     | 7.3.6   | Indexed Addressing Mode         | 92 |

| 7.4 | Special | Operations                      | 93 |

|     | 7.4.1   | Reset Sequence                  | 93 |

|     | 7.4.2   | Interrupt Sequence              | 93 |

|     | 7.4.3   | Wait Mode Operation             | 94 |

|     | 7.4.4   | Stop Mode Operation             | 94 |

|     | 7.4.5   | BGND Instruction                | 95 |

| 7.5 | HCS08   | Instruction Set Summary         | 96 |

### Chapter 8 Analog Comparator (S08ACMPV2)

| 8.1 | Introdu | iction                             |  |

|-----|---------|------------------------------------|--|

|     |         | ACMP Configuration Information.    |  |

|     |         | ACMP/TPM Configuration Information |  |

|     |         | Features                           |  |

|     |         |                                    |  |

**Section Number**

### Title

Page

# Chapter 14 Serial Communications Interface (S08SCIV3)

| 14.1 | 1 Introduction                                  |  |

|------|-------------------------------------------------|--|

|      | 14.1.1 Features                                 |  |

|      | 14.1.2 Modes of Operation                       |  |

|      | 14.1.3 Block Diagram                            |  |

| 14.2 | 2 Register Definition                           |  |

|      | 14.2.1 SCI Baud Rate Registers (SCIBDH, SCIBHL) |  |

|      | 14.2.2 SCI Control Register 1 (SCIC1)           |  |

|      | 14.2.3 SCI Control Register 2 (SCIC2)           |  |

|      | 14.2.4 SCI Status Register 1 (SCIS1)            |  |

|      | 14.2.5 SCI Status Register 2 (SCIS2)            |  |

|      | 14.2.6 SCI Control Register 3 (SCIC3)           |  |

|      | 14.2.7 SCI Data Register (SCID)                 |  |

| 14.3 | 3 Functional Description                        |  |

|      | 14.3.1 Baud Rate Generation                     |  |

|      | 14.3.2 Transmitter Functional Description       |  |

|      | 14.3.3 Receiver Functional Description          |  |

|      | 14.3.4 Interrupts and Status Flags              |  |

| 14.4 | 4 Additional SCI Functions                      |  |

|      | 14.4.1 8- and 9-Bit Data Modes                  |  |

|      | 14.4.2 Stop Mode Operation                      |  |

|      | 14.4.3 Loop Mode                                |  |

|      | 14.4.4 Single-Wire Operation                    |  |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| Introduction                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1.2 Block Diagrams                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1.3 SPI Baud Rate Generation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| External Signal Description                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.1 SPSCK — SPI Serial Clock              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.2 MOSI — Master Data Out, Slave Data In |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.3 MISO — Master Data In, Slave Data Out |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.4 $\overline{\text{SS}}$ — Slave Select |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Modes of Operation                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3.1 SPI in Stop Modes                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Register Definition                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.1 SPI Control Register 1 (SPIC1)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.2 SPI Control Register 2 (SPIC2)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.3 SPI Baud Rate Register (SPIBR)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | <ul> <li>15.1.1 Features.</li> <li>15.1.2 Block Diagrams</li> <li>15.1.3 SPI Baud Rate Generation</li> <li>External Signal Description</li> <li>15.2.1 SPSCK — SPI Serial Clock.</li> <li>15.2.2 MOSI — Master Data Out, Slave Data In</li> <li>15.2.3 MISO — Master Data In, Slave Data Out</li> <li>15.2.4 SS — Slave Select</li> <li>Modes of Operation.</li> <li>15.3.1 SPI in Stop Modes</li> <li>Register Definition</li> <li>15.4.1 SPI Control Register 1 (SPIC1)</li> <li>15.4.2 SPI Control Register 2 (SPIC2)</li> </ul> |

**Chapter 4 Memory Map and Register Definition**

# 4.5 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I,* Freescale Semiconductor document order number HCS08RMv1/D.

#### **Chapter 4 Memory Map and Register Definition**

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

| Table | 4-9. | Security | States <sup>1</sup> |

|-------|------|----------|---------------------|

|-------|------|----------|---------------------|

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

### 4.7.3 FLASH Configuration Register (FCNFG)

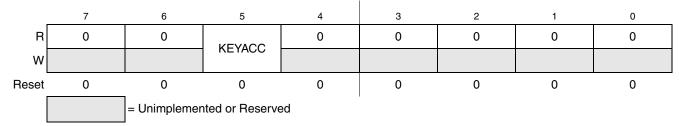

#### Figure 4-7. FLASH Configuration Register (FCNFG)

#### Table 4-10. FCNFG Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

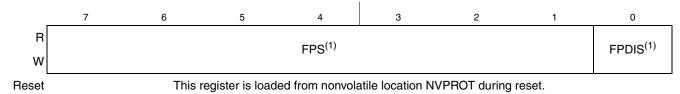

### 4.7.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT are copied from FLASH into FPROT. This register can be read at any time. If FPDIS = 0, protection can be increased, i.e., a smaller value of FPS can be written. If FPDIS = 1, writes do not change protection.

Background commands can be used to change the contents of these bits in FPROT.

Figure 4-8. FLASH Protection Register (FPROT)

MC9S08QG8 and MC9S08QG4 Data Sheet, Rev. 5

1

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT1 enabling the COP watchdog (see Section 5.8.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

The COPCLKS bit in SOPT2 (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there is an associated short and long time-out controlled by COPT in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the associated long time-out ( $2^8$  cycles).

| Control Bits |      | Clock Source | COP Overflow Count                          |

|--------------|------|--------------|---------------------------------------------|

| COPCLKS      | СОРТ | Clock Source |                                             |

| 0            | 0    | ~1 kHz       | 2 <sup>5</sup> cycles (32 ms) <sup>1</sup>  |

| 0            | 1    | ~1 kHz       | 2 <sup>8</sup> cycles (256 ms) <sup>1</sup> |

| 1            | 0    | Bus          | 2 <sup>13</sup> cycles                      |

| 1            | 1    | Bus          | 2 <sup>18</sup> cycles                      |

| Table 5-1. COP Configuration Option |

|-------------------------------------|

|-------------------------------------|

<sup>1</sup> Values are shown in this column based on  $t_{RTI} = 1$  ms. See  $t_{RTI}$  in the appendix Section A.8.1, "Control Timing," for the tolerance of this value.

Even if the application will use the reset default settings of COPE, COPCLKS, and COPT, the user must write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost. The initial writes to SOPT1 and SOPT2 will reset the COP counter.

The write to SRS that services (clears) the COP counter must not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

In background debug mode, the COP counter will not increment.

When the bus clock source is selected, the COP counter does not increment while the system is in stop mode. The COP counter resumes as soon as the MCU exits stop mode.

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

# 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

### 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

### 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

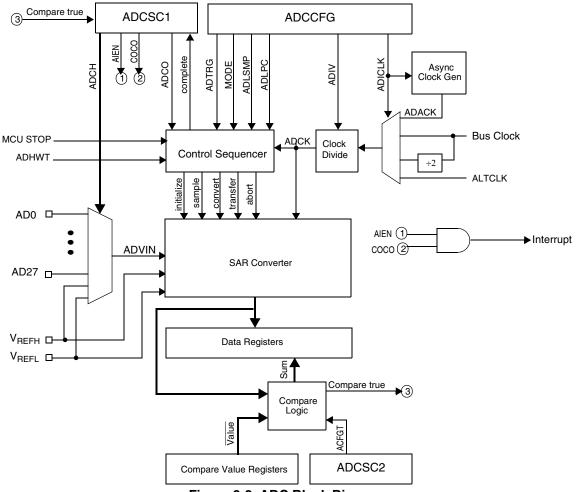

#### Analog-to-Digital Converter (S08ADC10V1)

Figure 9-2. ADC Block Diagram

# 9.2 External Signal Description

The ADC module supports up to 28 separate analog inputs. It also requires four supply/reference/ground connections.

| Name              | Function               |

|-------------------|------------------------|

| AD27–AD0          | Analog Channel inputs  |

| V <sub>REFH</sub> | High reference voltage |

| V <sub>REFL</sub> | Low reference voltage  |

| V <sub>DDAD</sub> | Analog power supply    |

| V <sub>SSAD</sub> | Analog ground          |

#### **Table 9-2. Signal Properties**

### 9.4.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

#### NOTE

It is possible for the ADC module to wake the system from low power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software should ensure that the data transfer blocking mechanism (discussed in Section 9.4.4.2, "Completing Conversions) is cleared when entering stop3 and continuing ADC conversions.

### 9.4.8 MCU Stop1 and Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters either stop1 or stop2 mode. All module registers contain their reset values following exit from stop1 or stop2. Therefore the module must be re-enabled and re-configured following exit from stop1 or stop2.

### 9.5 Initialization Information

This section gives an example which provides some basic direction on how a user would initialize and configure the ADC module. The user has the flexibility of choosing between configuring the module for 8-bit or 10-bit resolution, single or continuous conversion, and a polled or interrupt approach, among many other options. Refer to Table 9-6, Table 9-7, and Table 9-8 for information used in this example.

#### NOTE

Hexadecimal values designated by a preceding 0x, binary values designated by a preceding %, and decimal values have no preceding character.

### 9.5.1 ADC Module Initialization Example

### 9.5.1.1 Initialization Sequence

Before the ADC module can be used to complete conversions, an initialization procedure must be performed. A typical sequence is as follows:

1. Update the configuration register (ADCCFG) to select the input clock source and the divide ratio used to generate the internal clock, ADCK. This register is also used for selecting sample time and low-power configuration.

#### Analog-to-Digital Converter (S08ADC10V1)

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies must be at the  $V_{SSAD}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSAD}$  pin makes a good single point ground location.

### 9.6.1.2 Analog Reference Pins

In addition to the analog supplies, the ADC module has connections for two reference voltage inputs. The high reference is  $V_{REFH}$ , which may be shared on the same pin as  $V_{DDAD}$  on some devices. The low reference is  $V_{REFL}$ , which may be shared on the same pin as  $V_{SSAD}$  on some devices.

When available on a separate pin,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ). When available on a separate pin,  $V_{REFL}$  must be connected to the same voltage potential as  $V_{SSAD}$ . Both  $V_{REFH}$  and  $V_{REFL}$  must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as near as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

### 9.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer will be in its high impedance state and the pullup is disabled. Also, the input buffer draws dc current when its input is not at either  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of 0.01  $\mu$ F capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to V<sub>SSA</sub>.

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF (full scale 10-bit representation) or \$FF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

# Chapter 12 Keyboard Interrupt (S08KBIV2)

# 12.1 Introduction

The keyboard interrupt KBI module provides up to eight independently enabled external interrupt sources. Figure 12-1 Shows the MC9S08QG8/4 block guide with the KBI highlighted.

Modulo Timer (S08MTIMV1)

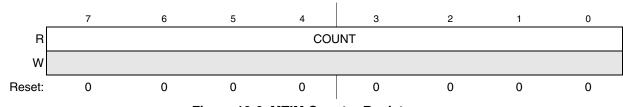

# 13.3.3 MTIM Counter Register (MTIMCNT)

MTIMCNT is the read-only value of the current MTIM count of the 8-bit counter.

| Field | Description                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>MTIM Count</b> — These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset clears the count to \$00. |

# 13.3.4 MTIM Modulo Register (MTIMMOD)

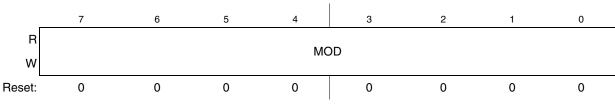

Figure 13-7. MTIM Modulo Register

#### Table 13-5. MTIM Modulo Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>MOD | MTIM Modulo — These eight read/write bits contain the modulo value used to reset the count and set TOF. A value of \$00 puts the MTIM in free-running mode. Writing to MTIMMOD resets the COUNT to \$00 and clears TOF. Reset sets the modulo to \$00. |

| Table 14-5. SCIS1 Register Field | <b>Descriptions (continued)</b> |

|----------------------------------|---------------------------------|

|----------------------------------|---------------------------------|

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCID). To clear RDRF, read SCIS1 with RDRF = 1 and then read the SCI data register (SCID).</li> <li>0 Receive data register empty.</li> <li>1 Receive data register full.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of<br>activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is<br>all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times<br>depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't<br>start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the<br>previous character do not count toward the full character time of logic high needed for the receiver to detect an<br>idle line.To clear IDLE, read SCIS1 with IDLE = 1 and then read the SCI data register (SCID). After IDLE has been<br> |  |  |  |  |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCID yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCID. To clear OR, read SCIS1 with OR = 1 and then read the SCI data register (SCID).</li> <li>No overrun.</li> <li>Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIS1 and then read the SCI data register (SCID).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCID.</li> </ul>                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 1<br>FE   | <ul> <li>Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIS1 with FE = 1 and then read the SCI data register (SCID).</li> <li>0 No framing error detected. This does not guarantee the framing is correct.</li> <li>1 Framing error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 0<br>PF   | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIS1 and then read the SCI data register (SCID).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

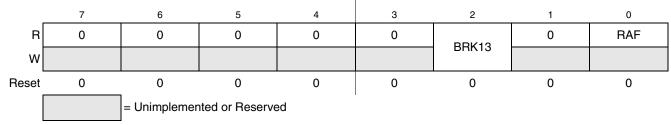

# 14.2.5 SCI Status Register 2 (SCIS2)

This register has one read-only status flag. Writes have no effect.

#### Figure 14-10. SCI Status Register 2 (SCIS2)

#### Table 14-6. SCIS2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>BRK13 | <ul> <li>Break Character Length — BRK13 is used to select a longer break character length. Detection of a framing error is not affected by the state of this bit.</li> <li>0 Break character is 10 bit times (11 if M = 1)</li> <li>1 Break character is 13 bit times (14 if M = 1)</li> </ul>                                                                                                                                          |

| 0<br>RAF   | <ul> <li>Receiver Active Flag — RAF is set when the SCI receiver detects the beginning of a valid start bit, and RAF is cleared automatically when the receiver detects an idle line. This status flag can be used to check whether an SCI character is being received before instructing the MCU to go to stop mode.</li> <li>SCI receiver idle waiting for a start bit.</li> <li>SCI receiver active (RxD input not idle).</li> </ul> |

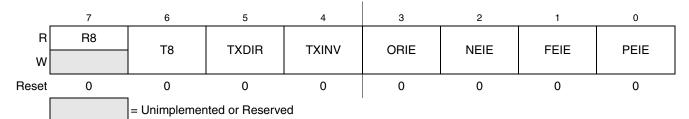

### 14.2.6 SCI Control Register 3 (SCIC3)

#### Figure 14-11. SCI Control Register 3 (SCIC3)

#### Table 14-7. SCIC3 Register Field Descriptions

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>R8 | <b>Ninth Data Bit for Receiver</b> — When the SCI is configured for 9-bit data ( $M = 1$ ), R8 can be thought of as a ninth receive data bit to the left of the MSB of the buffered data in the SCID register. When reading 9-bit data, read R8 before reading SCID because reading SCID completes automatic flag clearing sequences which could allow R8 and SCID to be overwritten with new data.                                                                                                                                                                                   |  |  |  |

| 6<br>T8 | <b>Ninth Data Bit for Transmitter</b> — When the SCI is configured for 9-bit data ( $M = 1$ ), T8 may be thought of as a ninth transmit data bit to the left of the MSB of the data in the SCID register. When writing 9-bit data, the entire 9-bit value is transferred to the SCI shift register after SCID is written so T8 should be written (if it needs to change from its previous value) before SCID is written. If T8 does not need to change in the new value (such as when it is used to generate mark or space parity), it need not be written each time SCID is written. |  |  |  |

# 15.5.2 SPI Interrupts

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

### 15.5.3 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS}$  pin (provided the  $\overline{SS}$  pin is configured as the mode fault input signal). The  $\overline{SS}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK, MOSI, and MISO (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPIC1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

# Chapter 17 Development Support

# 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins. Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

### 17.1.1 Module Configuration

The alternate BDC clock source is the ICSLCLK. This clock source is selected by clearing the CLKSW bit in the BDCSCR register. For details on ICSLCLK, see Section 10.4, "Functional Description" of the ICS chapter.

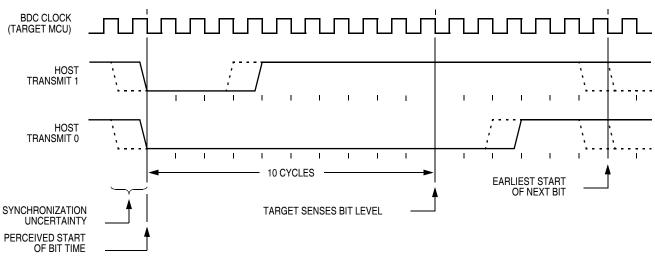

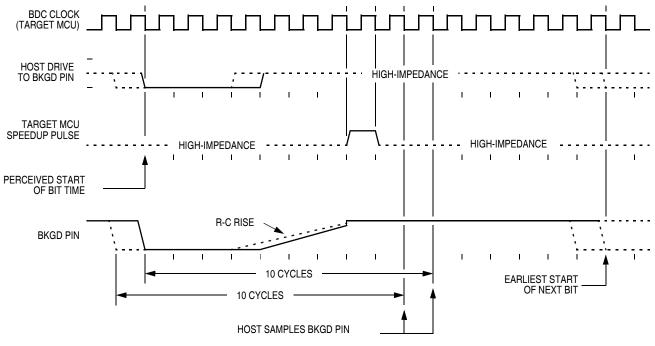

Figure 17-2. BDC Host-to-Target Serial Bit Timing

Figure 17-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host should sample the bit level about 10 cycles after it started the bit time.

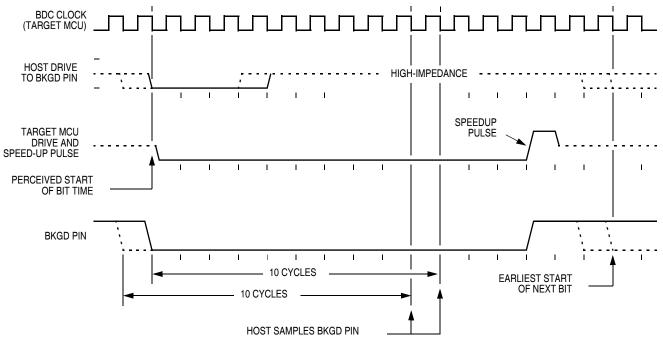

Figure 17-3. BDC Target-to-Host Serial Bit Timing (Logic 1)

#### Development Support

Figure 17-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

### 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

# Appendix A Electrical Characteristics

# A.1 Introduction

This section contains electrical and timing specifications.

# A.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-1 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                          | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                           | V <sub>In</sub>  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | Ι <sub>D</sub>   | ± 25                          | mA   |

| Storage temperature range                                                                       | T <sub>stg</sub> | –55 to 150                    | °C   |

Table A-1. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}.\,$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

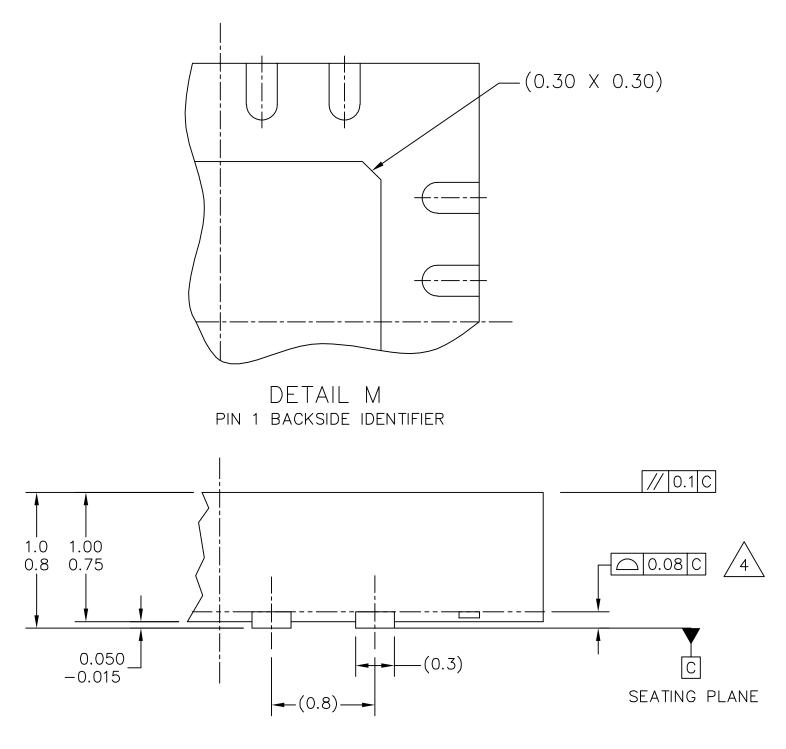

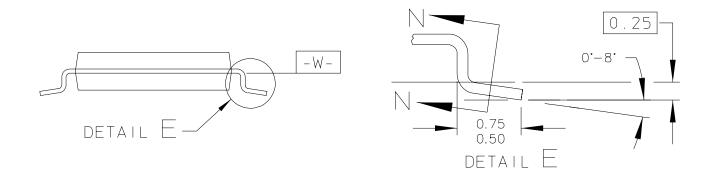

DETAIL G view rotated 90° cw

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                                               | MECHANICAL OUTLINE |              | PRINT VERSION NO | T TO SCALE  |

|-----------------------------------------------------------------------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>16 TERMINAL, 0.8 PITCH (5 X 5 X 1)<br>CASE OUTLINE |                    | DOCUMENT NC  | ): 98ARE10614D   | REV: O      |

|                                                                                                                       |                    | CASE NUMBER  | : 1679–01        | 23 MAR 2005 |

|                                                                                                                       |                    | STANDARD: FR | EESCALE          |             |

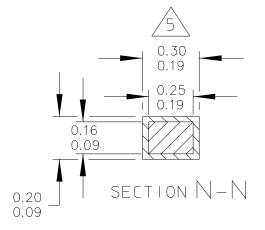

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |             | L OUTLINE       | PRINT VERSION NOT TO SCALE |        |

|---------------------------------------------------------|-------------|-----------------|----------------------------|--------|

| TITLE:                                                  |             | DOCUMENT NE     | ]: 98ASH70247A             | RE∨: B |

| 16 LD TSSOP, PITCH 0.                                   | CASE NUMBER | R: 948F-01      | 19 MAY 2005                |        |

|                                                         |             | STANDARD: JEDEC |                            |        |