Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | 508                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 20MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 4                                                          |

| Program Memory Size        | 8KB (8K × 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | A/D 4x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 8-VDFN Exposed Pad                                         |

| Supplier Device Package    | 8-DFN-EP (4x4)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qg8mfqe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.3 Register Addresses and Bit Assignments

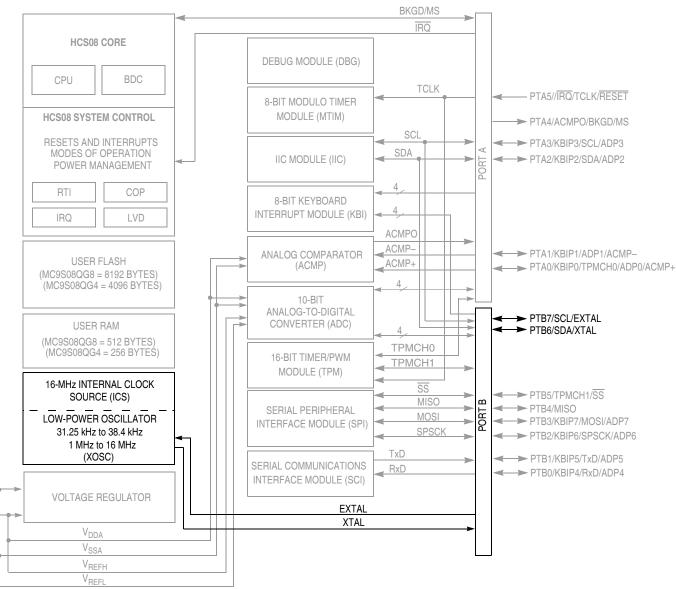

The registers in the MC9S08QG8/4 are divided into these groups:

- Direct-page registers are located in the first 96 locations in the memory map; these are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located from 0x1800 and above in the memory map. This leaves more room in the direct page for more frequently used registers and RAM.

- The nonvolatile register area consists of a block of 16 locations in FLASH memory at 0xFFB0–0xFFBF. Nonvolatile register locations include:

- NVPROT and NVOPT are loaded into working registers at reset.

- An 8-byte backdoor comparison key that optionally allows a user to gain controlled access to secure memory.

Because the nonvolatile register locations are FLASH memory, they must be erased and programmed like other FLASH memory locations.

Direct-page registers can be accessed with efficient direct addressing mode instructions. Bit manipulation instructions can be used to access any bit in any direct-page register. Table 4-2 is a summary of all user-accessible direct-page registers and control bits.

The direct page registers in Table 4-2 can use the more efficient direct addressing mode that requires only the lower byte of the address. Because of this, the lower byte of the address in column one is shown in bold text. In Table 4-3 and Table 4-4, the whole address in column one is shown in bold. In Table 4-2, Table 4-3, and Table 4-4, the register names in column two are shown in bold to set them apart from the bit names to the right. Cells that are not associated with named bits are shaded. A shaded cell with a 0 indicates this unused bit always reads as a 0. Shaded cells with dashes indicate unused or reserved bit locations that could read as 1s or 0s.

| Address                            | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD          | 0      | 0      | PTAD5  | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD         | 0      | 0      | PTADD5 | PTADD4 | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b>                     | PTBD          | PTBD7  | PTBD6  | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>03</b>                     | PTBDD         | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| 0x00 <b>04</b> –<br>0x00 <b>0B</b> | Reserved      | _      | _      | _      | _      | _      |        | _      | _      |

| 0x00 <b>0C</b>                     | KBISC         | 0      | 0      | 0      | 0      | KBF    | KBACK  | KBIE   | KBMOD  |

| 0x00 <b>0D</b>                     | KBIPE         | KBIPE7 | KBIPE6 | KBIPE5 | KBIPE4 | KBIPE3 | KBIPE2 | KBIPE1 | KBIPE0 |

| 0x00 <b>0E</b>                     | KBIES         | KBEDG7 | KBEDG6 | KBEDG5 | KBEDG4 | KBEDG3 | KBEDG2 | KBEDG1 | KBEDG0 |

| 0x00 <b>0F</b>                     | IRQSC         | 0      | IRQPDD | 0      | IRQPE  | IRQF   | IRQACK | IRQIE  | IRQMOD |

| 0x00 <b>10</b>                     | ADCSC1        | 0000   | AIEN   | ADCO   |        |        | ADCH   |        |        |

| 0x00 <b>11</b>                     | ADCSC2        | ADACT  | ADTRG  | ACFE   | ACFGT  | _      | —      | _      | _      |

| 0x00 <b>12</b>                     | ADCRH         | 0      | 0      | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADCRL         | ADR7   | ADR6   | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

### Table 4-2. Direct-Page Register Summary

#### **Chapter 6 Parallel Input/Output Control**

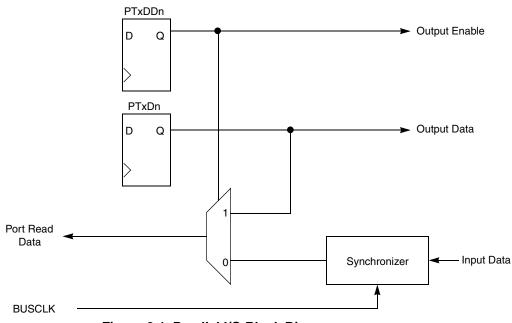

Figure 6-1. Parallel I/O Block Diagram

The data direction control bit (PTxDDn) determines whether the output buffer for the associated pin is enabled, and also controls the source for port data register reads. The input buffer for the associated pin is always enabled unless the pin is enabled as an analog function or is an output-only pin.

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTxDDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven momentarily with an old data value that happened to be in the port data register.

# 6.2 Pin Control — Pullup, Slew Rate, and Drive Strength

Associated with the parallel I/O ports is a set of registers located in the high page register space that operate independently of the parallel I/O registers. These registers are used to control pullups, slew rate, and drive strength for the pins.

### 6.4.3 Port B Registers

This section provides information about the registers associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory Map and Register Definition," for the absolute address assignments for all parallel I/O. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

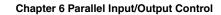

## 6.4.3.1 Port B Data (PTBD)

Figure 6-10. Port B Data Register (PTBD)

### Table 6-6. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

## 6.4.3.2 Port B Data Direction (PTBDD)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-11. Data Direction for Port B (PTBDD)

### Table 6-7. PTBDD Register Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTBDD[7:0] PT<br>0 | <b>Pata Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for TBD reads.<br>Input (output driver disabled) and reads return the pin value.<br>Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn. |

Chapter 6 Parallel Input/Output Control

# 6.4.4 Port B Control Registers

The pins associated with port B are controlled by the registers in this section. These registers control the pin pullup, slew rate, and drive strength of the port B pins independent of the parallel I/O register.

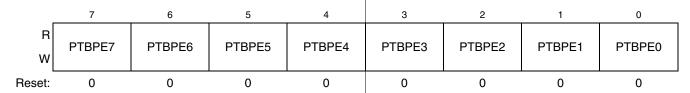

## 6.4.4.1 Port B Internal Pullup Enable (PTBPE)

An internal pullup device can be enabled for each port pin by setting the corresponding bit in the pullup enable register (PTBPEn). The pullup device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function.

Figure 6-12. Internal Pullup Enable for Port B Register (PTBPE)

Table 6-8. PTBPE Register Field Descriptions

| Field      | Description                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------|

| 7:0        | Internal Pullup Enable for Port B Bits — Each of these control bits determines if the internal pullup device is   |

| PTBPE[7:0] | enabled for the associated PTB pin. For port B pins that are configured as outputs, these bits have no effect and |

|            | the internal pullup devices are disabled.                                                                         |

|            | 0 Internal pullup device disabled for port B bit n.                                                               |

|            | 1 Internal pullup device enabled for port B bit n.                                                                |

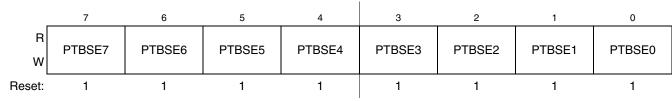

# 6.4.4.2 Port B Slew Rate Enable (PTBSE)

Slew rate control can be enabled for each port pin by setting the corresponding bit in the slew rate control register (PTBSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins which are configured as input.

Figure 6-14. Slew Rate Enable for Port B Register (PTBSE)

| Table 6-9. PTBSE Register F | Field Descriptions |

|-----------------------------|--------------------|

|-----------------------------|--------------------|

| Field | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Output Slew Rate Enable for Port B Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port B bit n.</li> <li>Output slew rate control enabled for port B bit n.</li> </ul> |

### 8.1.3 Features

The ACMP has the following features:

- Full rail-to-rail supply operation.

- Less than 40 mV of input offset.

- Less than 15 mV of hysteresis.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPO.

## 8.1.4 Modes of Operation

This section defines the ACMP operation in wait, stop, and background debug modes.

### 8.1.4.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt, ACIE, is enabled. For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 8.1.4.2 ACMP in Stop Modes

The ACMP is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the ACMP cannot be used as a wake up source from stop modes.

During either stop1 or stop2 mode, the ACMP module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the ACMP module will be in the reset state.

During stop3 mode, clocks to the ACMP module are halted. No registers are affected. In addition, the ACMP comparator circuit will enter a low power state. No compare operation will occur while in stop3.

If stop3 is exited with a reset, the ACMP will be put into its reset state. If stop3 is exited with an interrupt, the ACMP continues from the state it was in when stop3 was entered.

### 8.1.4.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP will continue to operate normally.

## 8.1.5 Block Diagram

The block diagram for the analog comparator module is shown Figure 8-2.

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC1 | <ul> <li>ADC Pin Control 1 — ADPC1 is used to control the pin associated with channel AD1.</li> <li>0 AD1 pin I/O control enabled</li> <li>1 AD1 pin I/O control disabled</li> </ul> |

| 0<br>ADPC0 | <ul> <li>ADC Pin Control 0 — ADPC0 is used to control the pin associated with channel AD0.</li> <li>0 AD0 pin I/O control enabled</li> <li>1 AD0 pin I/O control disabled</li> </ul> |

#### Table 9-9. APCTL1 Register Field Descriptions (continued)

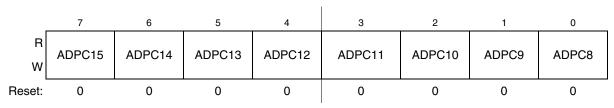

# 9.3.9 Pin Control 2 Register (APCTL2)

APCTL2 is used to control channels 8–15 of the ADC module.

Figure 9-12. Pin Control 2 Register (APCTL2)

### Table 9-10. APCTL2 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC15 | <ul> <li>ADC Pin Control 15 — ADPC15 is used to control the pin associated with channel AD15.</li> <li>0 AD15 pin I/O control enabled</li> <li>1 AD15 pin I/O control disabled</li> </ul> |

| 6<br>ADPC14 | <ul> <li>ADC Pin Control 14 — ADPC14 is used to control the pin associated with channel AD14.</li> <li>0 AD14 pin I/O control enabled</li> <li>1 AD14 pin I/O control disabled</li> </ul> |

| 5<br>ADPC13 | <ul> <li>ADC Pin Control 13 — ADPC13 is used to control the pin associated with channel AD13.</li> <li>0 AD13 pin I/O control enabled</li> <li>1 AD13 pin I/O control disabled</li> </ul> |

| 4<br>ADPC12 | <ul> <li>ADC Pin Control 12 — ADPC12 is used to control the pin associated with channel AD12.</li> <li>0 AD12 pin I/O control enabled</li> <li>1 AD12 pin I/O control disabled</li> </ul> |

| 3<br>ADPC11 | <ul> <li>ADC Pin Control 11 — ADPC11 is used to control the pin associated with channel AD11.</li> <li>0 AD11 pin I/O control enabled</li> <li>1 AD11 pin I/O control disabled</li> </ul> |

| 2<br>ADPC10 | <ul> <li>ADC Pin Control 10 — ADPC10 is used to control the pin associated with channel AD10.</li> <li>0 AD10 pin I/O control enabled</li> <li>1 AD10 pin I/O control disabled</li> </ul> |

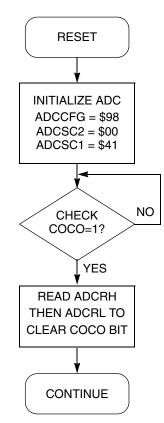

Analog-to-Digital Converter (S08ADC10V1)

Figure 9-14. Initialization Flowchart for Example

# 9.6 Application Information

This section contains information for using the ADC module in applications. The ADC has been designed to be integrated into a microcontroller for use in embedded control applications requiring an A/D converter.

# 9.6.1 External Pins and Routing

The following sections discuss the external pins associated with the ADC module and how they should be used for best results.

# 9.6.1.1 Analog Supply Pins

The ADC module has analog power and ground supplies ( $V_{DDAD}$  and  $V_{SSAD}$ ) which are available as separate pins on some devices. On other devices,  $V_{SSAD}$  is shared on the same pin as the MCU digital  $V_{SS}$ , and on others, both  $V_{SSAD}$  and  $V_{DDAD}$  are shared with the MCU digital supply pins. In these cases, there are separate pads for the analog supplies which are bonded to the same pin as the corresponding digital supply so that some degree of isolation between the supplies is maintained.

When available on a separate pin, both  $V_{DDAD}$  and  $V_{SSAD}$  must be connected to the same voltage potential as their corresponding MCU digital supply ( $V_{DD}$  and  $V_{SS}$ ) and must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

#### Analog-to-Digital Converter (S08ADC10V1)

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies must be at the  $V_{SSAD}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSAD}$  pin makes a good single point ground location.

### 9.6.1.2 Analog Reference Pins

In addition to the analog supplies, the ADC module has connections for two reference voltage inputs. The high reference is  $V_{REFH}$ , which may be shared on the same pin as  $V_{DDAD}$  on some devices. The low reference is  $V_{REFL}$ , which may be shared on the same pin as  $V_{SSAD}$  on some devices.

When available on a separate pin,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ). When available on a separate pin,  $V_{REFL}$  must be connected to the same voltage potential as  $V_{SSAD}$ . Both  $V_{REFH}$  and  $V_{REFL}$  must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as near as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

## 9.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer will be in its high impedance state and the pullup is disabled. Also, the input buffer draws dc current when its input is not at either  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of 0.01  $\mu$ F capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to V<sub>SSA</sub>.

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF (full scale 10-bit representation) or \$FF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

#### Chapter 10 Internal Clock Source (S08ICSV1)

#### NOTES:

$V_{SS}$

V<sub>DD</sub>

<sup>1</sup> Not all pins or pin functions are available on all devices, see Table 1-1 for available functions on each device.

- <sup>2</sup> Port pins are software configurable with pullup device if input port.

- <sup>3</sup> Port pins are software configurable for output drive strength.

- <sup>4</sup> Port pins are software configurable for output slew rate control.

- <sup>5</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>6</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> SDA and SCL pin locations can be repositioned under software control (IICPS), defaults on PTA2 and PTA3.

- <sup>9</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 10-1. MC9S08QG8/4 Block Diagram Highlighting ICS Block and Pins

Inter-Integrated Circuit (S08IICV1)

# 11.7 Initialization/Application Information

|    |                                                                                                           | Module Initialization (Slave)                                                                      |  |  |  |  |  |  |

|----|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1. |                                                                                                           | Vrite: IICA                                                                                        |  |  |  |  |  |  |

| 0  |                                                                                                           | to set the slave address                                                                           |  |  |  |  |  |  |

| 2. | Write: IIC                                                                                                | nable IIC and interrupts                                                                           |  |  |  |  |  |  |

| 3. |                                                                                                           | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                          |  |  |  |  |  |  |

| 4. |                                                                                                           | RAM variables used to achieve the routine shown in Figure 11-11                                    |  |  |  |  |  |  |

|    |                                                                                                           |                                                                                                    |  |  |  |  |  |  |

|    |                                                                                                           | Module Initialization (Master)                                                                     |  |  |  |  |  |  |

| 1. | Write: IIC                                                                                                |                                                                                                    |  |  |  |  |  |  |

| •  |                                                                                                           | et the IIC baud rate (example provided in this chapter)                                            |  |  |  |  |  |  |

| 2. | Write: IIC                                                                                                | nable IIC and interrupts                                                                           |  |  |  |  |  |  |

| 3. |                                                                                                           | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                          |  |  |  |  |  |  |

| 4. |                                                                                                           | RAM variables used to achieve the routine shown in Figure 11-11                                    |  |  |  |  |  |  |

| 5. | Write: IIC                                                                                                | C                                                                                                  |  |  |  |  |  |  |

| -  |                                                                                                           | nable TX                                                                                           |  |  |  |  |  |  |

| 6. | Write: IIC                                                                                                |                                                                                                    |  |  |  |  |  |  |

| 7. | Write: IIC                                                                                                | nable MST (master mode)                                                                            |  |  |  |  |  |  |

| 1. |                                                                                                           |                                                                                                    |  |  |  |  |  |  |

|    |                                                                                                           | ter receive or transmit.)                                                                          |  |  |  |  |  |  |

|    | Module Use                                                                                                |                                                                                                    |  |  |  |  |  |  |

|    |                                                                                                           | ine shown in Figure 11-11 can handle both master and slave IIC operations. For slave operation, an |  |  |  |  |  |  |

|    | incoming IIC message that contains the proper address will begin IIC communication. For master operation, |                                                                                                    |  |  |  |  |  |  |

|    | communication must be initiated by writing to the IICD register.                                          |                                                                                                    |  |  |  |  |  |  |

|    |                                                                                                           | Register Model                                                                                     |  |  |  |  |  |  |

|    |                                                                                                           |                                                                                                    |  |  |  |  |  |  |

|    | IICA                                                                                                      | ADDR 0                                                                                             |  |  |  |  |  |  |

|    |                                                                                                           | Address to which the module will respond when addressed as a slave (in slave mode)                 |  |  |  |  |  |  |

|    | IICF MULT ICR                                                                                             |                                                                                                    |  |  |  |  |  |  |

|    | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                                                           |                                                                                                    |  |  |  |  |  |  |

|    | IICC                                                                                                      | IICEN IICIE MST TX TXAK RSTA 0 0                                                                   |  |  |  |  |  |  |

|    |                                                                                                           | Module configuration                                                                               |  |  |  |  |  |  |

|    | IICS                                                                                                      | TCF IAAS BUSY ARBL 0 SRW IICIF RXAK                                                                |  |  |  |  |  |  |

|    | 100                                                                                                       | Module status flags                                                                                |  |  |  |  |  |  |

|    |                                                                                                           |                                                                                                    |  |  |  |  |  |  |

|    | IICD                                                                                                      | DATA                                                                                               |  |  |  |  |  |  |

|    | Data register; Write to transmit IIC data read to read IIC data                                           |                                                                                                    |  |  |  |  |  |  |

### Figure 11-10. IIC Module Quick Start

### Table 14-5. SCIS1 Register Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCID). To clear RDRF, read SCIS1 with RDRF = 1 and then read the SCI data register (SCID).</li> <li>0 Receive data register empty.</li> <li>1 Receive data register full.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIS1 with IDLE = 1 and then read the SCI data register (SCID). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line detected.         1       Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCID yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCID. To clear OR, read SCIS1 with OR = 1 and then read the SCI data register (SCID).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIS1 and then read the SCI data register (SCID).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCID.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1<br>FE   | <ul> <li>Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIS1 with FE = 1 and then read the SCI data register (SCID).</li> <li>0 No framing error detected. This does not guarantee the framing is correct.</li> <li>1 Framing error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0<br>PF   | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIS1 and then read the SCI data register (SCID).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### 15.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

### 15.1.2 Block Diagrams

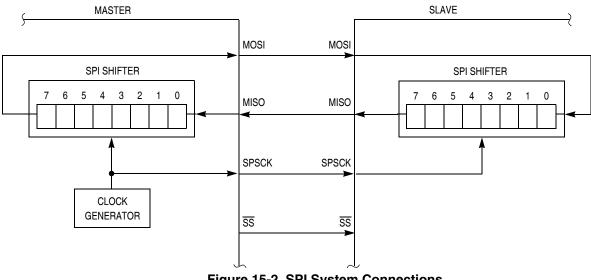

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 15.1.2.1 SPI System Block Diagram

Figure 15-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 15-2. SPI System Connections

Serial Peripheral Interface (S08SPIV3)

# 15.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 15.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

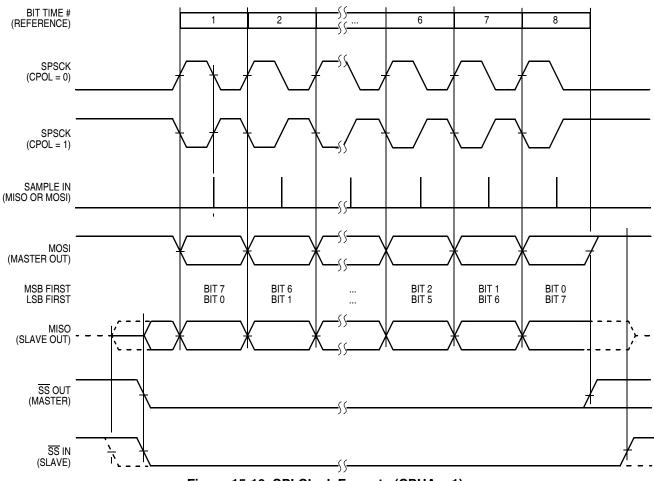

# 15.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 15-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the

MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 15-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

Timer/Pulse-Width Modulator (S08TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

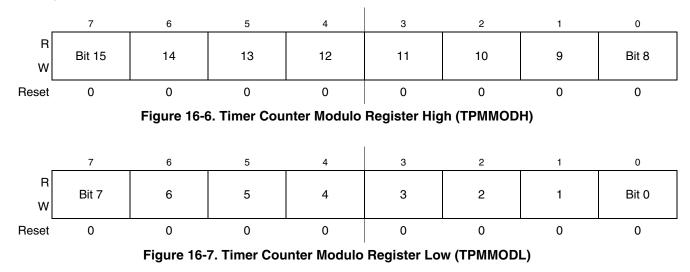

# 16.3.3 Timer Counter Modulo Registers (TPMMODH:TPMMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMMODH or TPMMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

#### Timer/Pulse-Width Modulator (S08TPMV2)

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMMODH:TPMMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

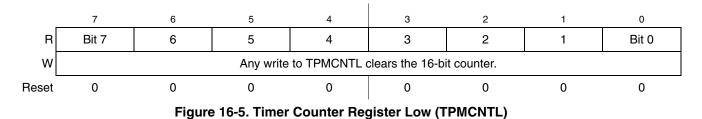

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMCNTH or TPMCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMCNTH or TPMCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

## 16.4.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

### 16.4.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMCnVH:TPMCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 17.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>0 Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>1 Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |

| 1<br>WSF | <ul> <li>Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)</li> <li>Memory access did not conflict with a wait or stop instruction</li> <li>Memory access command failed because the CPU entered wait or stop mode</li> </ul>                                                                                   |

| 0<br>DVF | <ul> <li>Data Valid Failure Status — This status bit is not used in the MC9S08QG8/4 because it does not have any slow access memory.</li> <li>0 Memory access did not conflict with a slow memory access</li> <li>1 Memory access command failed because CPU was not finished with a slow memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 17-2. BDCSCR Register Field Descriptions (continued)

## 17.4.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 17.2.4, "BDC Hardware Breakpoint."

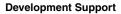

## 17.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background mode debug commands, not from user programs.

#### Figure 17-6. System Background Debug Force Reset Register (SBDFR)

#### Table 17-3. SBDFR Register Field Description

| Field     | Description                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial active background mode command such as WRITE_BYTE allows an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

## 17.4.3 DBG Registers and Control Bits

The debug module includes nine bytes of register space for three 16-bit registers and three 8-bit control and status registers. These registers are located in the high register space of the normal memory map so they are accessible to normal application programs. These registers are rarely if ever accessed by normal user application programs with the possible exception of a ROM patching mechanism that uses the breakpoint logic.

### 17.4.3.1 Debug Comparator A High Register (DBGCAH)

This register contains compare value bits for the high-order eight bits of comparator A. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.2 Debug Comparator A Low Register (DBGCAL)

This register contains compare value bits for the low-order eight bits of comparator A. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.3 Debug Comparator B High Register (DBGCBH)

This register contains compare value bits for the high-order eight bits of comparator B. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

### 17.4.3.4 Debug Comparator B Low Register (DBGCBL)

This register contains compare value bits for the low-order eight bits of comparator B. This register is forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

| Parameter                                                         | Symbol              | Conditions                                                     | f <sub>OSC</sub> /f <sub>BUS</sub> | Result | Amplitude <sup>1</sup><br>(Min) | Unit |

|-------------------------------------------------------------------|---------------------|----------------------------------------------------------------|------------------------------------|--------|---------------------------------|------|

| Conducted susceptibility, electrical fast transient/burst (EFT/B) |                     |                                                                |                                    | А      | TBD                             |      |

|                                                                   | V <sub>CS_EFT</sub> | $V_{DD} = 3.3V$<br>$T_A = +25^{\circ}C$<br>package type<br>TBD | ackage type                        | В      | TBD                             | kV   |

|                                                                   |                     |                                                                |                                    | С      | TBD                             | NV.  |

|                                                                   |                     |                                                                |                                    | D      | TBD                             |      |

### Table A-17. Conducted Susceptibility, EFT/B

<sup>1</sup> Data based on qualification test results. Not tested in production.

The susceptibility performance classification is described in Table A-18.

| Result |                            | Performance Criteria                                                                                                                                                              |

|--------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A      | No failure                 | The MCU performs as designed during and after exposure.                                                                                                                           |

| В      | Self-recovering<br>failure | The MCU does not perform as designed during exposure. The MCU returns automatically to normal operation after exposure is removed.                                                |

| С      | Soft failure               | The MCU does not perform as designed during exposure. The MCU does not return to normal operation until exposure is removed and the RESET pin is asserted.                        |

| D      | Hard failure               | The MCU does not perform as designed during exposure. The MCU does not return to normal operation until exposure is removed and the power to the MCU is cycled.                   |

| E      | Damage                     | The MCU does not perform as designed during and after exposure. The MCU cannot be returned to proper operation due to physical damage or other permanent performance degradation. |

### Table A-18. Susceptibility Performance Classification