#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ac3-rltim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

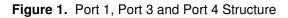

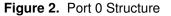

## Port 0 and Port 2

Ports 0 and 2 are used for general-purpose I/O or as the external address/data bus. Port 0, shown in Figure 3, differs from the other Ports in not having internal pull-ups. Figure 3 shows the structure of Port 2. An external source can pull a Port 2 pin low.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 0 or 2). To use a pin for general-purpose input, set the bit in the Px register to turn off the output driver FET.

- Notes: 1. Port 0 is precluded from use as general-purpose I/O Ports when used as address/data bus drivers.

- 2. Port 0 internal strong pull-ups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pull-up FET is off, Port 0 outputs are open-drain.

# SFR Mapping

The Special Function Registers (SFRs) of the AT89C51AC3 fall into the following categories:

| Mnemonic | Add | Name                                     | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator                              | _  | _  | -  | -   | _   | _  | -  | _ |

| В        | F0h | B Register                               | _  | _  | -  | -   | _   | _  | -  | _ |

| PSW      | D0h | Program Status Word                      | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer                            | _  | _  | -  | -   | _   | _  | -  | _ |

| DPL      | 82h | Data Pointer Low<br>byte<br>LSB of DPTR  | _  | _  | _  | _   | _   | _  | _  | _ |

| DPH      | 83h | Data Pointer High<br>byte<br>MSB of DPTR | _  | _  | _  | _   | _   | _  | _  | _ |

| Mnemonic | Add | Name        | 7 | 6 | 5 | 4              | 3             | 2              | 1    | 0    |

|----------|-----|-------------|---|---|---|----------------|---------------|----------------|------|------|

| P0       | 80h | Port 0      | - | _ | - | _              | _             | _              | -    | _    |

| P1       | 90h | Port 1      | - | _ | - | _              | _             | _              | -    | _    |

| P2       | A0h | Port 2      | - | _ | - | _              | _             | _              | -    | _    |

| P3       | B0h | Port 3      | - | _ | - | _              | _             | _              | -    | _    |

| P4       | C0h | Port 4 (x5) | _ | _ | _ | P4.4 /<br>MOSI | P4.3 /<br>SCK | P4.2 /<br>MISO | P4.1 | P4.0 |

| Mnemonic | Add | Name                          | 7     | 6     | 5   | 4   | 3     | 2     | 1   | 0   |

|----------|-----|-------------------------------|-------|-------|-----|-----|-------|-------|-----|-----|

| ТНО      | 8Ch | Timer/Counter 0 High byte     | _     | _     | -   | _   | _     | -     | -   | _   |

| TL0      | 8Ah | Timer/Counter 0 Low byte      | _     | _     | -   | _   | _     | -     | -   | -   |

| TH1      | 8Dh | Timer/Counter 1 High byte     | _     | _     | -   | _   | _     | -     | -   | _   |

| TL1      | 8Bh | Timer/Counter 1 Low byte      | _     | _     | -   | _   | _     | -     | -   | _   |

| TH2      | CDh | Timer/Counter 2 High byte     | _     | _     | -   | _   | _     | -     | -   | -   |

| TL2      | CCh | Timer/Counter 2 Low byte      | _     | _     | -   | _   | _     | -     | -   | _   |

| TCON     | 88h | Timer/Counter 0 and 1 control | TF1   | TR1   | TF0 | TR0 | IE1   | IT1   | IE0 | IT0 |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes   | GATE1 | C/T1# | M11 | M01 | GATE0 | C/T0# | M10 | M00 |

| Mnemonic | Add | Name                                           | 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|----------|-----|------------------------------------------------|-----|------|------|------|-------|-----|-------|---------|

| T2CON    | C8h | Timer/Counter 2 control                        | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2<br>Mode                        | _   | _    | _    | _    | _     | _   | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2<br>Reload/Capture High<br>byte | _   | _    | _    | _    | _     | _   | _     | _       |

| RCAP2L   | CAh | Timer/Counter 2<br>Reload/Capture Low<br>byte  | _   | _    | _    | _    | _     | _   | -     | _       |

| WDTRST   | A6h | WatchDog Timer<br>Reset                        | _   | _    | _    | _    | _     | _   | -     | -       |

| WDTPRG   | A7h | WatchDog Timer<br>Program                      | _   | _    | _    | _    | _     | S2  | S1    | S0      |

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|----------|-----|--------------------|--------|-----|-----|-----|-----|-----|----|----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

| SBUF     | 99h | Serial Data Buffer | -      | _   | _   | _   | -   | _   | -  | -  |

| SADEN    | B9h | Slave Address Mask | -      | _   | _   | _   | -   | _   | -  | -  |

| SADDR    | A9h | Slave Address      | -      | _   | _   | _   | -   | _   | -  | -  |

| Mnemonic | Add | Name                           | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|----------|-----|--------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| CCON     | D8h | PCA Timer/Counter Control      | CF      | CR      | -       | CCF4    | CCF3    | CCF2    | CCF1    | CCF0    |

| CMOD     | D9h | PCA Timer/Counter Mode         | CIDL    | WDTE    | -       | -       | -       | CPS1    | CPS0    | ECF     |

| CL       | E9h | PCA Timer/Counter Low byte     | _       | _       | _       | _       | _       | _       | _       | -       |

| СН       | F9h | PCA Timer/Counter High byte    | _       | _       | _       | _       | _       | _       | _       | -       |

| CCAPM0   | DAh | PCA Timer/Counter Mode 0       |         | ECOM0   | CAPP0   | CAPN0   | MAT0    | TOG0    | PWM0    | ECCF0   |

| CCAPM1   | DBh | PCA Timer/Counter Mode 1       |         | ECOM1   | CAPP1   | CAPN1   | MAT1    | TOG1    | PWM1    | ECCF1   |

| CCAPM2   | DCh | PCA Timer/Counter Mode 2       | -       | ECOM2   | CAPP2   | CAPN2   | MAT2    | TOG2    | PWM2    | ECCF2   |

| CCAPM3   | DDh | PCA Timer/Counter Mode 3       |         | ECOM3   | CAPP3   | CAPN3   | MAT3    | TOG3    | PWM3    | ECCF3   |

| CCAPM4   | DEh | PCA Timer/Counter Mode 4       |         | ECOM4   | CAPP4   | CAPN4   | MAT4    | TOG4    | PWM4    | ECCF4   |

| CCAP0H   | FAh | PCA Compare Capture Module 0 H | CCAP0H7 | CCAP0H6 | CCAP0H5 | CCAP0H4 | CCAP0H3 | CCAP0H2 | CCAP0H1 | CCAP0H0 |

| CCAP1H   | FBh | PCA Compare Capture Module 1 H | CCAP1H7 | CCAP1H6 | CCAP1H5 | CCAP1H4 | CCAP1H3 | CCAP1H2 | CCAP1H1 | CCAP1H0 |

| CCAP2H   | FCh | PCA Compare Capture Module 2 H | CCAP2H7 | CCAP2H6 | CCAP2H5 | CCAP2H4 | CCAP2H3 | CCAP2H2 | CCAP2H1 | CCAP2H0 |

| ССАРЗН   | FDh | PCA Compare Capture Module 3 H | CCAP3H7 | CCAP3H6 | CCAP3H5 | CCAP3H4 | CCAP3H3 | CCAP3H2 | CCAP3H1 | CCAP3H0 |

| CCAP4H   | FEh | PCA Compare Capture Module 4 H | CCAP4H7 | CCAP4H6 | CCAP4H5 | CCAP4H4 | CCAP4H3 | CCAP4H2 | CCAP4H1 | CCAP4H0 |

| CCAP0L   | EAh | PCA Compare Capture Module 0 L | CCAP0L7 | CCAP0L6 | CCAP0L5 | CCAP0L4 | CCAP0L3 | CCAP0L2 | CCAP0L1 | CCAP0L0 |

| CCAP1L   | EBh | PCA Compare Capture Module 1 L | CCAP1L7 | CCAP1L6 | CCAP1L5 | CCAP1L4 | CCAP1L3 | CCAP1L2 | CCAP1L1 | CCAP1L0 |

| CCAP2L   | ECh | PCA Compare Capture Module 2 L | CCAP2L7 | CCAP2L6 | CCAP2L5 | CCAP2L4 | CCAP2L3 | CCAP2L2 | CCAP2L1 | CCAP2L0 |

| CCAP3L   | EDh | PCA Compare Capture Module 3 L | CCAP3L7 | CCAP3L6 | CCAP3L5 | CCAP3L4 | CCAP3L3 | CCAP3L2 | CCAP3L1 | CCAP3L0 |

| CCAP4L   | EEh | PCA Compare Capture Module 4 L | CCAP4L7 | CCAP4L6 | CCAP4L5 | CCAP4L4 | CCAP4L3 | CCAP4L2 | CCAP4L1 | CCAP4L0 |

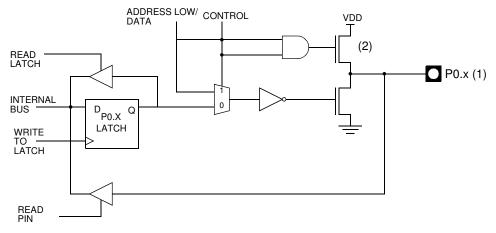

Note: In order to prevent any incorrect operation while operating in the X2 mode, users must be aware that all peripherals using the clock frequency as a time reference (UART, timers...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. A UART with a 4800 baud rate will have a 9600 baud rate.

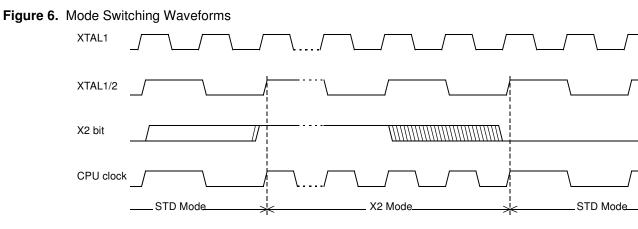

#### Figure 15. Power Fail Detect

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

.

## Registers

Table 10.PCON RegisterPCON (S87:h)Power configuration Register

| 7             | 6               | 5                                             | 4                                                                                                                                                                        | 3               | 2             | 1              | 0            |  |  |  |

|---------------|-----------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----------------|--------------|--|--|--|

| -             | -               | -                                             | -                                                                                                                                                                        | GF1             | GF0           | PD             | IDL          |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   | escription                                                                                                                                                               |                 |               |                |              |  |  |  |

| 7-4           | -               | <b>Reserved</b><br>The value re               | eserved<br>ne value read from these bits is indeterminate. Do not set these bits.                                                                                        |                 |               |                |              |  |  |  |

| 3             | GF1             | One use is to                                 | eneral Purpose flag 1<br>one use is to indicate whether an interrupt occurred during normal operation or<br>uring Idle mode.                                             |                 |               |                |              |  |  |  |

| 2             | GF0             | General Pur<br>One use is to<br>during Idle m | indicate whe                                                                                                                                                             | ther an interru | pt occurred d | uring normal o | operation or |  |  |  |

| 1             | PD              | Cleared by h<br>Set to activa                 | Power-Down Mode bit<br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Power-Down mode.<br>f IDL and PD are both set, PD takes precedence. |                 |               |                |              |  |  |  |

| 0             | IDL             | Cleared by h<br>Set to activa                 | dle Mode bit<br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Idle mode.<br>f IDL and PD are both set, PD takes precedence.              |                 |               |                |              |  |  |  |

Reset Value= XXXX 0000b

## Examples

```

;* DPTR contain address to read.

;* Acc contain the reading value

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

api_rd_eeprom_byte:

MOV EECON, #02h; map EEPROM in XRAM space

MOVX A, @DPTR

MOV EECON, #00h; unmap EEPROM

ret

;* NAME: api_ld_eeprom_cl

;* DPTR contain address to load

;* Acc contain value to load

;* NOTE: in this example we load only 1 byte, but it is possible upto

;* 128 Bytes.

;* before execute this function, be sure the EEPROM is not BUSY

api_ld_eeprom_cl:

MOV EECON, #02h ; map EEPROM in XRAM space

MOVX @DPTR, A

MOVEECON, #00h; unmap EEPROM

ret

;* NAME: api_wr_eeprom

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

******

api_wr_eeprom:

MOV EECON, #050h

MOV EECON, #0A0h

ret

```

## Registers

## Table 11. EECON Register

EECON (S:0D2h) EEPROM Control Register

| 7          | 6               | 5                         | 4                                                                                                                                                                    | 3               | 2              | 1             | 0      |  |  |  |

|------------|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|--------|--|--|--|

| EEPL3      | EEPL2           | EEPL1                     | EEPL0                                                                                                                                                                | -               | -              | EEE           | EEBUSY |  |  |  |

| Bit Number | Bit<br>Mnemonic | Descriptio                | n                                                                                                                                                                    |                 |                |               |        |  |  |  |

| 7-4        | EEPL3-0         | •                         | rogramming Launch command bits<br>rite 5Xh followed by AXh to EEPL to launch the programming.                                                                        |                 |                |               |        |  |  |  |

| 3          | -               | Reserved<br>The value r   | ead from this                                                                                                                                                        | bit is indetern | ninate. Do not | set this bit. |        |  |  |  |

| 2          | -               | Reserved<br>The value r   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                      |                 |                |               |        |  |  |  |

| 1          | EEE             | Set to map<br>latches)    | nable EEPROM Space bit<br>et to map the EEPROM space during MOVX instructions (Write in the column<br>tches)<br>lear to map the XRAM space during MOVX.              |                 |                |               |        |  |  |  |

| 0          | EEBUSY          | Set by hard<br>Cleared by | Programming Busy flag<br>Set by hardware when programming is in progress.<br>Cleared by hardware when programming is done.<br>Can not be set or cleared by software. |                 |                |               |        |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

## Cross Flash Memory Access

|           |                    | Action            | FM0<br>(user Flash) | FM1<br>(boot Flash) |

|-----------|--------------------|-------------------|---------------------|---------------------|

|           |                    | Read              | ok                  | -                   |

| E         | FM0                | Load column latch | ok                  | -                   |

| ig from   | (user Flash)       | Write             | -                   | -                   |

| executing |                    | Read              | ok                  | ok                  |

|           | FM1                | Load column latch | ok                  | -                   |

| Code      | (boot Flash)       | Write             | ok                  | -                   |

|           |                    | Read              | (a)                 | -                   |

|           | External<br>memory | Load column latch | -                   | -                   |

|           | EA = 0             | Write             | -                   | -                   |

(a) Depend upon general lock bit configuration.

# Sharing Instructions Table 19. Instructions shared

| Action | RAM | XRAM<br>ERAM | EEPROM<br>DATA | Boot<br>FLASH | FM0   | Hardware<br>Byte | XROW  |

|--------|-----|--------------|----------------|---------------|-------|------------------|-------|

| Read   | MOV | MOVX         | MOVX           | MOVC          | MOVC  | MOVC             | MOVC  |

| Write  | MOV | MOVX         | MOVX           | -             | by cl | by cl            | by cl |

Note: by cl : using Column Latch

## Table 20. Read MOVX A, @DPTR

| EEE bit in<br>EECON<br>Register | FPS in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>DATA | Flash<br>Column<br>Latch |

|---------------------------------|-------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                       | Х      | х  | OK           |                |                          |

| 0                               | 1                       | Х      | х  | ОК           |                |                          |

| 1                               | 0                       | Х      | х  |              | ОК             |                          |

| 1                               | 1                       | Х      | Х  | OK           |                |                          |

## Table 21. Write MOVX @DPTR,A

| EEE bit in<br>EECON<br>Register | FPS bit in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>Data | Flash<br>Column<br>Latch |

|---------------------------------|-----------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                           | х      | Х  | ОК           |                |                          |

| 0                               | 4                           | х      | 1  |              |                | ОК                       |

| 0                               | I                           | ~      | 0  | ОК           |                |                          |

| 1                               | 0                           | х      | Х  |              | ОК             |                          |

| 1                               | 1                           | x      | 1  |              |                | ОК                       |

| I                               | I                           | ~      | 0  | ОК           |                |                          |

| Timer 1                                   | <ul> <li>Timer 1 is identical to Timer 0 excepted for Mode 3 which is a hold-count mode. The following comments help to understand the differences:</li> <li>Timer 1 functions as either a Timer or event Counter in three modes of operation. Figure 35 to Figure 37 show the logical configuration for modes 0, 1, and 2. Timer 1's mode 3 is a hold-count mode.</li> <li>Timer 1 is controlled by the four high-order bits of TMOD register (see Figure 31) and bits 2, 3, 6 and 7 of TCON register (see Figure 30). TMOD register selects the method of Timer gating (GATE1), Timer or Counter operation (C/T1#) and mode of</li> </ul> |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | operation (M11 and M01). TCON register provides Timer 1 control functions:<br>overflow flag (TF1), run control bit (TR1), interrupt flag (IE1) and interrupt type<br>control bit (IT1).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           | • Timer 1 can serve as the Baud Rate Generator for the Serial Port. Mode 2 is best suited for this purpose.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                           | <ul> <li>For normal Timer operation (GATE1 = 0), setting TR1 allows TL1 to be incremented<br/>by the selected input. Setting GATE1 and TR1 allows external pin INT1# to control<br/>Timer operation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                           | • Timer 1 overflow (count rolls over from all 1s to all 0s) sets the TF1 flag generating an interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                           | • When Timer 0 is in mode 3, it uses Timer 1's overflow flag (TF1) and run control bit (TR1). For this situation, use Timer 1 only for applications that do not require an interrupt (such as a Baud Rate Generator for the Serial Port) and switch Timer 1 in and out of mode 3 to turn it off and on.                                                                                                                                                                                                                                                                                                                                     |

|                                           | It is important to stop Timer/Counter before changing mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mode 0 (13-bit Timer)                     | Mode 0 configures Timer 1 as a 13-bit Timer, which is set up as an 8-bit Timer (TH1 reg-<br>ister) with a modulo-32 prescaler implemented with the lower 5 bits of the TL1 register<br>(see Figure 35). The upper 3 bits of TL1 register are ignored. Prescaler overflow incre-<br>ments TH1 register.                                                                                                                                                                                                                                                                                                                                      |

| Mode 1 (16-bit Timer)                     | Mode 1 configures Timer 1 as a 16-bit Timer with TH1 and TL1 registers connected in cascade (see Figure 36). The selected input increments TL1 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Mode 2 (8-bit Timer with Auto-<br>Reload) | Mode 2 configures Timer 1 as an 8-bit Timer (TL1 register) with automatic reload from TH1 register on overflow (see Figure 37). TL1 overflow sets TF1 flag in TCON register and reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged.                                                                                                                                                                                                                                                                                                                                                         |

| Mode 3 (Halt)                             | Placing Timer 1 in mode 3 causes it to halt and hold its count. This can be used to halt Timer 1 when TR1 run control bit is not available i.e. when Timer 0 is in mode 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Table 31. TMOD Register

TMOD (S:89h) Timer/Counter Mode Control Register

| 7             | 6               | 5                                          | 4                                                                                                                                                                                                  | 3                                                     | 2               | 1               | 0           |

|---------------|-----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-------------|

| GATE1         | C/T1#           | M11                                        | M01                                                                                                                                                                                                | GATE0                                                 | C/T0#           | M10             | M00         |

| Bit<br>Number | Bit<br>Mnemonic | Description                                |                                                                                                                                                                                                    |                                                       |                 |                 |             |

| 7             | GATE1           | Clear to enal                              | Timer 1 Gating Control Bit<br>Clear to enable Timer 1 whenever TR1 bit is set.<br>Set to enable Timer 1 only while INT1# pin is high and TR1 bit is set.                                           |                                                       |                 |                 |             |

| 6             | C/T1#           | Clear for Tim                              | Timer 1 Counter/Timer Select Bit<br>Clear for Timer operation: Timer 1 counts the divided-down system clock.<br>Set for Counter operation: Timer 1 counts negative transitions on external pin T1. |                                                       |                 |                 |             |

| 5             | M11             |                                            | le Select Bits                                                                                                                                                                                     | -                                                     |                 |                 |             |

| 4             | M01             | <u>M11 M01</u><br>0 0<br>0 1<br>1 0<br>1 1 | <ul> <li>Mode 1: 16-bit Timer/Counter.</li> <li>Mode 2: 8-bit auto-reload Timer/Counter (TL1)<sup>(1)</sup></li> </ul>                                                                             |                                                       |                 |                 | er (TL1).   |

| 3             | GATE0           | Clear to enal                              | Timer 0 Gating Control Bit<br>Clear to enable Timer 0 whenever TR0 bit is set.<br>Set to enable Timer/Counter 0 only while INT0# pin is high and TR0 bit is set.                                   |                                                       |                 |                 | bit is set. |

| 2             | C/T0#           | Clear for Tim                              | Timer 0 Counter/Timer Select Bit<br>Clear for Timer operation: Timer 0 counts the divided-down system clock.<br>Set for Counter operation: Timer 0 counts negative transitions on external pin T0. |                                                       |                 |                 |             |

| 1             | M10             | <b>Timer 0 Mod</b><br>M10 M00<br>0 0       |                                                                                                                                                                                                    |                                                       |                 | ı 5-bit prescal | er (TL0).   |

| 0             | M00             | 1 0<br>1 1                                 | Mode 2: 8-<br>Mode 3: Tl                                                                                                                                                                           | bit auto-reload<br>L0 is an 8-bit T<br>g Timer 1's TF | I Timer/Counter | . ,             |             |

1. Reloaded from TH1 at overflow.

2. Reloaded from TH0 at overflow.

Reset Value = 0000 0000b

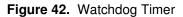

## Watchdog Timer

AT89C51AC3 contains a powerful programmable hardware Watchdog Timer (WDT) that automatically resets the chip if it software fails to reset the WDT before the selected time interval has elapsed. It permits large Time-Out ranking from 16ms to 2s @Fosc = 12MHz in X1 mode.

This WDT consists of a 14-bit counter plus a 7-bit programmable counter, a Watchdog Timer reset register (WDTRST) and a Watchdog Timer programming (WDTPRG) register. When exiting reset, the WDT is -by default- disable.

To enable the WDT, the user has to write the sequence 1EH and E1H into WDTRST register no instruction in between. When the Watchdog Timer is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is  $96xT_{OSC}$ , where  $T_{OSC}=1/F_{OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset

Note: When the Watchdog is enable it is impossible to change its period.

Table 45. WDTRST Register

WDTRST (S:A6h Write only) Watchdog Timer Enable Register

| 7             | 6               | 5           | 4            | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|--------------|---|---|---|---|

| -             | -               | -           | -            | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |              |   |   |   |   |

| 7             | _               | Watchdog Co | antral Value |   |   |   |   |

Reset Value = 1111 1111b

Note: The WDRST register is used to reset/enable the WDT by writing 1EH then E1H in sequence without instruction between these two sequences.

Functional Description

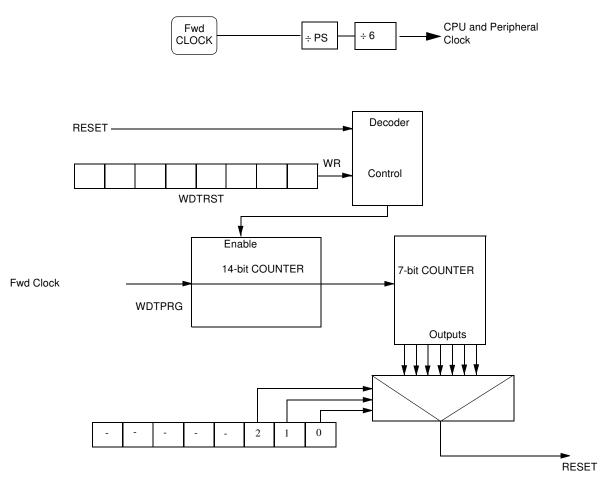

Figure 44 shows a detailed structure of the SPI Module.

Figure 44. SPI Module Block Diagram

### **Operating Modes**

The Serial Peripheral Interface can be configured in one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI Module is made through two registers:

- The Serial Peripheral Control register (SPCON)

- The Serial Peripheral Status and Control Register (SPSCR)

Once the SPI is configured, the data exchange is made using:

• The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

| Analog-to-Digital<br>Converter (ADC) | This section describes the on-chip 10 bit analog-to-digital converter of the AT89C51AC3. Eight ADC channels are available for sampling of the external sources AN0 to AN7. An analog multiplexer allows the single ADC converter to select one from the 8 ADC channels as ADC input voltage (ADCIN). ADCIN is converted by the 10-bit cascaded potentiometric ADC.                                                                                                                                                                      |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                      | Two kinds of conversion are available:<br>- Standard conversion (8 bits).<br>- Precision conversion (10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                      | For the precision conversion, set bit PSIDLE in ADCON register and start conversion. The device is in a pseudo-idle mode, the CPU does not run but the peripherals are always running. This mode allows digital noise to be as low as possible, to ensure high precision conversion.                                                                                                                                                                                                                                                    |  |  |  |  |

|                                      | For this mode it is necessary to work with end of conversion interrupt, which is the only way to wake the device up.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                      | If another interrupt occurs during the precision conversion, it will be treated only after this conversion is ended.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Features                             | <ul> <li>8 channels with multiplexed inputs</li> <li>10-bit cascaded potentiometric ADC</li> <li>Conversion time 16 micro-seconds (typ.)</li> <li>Zero Error (offset) ± 2 LSB max</li> <li>Positive External Reference Voltage Range (VREF) 2.4 to 3.0Volt (typ.)</li> <li>ADCIN Range 0 to 3Volt</li> <li>Integral non-linearity typical 1 LSB, max. 2 LSB</li> <li>Differential non-linearity typical 0.5 LSB, max. 1 LSB</li> <li>Conversion Complete Flag or Conversion Complete Interrupt</li> <li>Selectable ADC Clock</li> </ul> |  |  |  |  |

| ADC Port1 I/O Functions              | Port 1 pins are general I/O that are shared with the ADC channels. The channel select bit in ADCF register define which ADC channel/port1 pin will be used as ADCIN. The remaining ADC channels/port1 pins can be used as general-purpose I/O or as the alternate function that is available.                                                                                                                                                                                                                                           |  |  |  |  |

A conversion launched on a channel which are not selected on ADCF register will not have any effect.

## Table 70. IPH1 Register

IPH1 (S:F7h) Interrupt High Priority Register 1

| 7             | 6               | 5                                                                                                                                                                       | 4                                                                               | 3               | 2              | 1            | 0 |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|----------------|--------------|---|

| -             | -               | -                                                                                                                                                                       | -                                                                               | SPIH            | -              | PADCH        | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                             |                                                                                 |                 |                |              |   |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                                                        | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                                                        | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |

| 5             | -               | Reserved<br>The value rea                                                                                                                                               | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |

| 4             | -               | Reserved<br>The value rea                                                                                                                                               | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |

| 3             | SPIH            | SPI Interrup           SPIH         SPIL           0         0           0         1           1         0           1         1                                        |                                                                                 | vel Most Sign   | ificant bit    |              |   |

| 2             | -               | Reserved<br>The value rea                                                                                                                                               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |   |

| 1             | PADCH           | ADC Interrupt Priority Level Most Significant bit         PADCH PADCL Priority level         0       0         Lowest       0         1       0         1       Highest |                                                                                 |                 |                |              |   |

| 0             | -               | Reserved<br>The value rea                                                                                                                                               | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |

Reset Value = XXXX 0X0Xb

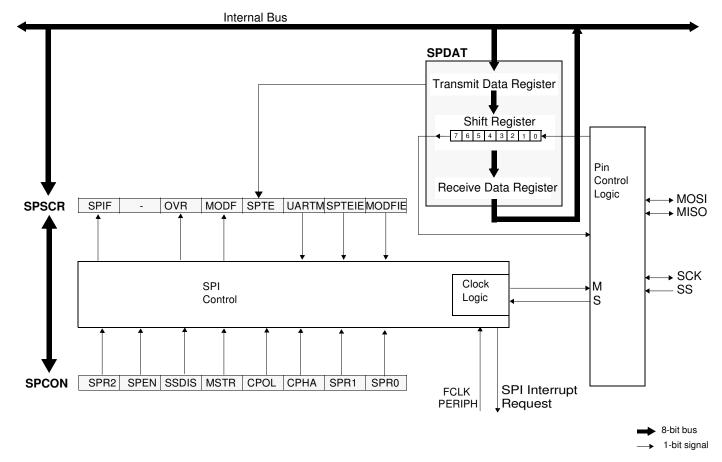

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# **Ordering Information**

## Table 85. Possible Order Entries

| Part Number      | Boot Loader | Temperature Range  | Package  | Packing | Product Marking |  |

|------------------|-------------|--------------------|----------|---------|-----------------|--|

| AT89C51AC3-RLTIM |             |                    |          |         |                 |  |

| AT89C51AC3-SLSIM |             |                    | OBSOLETE |         |                 |  |

| AT89C51AC3-RDTIM |             |                    | OBSOLETE |         |                 |  |

| AT89C51AC3-S3SIM |             |                    |          |         |                 |  |

|                  |             |                    |          |         |                 |  |

| AT89C51AC3-RLTUM | UART        | Industrial & Green | VQFP44   | Tray    | AT89C51AC3-M    |  |

| AT89C51AC3-SLSUM | UART        | Industrial & Green | PLCC44   | Stick   | AT89C51AC3-IM   |  |

| AT89C51AC3-RDTUM | UART        | Industrial & Green | VQFP64   | Tray    | AT89C51AC3-IM   |  |

| AT89C51AC3-S3SUM | UART        | Industrial & Green | PLCC52   | Stick   | AT89C51AC3-IM   |  |

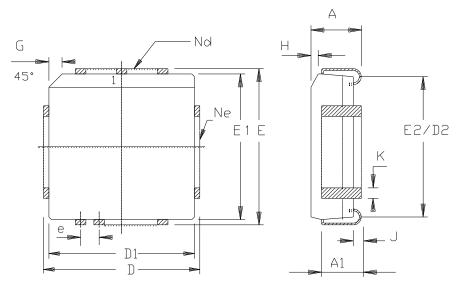

## PLCC52

|    | М          | М     | I NCH |        |  |

|----|------------|-------|-------|--------|--|

| Α  | 4. 20      | 4. 57 | . 165 | . 180  |  |

| A1 | 2, 29      | 3.30  | . 090 | . 1 30 |  |

| D  | 19.94      | 20.19 | . 785 | . 795  |  |

| D1 | 19.05      | 19.25 | . 750 | . 758  |  |

| D2 | 17.53      | 18.54 | . 690 | . 730  |  |

| E  | 19.94      | 20.19 | . 785 | . 795  |  |

| E1 | 19.05      | 19.25 | . 750 | . 758  |  |

| E5 | 17.53      | 18.54 | . 690 | . 730  |  |

| e  | 1.27       | BSC   | . 050 | BSC    |  |

| G  | 1.07       | 1.22  | . 042 | . 048  |  |

| Н  | 1.07       | 1.42  | . 042 | . 056  |  |

| J  | 0.51       | -     | . 020 | -      |  |

| К  | 0.33       | 0.53  | . 013 | . 021  |  |

| Nd | 1          | 3     | 1     | 3      |  |

| Ne | 1          | 3     | 13    |        |  |

| P  | PKG STD 00 |       |       |        |  |