Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 60MHz                                                       |

| Connectivity               | UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 36                                                          |

| Program Memory Size        | 64KB (64K × 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 2.25К х 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LQFP                                                     |

| Supplier Device Package    | 44-VQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51ac3-rltum |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

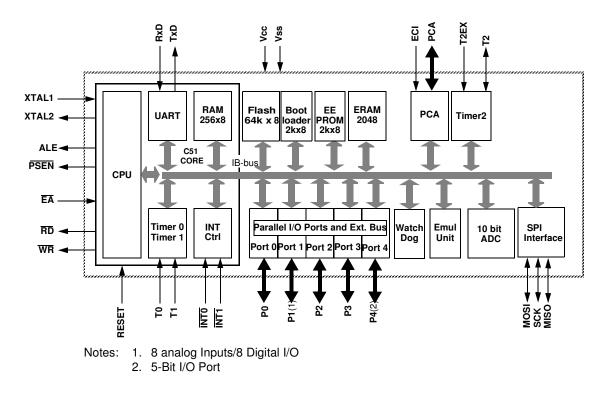

# **Block Diagram**

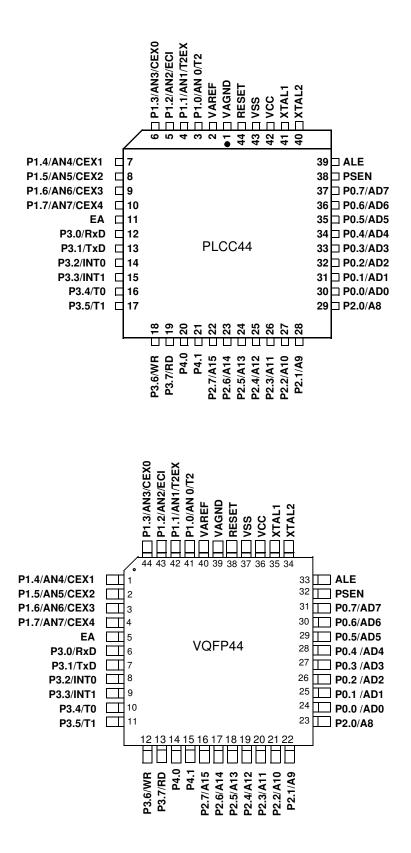

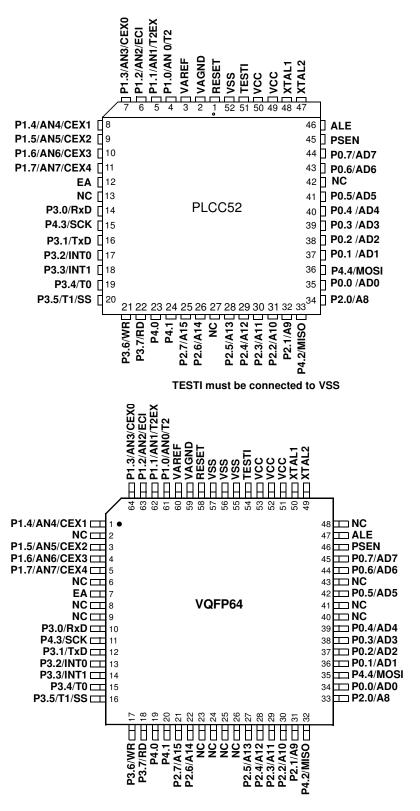

## **Pin Configuration**

**TESTI must be connected to VSS**

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | <b>Port 3:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current ( $I_{IL}$ , see section "Electrical Characteristic") because of the internal pull-ups. The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows: |

|          |      | P3.0/RxD:<br>Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface<br>P3.1/TxD:<br>Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface<br>P3.2/INT0:                                                                                                                                                                                                                                                                                                                                                                              |

|          |      | External interrupt 0 input/timer 0 gate control input<br>P3.3/INT1:<br>External interrupt 1 input/timer 1 gate control input<br>P3.4/T0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |      | Timer 0 counter input<br>P3.5/T1/SS:<br>Timer 1 counter input<br>SPI Slave Select<br>P3.6/WR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |      | External Data Memory write strobe; latches the data byte from port 0 into the external data memory<br>P3.7/RD:<br>External Data Memory read strobe; Enables the external data memory.<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                       |

| P4.0:4   | I/O  | Port 4:<br>Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled high by the internal<br>pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being pulled low externally will be a source of<br>current (IIL, on the datasheet) because of the internal pull-up transistor.<br>The secondary functions are assigned to the 5 pins of port 4 as follows:<br>P4.0: Regular Port I/O                                                                                                                                         |

|          |      | P4.1: Regular Port I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |      | P4.2/MISO:<br>Master Input Slave Output of SPI controller<br>P4.3/SCK:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |      | Serial Clock of SPI controller<br>P4.4/MOSI:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | Master Ouput Slave Input of SPI controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |      | It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

order. The page address of the last address loaded in the column latches will be used for the whole page.

When programming is launched, an automatic erase of the locations loaded in the column latches is first performed, then programming is effectively done. Thus no page or block erase is needed and only the loaded data are programmed in the corresponding page

- Notes: 1. : If no bytes are written in the column latches the SEQERR bit in the FSTA register will be set.

- 2. When a flash write sequence is in progress (FBUSY is set) a write sequence to the column latches will be ignored and the content of the column latches at the time of the launch write sequence will be preserved.

- 3. MOVX @DPTR, A instruction must be used to load the column latches. Never use MOVX @Ri, A instructions.

- 4. When a programming sequence is launched, Flash bytes corresponding to activated bytes in the column latches are first erased then the bytes in the column latches are copied into the Flash bytes. Flash bytes corresponding to bytes in the column latches not activated (not loaded during the load column latches sequence) will not be erased and written.

The following procedure is used to load the column latches and is summarized in Figure 25:

- Save and Disable interrupt and map the column latch space by setting FPS bit.

- Load the DPTR with the address to load.

- Load Accumulator register with the data to load.

- Execute the MOVX @DPTR, A instruction.

- If needed loop the three last instructions until the page is completely loaded.

- unmap the column latch.

- Restore Interrupt

# Sharing Instructions Table 19. Instructions shared

| Action | RAM | XRAM<br>ERAM | EEPROM<br>DATA | Boot<br>FLASH | FM0   | Hardware<br>Byte | XROW  |

|--------|-----|--------------|----------------|---------------|-------|------------------|-------|

| Read   | MOV | MOVX         | MOVX           | MOVC          | MOVC  | MOVC             | MOVC  |

| Write  | MOV | MOVX         | MOVX           | -             | by cl | by cl            | by cl |

Note: by cl : using Column Latch

#### Table 20. Read MOVX A, @DPTR

| EEE bit in<br>EECON<br>Register | FPS in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>DATA | Flash<br>Column<br>Latch |

|---------------------------------|-------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                       | Х      | х  | OK           |                |                          |

| 0                               | 1                       | Х      | х  | ОК           |                |                          |

| 1                               | 0                       | Х      | х  |              | ОК             |                          |

| 1                               | 1                       | Х      | Х  | OK           |                |                          |

#### Table 21. Write MOVX @DPTR,A

| EEE bit in<br>EECON<br>Register | FPS bit in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>Data | Flash<br>Column<br>Latch |

|---------------------------------|-----------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                           | х      | Х  | ОК           |                |                          |

| 0                               |                             | x      | 1  |              |                | ОК                       |

| 0                               | I                           |        | 0  | ОК           |                |                          |

| 1                               | 0                           | х      | Х  |              | ОК             |                          |

| 1                               |                             |        | 1  |              |                | ОК                       |

| 1                               | I                           | Х      | 0  | OK           |                |                          |

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Registers

Table 25. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                                                                                                         | 4                                                                                                                                                                                                                         | 3                                                 | 2                                  | 1                                           | 0       |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------|---------------------------------------------|---------|--|--|

| FE/SM0        | SM1             | SM2                                                                                                       | REN                                                                                                                                                                                                                       | TB8                                               | RB8                                | ТІ                                          | RI      |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                               |                                                                                                                                                                                                                           |                                                   |                                    |                                             |         |  |  |

| 7             | FE              | Clear to rese                                                                                             |                                                                                                                                                                                                                           |                                                   | d by a valid sto<br>t is detected. | op bit.                                     |         |  |  |

|               | SM0             |                                                                                                           | <b>lode bit 0 (Si</b><br>for serial por                                                                                                                                                                                   | MOD0=0)<br>t mode select                          | ion.                               |                                             |         |  |  |

| 6             | SM1             | Serial port N           SM0         SM1           0         0           1         0           1         1 | 0       Shift Register       F <sub>XTAL</sub> /12 (or F <sub>XTAL</sub> /6 in mode X2)         0       1       8-bit UART       Variable         0       9-bit UART       F <sub>XTAL</sub> /64 or F <sub>XTAL</sub> /32 |                                                   |                                    |                                             |         |  |  |

| 5             | SM2             | Clear to disa                                                                                             | ble multiproce                                                                                                                                                                                                            | essor commur                                      | ication feature                    | t <b>ion Enable b</b><br>e.<br>n mode 2 and |         |  |  |

| 4             | REN             |                                                                                                           | <b>nable bit</b><br>ble serial rece<br>serial recept                                                                                                                                                                      |                                                   |                                    |                                             |         |  |  |

| 3             | TB8             | Clear to trans                                                                                            | <b>Bit 8/Ninth b</b><br>smit a logic 0<br>nit a logic 1 in                                                                                                                                                                | in the 9th bit.                                   | in modes 2 a                       | and 3                                       |         |  |  |

| 2             | RB8             | Cleared by h                                                                                              | ardware if 9th                                                                                                                                                                                                            | eceived in m<br>bit received i<br>eceived is a lo | 0                                  |                                             |         |  |  |

| 1             | TI              | Clear to ackr<br>Set by hardw                                                                             | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>stop bit in the other modes.                                         |                                                   |                                    |                                             |         |  |  |

| 0             | RI              | Set by hardw                                                                                              | nowledge inter                                                                                                                                                                                                            | d of the 8th bit                                  | time in mode                       | 0, see Figure                               | 33. and |  |  |

Reset Value = 0000 0000b Bit addressable

#### Table 26. SADEN Register

SADEN (S:B9h) Slave Address Mask Register

| 7             | 6               | 5           | 4                                      | 3 | 2 | 1 | 0 |  |

|---------------|-----------------|-------------|----------------------------------------|---|---|---|---|--|

| -             | -               | -           | -                                      | - | - | - | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description |                                        |   |   |   |   |  |

| 7-0           |                 | Mask Data f | Mask Data for Slave Individual Address |   |   |   |   |  |

Reset Value = 0000 0000b Not bit addressable

Table 27. SADDR Register

SADDR (S:A9h) Slave Address Register

| 7             | 6               | 5            | 4                        | 3 | 2 | 1 | 0 |  |  |  |

|---------------|-----------------|--------------|--------------------------|---|---|---|---|--|--|--|

| -             | -               | -            | -                        | - | - | - | - |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description  | Description              |   |   |   |   |  |  |  |

| 7-0           |                 | Slave Indivi | Slave Individual Address |   |   |   |   |  |  |  |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. SBUF Register

SBUF (S:99h) Serial Data Buffer

| 7             | 6               | 5            | 4            | 3              | 2 | 1 | 0 |

|---------------|-----------------|--------------|--------------|----------------|---|---|---|

| -             | -               | -            | -            | -              | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |              |                |   |   |   |

| 7-0           |                 | Data sent/re | ceived by Se | erial I/O Port |   |   |   |

Reset Value = 0000 0000b Not bit addressable

| R |

|---|

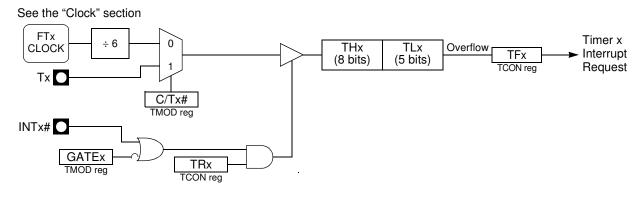

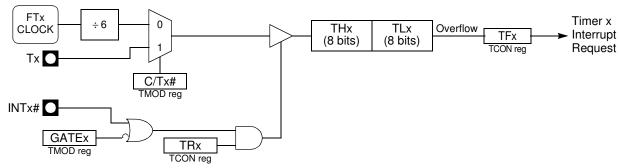

| Timers/Counters             | The AT89C51AC3 implements two general-purpose, 16-bit Timers/Counters. Such are identified as Timer 0 and Timer 1, and can be independently configured to operate in a variety of modes as a Timer or an event Counter. When operating as a Timer, the Timer/Counter runs for a programmed length of time, then issues an interrupt request. When operating as a Counter, the Timer/Counter counts negative transitions on an external pin. After a preset number of counts, the Counter issues an interrupt request. The various operating modes of each Timer/Counter are described in the following sections.                                                                        |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer/Counter<br>Operations | A basic operation is Timer registers THx and TLx ( $x = 0, 1$ ) connected in cascade to form a 16-bit Timer. Setting the run control bit (TRx) in TCON register (see Figure 30) turns the Timer on by allowing the selected input to increment TLx. When TLx overflows it increments THx; when THx overflows it sets the Timer overflow flag (TFx) in TCON register. Setting the TRx does not clear the THx and TLx Timer registers. Timer registers can be accessed to obtain the current count or to enter preset values. They can be read at any time but TRx bit must be cleared to preset their values, otherwise the behavior of the Timer/Counter is unpredictable.              |

|                             | The C/Tx# control bit selects Timer operation or Counter operation by selecting the divided-down peripheral clock or external pin Tx as the source for the counted signal. TRx bit must be cleared when changing the mode of operation, otherwise the behavior of the Timer/Counter is unpredictable.                                                                                                                                                                                                                                                                                                                                                                                   |

|                             | For Timer operation (C/Tx# = 0), the Timer register counts the divided-down peripheral clock. The Timer register is incremented once every peripheral cycle (6 peripheral clock periods). The Timer clock rate is $F_{PER}/6$ , i.e. $F_{OSC}/12$ in standard mode or $F_{OSC}/6$ in X2 mode.                                                                                                                                                                                                                                                                                                                                                                                           |

|                             | For Counter operation (C/Tx# = 1), the Timer register counts the negative transitions on the Tx external input pin. The external input is sampled every peripheral cycles. When the sample is high in one cycle and low in the next one, the Counter is incremented. Since it takes 2 cycles (12 peripheral clock periods) to recognize a negative transition, the maximum count rate is $F_{PER}/12$ , i.e. $F_{OSC}/24$ in standard mode or $F_{OSC}/12$ in X2 mode. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full peripheral cycle. |

| Timer 0                     | Timer 0 functions as either a Timer or event Counter in four modes of operation.<br>Figure 35 to Figure 38 show the logical configuration of each mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                             | Timer 0 is controlled by the four lower bits of TMOD register (see Figure 31) and bits 0, 1, 4 and 5 of TCON register (see Figure 30). TMOD register selects the method of Timer gating (GATE0), Timer or Counter operation (T/C0#) and mode of operation (M10 and M00). TCON register provides Timer 0 control functions: overflow flag (TF0), run control bit (TR0), interrupt flag (IE0) and interrupt type control bit (IT0).                                                                                                                                                                                                                                                       |

|                             | For normal Timer operation (GATE0 = 0), setting TR0 allows TL0 to be incremented by the selected input. Setting GATE0 and TR0 allows external pin INT0# to control Timer operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                             | Timer 0 overflow (count rolls over from all 1s to all 0s) sets TF0 flag generating an inter-<br>rupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                             | It is important to stop Timer/Counter before changing mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Mode 0 (13-bit Timer)

Mode 0 configures Timer 0 as an 13-bit Timer which is set up as an 8-bit Timer (TH0 register) with a modulo 32 prescaler implemented with the lower five bits of TL0 register (see Figure 35). The upper three bits of TL0 register are indeterminate and should be ignored. Prescaler overflow increments TH0 register.

**Figure 35.** Timer/Counter x (x = 0 or 1) in Mode 0

#### Mode 1 (16-bit Timer)

Mode 1 configures Timer 0 as a 16-bit Timer with TH0 and TL0 registers connected in cascade (see Figure 36). The selected input increments TL0 register.

Figure 36. Timer/Counter x (x = 0 or 1) in Mode 1 See the "Clock" section

#### Table 31. TMOD Register

TMOD (S:89h) Timer/Counter Mode Control Register

| 7             | 6               | 5                                          | 4                                                                                                                                                                                                  | 3                                                     | 2               | 1            | 0           |  |  |

|---------------|-----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|--------------|-------------|--|--|

| GATE1         | C/T1#           | M11                                        | M01                                                                                                                                                                                                | GATE0                                                 | C/T0#           | M10          | M00         |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                |                                                                                                                                                                                                    |                                                       |                 |              |             |  |  |

| 7             | GATE1           | Clear to enal                              | Timer 1 Gating Control Bit<br>Clear to enable Timer 1 whenever TR1 bit is set.<br>Set to enable Timer 1 only while INT1# pin is high and TR1 bit is set.                                           |                                                       |                 |              |             |  |  |

| 6             | C/T1#           | Clear for Tim                              | Timer 1 Counter/Timer Select Bit<br>Clear for Timer operation: Timer 1 counts the divided-down system clock.<br>Set for Counter operation: Timer 1 counts negative transitions on external pin T1. |                                                       |                 |              |             |  |  |

| 5             | M11             |                                            | le Select Bits                                                                                                                                                                                     | -                                                     |                 |              |             |  |  |

| 4             | M01             | <u>M11 M01</u><br>0 0<br>0 1<br>1 0<br>1 1 | <ul> <li>Mode 1: 16-bit Timer/Counter.</li> <li>Mode 2: 8-bit auto-reload Timer/Counter (TL1)<sup>(1)</sup></li> </ul>                                                                             |                                                       |                 |              |             |  |  |

| 3             | GATE0           | Clear to enal                              |                                                                                                                                                                                                    | <b>Bit</b><br>henever TR0 b<br>ter 0 only while       |                 | high and TR0 | bit is set. |  |  |

| 2             | C/T0#           | Clear for Tim                              |                                                                                                                                                                                                    | Select Bit<br>Timer 0 count<br>Timer 0 count          |                 |              |             |  |  |

| 1             | M10             | <b>Timer 0 Mod</b><br>M10 M00<br>0 0       | 0 0 Mode 0: 8-bit Timer/Counter (TH0) with 5-bit prescaler (TL0).                                                                                                                                  |                                                       |                 |              |             |  |  |

| 0             | M00             | 1 0<br>1 1                                 | Mode 2: 8-<br>Mode 3: Tl                                                                                                                                                                           | bit auto-reload<br>L0 is an 8-bit T<br>g Timer 1's TF | I Timer/Counter | . ,          |             |  |  |

1. Reloaded from TH1 at overflow.

2. Reloaded from TH0 at overflow.

Reset Value = 0000 0000b

### Registers

#### Table 36. T2CON Register

T2CON (S:C8h) Timer 2 Control Register

| 7             | 6               | 5                                                          | 4                                                                                                                                                                                                                                    | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|--|

| TF2           | EXF2            | RCLK                                                       | RCLK TCLK EXEN2 TR2 C/T2#                                                                                                                                                                                                            |   |   |   |   |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                | escription                                                                                                                                                                                                                           |   |   |   |   |  |  |

| 7             | TF2             | TF2 is not se<br>Must be clea                              | i <b>mer 2 Overflow Flag</b><br>F2 is not set if RCLK=1 or TCLK = 1.<br>lust be cleared by software.<br>et by hardware on timer 2 overflow.                                                                                          |   |   |   |   |  |  |

| 6             | EXF2            | Set when a c<br>EXEN2=1.<br>Set to cause<br>is enabled.    | et to cause the CPU to vector to timer 2 interrupt routine when timer 2 interrupt                                                                                                                                                    |   |   |   |   |  |  |

| 5             | RCLK            | Clear to use                                               | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                  |   |   |   |   |  |  |

| 4             | TCLK            | Clear to use                                               | Transmit Clock bit<br>Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                               |   |   |   |   |  |  |

| 3             | EXEN2           | Clear to igno<br>Set to cause                              | Timer 2 External Enable bit<br>Clear to ignore events on T2EX pin for timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is<br>detected, if timer 2 is not used to clock the serial port. |   |   |   |   |  |  |

| 2             | TR2             | Clear to turn                                              | Timer 2 Run Control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                                                                                                                                                     |   |   |   |   |  |  |

| 1             | C/T2#           | Clear for time                                             | <b>Timer/Counter 2 Select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin).                                                        |   |   |   |   |  |  |

| 0             | CP/RL2#         | If RCLK=1 or<br>timer 2 overf<br>Clear to auto<br>EXEN2=1. | <b>Timer 2 Capture/Reload bit</b><br>If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on<br>timer 2 overflow.<br>Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if          |   |   |   |   |  |  |

Reset Value = 0000 0000b Bit addressable

#### Table 39. TL2 Register

#### TL2 (S:CCh) Timer 2 Low Byte Register

| 7             | 6               | 5           | 4        | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|----------|---|---|---|---|

| -             | -               | -           | -        | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |          |   |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2. |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 40. RCAP2H Register

RCAP2H (S:CBh) Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5                                    | 4           | 3 | 2 | 1 | 0 |

|---------------|-----------------|--------------------------------------|-------------|---|---|---|---|

| -             | -               | -                                    | -           | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                          | Description |   |   |   |   |

| 7-0           |                 | High Byte of Timer 2 Reload/Capture. |             |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 41. RCAP2L Register

RCAP2L (S:CAH) TIMER 2 Reload/Capture Low Byte Register

| 7             | 6               | 5                                   | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------------------------------|---|---|---|---|---|

| -             | -               | -                                   | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                         |   |   |   |   |   |

| 7-0           |                 | Low Byte of Timer 2 Reload/Capture. |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

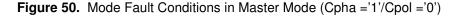

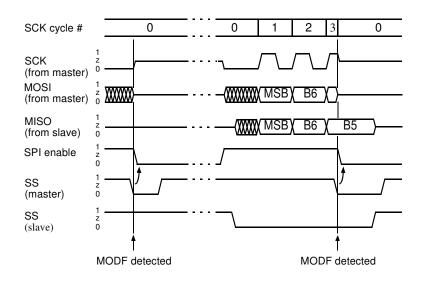

In a Master configuration, the  $\overline{SS}$  line can be used in conjunction with the MODF flag in the SPI Status register (SPSCR) to prevent multiple masters from driving MOSI and SCK (see Error conditions).

A high level on the  $\overline{SS}$  pin puts the MISO line of a Slave SPI in a high-impedance state.

The  $\overline{SS}$  pin could be used as a general-purpose if the following conditions are met:

- The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of configuration can be found when only one Master is driving the network and there is no way that the SS pin could be pulled low. Therefore, the MODF flag in the SPSCR will never be set<sup>(1)</sup>.

- The Device is configured as a Slave with CPHA and SSDIS control bits set<sup>(2)</sup>. This kind of configuration can happen when the system includes one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.

- Note: 1. Clearing SSDIS control bit does not clear MODF.

- 2. Special care should be taken not to set SSDIS control bit when CPHA ='0' because in this mode, the  $\overline{SS}$  is used to start the transmission.

Baud Rate In Master mode, the baud rate can be selected from a baud rate generator which is controlled by three bits in the SPCON register: SPR2, SPR1 and SPR0.The Master clock is selected from one of seven clock rates resulting from the division of the internal clock by 4, 8, 16, 32, 64 or 128.

Table 46 gives the different clock rates selected by SPR2:SPR1:SPR0.

In Slave mode, the maximum baud rate allowed on the SCK input is limited to  $F_{svs}/4$

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | Don't Use                    | No BRG                 |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

| 1    | 1    | 1    | Don't Use                    | No BRG                 |

#### Table 46. SPI Master Baud Rate Selection

#### **Error Conditions**

The following flags in the SPSCR register indicate the SPI error conditions:

Mode Fault Error (MODF)

Mode Fault error in Master mode SPI indicates that the level on the Slave Select  $(\overline{SS})$  pin is inconsistent with the actual mode of the device.

Mode fault detection in Master mode:

MODF is set to warn that there may be a multi-master conflict for system control. In this case, the SPI system is affected in the following ways:

- An SPI receiver/error CPU interrupt request is generated

- The SPEN bit in SPCON is cleared. This disables the SPI

- The MSTR bit in SPCON is cleared

Clearing the MODF bit is accomplished by a read of SPSCR register with MODF bit set, followed by a write to the SPCON register. SPEN Control bit may be restored to its original set state after the MODF bit has been cleared.

Mode fault detection in Slave mode

In slave mode, the MODF error is detected when SS goes high during a transmission. A transmission begins when SS goes low and ends once the incoming SCK goes back to its idle level following the shift of the eighteen data bit.

A MODF error occurs if a slave is selected (SS is low) and later unselected (SS is high) even if no SCK is sent to that slave.

At any time, a '1' on the SS pin of a slave SPI puts the MISO pin in a high impedance state and internal state counter is cleared. Also, the slave SPI ignores all incoming SCK clocks, even if it was already in the middle of a transmission. A new transmission will be performed as soon as SS pin returns low.

Table 54.

CCAPMn Registers

CCAPM0 (S:DAh) CCAPM1 (S:DBh) CCAPM2 (S:DCh) CCAPM3 (S:DDh) CCAPM4 (S:DEh) PCA Compare/Capture Module n Mode registers (n=0..4)

| 7             | 6               | 5                                                                                                                                                                                                       | 4                                                                                                                                                                                                                                                                     | 3                                          | 2    | 1    | 0         |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|-----------|--|

| -             | ECOMn           | CAPPn                                                                                                                                                                                                   | CAPNn                                                                                                                                                                                                                                                                 | MATn                                       | TOGn | PWMn | ECCFn     |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                             |                                                                                                                                                                                                                                                                       |                                            |      |      |           |  |

| 7             | -               | <b>Reserved</b><br>The Value re                                                                                                                                                                         | eserved<br>he Value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                         |                                            |      |      |           |  |

| 6             | ECOMn           | Clear to disa<br>Set to enable<br>The Compare                                                                                                                                                           | nable Compare Mode Module x bit<br>lear to disable the Compare function.<br>et to enable the Compare function.<br>he Compare function is used to implement the software Timer, the high-speed<br>utput, the Pulse Width Modulator (PWM) and the WatchDog Timer (WDT). |                                            |      |      |           |  |

| 5             | CAPPn           | Clear to disa                                                                                                                                                                                           | Capture Mode (Positive) Module x bit<br>Clear to disable the Capture function triggered by a positive edge on CEXx pin.<br>Set to enable the Capture function triggered by a positive edge on CEXx pin                                                                |                                            |      |      |           |  |

| 4             | CAPNn           | Capture Mode (Negative) Module x bit<br>Clear to disable the Capture function triggered by a negative edge on CEXx pin.<br>Set to enable the Capture function triggered by a negative edge on CEXx pin. |                                                                                                                                                                                                                                                                       |                                            |      |      |           |  |

| 3             | MATn            | Set when a r                                                                                                                                                                                            | Match Module x bit<br>Set when a match of the PCA Counter with the Compare/Capture register sets<br>CCFx bit in CCON register, flagging an interrupt.                                                                                                                 |                                            |      |      |           |  |

| 2             | TOGn            | The toggle m<br>Set when a r                                                                                                                                                                            | <b>Toggle Module x bit</b><br>The toggle mode is configured by setting ECOMx, MATx and TOGx bits.<br>Set when a match of the PCA Counter with the Compare/Capture register<br>toggles the CEXx pin.                                                                   |                                            |      |      |           |  |

| 1             | PWMn            | Set to config                                                                                                                                                                                           | Pulse Width Modulation Module x Mode bit<br>Set to configure the module x as an 8-bit Pulse Width Modulator with output<br>waveform on CEXx pin.                                                                                                                      |                                            |      |      | th output |  |

| 0             | ECCFn           | Clear to disa                                                                                                                                                                                           |                                                                                                                                                                                                                                                                       | <b>it</b><br>in CCON regis<br>CCON registe |      |      |           |  |

Reset Value = X000 0000b

#### Table 66. IEN1 Register

#### IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                   | 4                                                                                                   | 3    | 2 | 1    | 0 |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|---|------|---|--|

| -             | -               | -                                                                                                   | -                                                                                                   | ESPI | - | EADC | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                         | Vescription                                                                                         |      |   |      |   |  |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |      |   |      |   |  |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                    | eserved<br>he value read from this bit is indeterminate. Do not set this bit.                       |      |   |      |   |  |

| 5             | -               | <b>Reserved</b><br>The value rea                                                                    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |      |   |      |   |  |

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |                                                                                                     |      |   |      |   |  |

| 3             | ESPI            | Clear to disa                                                                                       | SPI Interrupt Enable bit<br>Clear to disable the SPI interrupt.<br>Set to enable the SPI interrupt. |      |   |      |   |  |

| 2             | -               | Reserved<br>The value rea                                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |      |   |      |   |  |

| 1             | EADC            | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt. |                                                                                                     |      |   |      |   |  |

| 0             | -               | Reserved<br>The value rea                                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |      |   |      |   |  |

Reset Value = xxxx 0x0xb bit addressable

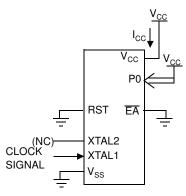

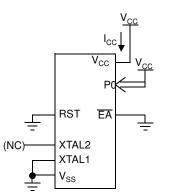

Figure 65. I<sub>CC</sub> Test Condition, Idle Mode

All other pins are disconnected.

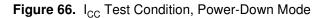

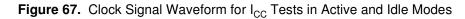

All other pins are disconnected.

# DC Parameters for A/D Converter

Table 72. DC Parameters for AD Converter in Precision Conversion

| Symbol | Parameter                       | Min      | Typ <sup>(1)</sup> | Мах        | Unit | Test Conditions |

|--------|---------------------------------|----------|--------------------|------------|------|-----------------|

| AVin   | Analog input voltage            | Vss- 0.2 |                    | Vref + 0.2 | V    |                 |

| Rref   | Resistance between Vref and Vss | 12       | 16                 | 24         | kΩ   |                 |

| Vref   | Reference voltage               | 2.40     |                    | 3.00       | V    |                 |

| Cai    | Analog input Capacitance        |          | 60                 |            | pF   | During sampling |

| Rai    | Analog input Resistor           |          |                    | 400        | Ω    | During sampling |

| INL    | Integral non linearity          |          | 1                  | 2          | lsb  |                 |

| DNL    | Differential non linearity      |          | 0.5                | 1          | lsb  |                 |

| OE     | Offset error                    | -2       |                    | 2          | lsb  |                 |

Note: 1. Typicals are based on a limited number of samples and are not guaranteed.

#### **AC Parameters**

Explanation of the AC Each timing symbol has 5 characters. The first character is always a "T" (stands for Symbols time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for. Example:  $T_{AVLL}$  = Time for Add<u>ress V</u>alid to ALE Low.  $T_{IIPI}$  = Time for ALE Low to PSEN Low. TA = -40°C to +85°C;  $V_{SS}$  = 0V;  $V_{CC}$  = 3V to 5.5V; F = 0 to 40 MHz. (Load Capacitance for port 0, ALE and PSEN = 60 pF; Load Capacitance for all other outputs = 60 pF.) Table 73, Table 76 and Table 79 give the description of each AC symbols. Table 74, Table 78 and Table 80 give for each range the AC parameter. Table 75, Table 78 and Table 81 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols: Take the x value and use this value in the formula. Example: T<sub>LLIV</sub> and 20 MHz, Standard clock. x = 30 nsT = 50 ns

$T_{CCIV} = 4T - x = 170 \text{ ns}$

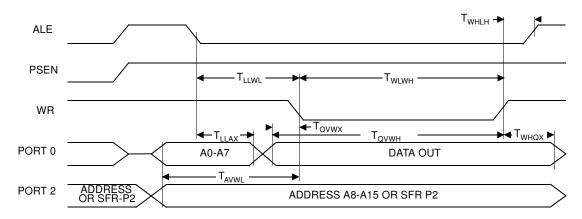

#### **External Data Memory Write Cycle**

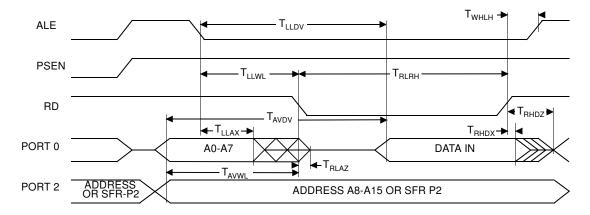

#### **External Data Memory Read Cycle**

#### Serial Port Timing – Shift Register Mode

Table 79. Symbol Description (F = 40 MHz)

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |