#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 52-LCC (J-Lead)                                                            |

| Supplier Device Package    | 52-PLCC (19.15x19.15)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ac3-s3sum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | <b>Port 3:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current ( $I_{IL}$ , see section "Electrical Characteristic") because of the internal pull-ups. The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows: |

|          |      | P3.0/RxD:<br>Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface<br>P3.1/TxD:<br>Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface<br>P3.2/INT0:                                                                                                                                                                                                                                                                                                                                                                              |

|          |      | External interrupt 0 input/timer 0 gate control input<br>P3.3/INT1:<br>External interrupt 1 input/timer 1 gate control input<br>P3.4/T0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |      | Timer 0 counter input<br>P3.5/T1/SS:<br>Timer 1 counter input<br>SPI Slave Select<br>P3.6/WR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |      | External Data Memory write strobe; latches the data byte from port 0 into the external data memory<br>P3.7/RD:<br>External Data Memory read strobe; Enables the external data memory.<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                       |

| P4.0:4   | I/O  | Port 4:<br>Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled high by the internal<br>pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being pulled low externally will be a source of<br>current (IIL, on the datasheet) because of the internal pull-up transistor.<br>The secondary functions are assigned to the 5 pins of port 4 as follows:<br>P4.0: Regular Port I/O                                                                                                                                         |

|          |      | P4.1: Regular Port I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |      | P4.2/MISO:<br>Master Input Slave Output of SPI controller<br>P4.3/SCK:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |      | Serial Clock of SPI controller<br>P4.4/MOSI:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | Master Ouput Slave Input of SPI controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |      | It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# AT89C51AC3

| Mnemonic | Add | Name                                 | 7  | 6    | 5    | 4   | 3    | 2    | 1     | 0    |

|----------|-----|--------------------------------------|----|------|------|-----|------|------|-------|------|

| IEN0     | A8h | Interrupt Enable<br>Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0   | EX0  |

| IEN1     | E8h | Interrupt Enable<br>Control 1        | _  | _    | _    | _   | ESPI | _    | EADC  | _    |

| IPL0     | B8h | Interrupt Priority<br>Control Low 0  | _  | PPC  | PT2  | PS  | PT1  | PX1  | PT0   | PX0  |

| IPH0     | B7h | Interrupt Priority<br>Control High 0 | _  | PPCH | PT2H | PSH | PT1H | PX1H | PT0H  | PX0H |

| IPL1     | F8h | Interrupt Priority<br>Control Low 1  | _  | _    | _    | _   | SPIL | _    | PADCL | _    |

| IPH1     | F7h | Interrupt Priority<br>Control High1  | _  | _    | _    | _   | SPIH | _    | PADCH | _    |

| Mnemonic | Add | Name               | 7     | 6      | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|--------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| ADCON    | F3h | ADC Control        | -     | PSIDLE | ADEN  | ADEOC | ADSST | SCH2  | SCH1  | SCH0  |

| ADCF     | F6h | ADC Configuration  | CH7   | CH6    | CH5   | CH4   | СНЗ   | CH2   | CH1   | CH0   |

| ADCLK    | F2h | ADC Clock          | -     | -      | _     | PRS4  | PRS3  | PRS2  | PRS1  | PRS0  |

| ADDH     | F5h | ADC Data High byte | ADAT9 | ADAT8  | ADAT7 | ADAT6 | ADAT5 | ADAT4 | ADAT3 | ADAT2 |

| ADDL     | F4h | ADC Data Low byte  | _     | _      | _     | _     | _     | _     | ADAT1 | ADAT0 |

| Mnemonic | Add | Name                      | 7     | 6     | 5      | 4     | 3    | 2     | 1      | 0      |

|----------|-----|---------------------------|-------|-------|--------|-------|------|-------|--------|--------|

| SPCON    | D4h | SPI Control               | SPR2  | SPEN  | SSDIS  | MSTR  | CPOL | СРНА  | SPR1   | SPR0   |

| SPSCR    | D5h | SPI Status and<br>Control | SPIF  | _     | OVR    | MODF  | SPTE | UARTM | SPTEIE | MOFIE  |

| SPDAT    | D6h | SPI Data                  | _     | _     | _      | _     | _    | -     | _      | _      |

| Mnemonic | Add | Name                      | 7     | 6     | 5      | 4     | 3    | 2     | 1      | 0      |

| PCON     | 87h | Power Control             | SMOD1 | SMOD0 | -      | POF   | GF1  | GF0   | PD     | IDL    |

| AUXR     | 8Eh | Auxiliary Register 0      | DPU   | VPFDP | M0     | XRS2  | XRS1 | XRS0  | EXTRAM | A0     |

| AUXR1    | A2h | Auxiliary Register 1      | -     | -     | ENBOOT | _     | GF3  | 0     | -      | DPS    |

| CKCON0   | 8Fh | Clock Control 0           | -     | WDX2  | PCAX2  | SIX2  | T2X2 | T1X2  | T0X2   | X2     |

| CKCON1   | 9Fh | Clock Control 1           | -     | -     | -      | _     | -    | -     | -      | SPIX2  |

| FCON     | D1h | Flash Control             | FPL3  | FPL2  | FPL1   | FPL0  | FPS  | FMOD1 | FMOD0  | FBUSY  |

| EECON    | D2h | EEPROM Contol             | EEPL3 | EEPL2 | EEPL1  | EEPL0 | -    | -     | EEE    | EEBUSY |

| FSTA     | D3  | Flash Status              | -     | -     | -      | -     | -    | -     | SEQERR | FLOAD  |

### Table 1. SFR Mapping

|        | 0/8 <sup>(2)</sup> | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 |     |

|--------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----|

| F8h    | IPL1<br>xxxx x0x0  | CH<br>0000 0000    | CCAP0H<br>0000 0000 | CCAP1H<br>0000 0000 | CCAP2H<br>0000 0000 | CCAP3H<br>0000 0000 | CCAP4H<br>0000 0000 |                     | FFh |

| F0h    | B<br>0000 0000     |                    | ADCLK<br>xxx0 0000  | ADCON<br>x000 0000  | ADDL<br>0000 0000   | ADDH<br>0000 0000   | ADCF<br>0000 0000   | IPH1<br>xxxx x0x0   | F7h |

| E8h    | IEN1<br>xxxx x0x0  | CL<br>0000 0000    | CCAP0L<br>0000 0000 | CCAP1L<br>0000 0000 | CCAP2L<br>0000 0000 | CCAP3L<br>0000 0000 | CCAP4L<br>0000 0000 |                     | EFh |

| E0h    | ACC<br>0000 0000   |                    |                     |                     |                     |                     |                     |                     | E7h |

| D8h    | CCON<br>0000 0000  | CMOD<br>00xx x000  | CCAPM0<br>×000 0000 | CCAPM1<br>x000 0000 | CCAPM2<br>x000 0000 | CCAPM3<br>×000 0000 | CCAPM4<br>x000 0000 |                     | DFh |

| D0h    | PSW<br>0000 0000   | FCON<br>0000 0000  | EECON<br>xxxx xx00  | FSTA<br>xxxx xx00   | SPCON<br>0001 0100  | SPSCR<br>0000 0000  | SPDAT<br>xxxx xxxx  |                     | D7h |

| C8h    | T2CON<br>0000 0000 | T2MOD<br>xxxx xx00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                     | CFh |

| C0h    | P4<br>xxx1 1111    |                    |                     |                     |                     |                     |                     |                     | C7h |

| B8h    | IPL0<br>x000 0000  | SADEN<br>0000 0000 |                     |                     |                     |                     |                     |                     | BFh |

| B0h    | P3<br>1111 1111    |                    |                     |                     |                     |                     |                     | IPH0<br>×000 0000   | B7h |

| A8h    | IEN0<br>0000 0000  | SADDR<br>0000 0000 |                     |                     |                     |                     |                     |                     | AFh |

| A0h    | P2<br>1111 1111    |                    | AUXR1<br>xxxx 00x0  |                     |                     |                     | WDTRST<br>1111 1111 | WDTPRG<br>xxxx x000 | A7h |

| 98h    | SCON<br>0000 0000  | SBUF<br>0000 0000  |                     |                     |                     |                     |                     | CKCON1<br>xxxx xxx0 | 9Fh |

| 90h    | P1<br>1111 1111    |                    |                     |                     |                     |                     |                     |                     | 97h |

| 88h    | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>x001 0100   | CKCON0<br>x00 0000  | 8Fh |

| 80h    | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                     |                     |                     | PCON<br>00x1 0000   | 87h |

| -<br>- | 0/8 <sup>(2)</sup> | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 | -   |

Reserved

Note: 1. Do not read or write Reserved Registers

These registers are bit-addressable. Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFR's are those whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

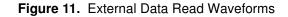

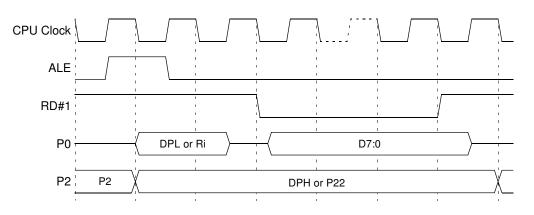

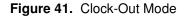

Notes: 1. RD# signal may be stretched using M0 bit in AUXR register.2. When executing MOVX @Ri instruction, P2 outputs SFR content.

# Registers

### Table 6. PSW Register

PSW (S:8Eh) Program Status Word Register

| 7             | 6               | 5                           | 4                                                                  | 3                             | 2  | 1  | 0 |  |  |  |  |

|---------------|-----------------|-----------------------------|--------------------------------------------------------------------|-------------------------------|----|----|---|--|--|--|--|

| СҮ            | AC              | F0                          | RS1                                                                | RS0                           | ov | F1 | Р |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                 | escription                                                         |                               |    |    |   |  |  |  |  |

| 7             | CY              | Carry Flag<br>Carry out fro | arry Flag<br>arry out from bit 1 of ALU operands.                  |                               |    |    |   |  |  |  |  |

| 6             | AC              | -                           | Auxiliary Carry Flag<br>Carry out from bit 1 of addition operands. |                               |    |    |   |  |  |  |  |

| 5             | F0              | User Defina                 | ble Flag 0.                                                        |                               |    |    |   |  |  |  |  |

| 4-3           | RS1:0           |                             | nk Select Bit<br>e 4 for bits de                                   |                               |    |    |   |  |  |  |  |

| 2             | OV              | Overflow Fla                | <b>ag</b><br>by arithmetic                                         | operations.                   |    |    |   |  |  |  |  |

| 1             | F1              | User Defina                 | User Definable Flag 1                                              |                               |    |    |   |  |  |  |  |

| 0             | Р               |                             |                                                                    | n odd number<br>ns an even nu |    |    |   |  |  |  |  |

Reset Value = 0000 0000b

# Table 7. AUXR Register

AUXR (S:8Eh) Auxiliary Register

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                  | 3    | 2    | 1      | 0  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|--------|----|--|--|--|

| -             | -               | MO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XRS2                                                                               | XRS1 | XRS0 | EXTRAM | A0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |      |      |        |    |  |  |  |

| 7-6           | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reserved<br>The value read from these bits are indeterminate. Do not set this bit. |      |      |        |    |  |  |  |

| 5             | MO              | the RD/ and the RD |                                                                                    |      |      |        |    |  |  |  |

# Registers

Table 10.PCON RegisterPCON (S87:h)Power configuration Register

| 7             | 6               | 5                                             | 4                                                                                                                                                                                | 3                                         | 2             | 1              | 0            |  |  |  |  |  |

|---------------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|----------------|--------------|--|--|--|--|--|

| -             | -               | -                                             | -                                                                                                                                                                                | GF1                                       | GF0           | PD             | IDL          |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   | Description                                                                                                                                                                      |                                           |               |                |              |  |  |  |  |  |

| 7-4           | -               | <b>Reserved</b><br>The value re               | Reserved<br>The value read from these bits is indeterminate. Do not set these bits.                                                                                              |                                           |               |                |              |  |  |  |  |  |

| 3             | GF1             | One use is to                                 | General Purpose flag 1<br>One use is to indicate whether an interrupt occurred during normal operation or<br>during Idle mode.                                                   |                                           |               |                |              |  |  |  |  |  |

| 2             | GF0             | General Pur<br>One use is to<br>during Idle m | indicate whe                                                                                                                                                                     | ther an interru                           | pt occurred d | uring normal o | operation or |  |  |  |  |  |

| 1             | PD              | Cleared by h<br>Set to activa                 | <b>Power-Down Mode bit</b><br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Power-Down mode.<br>If IDL and PD are both set, PD takes precedence. |                                           |               |                |              |  |  |  |  |  |

| 0             | IDL             | Set to activat                                | ardware when<br>the Idle mo                                                                                                                                                      | n an interrupt (<br>de.<br>, PD takes pre |               | 3.             |              |  |  |  |  |  |

Reset Value= XXXX 0000b

# Registers

# Table 11. EECON Register

EECON (S:0D2h) EEPROM Control Register

| 7          | 6               | 5                         | 4                                                                                                                                                           | 3                                                           | 2                          | 1          | 0      |  |  |

|------------|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|------------|--------|--|--|

| EEPL3      | EEPL2           | EEPL1                     | EEPL0                                                                                                                                                       | -                                                           | -                          | EEE        | EEBUSY |  |  |

| Bit Number | Bit<br>Mnemonic | Descriptio                | n                                                                                                                                                           |                                                             |                            |            |        |  |  |

| 7-4        | EEPL3-0         | •                         | •                                                                                                                                                           | <b>command bit</b><br>Kh to EEPL to                         | <b>s</b><br>launch the pre | ogramming. |        |  |  |

| 3          | -               | Reserved<br>The value r   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                             |                                                             |                            |            |        |  |  |

| 2          | -               | Reserved<br>The value r   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                             |                                                             |                            |            |        |  |  |

| 1          | EEE             | Set to map<br>latches)    | Enable EEPROM Space bit<br>Set to map the EEPROM space during MOVX instructions (Write in the column<br>atches)<br>Clear to map the XRAM space during MOVX. |                                                             |                            |            |        |  |  |

| 0          | EEBUSY          | Set by hard<br>Cleared by | hardware wh                                                                                                                                                 | <b>g</b><br>rogramming is<br>en programmi<br>d by software. | ng is done.                |            |        |  |  |

Reset Value = XXXX XX00b Not bit addressable

# **Operation Cross Memory Access**

Space addressable in read and write are:

- RAM

- ERAM (Expanded RAM access by movx)

- XRAM (eXternal RAM)

- EEPROM DATA

- FM0 (user flash)

- Hardware byte

- XROW

- Boot Flash

- Flash Column latch

The table below provide the different kind of memory which can be accessed from different code location.

| Table 18. | Cross | Memory | Access |

|-----------|-------|--------|--------|

|-----------|-------|--------|--------|

|                                          | Action | RAM | XRAM<br>ERAM | Boot FLASH | FM0               | E <sup>2</sup> Data | Hardware<br>Byte  | XROW              |

|------------------------------------------|--------|-----|--------------|------------|-------------------|---------------------|-------------------|-------------------|

|                                          | Read   |     |              | ОК         | OK                | ОК                  | OK                | -                 |

| boot FLASH                               | Write  |     |              | -          | OK <sup>(1)</sup> | OK <sup>(1)</sup>   | OK <sup>(1)</sup> | OK <sup>(1)</sup> |

| FM0                                      | Read   |     |              | ОК         | OK                | ОК                  | OK                | -                 |

| FIVIU                                    | Write  |     |              | -          | OK (idle)         | OK <sup>(1)</sup>   | -                 | ОК                |

| External                                 | Read   |     |              | -          | -                 | ОК                  | -                 | -                 |

| memory<br>EA = 0<br>or Code Roll<br>Over | Write  |     |              | -          | -                 | OK <sup>(1)</sup>   | -                 | -                 |

Note: 1. RWW: Read While Write

# Table 22. Read MOVC A, @DPTR

|                                              | FC    | ON Regis | ter |        |                                     |               |                               |                 | Hardware | Externa |  |

|----------------------------------------------|-------|----------|-----|--------|-------------------------------------|---------------|-------------------------------|-----------------|----------|---------|--|

| Code Execution                               | FMOD1 | FMOD0    | FPS | ENBOOT | DPTR                                | FM1           | FM0                           | XROW            | Byte     | Code    |  |

|                                              |       |          |     | 0      | 0000h to FFFFh                      |               | ОК                            |                 |          |         |  |

|                                              | 0     | 0        | Х   |        | 0000h to F7FF                       |               | ОК                            |                 |          |         |  |

|                                              |       |          |     | 1      | F800h to FFFFh                      |               | Do not u                      | se this configu | uration  | 1       |  |

| From FM0                                     | 0     | 1        | х   | х      | 0000 to 007Fh<br>See <sup>(1)</sup> |               |                               | ОК              |          |         |  |

|                                              | 1     | 0        | Х   | х      | х                                   |               |                               |                 | ОК       |         |  |

|                                              |       |          |     | 0      | 000h to FFFFh                       |               | OK                            |                 |          |         |  |

| 1                                            | 1     | 1        | 1   | х      |                                     | 0000h to F7FF |                               | ОК              |          |         |  |

|                                              |       |          |     | 1      | F800h to FFFFh                      |               | Do not use this configuration |                 |          |         |  |

|                                              |       |          |     | 4      | 0000h to F7FF                       |               | ОК                            |                 |          |         |  |

|                                              | 0     |          | 0   | 1      | F800h to FFFFh                      | OK            |                               |                 |          |         |  |

|                                              | 0     | 0        |     | 0      | х                                   |               |                               | NA              |          |         |  |

|                                              |       |          | 1   | 1      | х                                   |               | ОК                            |                 |          |         |  |

|                                              |       |          | -   | 0      | х                                   |               |                               | NA              |          |         |  |

| From FM1<br>(ENBOOT =1                       | 0     | 1        | х   | 1      | 0000h to 007h                       |               |                               | OK              |          |         |  |

|                                              | 0     | I        | ~   | 0      | See (2)                             |               |                               | NA              |          | -       |  |

|                                              | 1     | 0        | х   | 1      | x                                   |               |                               |                 | ОК       |         |  |

|                                              |       | Ű        | ~   | 0      | ~                                   |               |                               | NA              |          |         |  |

|                                              | 1     | 1        | х   | 1      | 000h to FFFFh                       |               | OK                            |                 |          |         |  |

|                                              |       |          |     | 0      |                                     |               |                               | NA              |          | i       |  |

| External code :<br>EA=0 or Code<br>Roll Over | х     | 0        | х   | x      | Х                                   |               |                               |                 |          | ОК      |  |

1. For DPTR higher than 007Fh only lowest 7 bits are decoded, thus the behavior is the same as for addresses from 0000h to 007Fh

For DPTR higher than 007Fh only lowest 7 bits are decoded, thus the behavior is the same as for addresses from 0000h to 007Fh

# Hardware Security Byte

Table 24.

Hardware Security Byte

| 7             | 6               | 5                                                             | 4                                                                                                                                                           | 3 | 2   | 1   | 0   |  |  |

|---------------|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|--|--|

| X2B           | BLJB            | -                                                             | -                                                                                                                                                           | - | LB2 | LB1 | LB0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                   | Description                                                                                                                                                 |   |     |     |     |  |  |

| 7             | X2B             |                                                               | <b>X2 Bit</b><br>Set this bit to start in standard mode<br>Clear this bit to start in X2 mode.                                                              |   |     |     |     |  |  |

| 6             | BLJB            | - 1: To start th                                              | Boot Loader JumpBit<br>- 1: To start the user's application on next RESET (@0000h) located in FM0,<br>- 0: To start the boot loader(@F800h) located in FM1. |   |     |     |     |  |  |

| 5-3           | -               | Reserved<br>The value read from these bits are indeterminate. |                                                                                                                                                             |   |     |     |     |  |  |

| 2-0           | LB2:0           | Lock Bits                                                     |                                                                                                                                                             |   |     |     |     |  |  |

Default value after erasing chip: FFh

Notes: 1. Only the 4 MSB bits can be accessed by software.

2. The 4 LSB bits can only be accessed by parallel mode.

#### Table 26. SADEN Register

SADEN (S:B9h) Slave Address Mask Register

| 7             | 6               | 5                                      | 4           | 3 | 2 | 1 | 0 |  |

|---------------|-----------------|----------------------------------------|-------------|---|---|---|---|--|

| -             | -               | -                                      | -           | - | - | - | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                            | Description |   |   |   |   |  |

| 7-0           |                 | Mask Data for Slave Individual Address |             |   |   |   |   |  |

Reset Value = 0000 0000b Not bit addressable

Table 27. SADDR Register

SADDR (S:A9h) Slave Address Register

| 7             | 6               | 5                        | 4           | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|--------------------------|-------------|---|---|---|---|--|--|

| -             | -               | -                        | -           | - | - | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              | Description |   |   |   |   |  |  |

| 7-0           |                 | Slave Individual Address |             |   |   |   |   |  |  |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. SBUF Register

SBUF (S:99h) Serial Data Buffer

| 7             | 6               | 5            | 4                                     | 3 | 2 | 1 | 0 |  |

|---------------|-----------------|--------------|---------------------------------------|---|---|---|---|--|

| -             | -               | -            | -                                     | - | - | - | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description  |                                       |   |   |   |   |  |

| 7-0           |                 | Data sent/re | Data sent/received by Serial I/O Port |   |   |   |   |  |

Reset Value = 0000 0000b Not bit addressable

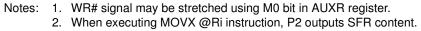

# Programmable Clock-Output

In clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 41). The input clock increments TL2 at frequency  $F_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency depending on the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock - OutFrequency = \frac{FT2clock}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock in x1 mode, timer 2 has a programmable frequency range of 61 Hz ( $F_{OSC}/2^{16}$ ) to 4 MHz ( $F_{OSC}/4$ ). The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or different depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

# AT89C51AC3

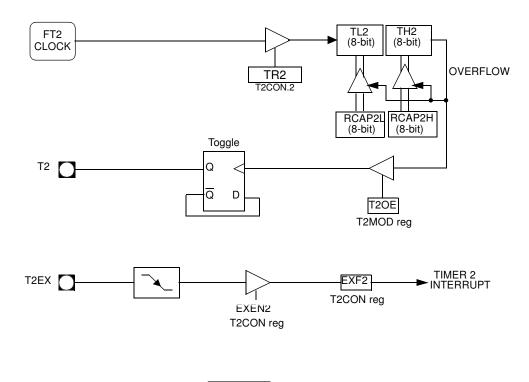

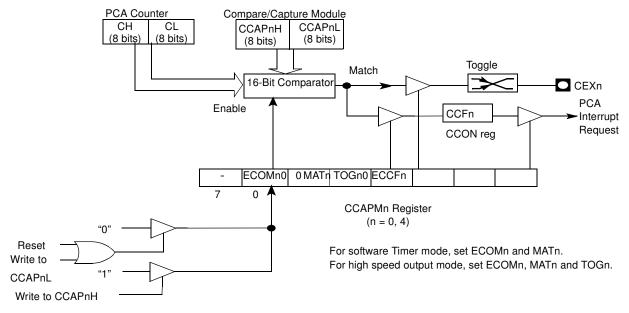

Figure 55. PCA Capture Mode

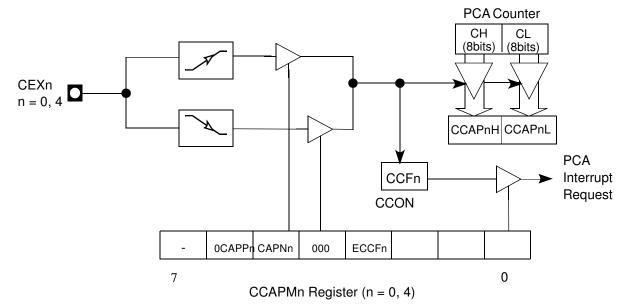

# 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

Figure 56. PCA 16-bit Software Timer and High Speed Output Mode

# **PCA Registers**

# Table 50. CMOD Register

CMOD (S:D9h) PCA Counter Mode Register

| 7             | 6               | 5                                                                                                                                                                                                                                                                                  | 4                                                                                                       | 3               | 2              | 1            | 0   |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|-----|--|--|--|

| CIDL          | WDTE            | -                                                                                                                                                                                                                                                                                  | -                                                                                                       | -               | CPS1           | CPS0         | ECF |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                        | Description                                                                                             |                 |                |              |     |  |  |  |

| 7             | CIDL            | PCA Counter Idle Control bit<br>Clear to let the PCA run during Idle mode.<br>Set to stop the PCA when Idle mode is invoked.                                                                                                                                                       |                                                                                                         |                 |                |              |     |  |  |  |

| 6             | WDTE            | Clear to disa                                                                                                                                                                                                                                                                      | WatchDog Timer Enable<br>Clear to disable WatchDog Timer function on PCA Module 4,<br>Set to enable it. |                 |                |              |     |  |  |  |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                    |                                                                                                         |                 |                |              |     |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                                                                                   | ad from this b                                                                                          | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                                                                                   | ad from this b                                                                                          | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |

| 2-1           | CPS1:0          | EWC Count Pulse Select bits <u>CPS1</u> <u>CPS0</u> <u>Clock source</u> 0       0       Internal Clock, FPca/6         0       1       Internal Clock, FPca/2         1       0       Timer 0 overflow         1       1       External clock at ECI/P1.2 pin (Max. Rate = FPca/4) |                                                                                                         |                 |                |              |     |  |  |  |

| 0             | ECF             | Enable PCA Counter Overflow Interrupt bit<br>Clear to disable CF bit in CCON register to generate an interrupt.<br>Set to enable CF bit in CCON register to generate an interrupt.                                                                                                 |                                                                                                         |                 |                |              |     |  |  |  |

Reset Value = 00XX X000b

# Table 51. CCON Register

CCON (S:D8h) PCA Counter Control Register

| 7             | 6               | 5                               | 4                                                                                                                                                                                                            | 3                                                               | 2    | 1    | 0    |  |  |

|---------------|-----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|------|------|--|--|

| CF            | CR              | -                               | CCF4                                                                                                                                                                                                         | CCF3                                                            | CCF2 | CCF1 | CCF0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     | Description                                                                                                                                                                                                  |                                                                 |      |      |      |  |  |

| 7             | CF              | Set by hardw<br>interrupt requ  | PCA Timer/Counter Overflow flag<br>Set by hardware when the PCA Timer/Counter rolls over. This generates a PCA<br>nterrupt request if the ECF bit in CMOD register is set.<br>Must be cleared by software.   |                                                                 |      |      |      |  |  |

| 6             | CR              | Clear to turn                   | PCA Timer/Counter Run Control bit<br>Clear to turn the PCA Timer/Counter off.<br>Set to turn the PCA Timer/Counter on.                                                                                       |                                                                 |      |      |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                              |                                                                 |      |      |      |  |  |

| 4             | CCF4            | Set by hardw<br>interrupt requ  | PCA Module 4 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 4 bit in CCAPM 4 register is set.<br>Must be cleared by software. |                                                                 |      |      |      |  |  |

| 3             | CCF3            | Set by hardw<br>interrupt requ  | are when a n                                                                                                                                                                                                 | <b>Capture flag</b><br>natch or captu<br>CF 3 bit in CC<br>rre. |      | •    | PCA  |  |  |

| 2             | CCF2            | Set by hardw<br>interrupt requ  | PCA Module 2 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 2 bit in CCAPM 2 register is set.<br>Must be cleared by software. |                                                                 |      |      |      |  |  |

| 1             | CCF1            | Set by hardw<br>interrupt requ  | PCA Module 1 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 1 bit in CCAPM 1 register is set.<br>Must be cleared by software. |                                                                 |      |      |      |  |  |

| 0             | CCF0            | Set by hardw<br>interrupt requ  | vare when a n                                                                                                                                                                                                | <b>Capture flag</b><br>natch or captu<br>CF 0 bit in CC<br>re.  |      |      | PCA  |  |  |

Reset Value = 00X0 0000b

EADC = 1 // clear the field SCH[2:0] ADCON and = F8h // Select the channel ADCON | = channel // Start conversion in precision mode ADCON | = 48h

Note: to enable the ADC interrupt: EA = 1

Table 60. ADCLK Register

ADCLK (S:F2h) ADC Clock Prescaler

| 7             | 6               | 5                                      | 4                                                                                    | 3     | 2     | 1     | 0     |  |  |

|---------------|-----------------|----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| -             | -               | -                                      | PRS 4                                                                                | PRS 3 | PRS 2 | PRS 1 | PRS 0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                            |                                                                                      |       |       |       |       |  |  |

| 7-5           | -               | <b>Reserved</b><br>The value re        | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |       |       |       |       |  |  |

| 4-0           | PRS4:0          | Clock Presc<br>See Note <sup>(1)</sup> | aler                                                                                 |       |       |       |       |  |  |

Reset Value = XXX0 0000b

Note:

1. In X1 mode: For PRS > 0  $F_{ADC} = \frac{EXTAL}{4xPRS}$ For PRS = 0  $F_{ADC} = \frac{FXTAL}{128}$ In X2 mode: For PRS > 0  $F_{ADC} = \frac{FXTAL}{2xPRS}$ For PRS = 0  $F_{ADC} = \frac{FXTAL}{64}$

Table 61. ADDH Register

ADDH (S:F5h Read Only) ADC Data High Byte Register

| 7             | 6               | 5                      | 4      | 3      | 2      | 1      | 0      |

|---------------|-----------------|------------------------|--------|--------|--------|--------|--------|

| ADAT 9        | ADAT 8          | ADAT 7                 | ADAT 6 | ADAT 5 | ADAT 4 | ADAT 3 | ADAT 2 |

| Bit<br>Number | Bit<br>Mnemonic | Description            |        |        |        |        |        |

| 7-0           | ADAT9:2         | ADC result<br>bits 9-2 |        |        |        |        |        |

Reset Value = 00h

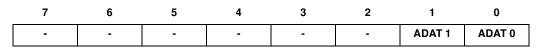

Table 62. ADDL Register

ADDL (S:F4h Read Only) ADC Data Low Byte Register

# Table 70. IPH1 Register

IPH1 (S:F7h) Interrupt High Priority Register 1

| 7             | 6               | 5                                                                                                                                                                                                                           | 4                                                                               | 3               | 2              | 1            | 0 |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|----------------|--------------|---|--|

| -             | -               | -                                                                                                                                                                                                                           | -                                                                               | SPIH            | -              | PADCH        | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                 |                                                                                 |                 |                |              |   |  |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                            | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |  |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                            | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |  |

| 5             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                            | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |   |  |

| 4             | -               | Reserved<br>The value rea                                                                                                                                                                                                   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |   |  |

| 3             | SPIH            |                                                                                                                                                                                                                             | 0 1<br>1 0                                                                      |                 |                |              |   |  |

| 2             | -               | Reserved<br>The value rea                                                                                                                                                                                                   | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |  |

| 1             | PADCH           | ADC Interrupt Priority Level Most Significant bit         PADCH       PADCL       Priority level         0       0       Lowest         0       1       1         1       0       Interrupt         1       1       Highest |                                                                                 |                 |                |              |   |  |

| 0             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                            | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |   |  |

Reset Value = XXXX 0X0Xb

# **AC Parameters**

Explanation of the AC Each timing symbol has 5 characters. The first character is always a "T" (stands for Symbols time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for. Example:  $T_{AVLL}$  = Time for Add<u>ress V</u>alid to ALE Low.  $T_{IIPI}$  = Time for ALE Low to PSEN Low. TA = -40°C to +85°C;  $V_{SS}$  = 0V;  $V_{CC}$  = 3V to 5.5V; F = 0 to 40 MHz. (Load Capacitance for port 0, ALE and PSEN = 60 pF; Load Capacitance for all other outputs = 60 pF.) Table 73, Table 76 and Table 79 give the description of each AC symbols. Table 74, Table 78 and Table 80 give for each range the AC parameter. Table 75, Table 78 and Table 81 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols: Take the x value and use this value in the formula. Example: T<sub>LLIV</sub> and 20 MHz, Standard clock. x = 30 nsT = 50 ns

$T_{CCIV} = 4T - x = 170 \text{ ns}$

# External Program Memory Characteristics

# Table 73. Symbol Description

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

# Table 74. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Max | Units |

|-------------------|-----|-----|-------|

| Т                 | 25  |     | ns    |

| T <sub>LHLL</sub> | 40  |     | ns    |

| T <sub>AVLL</sub> | 10  |     | ns    |

| T <sub>LLAX</sub> | 10  |     | ns    |

| T <sub>LLIV</sub> |     | 70  | ns    |

| T <sub>LLPL</sub> | 15  |     | ns    |

| T <sub>PLPH</sub> | 55  |     | ns    |

| T <sub>PLIV</sub> |     | 35  | ns    |

| T <sub>PXIX</sub> | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 18  | ns    |

| T <sub>AVIV</sub> |     | 85  | ns    |

| T <sub>PLAZ</sub> |     | 10  | ns    |