Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | UART/USART                                             |

| Peripherals                | -                                                      |

| Number of I/O              | 24                                                     |

| Program Memory Size        | -                                                      |

| Program Memory Type        | ROMIess                                                |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                     |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 40-DIP (0.620", 15.75mm)                               |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c9116peg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Architectural Overview**

ZiLOG's large Z8<sup>®</sup> family of 8-bit ROMless microcontrollers includes the Z86C91 product with 236 bytes of RAM. Each of these devices offer fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion along with low cost and low power consumption.

For applications demanding powerful I/O capabilities, the Z86C91 offers 24 pins dedicated to input and output. These lines are grouped into four ports. Each port consists of eight lines and is configurable under software control to proviide timing, status signals, serial or parallel I/O with or without handshake and an address/data bus for interfacing external memory. The Z86C91 MCU features three basic address spaces to support this wide range of configurations: Program Memory, Data Memory, and 236 General Purposes Registers.

The Z86C91 operates at 16 MHz with a voltage range of 4.5 to 5.5 VDC.

To unburden the system from coping with real-time tasks such as counting/timing and data communication, the Z86C91 offers two on-chip counter/timers with a large number of user-selectable modes and a full-duplex hardware UART.

The Z86C91 is a ROMless part and offers the use of external memory, which enables this  $Z8^{\text{\ensuremath{\mathbb{R}}}}$  MCU to be used in high-volume applications, or where code flexibility is required.

**Note:** All signals with an overline are active Low. For example,  $B/\overline{W}$ , for which WORD is active Low, and  $\overline{B}/W$ , for which BYTE is active Low.

Power connections follow these conventional descriptions:

| Connection | Circuit  | Device   |  |

|------------|----------|----------|--|

| Power      | $V_{CC}$ | $V_{DD}$ |  |

| Ground     | GND      | $V_{SS}$ |  |

#### **Z86C91 Features**

- Asynchronous receiver/transmitter UART

- 40-Pin DIP and 44-Pin PLCC and QFP Packages

- 4.5- to 5.5-Volt Operating Range

- Operating Temperature Ranges:

Standard: 0°C to 70°C

Extended: -40°C to 105°C

• 24 Input/Output Lines

- Six Vectored, Prioritized Interrupts from Eight Different Sources

- Two Programmable 8-Bit Counter/Timers, each with two 6-Bit Programmable Prescalers

- On-Chip Oscillator that accepts a Crystal, Ceramic Resonator, LC, or External Clock

- Two Standby Modes: STOP and HALT

- Auto Latches

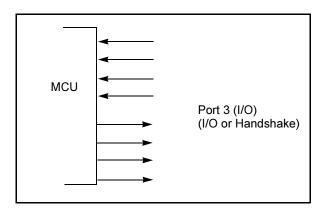

Port 3 (P37–P30). Port 3 is an 8-bit, TTL-compatible port, with four fixed inputs (P33–P30) and four fixed outputs (P34–P37). Port 3 is configured under software control for Input/Output, Counter/Timers, interrupt, UART, port handshake, and data Memory functions. Port 3, when used as serial I/O are programmed as serial in and serial out respectively (Figure 8).

Figure 8. Port 3 Configuration

For interrupt functions, Port 3 inputs are falling-edge interrupt inputs. Access to Counter/Timer 1 is made through P31 ( $T_{\rm IN}$ ) and P36 ( $T_{\rm OUT}$ ). Handshake lines for Ports 0, 1, and 2 are available on P31 through P36.

Port 3 also provides the following control functions: handshake for Ports 0, 1, and 2 ( $\overline{DAV}$  and RDY); four external interrupt request signals (IRQ3–IRQ0); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ); Data Memory Select.

P34 output is software-programmed to function as a Data Memory Select ( $\overline{DM}$ ). The Port 3 Mode Register (P3M) bit D3,D4 selects this function. When accessing external data memory, P34 goes active Low; when accessing external program memory, P34 goes High.

An onboard UART is enabled by software setting bit D5 of the Port 3 Mode Register P3M. When enabled, P30 is the receive input and P37 is the transmit output.

Port 3, lines P30 and P37 are programmed as serial I/O for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by Counter/Timer0.

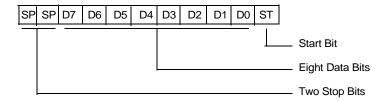

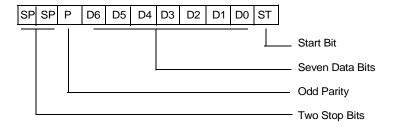

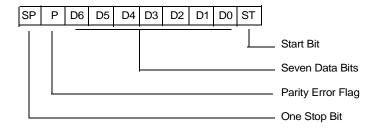

The Z8 automatically adds a start bit and two stop bits to transmitted data. Serial Data formats are shown in Figure 9 and Figure 10. Odd parity is also available by setting bit D7 in the P3M register. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

PS018501-1002 Pin Functions

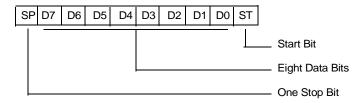

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

Figure 9. Transmitted Data (No Parity)

Figure 10. Transmitted Data (With Parity)

Figure 11. Received Data (No Parity)

Figure 12. Received Data (With Parity)

PS018501-1002 Pin Functions

# **Functional Description**

The Z8 MCU incorporates the following functions that enhance the standard Z8<sup>®</sup> architecture and provide the user with increased design flexibility:

- Reset

- Program Memory

- Data Memory

- Working Register

- General-Purpose Registers

- Stack Pointer

- Counter/Timers

- Interrupts

- Clock

- HALT and STOP Modes

- Port Configuration Register

**RESET.** The device is reset in the following condition:

External Reset

Automatic Power-On Reset circuitry is not built into this Z8. This Z8 requires an external reset circuit to reset upon power-up. The internal pull-up resistor is on the  $\overline{\text{RESET}}$  pin, so a pull-up resistor is not required; however, in a high-EMI (noisy) environment, it is recommended that a low-value pull-up resistor be used.

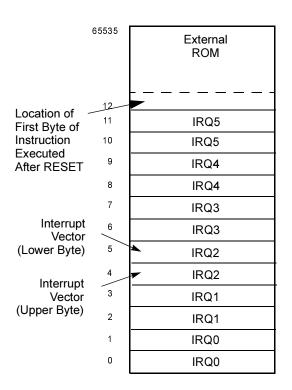

**Program Memory.** The Z86C91 can address up to 64 KB of external program memory. The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Program execution begins at external location 000Ch after reset. See Figure 13.

Figure 13. Program Memory Map

**Data Memory** ( $\overline{DM}$ ). The Z86C91addresses up to 64 KB of external data memory. External data memory may be included with, or separated from, the external program memory space.  $\overline{DM}$ , an optional I/O function that is programmed to appear on pin P34, is used to distinguish between data and program memory space (Figure 14). The state of the  $\overline{DM}$  signal is controlled by the type of instruction being executed. An LDC Op Code references PROGRAM ( $\overline{DM}$  inactive) memory, and an LDE instruction references data ( $\overline{DM}$  active Low) memory. The user must configure Port 3 Mode Register (P3M) bits D3 and D4 for this mode.

General-Purpose Registers (GPR). General-purpose registers are undefined after the device is powered up. These registers keep the most recent value after any RESET, as long as the RESET occurs in the  $V_{CC}$  voltage-specified operating range. General-purpose registers are not guaranteed to keep their most recent state from if  $V_{CC}$  drops below the minimum  $V_{CC}$  operating range.

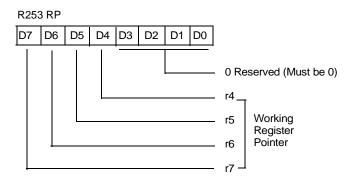

**Stack Pointer.** The Z86C91 has a 16-bit Stack Pointer (SPH and SPL) used for the external stack, that resides anywhere in the data memory. An 8-bit Stack Pointer (SPL) is used for the internal stack that resides within the 236 general-purpose registers. Stack Pointer High (SPH) is used as a general-purpose register only when using an internal stack.

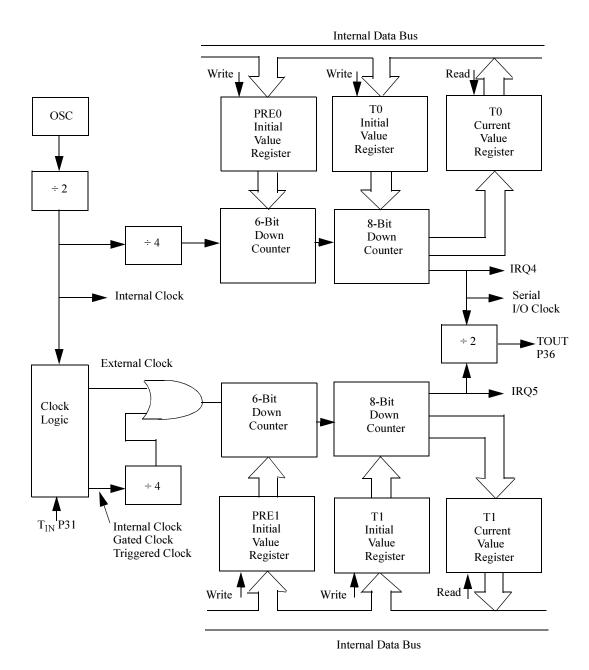

**Counter/Timers.** There are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only (Figure 17).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that is loaded into the counter. When both the counter and prescaler reach the end of the count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters are programmed to START, STOP, restart to CONTINUE, or restart from the initial value. The counters can also be programmed to STOP upon reaching 1 (SIN-GLE-PASS mode) or to automatically reload the initial value and continue counting (MODULO–N CONTINUOUS mode).

The counters, but not the prescalers, are read at any time without disturbing their value or count mode. Reading the prescalers returns the value FFh. The clock source for T1 is user-definable and is either the internal micro controller clock divide-by-four, or an external signal input through Port 3. The maximum frequency of the external timer signal is the XTAL clock signal divided by 8. The Timer Mode Register configures the external timer input (P31) as an external clock, a trigger input that is retriggerable or nonretriggerable, or as a gate input for the internal clock. Port 3 line P36 also serves as an output ( $T_{\rm OUT}$ ) through which T0, T1, or the internal clock is output. The counter/timers are cascaded by connecting the T0 output to the input of T1.

Figure 18. Counter/Timer Block Diagram

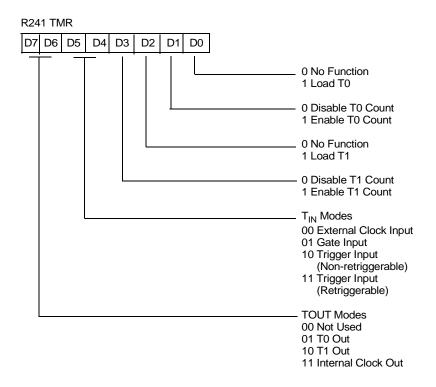

#### **Timer Mode Register**

The Timer Mode Register, TMR, controls timing and counter functions and shown.in Figure 22.

Figure 22. Timer Mode Register (F1h: Read/Write)

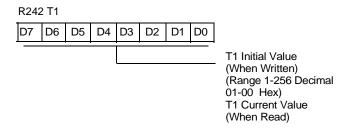

#### Counter/Timer 1 Register

The Counter/Timer 1 Register, T1 is shown in Figure 23.

Figure 23. Counter Timer 1 Register (F2h: Read/Write)

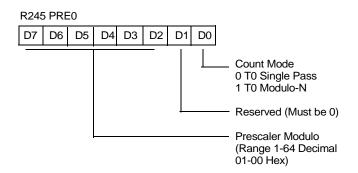

Figure 26. Prescaler 0 Register (F5h: Write Only)

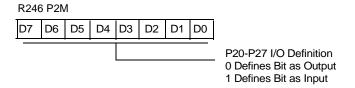

#### Port 2 Mode Register

The Port 2 Mode Register, P2M, controls Port 2 I/O functions and is shown in Figure 27.

Figure 27. Port 2 Mode Register (F6h: Write Only)

#### Port 3 Mode Register

The Port 3 Mode Register P3M controls Port 3 I/O functions and is shown in Figure 28.

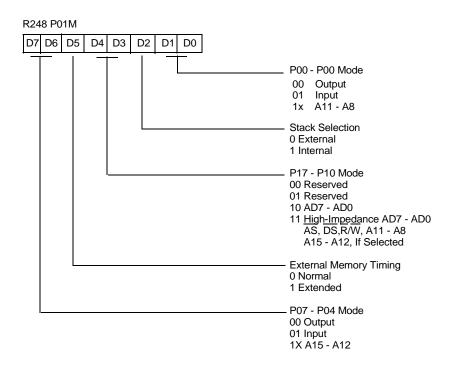

Figure 29. Port 0 and 1 Mode Register (F8h: Write Only)

**Interrupt Priority Register.** The Interrupt Priority Register, IPR, prioritizes interrupt functions and is shown in Figure 30.

ZiLOG

Figure 34. Register Pointer Register (FDh: Read/Write)

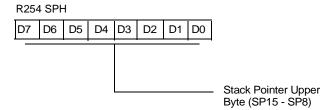

#### **Stack Pointer High Register**

The Stack Pointer High Register, SPH, controls pointer functions in the upper byte when the external stack is used and is shown in Figure 35.

Figure 35. Stack Pointer Register (FEh: Read/Write)

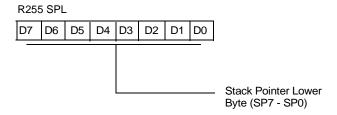

#### **Stack Pointer Low Register**

The Stack Pointer Low Register, SPL, controls pointer functions in the lower byte and is shown in Figure 36.

Figure 36. Stack Pointer Register (FFh: Read/Write)

#### **Electrical Characteristics**

#### **Absolute Maximum Ratings**

Stresses greater than the Absolute Maximum Ratings listed in Table 16 may cause permanent damage to the device. This rating is a stress rating only. Functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

**Table 16. Absolute Maximum Ratings**

| Symbol           | Parameter                     | Min  | Max  | Units |

|------------------|-------------------------------|------|------|-------|

| $V_{\rm CC}$     | Supply Voltage <sup>1</sup>   | -0.3 | +7.0 | V     |

| T <sub>STO</sub> | Storage Temperature           | -65  | +150 | С     |

| T <sub>A</sub>   | Operating Ambient Temperature |      | 2    | С     |

#### Notes:

- 1. Voltages on all pins with respect to GND.

- 2. See Ordering Information.

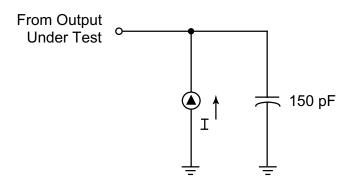

#### **Standard Test Conditions**

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 37).

Figure 37. Test Load Diagram

# Capacitance

$T_A$  = 25°C,  $V_{CC}$  = GND = 0V, f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

#### **DC Electrical Characteristics**

Table 17. DC Electrical Characteristics at Standard and External Temperatures

|                 |                             | $T_A = 0$ °C to +70°C |                 | $T_A = -40$ °C to $+105$ °C |          | Typical <sup>2</sup> |       |                                          |

|-----------------|-----------------------------|-----------------------|-----------------|-----------------------------|----------|----------------------|-------|------------------------------------------|

| Sym             | Parameter                   | Min                   | Max             | Min                         | Max      | @25°C                | Units | Conditions                               |

|                 | Max Input<br>Voltage        |                       | 7               |                             | 7        |                      | V     | I <sub>IH</sub> <200μA                   |

| V <sub>CH</sub> | Clock Input<br>High Voltage | 3.8                   | V <sub>CC</sub> | 3.8                         | $V_{CC}$ |                      | V     | Driven by<br>External Clock<br>Generator |

#### Note:

- 1. All inputs driven to 0V,  $V_{\mbox{\footnotesize{CC}}}$  and outputs floating.

- 2.  $V_{CC} = 5.0V$

Table 17. DC Electrical Characteristics at Standard and External Temperatures (Continued)

|                              |                             | $T_A = 0$ °C          | to +70°C | $T_{A} = -40^{\circ}$ | C to +105°C     | Typical <sup>2</sup> |       |                                                                 |

|------------------------------|-----------------------------|-----------------------|----------|-----------------------|-----------------|----------------------|-------|-----------------------------------------------------------------|

| Sym                          | Parameter                   | Min                   | Max      | Min                   | Max             | @25°C                | Units | Conditions                                                      |

| $\overline{v_{\mathrm{CL}}}$ | Clock Input<br>Low Voltage  | -0.3                  | 0.8      | -0.3                  | 0.8             |                      | V     | Driven by<br>External Clock<br>Generator                        |

| $V_{IH}$                     | Input High<br>Voltage       | 2.0                   | $V_{CC}$ | 2.0                   | V <sub>CC</sub> |                      | V     |                                                                 |

| $\overline{v_{IL}}$          | Input Low<br>Voltage        | -0.3                  | 0.8      | -0.3                  | 0.8             |                      | V     |                                                                 |

| V <sub>OH</sub>              | Output High<br>Voltage      | 2.4                   |          | 2.4                   |                 |                      | V     | $I_{OH} = -2.0 \text{ mA}$                                      |

| V <sub>OH</sub>              | Output High<br>Voltage      | V <sub>CC</sub> -100r | nV       | V <sub>CC</sub> -100  | mV              |                      | V     | $I_{OH} = -100 \ \mu A$                                         |

| V <sub>OL</sub>              | Output Low<br>Voltage       |                       | 0.4      |                       | 0.4             |                      | V     | $I_{OH} = +2 \text{ mA}$                                        |

| V <sub>RH</sub>              | Reset Input<br>High Voltage | 3.8                   | $V_{CC}$ | 3.8                   | $V_{CC}$        |                      | V     |                                                                 |

| $V_{RL}$                     | Reset Input<br>Low Voltage  | -0.3                  | 0.8      | -0.3                  | 0.8             |                      | V     |                                                                 |

| $I_{IL}$                     | Input Leakage               | -2                    | 2        | -2                    | 2               |                      | μΑ    | Test at 0V, V <sub>CC</sub>                                     |

| $I_{OL}$                     | Output<br>Leakage           | -2                    | 2        | -2                    | 2               |                      | μΑ    | Test at 0V, V <sub>CC</sub>                                     |

| I <sub>IR</sub>              | Reset Input<br>Current      |                       | -80      |                       | -80             |                      | μΑ    | V <sub>RL</sub> =0V                                             |

| $I_{CC}$                     | Supply Current              | -                     | 35       |                       | 35              | 24                   | mA    | @ 16 MHz( <sup>1</sup> )                                        |

| I <sub>CC1</sub>             | Standby<br>Current          |                       | 7        |                       | 7               | 4.5                  | mA    | HALT Mode<br>V <sub>IN</sub> = 0 V, V <sub>CC</sub><br>@ 16 MHz |

| I <sub>CC2</sub>             | Standby<br>Current          |                       | 10       |                       | 10              | 1                    | μΑ    | STOP Mode $V_{IN} = 0 V, V_{CC}$ (1)                            |

| I <sub>ALL</sub>             | Autolatch Low<br>Current    | -10                   | 10       | -14                   | 14              |                      | μΑ    |                                                                 |

- 1. All inputs driven to 0V,  $V_{CC}$  and outputs floating. 2.  $V_{CC}$  = 5.0V

Table 18. External I/O or Memory READ/WRITE Timing—Standard/Extended **Temperature**

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Notes |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2,3   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2,3 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 8 $T_DDSR(DR)$ $\overline{DS}$ Fall to Read Data Req'd Valid7575ns9 $T_HDR(DS)$ Read Data to $\overline{DS}$ Rise Hold Time00ns10 $T_DDS(A)$ $\overline{DS}$ Rise to Address Active Delay5050ns11 $T_DDS(AS)$ $\overline{DS}$ Rise to $\overline{AS}$ Fall Delay3535ns12 $T_DR/W(AS)$ $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay2525ns13 $T_DDS(R/W)$ $\overline{DS}$ Rise to $R/\overline{W}$ Not Valid3535ns14 $T_DDW(DSW)$ WRITE Data Valid to $\overline{DS}$ Fall2525ns15 $T_DDS(DW)$ $\overline{DS}$ Rise to WRITE Data Not Valid3535ns15 $T_DDS(DW)$ $\overline{DS}$ Rise to WRITE Data Not Valid3535ns | 1,2,3 |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,2,3 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1,2,3 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2,3   |

| (WRITE) Delay  15 T <sub>D</sub> DS(DW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2,3   |

| Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2,3   |

| 16 Tp A(DR) Address Valid to Read Data Reg'd 230 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2,3   |

| Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1,2,3 |

| $\overline{17}$ T <sub>D</sub> AS(DS) $\overline{AS}$ Rise to $\overline{DS}$ Fall Delay 45 45 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2,3   |

| 18 $T_DDI(DS)$ Data Input Setup to $\overline{DS}$ Rise 60 60 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1,2,3 |

| $ \overline{19}  T_D DM(AS)  \overline{DM} \text{ Valid to } \overline{AS} \text{ Rise Delay} \qquad 30 \qquad \qquad 30 \qquad \qquad \text{ns} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2,3   |

#### Notes:

- 1. When using extended memory timing add 2 TpC.

- Timing numbers provided are for minimum T<sub>P</sub>C.

See Clock Cycle Dependent Characteristics table

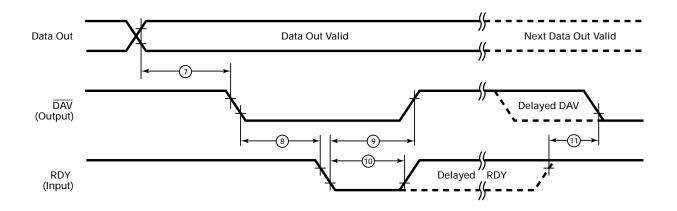

Figure 41. Output Handshake Timing

Table 21. Handshake Timing (Standard and Extended Temperatures)

|    |                           |                                | $T_A = 0^\circ$ | C to +70° | $C  T_A = -40$ | 0°C to +105°C | Data      |

|----|---------------------------|--------------------------------|-----------------|-----------|----------------|---------------|-----------|

| No | Symbol                    | Parameter                      | Min             | Max       | Min            | Max           | Direction |

| 1  | T <sub>S</sub> DI(DAV)    | Data In Setup Time 0           |                 |           | 0              |               | Input     |

| 2  | T <sub>H</sub> DI(RDY)    | Data In Hold Time 14           |                 |           | 145            |               | Input     |

| 3  | $T_{W}DAV$                | Data Available Width 110       |                 |           | 110            |               | Input     |

| 4  | T <sub>D</sub> DAVI(RDY)  | DAV Fall to RDY Fall Delay     |                 | 115       |                | 115           | Input     |

| 5  | T <sub>D</sub> DAVId(RDY) | DAV Out to DAV Fall Delay      |                 | 115       |                | 115           | Input     |

| 6  | RDY0 <sub>D</sub> (DAV)   | RDY Rise to DAV Fall Delay 0   |                 |           | 0              |               | Input     |

| 7  | T <sub>D</sub> D0(DAV)    | Data Out to DAV Fall Delay     |                 | ТрС       |                | ТрС           | Output    |

| 8  | T <sub>D</sub> DAV0(RDY)  | DAV Fall to RDY Fall Delay 0   |                 |           | 0              |               | Output    |

| 9  | T <sub>D</sub> RDY0(DAV)  | RDY Fall to DAV Rise Delay 115 |                 | 115       | Output         |               |           |

| 10 | $T_{W}RDY$                | RDY Width                      | 110             |           | 110            |               | Output    |

| 11 | $T_DRDY0_D(DAV)$          | RDY Rise to DAV Fall Delay     |                 | 115       |                | 115           | Output    |

>

**Note:** All timing references use 2.0V for a logic 1 and 0.8V for a logic 0.

# **Packaging**

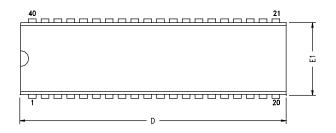

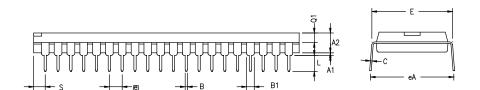

Figure 42 illustrates the 40-pin DIP package for the microcontroller devices.

| SYMBOL  | MILLIN      | 1ETER | INC      | :H    |

|---------|-------------|-------|----------|-------|

| STWIDOL | MIN         | MAX   | MIN      | MAX   |

| A1      | 0.51        | 1.02  | .020     | .040  |

| A2      | 3.18        | 3.94  | .125     | .155  |

| В       | 0.38        | 0.53  | .015     | .021  |

| B1      | 1.02        | 1.52  | .040     | .060  |

| С       | 0.23        | 0.38  | .009     | .015  |

| D       | 52.07       | 52.58 | 2.050    | 2.070 |

| E       | 15.24       | 15.75 | .600     | .620  |

| E1      | 13.59 14.22 |       | .535     | .560  |

| e       | 2.54 TYP    |       | .100 TYP |       |

| eA      | 15.49       | 16.76 | .610     | .660  |

| L       | 3.05        | 3.81  | .120     | .150  |

| Q1      | 1.40        | 1.91  | .055     | .075  |

| S       | 1.52        | 2.29  | .060     | .090  |

CONTROLLING DIMENSIONS : INCH

Figure 42. 40-Pin DIP Package Diagram

PS018501-1002 Packaging

# **Document Information**

# **Document Number Description**

The Document Control Number that appears in the footer of each page of this document contains unique identifying attributes, as indicated in the following table:

| PS   | Product Specification    |

|------|--------------------------|

| 0185 | Unique Document Number   |

| 01   | Revision Number          |

| 0802 | Month and Year Published |

#### **Customer Feedback Form**

### **Z86C91 Product Specification**

If you experience any problems while operating this product, or if you note any inaccuracies while reading this Product Specification, please copy and complete this form, then mail or fax it to ZiLOG (see Return Information, below). We also welcome your suggestions!

#### **Customer Information**

| Name           | Country |

|----------------|---------|

| Company        | Phone   |

| Address        | Fax     |

| City/State/Zip | E-Mail  |

#### **Product Information**

| Serial # or Board Fab #/Rev. # |

|--------------------------------|

| Software Version               |

| Document Number                |

| Host Computer Description/Type |

#### **Return Information**

**ZiLOG** System Test/Customer Support 532 Race Street San Jose, CA 95126-3432 Fax: (408) 558-8536

Email: <u>zservice@zilog.com</u>

### **Problem Description or Suggestion**

| Provide a complete description of the problem or your suggestion. If you are reporting a specific problem, include all steps leading up to the occurrence of the problem. Attach additional pages as necessary. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                 |