Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 16MHz                                                      |

| Connectivity               | UART/USART                                                 |

| Peripherals                | -                                                          |

| Number of I/O              | 24                                                         |

| Program Memory Size        | -                                                          |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | -                                                          |

| RAM Size                   | 236 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LCC (J-Lead)                                            |

| Supplier Device Package    | -                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c9116vsc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

532 Race Street Campbell, CA 95126-3432 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

© 2002 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

PS018501-1002

## List of Figures

| Figure 1.  | Z86C91 Functional Block Diagram               |

|------------|-----------------------------------------------|

| Figure 2.  | 40-Pin DIP Pin Configuration                  |

| Figure 3.  | 44-Pin PQFP Pin Configuration                 |

| Figure 4.  | 44-Pin PLCC Configuration                     |

| Figure 5.  | Port 0 Configuration                          |

| Figure 6.  | Port 1 Configuration                          |

| Figure 7.  | Port 2 Configuration                          |

| Figure 8.  | Port 3 Configuration                          |

| Figure 9.  | Transmitted Data (No Parity) 1                |

| Figure 10. | Transmitted Data (With Parity) 1              |

| Figure 11. | Received Data (No Parity)                     |

| Figure 12. | Received Data (With Parity)                   |

| Figure 13. | Program Memory Map                            |

| Figure 14. | Data Memory Map                               |

| Figure 15. | Register File                                 |

| Figure 16. | Register Pointer Register                     |

| Figure 17. | Register Pointer—Detail                       |

| Figure 18. | Counter/Timer Block Diagram                   |

| Figure 19. | Interrupt Block Diagram                       |

| Figure 20. | Oscillator Configuration                      |

| Figure 21. | Serial I/O Register (F0h: Read/Write)         |

| Figure 22. | Timer Mode Register (F1h: Read/Write)         |

| Figure 23. | Counter Timer 1 Register (F2h: Read/Write)    |

| Figure 24. | Prescaler 1 Register (F3h: Write Only)        |

| Figure 25. | Counter/Timer 0 Register (F4h: Read/Write)    |

| Figure 26. | Prescaler 0 Register (F5h: Write Only)        |

| Figure 27. | Port 2 Mode Register (F6h: Write Only)        |

| Figure 28. | Port 3 Mode Register (F7h: Write Only)        |

| Figure 29. | Port 0 and 1 Mode Register (F8h: Write Only)  |

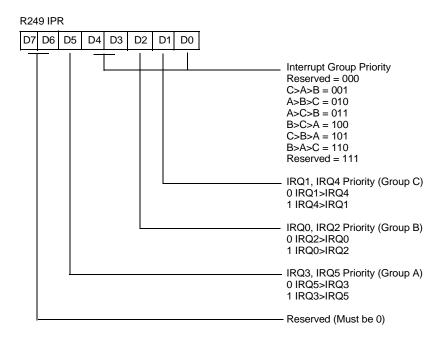

| Figure 30. | Interrupt Priority Register (F9h: Write Only) |

| Figure 31. | Interrupt Request Register (FAh: Read/Write)  |

| Figure 32. | Interrupt Mask Register (FBh: Read/Write)     |

| Figure 33. | Flags Register (FCh: Read/Write)              |

| Figure 34. | Register Pointer Register (FDh: Read/Write)   |

# Z86C91 | CMOS Z8® ROMLess Microcontrollers

| Figure 35. | Stack Pointer Register (FEh: Read/Write)     |

|------------|----------------------------------------------|

| Figure 36. | Stack Pointer Register (FFh: Read/Write)     |

| Figure 37. | Test Load Diagram                            |

| Figure 38. | External I/O or Memory Read and Write Timing |

| Figure 39. | Additional Timing                            |

| Figure 40. | Input Handshake Timing                       |

| Figure 41. | Output Handshake Timing                      |

| Figure 42. | 40-Pin DIP Package Diagram                   |

| Figure 43. | 44-Pin PLCC Package Diagram                  |

| Figure 44. | 44-Pin PQFP Package Diagram                  |

ZiLOG

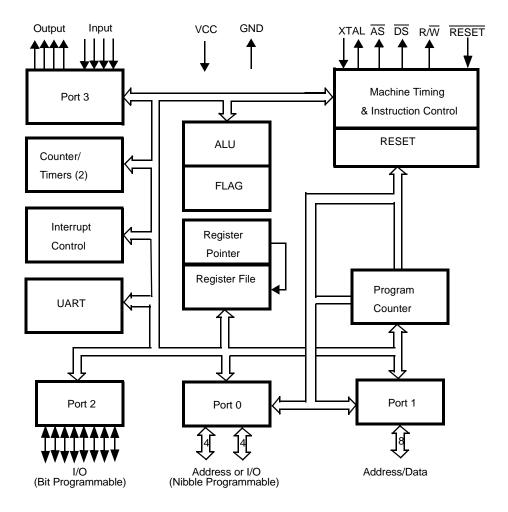

#### **Functional Block Diagrams**

Figure 1. Z86C91 Functional Block Diagram

Table 12. 40-Pin DIP Pin Identification (Continued)

| Pin # | Symbol  | Function                | Direction    |

|-------|---------|-------------------------|--------------|

| 11    | GND     | Ground, V <sub>SS</sub> | Output       |

| 12    | P32     | Port 3, Pin 2           | Input        |

| 13-20 | P00-P07 | Port 0, Pins 0-7        | Input/Output |

| 21-28 | P10-P17 | Port 3, Pins 0-7        | Input/Output |

| 29    | P34     | Port 3, Pin 4           | Output       |

| 30    | P33     | Port 3, Pin 3           | Input        |

| 31-38 | P20-P27 | Port 2, Pins 0-7        | Input/Output |

| 39    | P31     | Port 3, Pin 1           | Input        |

| 40    | P36     | Port 3, Pin 6           | Output       |

ZiLOG

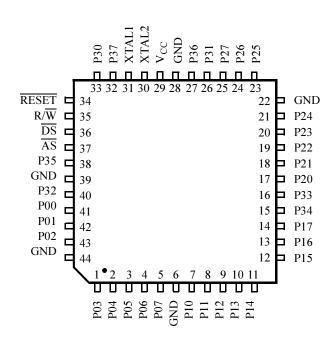

Figure 3. 44-Pin PQFP Pin Configuration

Table 13. 44-Pin PQFP Pin Identification

| Pin # | Symbol  | Function         | Direction    |

|-------|---------|------------------|--------------|

| 1-5   | P03-P07 | Port 0, Bits 3-7 | Input/Output |

| 6     | GND     | Ground           | Output       |

| 7-14  | P10-P17 | Port 1, Bits 0-7 | Input/Output |

| 15    | P34     | Port 3, Bit 4    | Output       |

| 16    | P33     | Port 3, Bit 3    | Intput       |

| 17-21 | P20-P24 | Port 2, Bits 0-4 | Input/Output |

| 22    | GND     | Ground           | Output       |

| 23-25 | P25-P27 | Port 2, Bits 5-7 | Input/Output |

| 26    | P31     | Port 3, Bit 1    | Input        |

| 27    | P36     | Port 3, Bit 6    | Output       |

| 28    | GND     | Ground           | Output       |

Table 13. 44-Pin PQFP Pin Identification (Continued)

| Pin # | Symbol           | Function                  | Direction    |

|-------|------------------|---------------------------|--------------|

| 29    | $V_{CC}$         | Power Supply              | Input        |

| 30    | XTAL2            | Crystal, Oscillator Clock | Output       |

| 31    | XTAL1            | Crystal, Oscillator Clock | Input        |

| 32    | P37              | Port 3, Bit 7             | Output       |

| 33    | P30              | Port 3, Bit 0             | Intput       |

| 34    | RESET            | Reset                     | Input        |

| 35    | $R/\overline{W}$ | Read/Write                | Output       |

| 36    | DS               | Data Strobe               | Output       |

| 37    | ĀS               | Address Strobe            | Output       |

| 38    | P35              | Port 3, Bit 5             | Output       |

| 39    | GND              | Ground                    | Output       |

| 40    | P32              | Port 3, Bit 2             | Input        |

| 41-43 | P00-P02          | Port 0, Bits 0-2          | Input/Output |

| 44    | GND              | Ground                    | Output       |

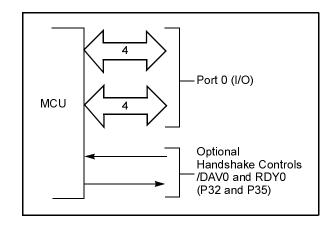

both nibbles are required for I/O operation, they are configured by writing to the Port 01 mode register (P01M).

After a hardware RESET, Port 0 is configured as address lines A15–A8, and extended timing is set to accommodate slow memory access. The initialization routine can include reconfiguration to eliminate this extended timing mode.

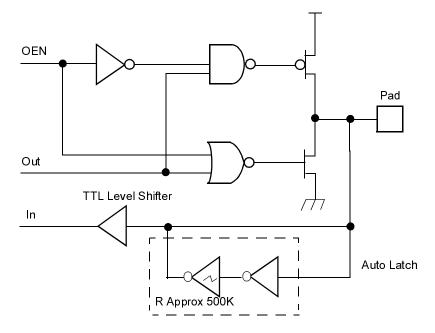

Port 0 can be placed in a high-impedance state along with Port 1,  $\overline{AS}$ ,  $\overline{DS}$  and  $R/\overline{W}$ , allowing the Z8 to share common resources in multiprocessor and DMA applications (Figure 5). A hardware RESET is required to exit this high-impedance state.

Figure 5. Port 0 Configuration

PS018501-1002 Pin Functions

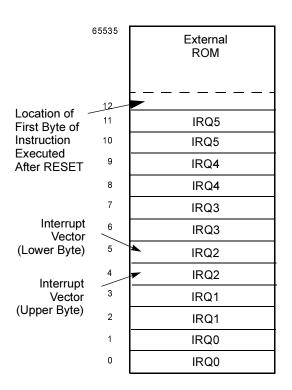

Figure 13. Program Memory Map

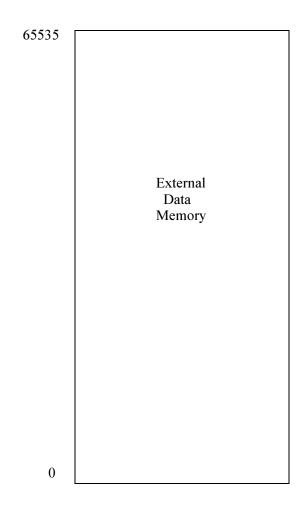

**Data Memory** ( $\overline{DM}$ ). The Z86C91addresses up to 64 KB of external data memory. External data memory may be included with, or separated from, the external program memory space.  $\overline{DM}$ , an optional I/O function that is programmed to appear on pin P34, is used to distinguish between data and program memory space (Figure 14). The state of the  $\overline{DM}$  signal is controlled by the type of instruction being executed. An LDC Op Code references PROGRAM ( $\overline{DM}$  inactive) memory, and an LDE instruction references data ( $\overline{DM}$  active Low) memory. The user must configure Port 3 Mode Register (P3M) bits D3 and D4 for this mode.

Figure 14. Data Memory Map

Register File. The register file contains three I/O port registers, 236 general-purpose registers, and 16 control and status registers (Figure 15). The instructions can access registers directly or indirectly via an 8-bit address field. The Z86C91 also allows short 4-bit register addressing using the Register Pointer (Figure 16). In the 4-bit mode, the register file is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working register group.

General-Purpose Registers (GPR). General-purpose registers are undefined after the device is powered up. These registers keep the most recent value after any RESET, as long as the RESET occurs in the  $V_{CC}$  voltage-specified operating range. General-purpose registers are not guaranteed to keep their most recent state from if  $V_{CC}$  drops below the minimum  $V_{CC}$  operating range.

**Stack Pointer.** The Z86C91 has a 16-bit Stack Pointer (SPH and SPL) used for the external stack, that resides anywhere in the data memory. An 8-bit Stack Pointer (SPL) is used for the internal stack that resides within the 236 general-purpose registers. Stack Pointer High (SPH) is used as a general-purpose register only when using an internal stack.

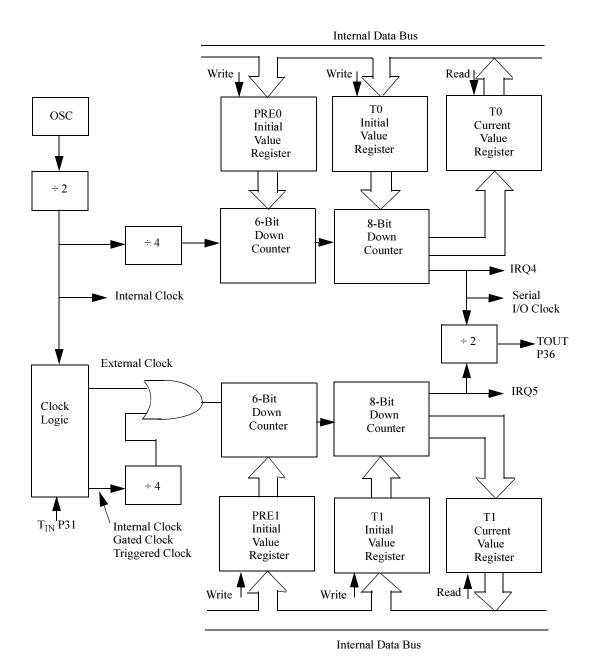

**Counter/Timers.** There are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only (Figure 17).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that is loaded into the counter. When both the counter and prescaler reach the end of the count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters are programmed to START, STOP, restart to CONTINUE, or restart from the initial value. The counters can also be programmed to STOP upon reaching 1 (SIN-GLE-PASS mode) or to automatically reload the initial value and continue counting (MODULO–N CONTINUOUS mode).

The counters, but not the prescalers, are read at any time without disturbing their value or count mode. Reading the prescalers returns the value FFh. The clock source for T1 is user-definable and is either the internal micro controller clock divide-by-four, or an external signal input through Port 3. The maximum frequency of the external timer signal is the XTAL clock signal divided by 8. The Timer Mode Register configures the external timer input (P31) as an external clock, a trigger input that is retriggerable or nonretriggerable, or as a gate input for the internal clock. Port 3 line P36 also serves as an output ( $T_{\rm OUT}$ ) through which T0, T1, or the internal clock is output. The counter/timers are cascaded by connecting the T0 output to the input of T1.

Figure 18. Counter/Timer Block Diagram

Interrupts. The Z8 has six different interrupts from eight different sources. These interrupts are maskable and prioritized. The 8 sources are divided as follows: 4 sources are claimed by Port 3 lines P33–P30, one in Serial Out, one in Serial In, and 2 are claimed by counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register

All interrupts are vectored through locations in Program Memory. When an interrupt request is granted, the interrupt machine cycle is activated. This resets the interrupt request flag and disables all of the subsequent interrupts, except Program Counter and Status Flags, and branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16 bit address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service. Software initiated interrupts are supported by setting the appropriate bit in the Interrupt Request Register (IRQ).

Nested interrupts are supported by enabling interrupts in the interrupt service routine.

Internal interrupt requests are sampled on the falling edge of the last cycle of every instruction, and the interrupt request must be valid 5TpC before the falling edge of the last clock cycle of the currently executing instruction.

When the device samples a valid interrupt request, the next 48TpC (external XTAL clock cycles) are used to prioritize the interrupt, and push the two PC bytes and the FLAG register on the stack. The following nine cycles are used to fetch the interrupt vector from external memory. The first byte of the interrupt service routine is fetched beginning on the 58th TpC cycle following the internal sample point, which corresponds to the 63rd TpC cycle following the external interrupt sample point.

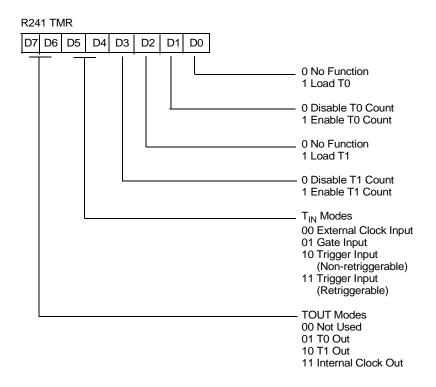

#### **Timer Mode Register**

The Timer Mode Register, TMR, controls timing and counter functions and shown.in Figure 22.

Figure 22. Timer Mode Register (F1h: Read/Write)

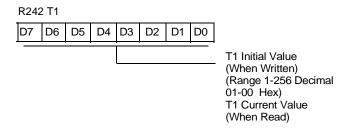

#### Counter/Timer 1 Register

The Counter/Timer 1 Register, T1 is shown in Figure 23.

Figure 23. Counter Timer 1 Register (F2h: Read/Write)

30

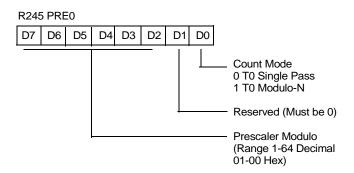

Figure 26. Prescaler 0 Register (F5h: Write Only)

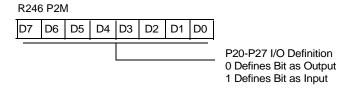

#### Port 2 Mode Register

The Port 2 Mode Register, P2M, controls Port 2 I/O functions and is shown in Figure 27.

Figure 27. Port 2 Mode Register (F6h: Write Only)

### Port 3 Mode Register

The Port 3 Mode Register P3M controls Port 3 I/O functions and is shown in Figure 28.

Figure 30. Interrupt Priority Register (F9h: Write Only)

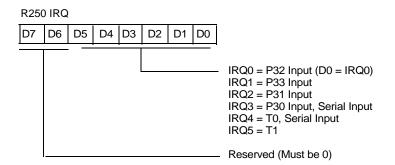

#### **Interrupt Request Register**

The Interrupt Request Register, IRQ, controls interrupt functions and is shown in Figure 31.

Figure 31. Interrupt Request Register (FAh: Read/Write)

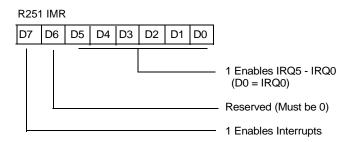

#### **Interrupt Mask Register**

The Interrupt Mask Register, IMR, controls interrupt functions and is shown in Figure 32.

ZiLOG

Figure 32. Interrupt Mask Register (FBh: Read/Write)

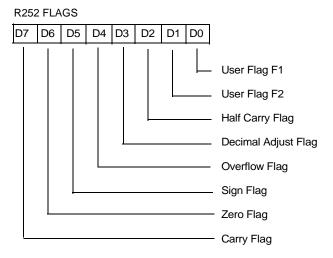

#### Flags Register

The CPU sets flags in the Flags Register, FLAGS, to allow the user to perform tests based on differing logical states. The FLAGS Register is shown in Figure 33.

Figure 33. Flags Register (FCh: Read/Write)

#### Register Pointer Register

The Register Pointer Register, RP, controls pointer functions in the working registers and is shown in Figure 34.

**Table 19. Clock Dependent Formulas**

| Number | Symbol                   | Equation        |  |

|--------|--------------------------|-----------------|--|

| 1      | T <sub>D</sub> A(AS)     | 0.40 TpC + 0.32 |  |

| 2      | T <sub>D</sub> AS(A)     | 0.59 TpC - 3.25 |  |

| 3      | $T_DAS(DR)$              | 2.38 TpC + 6.14 |  |

| 4      | $T_{W}AS$                | 0.66 TpC -1.65  |  |

| 6      | $T_WDSR$                 | 2.33TpC - 10.56 |  |

| 7      | $T_WDSW$                 | 1.27 TpC + 1.67 |  |

| 8      | $T_DDSR(DR)$             | 1.97 TpC - 42.5 |  |

| 10     | $T_DDS(A)$               | 0.8 TpC         |  |

| 11     | $T_DDS(AS)$              | 0.59 TpC - 3.14 |  |

| 12     | $T_D R \overline{W}(AS)$ | 0.4 TpC         |  |

| 13     | $T_DDS(R\overline{W})$   | 0.8 TpC - 15    |  |

| 14     | $T_DDW(DSW)$             | 0.4 TpC         |  |

| 15     | $T_DDS(DW)$              | 0.88 TpC - 19   |  |

| 16     | $T_DA(DR)$               | 4 TpC - 20      |  |

| 17     | T <sub>D</sub> AS(DS)    | 0.91 TpC - 10.7 |  |

| 18     | T <sub>S</sub> DI(DS)    | 0.8 TpC - 10    |  |

| 19     | T <sub>D</sub> DM(AS)    | 0.9 TpC - 26.3  |  |

### **Packaging**

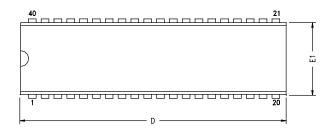

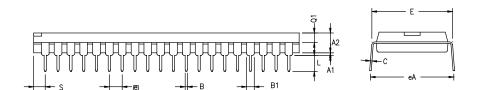

Figure 42 illustrates the 40-pin DIP package for the microcontroller devices.

| SYMBOL  | MILLIN   | MILLIMETER |       | INCH  |  |

|---------|----------|------------|-------|-------|--|

| STINDOL | MIN      | MAX        | MIN   | MAX   |  |

| A1      | 0.51     | 1.02       | .020  | .040  |  |

| A2      | 3.18     | 3.94       | .125  | .155  |  |

| В       | 0.38     | 0.53       | .015  | .021  |  |

| B1      | 1.02     | 1.52       | .040  | .060  |  |

| С       | 0.23     | 0.38       | .009  | .015  |  |

| D       | 52.07    | 52.58      | 2.050 | 2.070 |  |

| E       | 15.24    | 15.75      | .600  | .620  |  |

| E1      | 13.59    | 14.22      | .535  | .560  |  |

| e       | 2.54 TYP |            | .100  | TYP   |  |

| eA      | 15.49    | 16.76      | .610  | .660  |  |

| L       | 3.05     | 3.81       | .120  | .150  |  |

| Q1      | 1.40     | 1.91       | .055  | .075  |  |

| S       | 1.52     | 2.29       | .060  | .090  |  |

CONTROLLING DIMENSIONS : INCH

Figure 42. 40-Pin DIP Package Diagram

PS018501-1002 Packaging

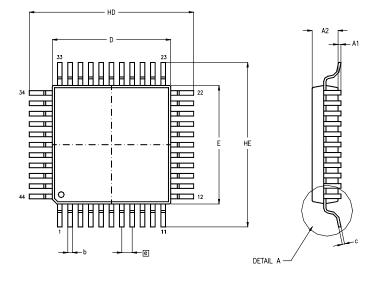

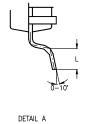

| SYMBOL | MILLIMETER |       | INCH  |      |

|--------|------------|-------|-------|------|

|        | MIN        | MAX   | MIN   | MAX  |

| A1     | 0.05       | 0.25  | .002  | .010 |

| A2     | 2.00       | 2.25  | .078  | .089 |

| Ь      | 0.25       | 0.45  | .010  | .018 |

| С      | 0.13       | 0.20  | .005  | .008 |

| HD     | 13.70      | 14.15 | .539  | .557 |

| D      | 9.90       | 10.10 | .390  | .398 |

| Ħ      | 13.70      | 14.15 | .539  | .557 |

| E      | 9.90       | 10.10 | .390  | .398 |

| е      | 0.80 BSC   |       | .0315 | BSC  |

| L      | 0.60       | 1.20  | .024  | .047 |

NOTES:

1. CONTROLLING DIMENSIONS : MILLIMETER

2. LEAD COPLANARITY : MAX .10 .004"

Figure 44. 44-Pin PQFP Package Diagram

PS018501-1002 Packaging