Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C                                                               |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s2313-10sc |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Description

The AT90S2313 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S2313 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

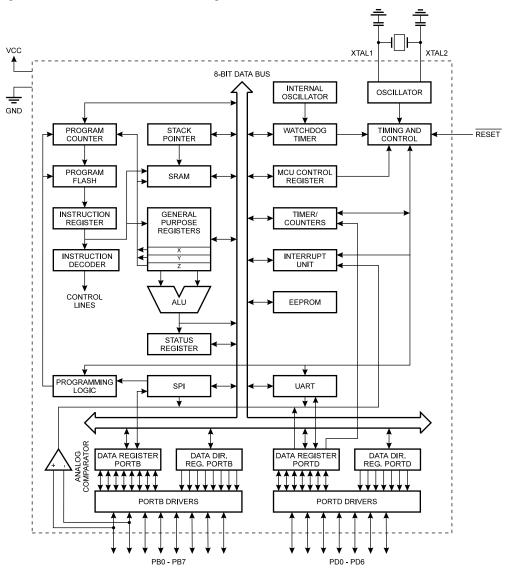

Figure 1. The AT90S2313 Block Diagram

The AT90S2313 provides the following features: 2K bytes of In-System Programmable Flash, 128 bytes EEPROM, 128 bytes SRAM, 15 general purpose I/O lines, 32 general purpose working registers, flexible Timer/Counters with compare modes, internal and external interrupts, a programmable serial UART, programmable Watchdog Timer with internal Oscillator, an SPI serial port for Flash memory downloading and two software

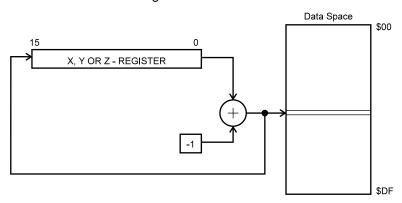

Figure 15. Data Indirect Addressing with Pre-decrement

The X-, Y-, or Z-register is decremented before the operation. Operand address is the decremented contents of the X-, Y-, or Z-register.

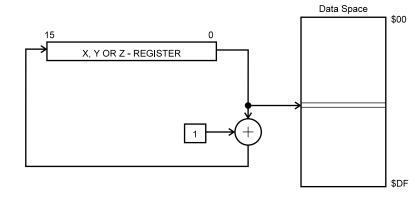

Figure 16. Data Indirect Addressing with Post-increment

The X-, Y-, or Z-register is incremented after the operation. Operand address is the contents of the X-, Y-, or Z-register prior to incrementing.

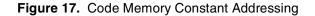

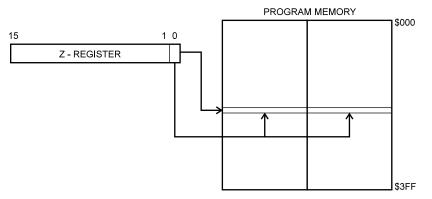

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 1K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

#### Data Indirect with Predecrement

Data Indirect with Postincrement

Constant Addressing Using the LPM Instruction

#### • Bit 5 - H: Half-carry Flag

The Half-carry Flag H indicates a Half-carry in some arithmetic operations. See the Instruction Set description for detailed information.

#### • Bit 4 – S: Sign Bit, S = N $\oplus$ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the Instruction Set description for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the Instruction Set description for detailed information.

#### • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result after the different arithmetic and logic operations. See the Instruction Set description for detailed information.

#### • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result after the different arithmetic and logic operations. See the Instruction Set description for detailed information.

#### • Bit 0 – C: Carry Flag

The Carry Flag C indicates a Carry in an arithmetic or logic operation. See the Instruction Set description for detailed information.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

#### Stack Pointer – SP

An 8-bit register at I/O address \$3D (\$5D) forms the Stack Pointer of the AT90S2313. 8 bits are used to address the 128 bytes of SRAM in locations \$60 - \$DF.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |     |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| \$3D (\$5D)   | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 | SPL |

| Read/Write    | R/W | -   |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

The Stack Pointer points to the data SRAM stack area where the Subroutine and Interrupt Stacks are located. This stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer must be set to point above \$60. The Stack Pointer is decremented by 1 when data is pushed onto the stack with the PUSH instruction, and it is decremented by 2 when an address is pushed onto the stack with subroutine calls and interrupts. The Stack Pointer is incremented by 1 when data is popped from the stack with the POP instruction, and it is incremented by 2 when an address is popped from the stack with return from subroutine RET or return from interrupt RETI.

interrupt. Some of the Interrupt Flags can also be cleared by writing a logical "1" to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the Interrupt Flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditions occur when the Global Interrupt Enable bit is cleared (zero), the corresponding interrupt flag(s) will be set and remembered until the Global Interrupt Enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is active.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

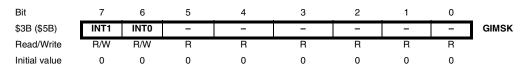

#### General Interrupt Mask Register – GIMSK

#### • Bit 7 - INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from program memory address \$002. See also "External Interrupts".

#### • Bit 6 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the MCU general Control Register (MCUCR) defines whether the External Interrupt is activated on rising or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts."

#### • Bits 5..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S2313 and always read as zero.

Timer/Counter1 can also be used as an 8-, 9-, or 10-bit Pulse Width Modulator. In this mode the counter and the OCR1 Register serve as a glitch-free standalone PWM with centered pulses. Refer to page 35 for a detailed description of this function.

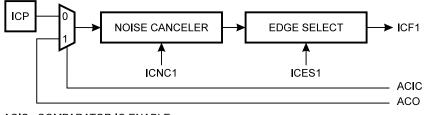

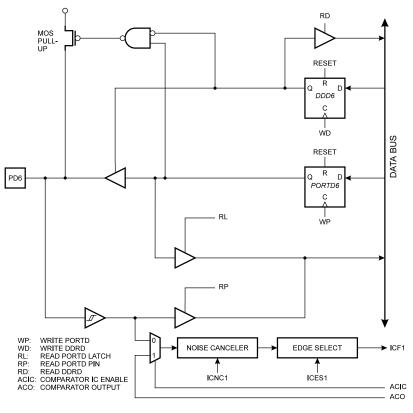

The Input Capture function of Timer/Counter1 provides a capture of the Timer/Counter1 contents to the Input Capture Register (ICR1), triggered by an external event on the Input Capture Pin (ICP). The actual capture event settings are defined by the Timer/Counter1 Control Register (TCCR1B). In addition, the Analog Comparator can be set to trigger the input capture. Refer to "Analog Comparator" on page 48 for details on this. The ICP pin logic is shown in Figure 31.

Figure 31. ICP Pin Schematic Diagram

ACIC: COMPARATOR IC ENABLE ACO: COMPARATOR OUTPUT

If the Noise Canceler function is enabled, the actual trigger condition for the capture event is monitored over four samples, and all four must be equal to activate the capture flag.

#### Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5 | 4 | 3 | 2 | . 1   | 0     |        |

|---------------|--------|--------|---|---|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | - | - | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R | R | R | R | R/W   | R/W   |        |

| Initial value | 0      | 0      | 0 | 0 | 0 | 0 | 0     | 0     |        |

#### • Bits 7, 6 - COM1A1, COM1A0: Compare Output Mode1, Bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1 (Output Compare pin 1) (PB3). This is an alternative function to the I/O port, and the corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in Table 8.

Table 8. Compare 1 Mode Select<sup>(1)(2)</sup>

| COM1A1 | COM1A0 | Description                                     |

|--------|--------|-------------------------------------------------|

| 0      | 0      | Timer/Counter1 disconnected from output pin OC1 |

| 0      | 1      | Toggle the OC1 output line.                     |

| 1      | 0      | Clear the OC1 output line (to zero).            |

| 1      | 1      | Set the OC1 output line (to one).               |

Notes: 1. In PWM mode, these bits have a different function. Refer to Table 12 for a detailed description.

2. The initial state of the OC1 output line is undefined.

#### • Bits 5..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2313 and always read zero.

#### • Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, Bits 2, 1 and 0

The Clock Select1 bits 2, 1, and 0 define the prescaling source of Timer/Counter1.

| CS12 | CS11 | CS10 | Description                          |  |  |  |  |  |  |

|------|------|------|--------------------------------------|--|--|--|--|--|--|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |  |  |  |  |  |  |

| 0    | 0    | 1    | СК                                   |  |  |  |  |  |  |

| 0    | 1    | 0    | CK/8                                 |  |  |  |  |  |  |

| 0    | 1    | 1    | CK/64                                |  |  |  |  |  |  |

| 1    | 0    | 0    | CK/256                               |  |  |  |  |  |  |

| 1    | 0    | 1    | CK/1024                              |  |  |  |  |  |  |

| 1    | 1    | 0    | External Pin T1, falling edge        |  |  |  |  |  |  |

| 1    | 1    | 1    | External Pin T1, rising edge         |  |  |  |  |  |  |

Table 10. Clock 1 Prescale Select

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK Oscillator clock. If the external pin modes are used for Timer/Counter1, transitions on PD5/(T1) will clock the counter even if the pin is configured as an output. This feature can give the user software control of the counting.

# Timer/Counter1 – TCNT1H and TCNT1L

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2D (\$4D)   | MSB |     |     |     |     |     |     |     | TCNT1H |

| \$2C (\$4C)   |     |     |     |     |     |     |     | LSB | TCNT1L |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | -      |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP). This temporary register is also used when accessing OCR1A and ICR1. If the main program and interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program or interrupts if interrupts are re-enabled.

TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP Register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP Register, and all 16 bits are written to the TCNT1 Timer/Counter1 Register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

TCNT1 Timer/Counter1 Read: When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP Register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP Register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock cycle after it is preset with the written value.

#### Timer/Counter1 Output Compare Register A – OCR1AH and OCR1AL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2B (\$4B)   | MSB |     |     |     |     |     |     |     | OCR1AH |

| \$2A (\$4A)   |     |     |     |     |     |     |     | LSB | OCR1AL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

The Output Compare Register is a 16-bit read/write register.

The Timer/Counter1 Output Compare Register contains the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status Registers.

Since the Output Compare Register (OCR1A) is a 16-bit register, a temporary register TEMP is used when OCR1A is written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH, the data is temporarily stored in the TEMP Register. When the CPU writes the low byte, OCR1AL, the TEMP Register is simultaneously written to OCR1AH. Consequently, the high byte OCR1AH must be written first for a full 16-bit register write operation.

The TEMP Register is also used when accessing TCNT1, and ICR1. If the main program and interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program or interrupts if interrupts are re-enabled.

| Bit           | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   |       |

|---------------|-----|----|----|----|----|----|---|-----|-------|

| \$25 (\$45)   | MSB |    |    |    |    |    |   |     | ICR1H |

| \$24 (\$44)   |     |    |    |    |    |    |   | LSB | ICR1L |

|               | 7   | 6  | 5  | 4  | 3  | 2  | 1 | 0   |       |

| Read/Write    | R   | R  | R  | R  | R  | R  | R | R   |       |

|               | R   | R  | R  | R  | R  | R  | R | R   |       |

| Initial value | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

|               | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

#### Timer/Counter1 Input Capture Register – ICR1H and ICR1L

The Input Capture Register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting [ICES1]) of the signal at the input capture pin (ICP) is detected, the current value of the Timer/Counter1 is transferred to the Input Capture Register (ICR1). At the same time, the Input Capture Flag (ICF1) is set (one).

Since the Input Capture Register (ICR1) is a 16-bit register, a temporary register TEMP is used when ICR1 is read to ensure that both bytes are read simultaneously. When the CPU reads the low byte ICR1L, the data is sent to the CPU and the data of the high byte ICR1H is placed in the TEMP Register. When the CPU reads the data in the high byte ICR1H, the CPU receives the data in the TEMP Register. Consequently, the low byte ICR1L must be accessed first for a full 16-bit register read operation.

f<sub>TC1</sub>/2046

The TEMP Register is also used when accessing TCNT1 and OCR1A. If the main program and interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program or interrupts if interrupts are re-enabled.

Timer/Counter1 in PWM Mode When the PWM mode is selected, Timer/Counter1 and the Output Compare Register1 (OCR1A) form an 8-, 9-, or 10-bit, free-running, glitch-free and phase-correct PWM with output on the PB3(OC1) pin. Timer/Counter1 acts as an up/down counter, counting up from \$0000 to TOP (see Table 11), where it turns and counts down again to zero before the cycle is repeated. When the counter value matches the contents of the 8, 9 or 10 least significant bits of OCR1A, the PB3(OC1) pin is set or cleared according to the settings of the COM1A1 and COM1A0 bits in the Timer/Counter1 Control Register (TCCR1). Refer to Table 12 for details.

| PWM Resolution | Timer TOP Value | Frequency              |

|----------------|-----------------|------------------------|

| 8-bit          | \$00FF (255)    | f <sub>TC1</sub> /510  |

| 9-bit          | \$01FF (511)    | f <sub>TC1</sub> /1022 |

Table 11. Timer TOP Values and PWM Frequency

**Table 12.** Compare1 Mode Select in PWM Mode<sup>(1)</sup>

10-bit

| COM1A1 | COM1A0 | Effect on OC1                                                                                 |

|--------|--------|-----------------------------------------------------------------------------------------------|

| 0      | 0      | Not connected                                                                                 |

| 0      | 1      | Not connected                                                                                 |

| 1      | 0      | Cleared on compare match, upcounting. Set on compare match, down-counting (non-inverted PWM). |

| 1      | 1      | Cleared on compare match, downcounting. Set on compare match, up-counting (inverted PWM).     |

\$03FF(1023)

Note: 1. The initial state of the OC1 output line is undefined.

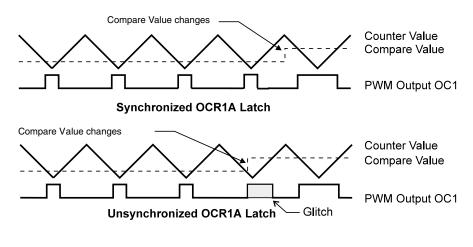

Note that in the PWM mode, the 10 least significant OCR1A bits, when written, are transferred to a temporary location. They are latched when Timer/Counter1 reaches TOP. This prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A write. See Figure 32 for an example.

Figure 32. Effects on Unsynchronized OCR1 Latching

## Watchdog Timer

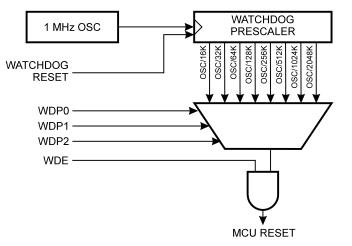

The Watchdog Timer is clocked from a separate On-chip Oscillator that runs at 1 MHz. This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog Reset interval can be adjusted. See Table 14 for a detailed description. The WDR (Watchdog Reset) instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog Reset, the AT90S2313 resets and executes from the Reset Vector. For timing details on the Watchdog Reset, refer to page 21.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

#### Figure 33. Watchdog Timer

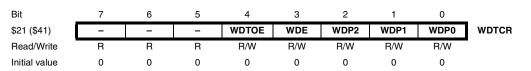

#### Watchdog Timer Control Register – WDTCR

#### • Bits 7..5 - Res: Reserved Bits

These bits are reserved bits in the AT90S2313 and will always read as zero.

#### • Bit 4 – WDTOE: Watchdog Turn-off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the Watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a Watchdog disable procedure.

#### • Bit 3 – WDE: Watchdog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero), the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set (one). To disable an enabled Watchdog Timer, the following procedure must be followed:

found to be logical "1"s, the start bit is rejected as a noise spike and the receiver starts looking for the next 1-to-0 transition.

If, however, a valid start bit is detected, sampling of the data bits following the start bit is performed. These bits are also sampled at samples 8, 9 and 10. The logical value found in at least two of the three samples is taken as the bit value. All bits are shifted into the Transmitter Shift Register as they are sampled. Sampling of an incoming character is shown in Figure 36.

Figure 36. Sampling Received Data

When the stop bit enters the Receiver, the majority of the three samples must be "1" to accept the stop bit. If two or more samples are logical "0"s, the Framing Error (FE) Flag in the UART Status Register (USR) is set. Before reading the UDR Register, the user should always check the FE bit to detect Framing Errors.

Whether or not a valid stop bit is detected at the end of a character-reception cycle, the data is transferred to UDR and the RXC Flag in USR is set. UDR is in fact two physically separate registers; one for transmitted data and one for received data. When UDR is read, the Receive Data Register is accessed, and when UDR is written, the Transmit Data Register is accessed. If 9-bit data word is selected (the CHR9 bit in the UART Control Register [UCR] is set), the RXB8 bit in UCR is loaded with bit 9 in the Transmit Shift Register when data is transferred to UDR.

If, after having received a character, the UDR Register has not been read since the last receive, the OverRun (OR) Flag in UCR is set. This means that the last data byte shifted into the Shift Register could not be transferred to UDR and has been lost. The OR bit is buffered and is updated when the valid data byte in UDR is read. Thus, the user should always check the OR bit after reading the UDR Register in order to detect any overruns if the baud rate is high or CPU load is high.

When the RXEN bit in the UCR Register is cleared (zero), the receiver is disabled. This means that the PD0 pin can be used as a general I/O pin. When RXEN is set, the UART Receiver will be connected to PD0, which is forced to be an input pin regardless of the setting of the DDD0 bit in DDRD. When PD0 is forced to input by the UART, the PORTD0 bit can still be used to control the pull-up resistor on the pin.

When the CHR9 bit in the UCR Register is set, transmitted and received characters are nine bits long plus start and stop bits. The ninth data bit to be transmitted is the TXB8 bit in UCR Register. This bit must be set to the wanted value before a transmission is initiated by writing to the UDR Register. The ninth data bit received is the RXB8 bit in the UCR Register.

#### • Bit 4 – FE: Framing Error

This bit is set if a Framing Error condition is detected (i.e., when the stop bit of an incoming character is zero).

The FE bit is cleared when the stop bit of received data is one.

#### • Bit 3 - OR: OverRun

This bit is set if an OverRun condition is detected (i.e., when a character already present in the UDR Register is not read before the next character has been shifted into the Receiver Shift Register). The OR bit is buffered, which means that it will be set once the valid data still in UDRE is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

#### • Bits 2..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S2313 and will always read as zero.

#### UART Control Register – UCR

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _   |

|---------------|-------|-------|-------|------|------|------|------|------|-----|

| \$0A (\$2A)   | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCR |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | W    | •   |

| Initial value | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |     |

#### • Bit 7 – RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 6 – TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 5 – UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in USR will cause the UART Data Register Empty Interrupt routine to be executed provided that global interrupts are enabled.

#### • Bit 4 – RXEN: Receiver Enable

This bit enables the UART Receiver when set (one). When the Receiver is disabled, the RXC, OR and FE Status Flags cannot become set. If these flags are set, turning off RXEN does not cause them to be cleared.

#### • Bit 3 – TXEN: Transmitter Enable

This bit enables the UART Transmitter when set (one). When disabling the Transmitter while transmitting a character, the Transmitter is not disabled before the character in the Shift Register plus any following character in UDR has been completely transmitted.

#### • Bit 2 - CHR9: 9 Bit Characters

When this bit is set (one), transmitted and received characters are nine bits long plus start and stop bits. The ninth bit is read and written by using the RXB8 and TXB8 bits in UCR, respectively. The ninth data bit can be used as an extra stop bit or a parity bit.

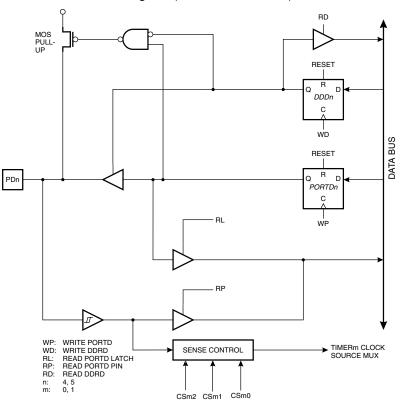

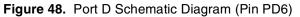

Figure 47. Port D Schematic Diagram (Pins PD4 and PD5)

## **Memory Programming**

### Program and Data Memory Lock Bits

The AT90S2313 MCU provides two Lock bits that can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 21. The Lock bits can only be erased with the Chip Erase operation.

Table 21. Lock Bit Protection Modes

|                                     | Memo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ry Lock   | Bits                   |                                                                                                                                             |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                     | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LB1       | LB2                    | Protection Type                                                                                                                             |  |  |  |

|                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1         | 1                      | No memory lock features enabled.                                                                                                            |  |  |  |

|                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0         | 1                      | Further programming of the Flash and EEPROM is disabled. <sup>(1)</sup>                                                                     |  |  |  |

|                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0         | 0                      | Same as mode 2, and verify is also disabled.                                                                                                |  |  |  |

|                                     | Note: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                        | I mode, further programming of the Fuse bits are also disabled. Program before programming the Lock bits.                                   |  |  |  |

| Fuse Bits                           | The AT9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0S2313    | 3 has tw               | o Fuse bits: SPIEN and FSTRT.                                                                                                               |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                        | use is programmed ("0"), Serial Program and Data Downloading ault value is programmed ("0").                                                |  |  |  |

|                                     | • When the FSTRT Fuse is programmed ("0"), the short start-up time is selected. The default value is unprogrammed ("1"). Parts with this bit pre-programmed ("0") can be delivered on demand.                                                                                                                                                                                                                                                                                                                                         |           |                        |                                                                                                                                             |  |  |  |

|                                     | The Fuse<br>are not a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | accessible in Serial Programming mode. The status of the fuses o Erase.                                                                     |  |  |  |

| Signature Bytes                     | All Atmel microcontrollers have a 3-byte signature code that identifies the device. T code can be read in both serial and parallel mode. The three bytes reside in a separ address space.                                                                                                                                                                                                                                                                                                                                             |           |                        |                                                                                                                                             |  |  |  |

|                                     | For the A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | T90S2     | .313 <sup>(1)</sup> tl | hey are:                                                                                                                                    |  |  |  |

|                                     | 1.\$0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000: \$11 | E (indica              | ates manufactured by Atmel).                                                                                                                |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                        | ates 2 Kb Flash memory).                                                                                                                    |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | •                      | ates AT90S2313 device when signature byte \$001 is \$91).                                                                                   |  |  |  |

|                                     | Note: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                        | ock bits are programmed (Lock mode 3), the signature bytes cannot be<br>mode. Reading the signature bytes will return: \$00, \$01 and \$02. |  |  |  |

| Programming the Flash<br>and EEPROM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                        | ffers 2K bytes of In-System Reprogrammable Flash Program of EEPROM Data memory.                                                             |  |  |  |

|                                     | The AT90S2313 is shipped with the On-chip Flash Program and EEPROM Data mem-<br>ory arrays in the erased state (i.e., contents = \$FF) and ready to be programmed. This<br>device supports a high-voltage (12V) Parallel Programming mode and a low-voltage<br>Serial Programming mode. The +12V is used for programming enable only, and no cur-<br>rent of significance is drawn by this pin. The Serial Programming mode provides a<br>convenient way to download program and data into the AT90S2313 inside the user's<br>system. |           |                        |                                                                                                                                             |  |  |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                        | ROM memory arrays in the AT90S2313 are programmed byte-<br>mming mode. For the EEPROM, an auto-erase cycle is provided                      |  |  |  |

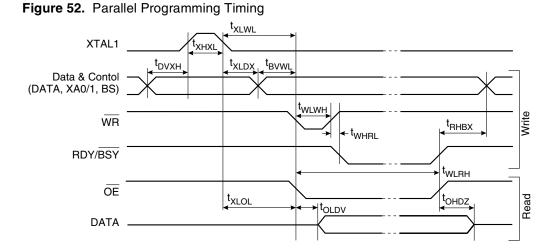

### **Parallel Programming Characteristics**

| Table 26. | Parallel | Programming | Characteristics, | , T <sub>A</sub> = 25°C ± | 10%, $V_{CC} = 5V \pm 10\%$ |

|-----------|----------|-------------|------------------|---------------------------|-----------------------------|

|-----------|----------|-------------|------------------|---------------------------|-----------------------------|

| Symbol                | Parameter                                        | Min  | Тур  | Max   | Units |

|-----------------------|--------------------------------------------------|------|------|-------|-------|

| V <sub>PP</sub>       | Programming Enable Voltage                       | 11.5 |      | 12.5  | V     |

| I <sub>PP</sub>       | Programming Enable Current                       |      |      | 250.0 | μA    |

| t <sub>DVXH</sub>     | Data and Control Setup before XTAL1 High         | 67.0 |      |       | ns    |

| t <sub>XHXL</sub>     | XTAL1 Pulse Width High                           | 67.0 |      |       | ns    |

| t <sub>XLDX</sub>     | Data and Control Hold after XTAL1 Low            | 67.0 |      |       | ns    |

| t <sub>XLWL</sub>     | XTAL1 Low to WR Low                              | 67.0 |      |       | ns    |

| t <sub>BVWL</sub>     | BS Valid to WR Low                               | 67.0 |      |       | ns    |

| t <sub>RHBX</sub>     | BS Hold after RDY/BSY High                       | 67.0 |      |       | ns    |

| t <sub>wLWH</sub>     | WR Pulse Width Low <sup>(1)</sup>                | 67.0 |      |       | ns    |

| t <sub>WHRL</sub>     | WR High to RDY/BSY Low <sup>(2)</sup>            |      | 20.0 |       | ns    |

| t <sub>WLRH</sub>     | WR Low to RDY/BSY High <sup>(2)</sup>            | 0.5  | 0.7  | 0.9   | ms    |

| t <sub>XLOL</sub>     | XTAL1 Low to OE Low                              | 67.0 |      |       | ns    |

| t <sub>OLDV</sub>     | OE Low to DATA Valid                             |      | 20.0 |       | ns    |

| t <sub>OHDZ</sub>     | OE High to DATA Tri-stated                       |      |      | 20.0  | ns    |

| t <sub>wLWH_CE</sub>  | WR Pulse Width Low for Chip Erase                | 5.0  | 10.0 | 15.0  | ms    |

| t <sub>WLWH_PFB</sub> | WR Pulse Width Low for Programming the Fuse Bits | 1.0  | 1.5  | 1.8   | ms    |

Notes: 1. Use  $t_{WLWH\_CE}$  for chip erase and  $t_{WLWH\_PFB}$  for programming the Fuse bits. 2. If  $t_{WLWH}$  is held longer than  $t_{WLRH}$ , no RDY/BSY pulse will be seen.

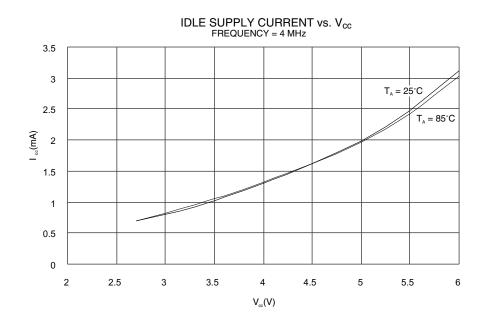

Figure 60. Idle Supply Current vs.  $V_{CC}$

Note: Sink and source capabilities of I/O ports are measured on one pin at a time.

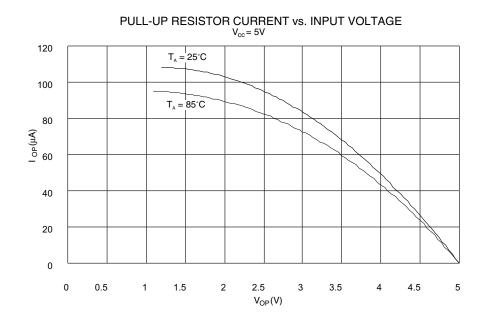

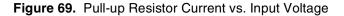

Figure 68. Pull-up Resistor Current vs. Input Voltage

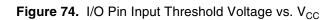

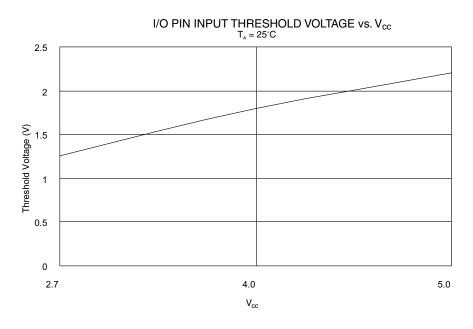

Figure 75. I/O Pin Input Hysteresis vs.  $V_{CC}$

## AT90S2313

## Instruction Set Summary

| Mnemonic       | Operands           | Description                            | Operation                                             | Flags     | # Clocks |

|----------------|--------------------|----------------------------------------|-------------------------------------------------------|-----------|----------|

| ARITHMETIC AND | LOGIC INSTRUCTIONS |                                        |                                                       |           | k        |

| ADD            | Rd, Rr             | Add Two Registers                      | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H | 1        |

| ADC            | Rd, Rr             | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H | 1        |

| ADIW           | Rdl, K             | Add Immediate to Word                  | Rdh:Rdl ← Rdh:Rdl + K                                 | Z,C,N,V,S | 2        |

| SUB            | Rd, Rr             | Subtract Two Registers                 | $Rd \leftarrow Rd - Rr$                               | Z,C,N,V,H | 1        |

| SUBI           | Rd, K              | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                | Z,C,N,V,H | 1        |

| SBIW           | Rdl, K             | Subtract Immediate from Word           | Rdh:Rdl ← Rdh:Rdl – K                                 | Z,C,N,V,S | 2        |

| SBC            | Rd, Rr             | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                           | Z,C,N,V,H | 1        |

| SBCI           | Rd, K              | Subtract with Carry Constant from Reg. | $Rd \gets Rd - K - C$                                 | Z,C,N,V,H | 1        |

| AND            | Rd, Rr             | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                         | Z,N,V     | 1        |

| ANDI           | Rd, K              | Logical AND Register and Constant      | $Rd \gets Rd \bullet K$                               | Z,N,V     | 1        |

| OR             | Rd, Rr             | Logical OR Registers                   | Rd ← Rd v Rr                                          | Z,N,V     | 1        |

| ORI            | Rd, K              | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1        |

| EOR            | Rd, Rr             | Exclusive OR Registers                 | $Rd \gets Rd \oplus Rr$                               | Z,N,V     | 1        |

| COM            | Rd                 | One's Complement                       | $Rd \leftarrow FF - Rd$                               | Z,C,N,V   | 1        |

| NEG            | Rd                 | Two's Complement                       | Rd ← \$00 – Rd                                        | Z,C,N,V,H | 1        |

| SBR            | Rd, K              | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1        |

| CBR            | Rd, K              | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (\$FF - K)$                 | Z,N,V     | 1        |

| INC            | Rd                 | Increment                              | $Rd \leftarrow Rd + 1$                                | Z,N,V     | 1        |

| DEC            | Rd                 | Decrement                              | $Rd \leftarrow Rd - 1$                                | Z,N,V     | 1        |

| TST            | Rd                 | Test for Zero or Minus                 | $Rd \gets Rd \bullet Rd$                              | Z,N,V     | 1        |

| CLR            | Rd                 | Clear Register                         | $Rd \gets Rd \oplus Rd$                               | Z,N,V     | 1        |

| SER            | Rd                 | Set Register                           | $Rd \gets \$FF$                                       | None      | 1        |

| BRANCH INSTRUC | TIONS              |                                        |                                                       |           |          |

| RJMP           | k                  | Relative Jump                          | $PC \gets PC + k + 1$                                 | None      | 2        |

| IJMP           |                    | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                     | None      | 2        |

| RCALL          | k                  | Relative Subroutine Call               | $PC \gets PC + k + 1$                                 | None      | 3        |

| ICALL          |                    | Indirect Call to (Z)                   | $PC \leftarrow Z$                                     | None      | 3        |

| RET            |                    | Subroutine Return                      | $PC \leftarrow STACK$                                 | None      | 4        |

| RETI           |                    | Interrupt Return                       | $PC \leftarrow STACK$                                 | Ι         | 4        |

| CPSE           | Rd, Rr             | Compare, Skip if Equal                 | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$     | None      | 1/2      |

| CP             | Rd, Rr             | Compare                                | Rd – Rr                                               | Z,N,V,C,H | 1        |

| CPC            | Rd, Rr             | Compare with Carry                     | Rd – Rr – C                                           | Z,N,V,C,H | 1        |

| CPI            | Rd, K              | Compare Register with Immediate        | Rd – K                                                | Z,N,V,C,H | 1        |

| SBRC           | Rr, b              | Skip if Bit in Register Cleared        | if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$   | None      | 1/2      |

| SBRS           | Rr, b              | Skip if Bit in Register is Set         | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$   | None      | 1/2      |

| SBIC           | P, b               | Skip if Bit in I/O Register Cleared    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$    | None      | 1/2      |

| SBIS           | P, b               | Skip if Bit in I/O Register is Set     | if $(R(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$    | None      | 1/2      |

| BRBS           | s, k               | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1      | None      | 1/2      |

| BRBC           | s, k               | Branch if Status Flag Cleared          | if (SREG(s) = 0) then $PC \leftarrow PC + k + 1$      | None      | 1/2      |

| BREQ           | k                  | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRNE           | k                  | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRCS           | k                  | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRCC           | k                  | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRSH           | k                  | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRLO           | k                  | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRMI           | k                  | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRPL           | k                  | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRGE           | k                  | Branch if Greater or Equal, Signed     | if (N $\oplus$ V = 0) then PC $\leftarrow$ PC + k + 1 | None      | 1/2      |

| BRLT           | k                  | Branch if Less than Zero, Signed       | if (N $\oplus$ V = 1) then PC $\leftarrow$ PC + k + 1 | None      | 1/2      |

| BRHS           | k                  | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRHC           | k                  | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRTS           | k                  | Branch if T-Flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRTC           | k                  | Branch if T-Flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRVS           | k                  | Branch if Overflow Flag is Set         | if (V = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRVC           | k                  | Branch if Overflow Flag is Cleared     | if (V = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

| BRIE           | k                  | Branch if Interrupt Enabled            | if (I = 1) then $PC \leftarrow PC + k + 1$            | None      | 1/2      |

| BRID           | k                  | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2      |

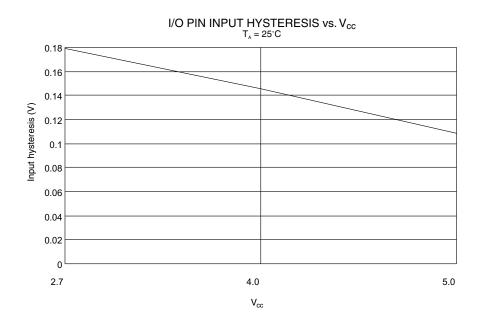

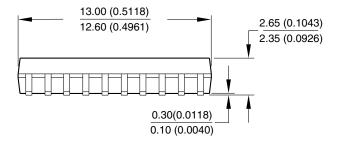

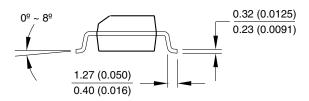

20S, 20-lead, Plastic Gull Wing Small Outline (SOIC), 0.300" body. Dimensions in Millineters and (Inches)\* JEDEC STANDARD MS-013

\*Controlling dimension: Inches

REV. A 04/11/2001

# AT90S2313

|                         | ariation                                                                                                                                                                                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Des                     | scription                                                                                                                                                                                        |

|                         | Pin Descriptions                                                                                                                                                                                 |

|                         | Crystal Oscillator                                                                                                                                                                               |

| Arc                     | hitectural Overview                                                                                                                                                                              |

|                         | General Purpose Register File                                                                                                                                                                    |

|                         | ALU – Arithmetic Logic Unit                                                                                                                                                                      |

|                         | In-System Programmable Flash Program Memory                                                                                                                                                      |

|                         | EEPROM Data Memory                                                                                                                                                                               |

|                         | SRAM Data Memory                                                                                                                                                                                 |

|                         | Program and Data Addressing Modes                                                                                                                                                                |

|                         | Memory Access and Instruction Execution Timing                                                                                                                                                   |

|                         | I/O Memory                                                                                                                                                                                       |

|                         | Reset and Interrupt Handling                                                                                                                                                                     |

|                         | Sleep Modes                                                                                                                                                                                      |

| Tin                     | ner/Counters                                                                                                                                                                                     |

|                         | Timer/Counter Prescaler                                                                                                                                                                          |

|                         | 8-bit Timer/Counter0                                                                                                                                                                             |

|                         | 16-bit Timer/Counter1                                                                                                                                                                            |

|                         |                                                                                                                                                                                                  |

| 14/~                    | tabday Timay                                                                                                                                                                                     |

| Wa                      | tchdog Timer                                                                                                                                                                                     |

|                         | -                                                                                                                                                                                                |

|                         | tchdog Timer<br>PROM Read/Write Access<br>Prevent EEPROM Corruption                                                                                                                              |

| EE                      | PROM Read/Write Access                                                                                                                                                                           |

| EE                      | PROM Read/Write Access<br>Prevent EEPROM Corruption                                                                                                                                              |

| EE                      | PROM Read/Write Access<br>Prevent EEPROM Corruption<br>RT<br>Data Transmission                                                                                                                   |

| EE                      | PROM Read/Write Access<br>Prevent EEPROM Corruption<br>RT<br>Data Transmission<br>Data Reception                                                                                                 |

| EEI<br>UA               | PROM Read/Write Access<br>Prevent EEPROM Corruption<br>RT<br>Data Transmission<br>Data Reception<br>UART Control                                                                                 |

| EE<br>UA<br>Ana         | PROM Read/Write Access Prevent EEPROM Corruption RT Data Transmission Data Reception UART Control alog Comparator                                                                                |

| EE<br>UA<br>Ana         | PROM Read/Write Access Prevent EEPROM Corruption RT Data Transmission Data Reception UART Control Alog Comparator Ports                                                                          |

| EE<br>UA<br>Ana         | PROM Read/Write Access Prevent EEPROM Corruption RT Data Transmission Data Reception UART Control Alog Comparator Ports                                                                          |

| EE<br>UA<br>Ana         | PROM Read/Write Access                                                                                                                                                                           |

| EEI<br>UA<br>Ana<br>I/O | PROM Read/Write Access Prevent EEPROM Corruption RT Data Transmission Data Reception UART Control alog Comparator Ports Port B                                                                   |

| EEI<br>UA<br>Ana<br>I/O | <b>PROM Read/Write Access.</b> Prevent EEPROM Corruption <b>RT</b> Data Transmission.         Data Reception.         UART Control <b>alog Comparator</b> Ports.         Port B.         Port D. |

**Table of Contents**