#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21e16b-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- OPAMP

- OSC16M

- PTC

- All 32KHz clock sources and peripherals

Full functionality and capability will be ensured in PL2. When transitioning between performance levels, the Supply Controller (SUPC) will provide a configurable smooth voltage scaling transition.

## **Related Links**

PM – Power Manager on page 192 SUPC – Supply Controller on page 292 Block Diagram on page 22

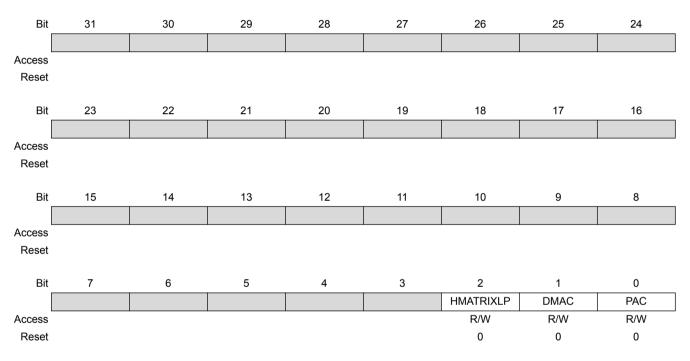

## 13.7.10. Peripheral Interrupt Flag Status and Clear E

This flag is cleared by writing a one to the flag.

This flag is set when a Peripheral Access Error occurs while accessing the peripheral associated with the respective INTFLAGE bit, and will generate an interrupt request if INTENCLR/SET.ERR is one.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the corresponding INTFLAGE interrupt flag.

Name: INTFLAGE Offset: 0x24 Reset: 0x00000 Property: –

Bit 2 – HMATRIXLP: Interrupt Flag for HMATRIXLP

Bit 1 – DMAC: Interrupt Flag for DMAC

Bit 0 – PAC: Interrupt Flag for PAC

## 15.13.10. CoreSight ROM Table Entry 0

Name:ENTRY0Offset:0x1000Reset:0xXXXXX00XProperty:PAC Write-Protection

| Bit    | 31 | 30   | 29      | 28    | 27       | 26 | 25  | 24    |

|--------|----|------|---------|-------|----------|----|-----|-------|

|        |    |      |         |       |          |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | х  | x    | x       | x     | x        | x  | x   | x     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 23 | 22   | 21      | 20    | 19       | 18 | 17  | 16    |

|        |    |      |         | ADDOI | FF[11:4] |    |     |       |

| Access | R  | R    | R       | R     | R        | R  | R   | R     |

| Reset  | x  | x    | x       | x     | x        | x  | x   | x     |

|        |    |      |         |       |          |    |     |       |

| Bit    | 15 | 14   | 13      | 12    | 11       | 10 | 9   | 8     |

|        |    | ADDO | FF[3:0] |       |          |    |     |       |

| Access | R  | R    | R       | R     |          |    |     |       |

| Reset  | x  | x    | x       | х     |          |    |     |       |

|        |    |      |         |       |          |    |     |       |

| Bit    | 7  | 6    | 5       | 4     | 3        | 2  | 1   | 0     |

|        |    |      |         |       |          |    | FMT | EPRES |

| Access |    |      |         |       |          |    | R   | R     |

| Reset  |    |      |         |       |          |    | 1   | x     |

## Bits 31:12 – ADDOFF[19:0]: Address Offset

The base address of the component, relative to the base address of this ROM table.

#### Bit 1 – FMT: Format

Always reads as '1', indicating a 32-bit ROM table.

#### Bit 0 – EPRES: Entry Present

This bit indicates whether an entry is present at this location in the ROM table.

This bit is set at power-up if the device is not protected indicating that the entry is not present.

This bit is cleared at power-up if the device is not protected indicating that the entry is present.

## 21.8.3. Interrupt Flag Status and Clear

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x08<br>0x00000000<br>- |    |           |           |          |          |          |

|--------|-----------------------------------------|------------------------------------|----|-----------|-----------|----------|----------|----------|

| Bit    | 31                                      | 30                                 | 29 | 28        | 27        | 26       | 25       | 24       |

|        |                                         |                                    |    |           |           |          |          |          |

| Access |                                         |                                    |    |           |           |          |          |          |

| Reset  |                                         |                                    |    |           |           |          |          |          |

|        |                                         |                                    |    |           |           |          |          |          |

| Bit    | 23                                      | 22                                 | 21 | 20        | 19        | 18       | 17       | 16       |

|        |                                         |                                    |    |           | DPLLLDRTO | DPLLLTO  | DPLLLCKF | DPLLLCKR |

| Access |                                         | 1                                  |    |           | R/W       | R/W      | R/W      | R/W      |

| Reset  |                                         |                                    |    |           | 0         | 0        | 0        | 0        |

|        |                                         |                                    |    |           |           |          |          |          |

| Bit    | 15                                      | 14                                 | 13 | 12        | 11        | 10       | 9        | 8        |

|        |                                         |                                    |    | DFLLRCS   | DFLLLCKC  | DFLLLCKF | DFLLOOB  | DFLLRDY  |

| Access |                                         | I                                  |    | R/W       | R/W       | R/W      | R/W      | R/W      |

| Reset  |                                         |                                    |    | 0         | 0         | 0        | 0        | 0        |

|        |                                         |                                    |    |           |           |          |          |          |

| Bit    | 7                                       | 6                                  | 5  | 4         | 3         | 2        | 1        | 0        |

|        |                                         |                                    |    | OSC16MRDY |           |          |          | XOSCRDY  |

| Access |                                         |                                    |    | R/W       |           |          |          | R/W      |

| Reset  |                                         |                                    |    | 0         |           |          |          | 0        |

## Bit 19 – DPLLLDRTO: DPLL Loop Divider Ratio Update Complete

This flag is cleared by writing '1' to it.

This flag is set on 0-to-1 transition of the DPLL Loop Divider Ratio Update Complete bit in the Status register (STATUS.DPLLLDRTO) and will generate an interrupt request if INTENSET.DPLLLDRTO is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the DPLL Loop Divider Ratio Update Complete interrupt flag.

## Bit 18 – DPLLLTO: DPLL Lock Timeout

This flag is cleared by writing '1' to it.

This flag is set on 0-to-1 transition of the DPLL Lock Timeout bit in the Status register (STATUS.DPLLLTO) and will generate an interrupt request if INTENSET.DPLLLTO is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the DPLL Lock Timeout interrupt flag.

#### Bit 17 – DPLLLCKF: DPLL Lock Fall

This flag is cleared by writing '1' to it.

This flag is set on 0-to-1 transition of the DPLL Lock Fall bit in the Status register (STATUS.DPLLLCKF) and will generate an interrupt request if INTENSET.DPLLLCKF is '1'.

Writing '0' to this bit has no effect.

the backup sleep modes. In backup sleep modes, a different voltage reference is used, which is configured by the BOD33.BKUPLEVEL bits.

When VDD crosses below the brown-out threshold level, the BOD33 can generate either an interrupt, a Reset, or an Automatic Battery Backup Power Switch, depending on the BOD33 Action bit field (BOD33.ACTION).

If VBAT is monitored, the BOD33 compares the voltage with the brown-out threshold level set in the BOD33 Backup Level field in the BOD33 register (BOD33.BKUPLEVEL).

When VBAT crosses below the backup brown-out threshold level, the BOD33 can generate either an interrupt or a Reset.

The BOD33 detection status can be read from the BOD33 Detection bit in the Status register (STATUS.BOD33DET).

At start-up or at Power-On Reset (POR), the BOD33 register values are loaded from the NVM User Row.

#### **Related Links**

NVM User Row Mapping on page 47

#### 23.6.5.4. 1.2V Brown-Out Detector (BOD12)

The BOD12 is calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration must not be changed to assure the correct behavior of the BOD12. The BOD12 generates a reset when 1.2V crosses below the preset brown-out level. The BODCORE is always disabled in standby sleep mode.

#### **Related Links**

NVM User Row Mapping on page 47

#### 23.6.5.5. Continuous Mode

Continuous mode is the default mode for BOD33.

The BOD33 is continuously monitoring the supply voltage (VDD or VBAT, depending on BOD33.VMON) if it is enabled (BOD33.ENABLE=1) and if the BOD33 Configuration bit in the BOD33 register is cleared (BOD33.ACTCFG=0 for active mode, BOD33.STDBYCFG=0 for standby mode).

#### 23.6.5.6. Sampling Mode

The Sampling Mode is a low-power mode where the BOD33 is being repeatedly enabled on a sampling clock's ticks. The BOD33 will monitor the supply voltage for a short period of time and then go to a low-power disabled state until the next sampling clock tick.

Sampling mode is enabled in Active mode for BOD33 by writing the ACTCFG bit (BOD33.ACTCFG=1). Sampling mode is enabled in Standby mode by writing to the STDBYCFG bit (BOD33.STBYCFG=1). The frequency of the clock ticks (F<sub>clksampling</sub>) is controlled by the Prescaler Select bit groups in the BOD33 register (BOD33.PSEL).

$$F_{clksampling} = \frac{F_{clkprescaler}}{2^{(\text{PSEL}+1)}}$$

The prescaler signal ( $F_{clkprescaler}$ ) is a 1KHz clock, output by the 32KHz Ultra Low Power Oscillator OSCULP32K.

As the sampling clock is different from the APB clock domain, synchronization among the clocks is necessary. See also Synchronization.

# Atmel

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The output is not enabled.                    |

| 1     | The output is enabled and driven by the SUPC. |

## 24.8.8. Clear

Name:CLEAROffset:0x0CReset:0x00Property:Write-Synchronized

| Bit    | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------------|---|---|---|---|---|---|---|

|        | CLEAR[7:0] |   |   |   |   |   |   |   |

| Access | W          | W | W | W | W | W | W | W |

| Reset  | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## Bits 7:0 – CLEAR[7:0]: Watchdog Clear

In Normal mode, writing 0xA5 to this register during the watchdog time-out period will clear the Watchdog Timer and the watchdog time-out period is restarted.

In Window mode, any writing attempt to this register before the time-out period started (i.e., during  $TO_{WDTW}$ ) will issue an immediate system Reset. Writing 0xA5 during the time-out period  $TO_{WDT}$  will clear the Watchdog Timer and the complete time-out sequence (first  $TO_{WDTW}$  then  $TO_{WDT}$ ) is restarted.

In both modes, writing any other value than 0xA5 will issue an immediate system Reset.

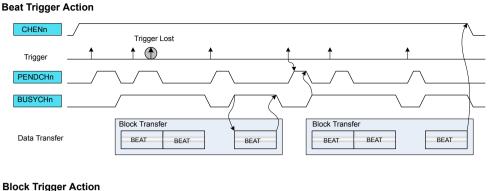

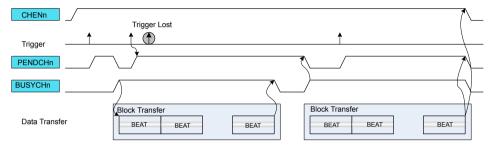

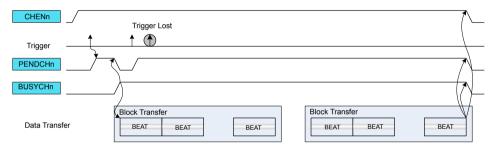

#### Figure 26-7. Trigger Action and Transfers

#### **Block Trigger Action**

#### **Transaction Trigger Action**

If the trigger source generates a transfer request for a channel during an ongoing transfer, the new transfer request will be kept pending (CHSTATUS.PEND=1), and the new transfer can start after the ongoing one is done. Only one pending transfer can be kept per channel. If the trigger source generates more transfer requests while one is already pending, the additional ones will be lost. All channels pending status flags are also available in the Pending Channels register (PENDCH).

When the transfer starts, the corresponding Channel Busy status flag is set in Channel Status register (CHSTATUS.BUSY). When the trigger action is complete, the Channel Busy status flag is cleared. All channel busy status flags are also available in the Busy Channels register (BUSYCH) in DMAC.

#### 26.6.2.7. Addressing

Each block transfer needs to have both a source address and a destination address defined. The source address is set by writing the Transfer Source Address (SRCADDR) register, the destination address is set by writing the Transfer Destination Address (SRCADDR) register.

The addressing of this DMAC module can be static or incremental, for either source or destination of a block transfer, or both.

Incrementation for the source address of a block transfer is enabled by writing the Source Address Incrementation Enable bit in the Block Transfer Control register (BTCTRL.SRCINC=1). The step size of the incrementation is configurable and can be chosen by writing the Step Selection bit in the Block Transfer Control register (BTCTRL.STEPSEL=1) and writing the desired step size in the Address

- BEATSIZE is the configured number of bytes in a beat

- STEPSIZE is the configured number of beats for each incrementation

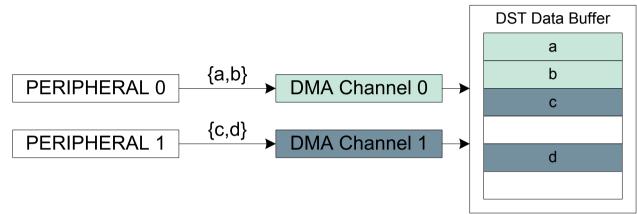

Figure 26-9shows an example where DMA channel 0 is configured to increment destination address by one beat (BTCTRL.DSTINC=1) and DMA channel 1 is configured to increment destination address by two beats (BTCTRL.DSTINC=1, BTCTRL.STEPSEL=0, and BTCTRL.STEPSIZE=0x1). As the source address for both channels are peripherals, source incrementation is disabled (BTCTRL.SRCINC=0).

## Figure 26-9. Destination Address Increment

## 26.6.2.8. Error Handling

If a bus error is received from an AHB slave during a DMA data transfer, the corresponding active channel is disabled and the corresponding Channel Transfer Error Interrupt flag in the Channel Interrupt Status and Clear register (CHINTFLAG.TERR) is set. If enabled, the optional transfer error interrupt is generated. The transfer counter will not be decremented and its current value is written-back in the write-back memory section before the channel is disabled.

When the DMAC fetches an invalid descriptor (BTCTRL.VALID=0) or when the channel is resumed and the DMA fetches the next descriptor with null address (DESCADDR=0x00000000), the corresponding channel operation is suspended, the Channel Suspend Interrupt Flag in the Channel Interrupt Flag Status and Clear register (CHINTFLAG.SUSP) is set, and the Channel Fetch Error bit in the Channel Status register (CHSTATUS.FERR) is set. If enabled, the optional suspend interrupt is generated.

## 26.6.3. Additional Features

#### 26.6.3.1. Linked Descriptors

A transaction can consist of either a single block transfer or of several block transfers. When a transaction consist of several block transfers it is called linked descriptors.

Figure Figure 26-3 illustrates how linked descriptors work. When the first block transfer is completed on DMA channel 0, the DMAC fetches the next transfer descriptor which is pointed to by the value stored in the Next Descriptor Address (DESCADDR) register of the first transfer descriptor. Fetching the next transfer descriptor (DESCADDR) is continued until the last transfer descriptor. When the block transfer for the last transfer descriptor is executed and DESCADDR=0x00000000, the transaction is terminated. For further details on how the next descriptor is fetched from LP SRAM, refer to section Data Transmission.

#### Adding Descriptor to the End of a List

To add a new descriptor at the end of the descriptor list, create the descriptor in LP SRAM, with DESCADDR=0x00000000 indicating that it is the new last descriptor in the list, and modify the DESCADDR value of the current last descriptor to the address of the newly created descriptor.

#### Modifying a Descriptor in a List

In order to add descriptors to a linked list, the following actions must be performed:

## 27.8.6. Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x0CReset:0x0000000Property:PAC Write-Protection

| Bit    | 31  | 30  | 29  | 28    | 27      | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|---------|-----|-----|-----|

|        |     |     |     |       |         |     |     |     |

| Access |     |     |     |       |         |     |     |     |

| Reset  |     |     |     |       |         |     |     |     |

|        |     |     |     |       |         |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19      | 18  | 17  | 16  |

|        |     |     |     |       |         |     |     |     |

| Access |     |     |     |       |         |     |     |     |

| Reset  |     |     |     |       |         |     |     |     |

|        |     |     |     |       |         |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11      | 10  | 9   | 8   |

|        |     |     |     | EXTIN | T[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |     |     |       |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|        |     |     |     | EXTIN | IT[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

## Bits 15:0 – EXTINT[15:0]: External Interrupt x Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the External Interrupt x Enable bit, which disables the external interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

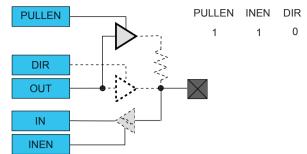

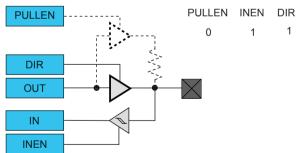

#### Figure 29-5. I/O Configuration - Input with Pull

**Note:** When pull is enabled, the pull value is defined by the OUT value.

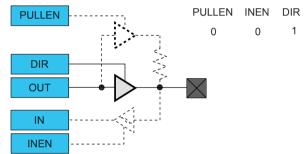

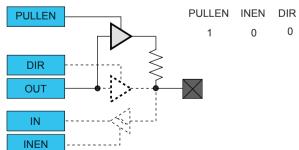

## 29.6.3.3. Totem-Pole Output

When configured for totem-pole (push-pull) output, the pin is driven low or high according to the corresponding bit setting in the OUT register. In this configuration there is no current limitation for sink or source other than what the pin is capable of. If the pin is configured for input, the pin will float if no external pull is connected.

Note: Enabling the output driver will automatically disable pull.

#### Figure 29-6. I/O Configuration - Totem-Pole Output with Disabled Input

#### Figure 29-7. I/O Configuration - Totem-Pole Output with Enabled Input

#### Figure 29-8. I/O Configuration - Output with Pull

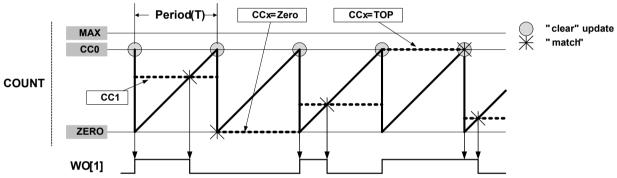

register values. When down-counting, the WO[x] is cleared at start or compare match between the COUNT and ZERO values, and set on compare match between COUNT and CCx register values.

The following equation calculates the exact resolution for a single-slope PWM ( $R_{PWM SS}$ ) waveform:

$$R_{\text{PWM}\_\text{SS}} = \frac{\log(\text{TOP}+1)}{\log(2)}$$

The PWM frequency ( $f_{PWM SS}$ ) depends on TOP value and the peripheral clock frequency ( $f_{GCLK TCC}$ ), and can be calculated by the following equation:

$$f_{\text{PWM}\_\text{SS}} = \frac{f_{\text{GCLK}\_\text{TC}}}{N(\text{TOP}+1)}$$

Where N represents the prescaler divider used (1, 2, 4, 8, 16, 64, 256, 1024).

## Match Pulse-Width Modulation Operation (MPWM)

In MPWM, the output of WO[1] is depending on CC1 as shown in the figure below. On on every overflow/ underflow, a one-TC-clock-cycle negative pulse is put out on WO[0] (not shown in the figure).

The table below shows the update counter and overflow event/interrupt generation conditions in different operation modes.

| Table 55-5. | Table 55-5. Counter opuale and Overnow Eventimetrupt Conditions in TC |     |           |                 |           |             |      |  |  |

|-------------|-----------------------------------------------------------------------|-----|-----------|-----------------|-----------|-------------|------|--|--|

| Name        | Operation                                                             | ТОР | Update    | Output Wave     | eform     | OVFIF/Event |      |  |  |

|             |                                                                       |     |           | On Match        | On Update | Up          | Down |  |  |

| NFRQ        | Normal Frequency                                                      | PER | TOP/ ZERO | Toggle          | Stable    | TOP         | ZERO |  |  |

| MFRQ        | Match Frequency                                                       | CC0 | TOP/ ZERO | Toggle          | Stable    | TOP         | ZERO |  |  |

| NPWM        | Single-slope PWM                                                      | PER | TOP/ ZERO | See description | on above. | TOP         | ZERO |  |  |

| MPWM        | Single-slope PWM                                                      | CC0 | TOP/ ZERO | Toggle          | Toggle    | TOP         | ZERO |  |  |

Table 35-3 Counter Undate and Overflow Event/interrupt Conditions in TC

#### **Related Links**

PORT: IO Pin Controller on page 512

## 35.6.2.7. Double Buffering

The Compare Channels (CCx) registers, and the Period (PER) register in 8-bit mode are double buffered. Each buffer register has a buffer valid bit (CCBUFVx or PERBUFV) in the STATUS register, which indicates that the buffer register contains a new valid value that can be copied into the corresponding register. As long as the respective buffer valid status flag (PERBUFV or CCBUFVx) are set to '1', related syncbusy bits are set (SYNCBUSY.PER or SYNCBUSY.CCx), a write to the respective PER/PERBUF or

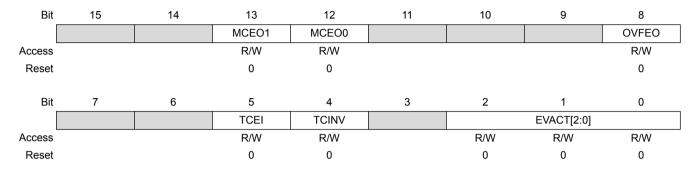

## 35.8.4. Event Control

Name:EVCTRLOffset:0x06Reset:0x0000Property:PAC Write-Protection, Enable-Protected

## Bit 8 – OVFEO: Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

## Bit 5 – TCEI: TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Va | lue | Description                   |

|----|-----|-------------------------------|

| 0  |     | Incoming events are disabled. |

| 1  |     | Incoming events are enabled.  |

#### Bit 4 – TCINV: TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |  |

|-------|-------------------------------------|--|

| 0     | Input event source is not inverted. |  |

| 1     | Input event source is inverted.     |  |

## Bits 2:0 – EVACT[2:0]: Event Action

These bits define the event action the TC will perform on an event.

| Value | Name      | Description                             |

|-------|-----------|-----------------------------------------|

| 0x0   | OFF       | Event action disabled                   |

| 0x1   | RETRIGGER | Start, restart or retrigger TC on event |

| 0x2   | COUNT     | Count on event                          |

## 35.8.18. Channel x Compare/Capture Value, 16-bit Mode

Name:CCxOffset:0x1C+i\*0x2 [i=0..1]Reset:0x0000Property:Write-Synchronized

| 15       | 14                   | 13                               | 12                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------------|----------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC[15:8] |                      |                                  |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| R/W      | R/W                  | R/W                              | R/W                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | 0                    | 0                                | 0                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                      |                                  |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7        | 6                    | 5                                | 4                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                  |

| CC[7:0]  |                      |                                  |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| R/W      | R/W                  | R/W                              | R/W                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | 0                    | 0                                | 0                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | R/W<br>0<br>7<br>R/W | R/W R/W<br>0 0<br>7 6<br>R/W R/W | R/W R/W R/W   0 0 0   7 6 5   R/W R/W R/W | R/W R/W R/W R/W R/W O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O O <th< td=""><td>R/W R/W R/W R/W R/W R/W R/W R/W Q/W Q/W</td></th<> <td>CC[15:8]   R/W R/W</td> <td>CC[15:8]   R/W R/W</td> | R/W R/W R/W R/W R/W R/W R/W R/W Q/W | CC[15:8]   R/W | CC[15:8]   R/W |

## Bits 15:0 – CC[15:0]: Channel x Compare/Capture Value

These bits contain the compare/capture value in 16-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (WAVE.WAVEGEN), the CC0 register is used as a period register.

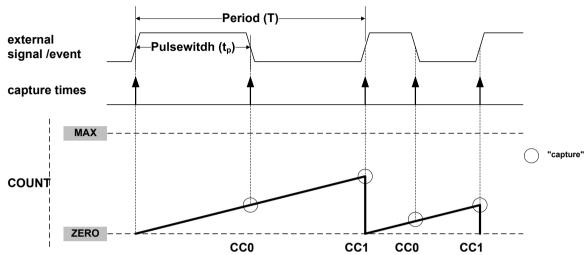

The TCC can perform two input captures and restart the counter on one of the edges. This enables the TCC to measure the pulse-width and period and to characterize the frequency *f* and *dutyCycle* of an input signal:

$$f = \frac{1}{T}$$

,  $dutyCycle = \frac{t_p}{T}$

Figure 36-16. PWP Capture

Selecting PWP or PPW in the Timer/Counter Event Input 1 Action bit group in the Event Control register (EVCTRL.EVACT1) enables the TCC to perform one capture action on the rising edge and the other one on the falling edge. When using PPW (period and pulse-width) event action, period T will be captured into CC0 and the pulse-width  $t_p$  into CC1. The PWP (Pulse-width and Period) event action offers the same functionality, but T will be captured into CC1 and  $t_p$  into CC0.

The Timer/Counter Event x Invert Enable bit in Event Control register (EVCTRL.TCEINVx) is used for event source x to select whether the wraparound should occur on the rising edge or the falling edge. If EVCTRL.TCEINVx=1, the wraparound will happen on the falling edge.

The corresponding capture is done only if the channel is enabled in capture mode (CTRLA.CPTENx=1). If not, the capture action will be ignored and the channel will be enabled in compare mode of operation. When only one of these channel is required, the other channel can be used for other purposes.

The TCC can detect capture overflow of the input capture channels: When a new capture event is detected while the INTFLAG.MCx is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

**Note:** When up-counting (CTRLBSET.DIR=0), counter values lower than 1 cannot be captured in Capture Minimum mode (FCTRLn.CAPTURE=CAPTMIN). To capture the full range including value 0, the TCC must be configured in down-counting mode (CTRLBSET.DIR=0).

**Note:** In dual-slope PWM operation, and when TOP is lower than MAX/2, the CCx MSB captures the CTRLB.DIR state to identify the ramp on which the capture has been done. For rising ramps CCx[MSB] is zero, for falling ramps CCx[MSB]=1.

## 36.6.3. Additional Features

## 36.6.3.1. One-Shot Operation

When one-shot is enabled, the counter automatically stops on the next counter overflow or underflow condition. When the counter is stopped, the Stop bit in the Status register (STATUS.STOP) is set and the waveform outputs are set to the value defined by DRVCTRL.NREx and DRVCTRL.NRVx.

## Bit 2 – CTRLB: CTRLB Synchronization Busy

This bit is cleared when the synchronization of CTRLB register between the clock domains is complete.

This bit is set when the synchronization of CTRLB register between clock domains is started.

#### Bit 1 – ENABLE: ENABLE Synchronization Busy

This bit is cleared when the synchronization of ENABLE bit between the clock domains is complete.

This bit is set when the synchronization of ENABLE bit between clock domains is started.

#### Bit 0 – SWRST: SWRST Synchronization Busy

This bit is cleared when the synchronization of SWRST bit between the clock domains is complete.

This bit is set when the synchronization of SWRST bit between clock domains is started.

#### Bits 8, 9, 10, 11 – CCn: Compare/Capture Channel x Synchronization Busy

This bit is cleared when the synchronization of Compare/Capture Channel x register between the clock domains is complete.

This bit is set when the synchronization of Compare/Capture Channel x register between clock domains is started.

CCx bit is available only for existing Compare/Capture Channels. For details on CC channels number, refer to each TCC feature list.

This bit is set when the synchronization of CCx register between clock domains is started.

#### Table 36-8. Fault n Capture Action

| Value    | Name    | Description                                                                                                                                                               |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0      | DISABLE | Capture on valid recoverable Fault n is disabled                                                                                                                          |

| 0x1 CAPT |         | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].                                                                   |

|          |         | INTFLAG.FAULTn flag rises on each new captured value.                                                                                                                     |

| 0x2      | CAPTMIN | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0], if COUNT value is lower than the last stored capture value (CC).  |

|          |         | INTFLAG.FAULTn flag rises on each local minimum detection.                                                                                                                |

| 0x3      | CAPTMAX | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0], if COUNT value is higher than the last stored capture value (CC). |

|          |         | INTFLAG.FAULTn flag rises on each local maximun detection.                                                                                                                |

| 0x4      | LOCMIN  | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].                                                                   |

|          |         | INTFLAG.FAULTn flag rises on each local minimum value detection.                                                                                                          |

| 0x5      | LOCMAX  | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].                                                                   |

|          |         | INTFLAG.FAULTn flag rises on each local maximun detection.                                                                                                                |

| 0x6      | DERIV0  | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].                                                                   |

|          |         | INTFLAG.FAULTn flag rises on each local maximun or minimum detection.                                                                                                     |

## Bits 11:10 – CHSEL[1:0]: Recoverable Fault n Capture Channel

These bits select the channel for capture operation triggered by recoverable Fault n.

| Value | Name | Description                   |

|-------|------|-------------------------------|

| 0x0   | CC0  | Capture value stored into CC0 |

| 0x1   | CC1  | Capture value stored into CC1 |

| 0x2   | CC2  | Capture value stored into CC2 |

| 0x3   | CC3  | Capture value stored into CC3 |

## Bits 9:8 – HALT[1:0]: Recoverable Fault n Halt Operation

These bits select the halt action for recoverable Fault n.

## 38. AES – Advanced Encryption Standard

## 38.1. Overview

The Advanced Encryption Standard peripheral (AES) provides a means for symmetric-key encryption of 128-bit blocks, in compliance to NIST specifications.

A symmetric-key algorithm requires the same key for both encryption and decryption.

Different key sizes are supported. The key size determines the number of repetitions of transformation rounds that convert the input (called the "plaintext") into the final output ("ciphertext"). The number of rounds of repetition is as follows:

- 10 rounds of repetition for 128-bit keys

- 12 rounds of repetition for 192-bit keys

- 14 rounds of repetition for 256-bit keys

## 38.2. Features

- Compliant with FIPS Publication 197, Advanced Encryption Standard (AES)

- 128/192/256 bit cryptographic key supported

- Encryption time of 57/67/77 cycles with 128-bit/192-bit/256-bit cryptographic key

- Five confidentiality modes of operation as recommended in NIST Special Publication 800-38A

- Electronic Code Book (ECB)

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR)

- Supports Counter with CBC-MAC (CCM/CCM\*) mode for authenticated encryption

- 8, 16, 32, 64, 128-bit data sizes possible in CFB mode

- Optional (parameter) Galois Counter mode (GCM) encryption and authentication

- Intermediate GHASH is stored in GHASHx register and Cipher Text available in DATA register.

- Continue 3 to 5 till the input of plain text to get the cipher text and the Hash keys.

- At the last input, set CTRLB.EOM.

- Write last indata to DATA reg.

- Wait for INTFLAG.ENCCMP to be set.

- AES Hardware generates output in DATA register and final Hash key in GHASHx register.

- Load [LEN(A)]64||[LEN(C)]64 in DATA register and set CTRLB.GFMUL and CTRLB.START as 1.

- Wait for INTFLAG.GFMCMP to be set.

- AES Hardware generates final GHASH value in GHASHx register.

## **Tag Generation**

- Configure CTRLA

- 1.1. Set CTRLA.ENABLE to 0

- 1.2. Set CTRLA.AESMODE as CTR

- 1.3. Set CTRLA.ENABLE to 1

- Load J0 value to INITVECTVx reg.

- Load GHASHx value to DATA reg.

- Set CTRLB.NEWMSG and CTRLB.START to start the Counter mode operation.

- Wait for INTFLAG.ENCCMP to be set.

- AES Hardware generates the GCM Tag output in DATA register.

## 38.6.4. Synchronization

Not applicable.

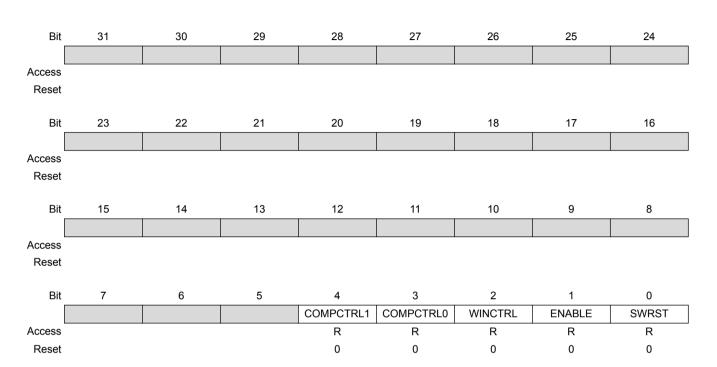

## 43.8.13. Synchronization Busy

Name:SYNCBUSYOffset:0x20Reset:0x0000000Property:Read-Only

#### Bit 2 – WINCTRL: WINCTRL Synchronization Busy

This bit is cleared when the synchronization of the WINCTRL register between the clock domains is complete.

This bit is set when the synchronization of the WINCTRL register between clock domains is started.

### Bit 1 – ENABLE: Enable Synchronization Busy

This bit is cleared when the synchronization of the CTRLA.ENABLE bit between the clock domains is complete.

This bit is set when the synchronization of the CTRLA.ENABLE bit between clock domains is started.

#### Bit 0 – SWRST: Software Reset Synchronization Busy

This bit is cleared when the synchronization of the CTRLA.SWRST bit between the clock domains is complete.

This bit is set when the synchronization of the CTRLA.SWRST bit between clock domains is started.

#### Bits 4,3 – COMPCTRLx: COMPCTRLx Synchronization Busy

This bit is cleared when the synchronization of the COMPCTRLx register between the clock domains is complete.

This bit is set when the synchronization of the COMPCTRLx register between clock domains is started.