#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21e17b-aut |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 9.4.1. Power-On Reset on VDDIN

VDDIN is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VDDIN goes below the threshold voltage, the entire chip is reset.

### 9.4.2. Power-On Reset on VSWOUT

VSWOUT is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VSWOUT goes below the threshold voltage, the entire chip is reset.

### 9.4.3. Power-On Reset on VDDIO

VDDIO is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VDDIO goes below the threshold voltage, all I/Os supplied by VSWOUT are reset.

### 9.4.4. Brown-Out Detector on VSWOUT/VBAT

BOD33 monitors VSWOUT or VBAT depending on configuration.

### **Related Links**

SUPC – Supply Controller on page 292 Battery Backup Power Switch on page 297

### 9.4.5. Brown-Out Detector on VDDCORE

Once the device has started up, BOD12 monitors the internal VDDCORE.

### **Related Links**

SUPC – Supply Controller on page 292 Battery Backup Power Switch on page 297

# 9.5. Performance Level Overview

By default, the device will start in Performance Level 0. This PL0 is aiming for the lowest power consumption by limiting logic speeds and the CPU frequency. As a consequence, all GCLK will have limited capabilities, and some peripherals and clock sources will not work or with limited capabilities:

List of peripherals/clock sources not available in PL0:

- USB (limited by logic frequency)

- DFLL48M

List of peripherals/clock sources with limited capabilities in PL0:

- All AHB/APB peripherals are limited by CPU frequency

- DPLL96M: may be able to generate 48MHz internally, but the output cannot be used by logic

- GCLK: the maximum frequency is by factor 4 compared to PL2

- SW interface: the maximum frequency is by factor 4 compared to PL2

- TC: the maximum frequency is by factor 4 compared to PL2

- TCC: the maximum frequency is by factor 4 compared to PL2

- SERCOM: the maximum frequency is by factor 4 compared to PL2

List of peripherals/clock sources with full capabilities in PL0:

- AC

- ADC

- DAC

- EIC

### PM – Power Manager on page 192

### 13.4.3. Clocks

The PAC bus clock (CLK\_PAC\_APB) can be enabled and disabled in the Main Clock module. The default state of CLK\_PAC\_APB can be found in the related links.

### **Related Links**

MCLK – Main Clock on page 154 Peripheral Clock Masking on page 157

### 13.4.4. DMA

Not applicable.

### 13.4.5. Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the PAC interrupt requires the Interrupt Controller to be configured first.

### Table 13-1. Interrupt Lines

| Instances | NVIC Line |

|-----------|-----------|

| PAC       | PACERR    |

# **Related Links**

Nested Vector Interrupt Controller on page 52

### 13.4.6. Events

The events are connected to the Event System, which may need configuration.

### **Related Links**

EVSYS - Event System on page 544

### 13.4.7. Debug Operation

When the CPU is halted in debug mode, write protection of all peripherals is disabled and the PAC continues normal operation.

# 13.4.8. Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

- Write Control (WRCTRL) register

- AHB Slave Bus Interrupt Flag Status and Clear (INTFLAGAHB) register

- Peripheral Interrupt Flag Status and Clear n (INTFLAG A/B/C...) registers

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

# 13.5. Functional Description

# 13.5.1. Principle of Operation

The Peripheral Access Control module allows the user to set a write protection on peripheral modules and generate an interrupt in case of a peripheral access violation. The peripheral's protection can be set,

There is one exception concerning the Generator 0. As it is used as GCLK\_MAIN, it cannot be locked. It is reset by any Reset and will start up in a known configuration. The software reset (CTRLA.SWRST) can not unlock the registers.

In case of an external Reset, the Generator source will be disabled. Even if the WRTLOCK bit is written to '1' the peripheral channels are disabled (PCHCTRLm.CHEN set to '0') until the Generator source is enabled again. Then, the PCHCTRLm.CHEN are set to '1' again.

### **Related Links**

CTRLA on page 146 PCHCTRLm on page 151

# 17.6.4. Additional Features

### 17.6.4.1. Peripheral Clock Enable after Reset

The Generic Clock Controller must be able to provide a generic clock to some specific peripherals after a Reset. That means that the configuration of the Generators and Peripheral Channels after Reset is device-dependent.

Refer to GENCTRLn.SRC for details on GENCTRLn reset.

Refer to PCHCTRLm.SRC for details on PCHCTRLm reset.

### 17.6.5. Sleep Mode Operation

### 17.6.5.1. SleepWalking

The GCLK module supports the SleepWalking feature.

If the system is in a sleep mode where the Generic Clocks are stopped, a peripheral that needs its clock in order to execute a process must request it from the Generic Clock Controller.

The Generic Clock Controller receives this request, determines which Generic Clock Generator is involved and which clock source needs to be awakened. It then wakes up the respective clock source, enables the Generator and Peripheral Channel stages successively, and delivers the clock to the peripheral.

The RUNSTDBY bit in the Generator Control register controls clock output to pin during standby sleep mode. If the bit is cleared, the Generator output is not available on pin. When set, the GCLK can continuously output the generator output to GCLK\_IO. Refer to External Clock for details.

### **Related Links**

PM – Power Manager on page 192

### 17.6.5.2. Minimize Power Consumption in Standby

The following table identifies when a Clock Generator is off in Standby Mode, minimizing the power consumption:

| Request for Clock n present | GENCTRLn.RUNSTDB<br>Y | GENCTRLn.OE | Clock Generator n |

|-----------------------------|-----------------------|-------------|-------------------|

| yes                         | -                     | -           | active            |

| no                          | 1                     | 1           | active            |

| no                          | 1                     | 0           | OFF               |

### Table 17-2. Clock Generator n Activity in Standby Mode

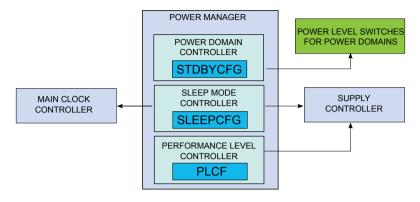

# 20.3. Block Diagram

### Figure 20-1. PM Block Diagram

# 20.4. Signal Description

Not applicable.

# 20.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 20.5.1. I/O Lines

Not applicable.

### 20.5.2. Clocks

The PM bus clock (CLK\_PM\_APB) can be enabled and disabled in the Main Clock module. If this clock is disabled, it can only be re-enabled by a system reset.

### 20.5.3. DMA

Not applicable.

### 20.5.4. Interrupts

The interrupt request line is connected to the interrupt controller. Using the PM interrupt requires the interrupt controller to be configured first.

### **Related Links**

Nested Vector Interrupt Controller on page 52

### 20.5.5. Events

Not applicable.

### 20.5.6. Debug Operation

When the CPU is halted in debug mode, the PM continues normal operation. If standby sleep mode is requested by the system while in debug mode, the power domains are not turned off. As a consequence, power measurements while in debug mode are not relevant.

If Backup sleep mode is requested by the system while in debug mode, the core domains are kept on, and the debug modules are kept running to allow the debugger to access internal registers. When exiting

The OSCULP32K can be used as a source for Generic Clock Generators (GCLK) or for the Real-Time Counter (RTC). To ensure proper operation, the GCLK or RTC modules must be disabled before the clock selection is changed.

### **Related Links**

RTC – Real-Time Counter on page 347 Real-Time Counter Clock Selection on page 279 GCLK - Generic Clock Controller on page 133

# 22.6.5. Watchdog Timer Clock Selection

The Watchdog Timer (WDT) uses the internal 1.024kHz OSCULP32K output clock. This clock is running all the time and internally enabled when requested by the WDT module.

### **Related Links**

WDT - Watchdog Timer on page 327

# 22.6.6. Real-Time Counter Clock Selection

Before enabling the RTC module, the RTC clock must be selected first. All oscillator outputs are valid as RTC clock. The selection is done in the RTC Control register (RTCCTRL). To ensure a proper operation, it is highly recommended to disable the RTC module first, before the RTC clock source selection is changed.

### **Related Links**

RTC - Real-Time Counter on page 347

### 22.6.7. Interrupts

The OSC32KCTRL has the following interrupt sources:

- XOSC32KRDY 32KHz Crystal Oscillator Ready: A 0-to-1 transition on the STATUS.XOSC32KRDY bit is detected

- OSC32KRDY 32KHz Internal Oscillator Ready: A 0-to-1 transition on the STATUS.OSC32KRDY bit is detected

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs. Each interrupt can be enabled individually by setting the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the OSC32KCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSC32KCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

### **Related Links**

PM – Power Manager on page 192 Nested Vector Interrupt Controller on page 52

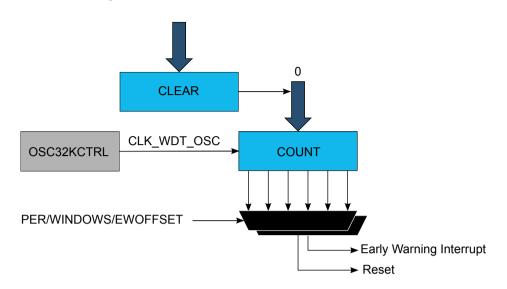

# 24.3. Block Diagram

Figure 24-1. WDT Block Diagram

# 24.4. Signal Description

Not applicable.

# 24.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 24.5.1. I/O Lines

Not applicable.

# 24.5.2. Power Management

The WDT can continue to operate in any sleep mode where the selected source clock is running. The WDT interrupts can be used to wake up the device from sleep modes. The events can trigger other operations in the system without exiting sleep modes.

# **Related Links**

PM - Power Manager on page 192

# 24.5.3. Clocks

The WDT bus clock (CLK\_WDT\_APB) can be enabled and disabled (masked) in the Main Clock module (MCLK).

A 1KHz oscillator clock (CLK\_WDT\_OSC) is required to clock the WDT internal counter. This clock must be configured and enabled in the 32KHz Oscillator Controller (OSC32KCTRL) before using the WDT.

CLK\_WDT\_OSC is normally sourced from the clock of the internal ultra-low-power oscillator, OSCULP32K. Due to the ultra-low-power design, the oscillator is not very accurate, and so the exact time-out period may vary from device to device. This variation must be kept in mind when designing software that uses the WDT to ensure that the time-out periods used are valid for all devices.

# 25.4. Signal Description

Not applicable.

# **Related Links**

I/O Multiplexing and Considerations on page 30

# 25.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 25.5.1. I/O Lines

Not applicable.

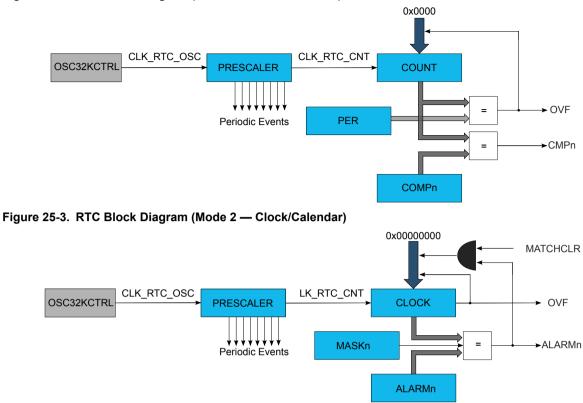

# 25.5.2. Power Management

The RTC will continue to operate in any sleep mode where the selected source clock is running. The RTC interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes. Refer to the *Power Manager* for details on the different sleep modes.

The RTC will be reset only at power-on (POR) or by setting the Software Reset bit in the Control A register (CTRLA.SWRST=1).

### **Related Links**

PM – Power Manager on page 192

Figure 25-2. RTC Block Diagram (Mode 1 — 16-Bit Counter)

refreshed when a new channel (with channel number less than the current one) with pending interrupts is detected, or when the application clears the corresponding channel interrupt sources. When no pending channels interrupts are available, these bits will always return zero value when read.

When the bits are written, indirect access to the corresponding Channel Interrupt Flag register is enabled.

### 28.8.4. Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x0CReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0 |

|--------|---|---|---|---|---|---|-------|---|

|        |   |   |   |   |   |   | ERROR |   |

| Access |   |   |   |   |   |   | R/W   |   |

| Reset  |   |   |   |   |   |   | 0     |   |

### Bit 1 – ERROR: Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the ERROR interrupt enable.

This bit will read as the current value of the ERROR interrupt enable.

# 29.8.6. Data Output Value Clear

This register allows the user to set one or more output I/O pin drive levels low, without doing a readmodify-write operation. Changes in this register will also be reflected in the Data Output Value (OUT), Data Output Value Toggle (OUTTGL) and Data Output Value Set (OUTSET) registers.

| Name:     | OUTCLR               |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

| Bit    | 31  | 30  | 29  | 28    | 27       | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|----------|-----|-----|-----|

|        |     |     |     | OUTCL | R[31:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19       | 18  | 17  | 16  |

|        |     |     |     | OUTCL | R[23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

|        |     |     |     | OUTCL | .R[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

|        |     |     |     | OUTC  | _R[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

# Bits 31:0 – OUTCLR[31:0]: PORT Data Output Value Clear

Writing '0' to a bit has no effect.

Writing '1' to a bit will clear the corresponding bit in the OUT register. Pins configured as outputs via the Data Direction register (DIR) will be set to low output drive level. Pins configured as inputs via DIR and with pull enabled via the Pull Enable bit in the Pin Configuration register (PINCFG.PULLEN) will set the input pull direction to an internal pull-down.

| Value | Description                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration.                                |

| 1     | The corresponding I/O pin output is driven low, or the input is connected to an internal pull-<br>down. |

This bit is not write-synchronized.

| Value | Description                |

|-------|----------------------------|

| 0     | Group command is disabled. |

| 1     | Group command is enabled.  |

# Bit 8 – SMEN: Smart Mode Enable

When smart mode is enabled, data is acknowledged automatically when DATA.DATA is read.

This bit is not write-synchronized.

| Value | Description             |

|-------|-------------------------|

| 0     | Smart mode is disabled. |

| 1     | Smart mode is enabled.  |

- 5. If desired, select one-shot operation by writing a '1' to the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT).

- 6. If desired, configure the counting direction 'down' (starting from the TOP value) by writing a '1' to the Counter Direction bit in the Control B register (CTRLBSET.DIR).

- 7. For capture operation, enable the individual channels to capture in the Capture Channel x Enable bit group in the Control A register (CTRLA.CAPTEN).

- 8. If desired, enable inversion of the waveform output or IO pin input signal for individual channels via the Invert Enable bit group in the Drive Control register (DRVCTRL.INVEN).

# 35.6.2.2. Enabling, Disabling, and Resetting

The TC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TC is disbled by writing a zero to CTRLA.ENABLE.

The TC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TC, except DBGCTRL, will be reset to their initial state. Refer to the CTRLA register for details.

The TC should be disabled before the TC is reset in order to avoid undefined behavior.

### 35.6.2.3. Prescaler Selection

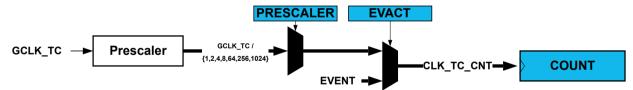

The GCLK\_TCx is fed into the internal prescaler.

The prescaler consists of a counter that counts up to the selected prescaler value, whereupon the output of the prescaler toggles.

If the prescaler value is higher than one, the counter update condition can be optionally executed on the next GCLK\_TCx clock pulse or the next prescaled clock pulse. For further details, refer to Prescaler (CTRLA.PRESCALER) and Counter Synchronization (CTRLA.PRESYNC) description.

Prescaler outputs from 1 to 1/1024 are available. For a complete list of available prescaler outputs, see the register description for the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

Note: When counting events, the prescaler is bypassed.

The joint stream of prescaler ticks and event action ticks is called CLK\_TC\_CNT.

### Figure 35-2. Prescaler

### 35.6.2.4. Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period Value and Period Buffer Value registers (PER and PERBUF).

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

- COUNT32: This mode is achieved by pairing two 16-bit TC peripherals. TC0 is paired with TC1, and TC2 is paired with TC3. TC4 does not support 32-bit resolution.

When paired, the TC peripherals are configured using the registers of the even-numbered TC (TC0 or TC2 respectively). The odd-numbered partner (TC1 or TC3 respectively) will act as slave, and the Slave bit in the Status register (STATUS.SLAVE) will be set. The register values of a slave will

### 39.5.7. Debug Operation

When the CPU is halted in debug mode the USB peripheral continues normal operation. If the USB peripheral is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

### 39.5.8. Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except the following:

- Device Interrupt Flag (INTFLAG) register

- Endpoint Interrupt Flag (EPINTFLAG) register

- Host Interrupt Flag (INTFLAG) register

- Pipe Interrupt Flag (PINTFLAG) register

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### 39.5.9. Analog Connections

Not applicable.

# 39.5.10. Calibration

The output drivers for the DP/DM USB line interface can be fine tuned with calibration values from production tests. The calibration values must be loaded from the NVM Software Calibration Area into the USB Pad Calibration register (PADCAL) by software, before enabling the USB, to achieve the specified accuracy. Refer to *NVM Software Calibration Area Mapping* for further details.

For details on Pad Calibration, refer to Pad Calibration (PADCAL) register.

### **Related Links**

NVM Software Calibration Area Mapping on page 48

# 39.6. Functional Description

### 39.6.1. USB General Operation

### 39.6.1.1. Initialization

After a hardware reset, the USB is disabled. The user should first enable the USB (CTRLA.ENABLE) in either device mode or host mode (CTRLA.MODE).

### 39.8.1.4. Finite State Machine Status

Name:FSMSTATUSOffset:0x0DReset:0xXXXXProperty:Read only

| Bit    | 7 | 6 | 5 | 4 | 3             | 2 | 1 | 0 |

|--------|---|---|---|---|---------------|---|---|---|

|        |   |   |   |   | FSMSTATE[6:0] |   |   |   |

| Access |   | R | R | R | R             | R | R | R |

| Reset  |   | 0 | 0 | 0 | 0             | 0 | 0 | 1 |

# Bits 6:0 – FSMSTATE[6:0]: Fine State Machine Status

These bits indicate the state of the finite state machine of the USB controller.

| Value  | Name         | Description                                                       |

|--------|--------------|-------------------------------------------------------------------|

| 0x01   | OFF (L3)     | Corresponds to the powered-off, disconnected, and disabled state. |

| 0x02   | ON (L0)      | Corresponds to the Idle and Active states.                        |

| 0x04   | SUSPEND (L2) |                                                                   |

| 0x08   | SLEEP (L1)   |                                                                   |

| 0x10   | DNRESUME     | Down Stream Resume.                                               |

| 0x20   | UPRESUME     | Up Stream Resume.                                                 |

| 0x40   | RESET        | USB lines Reset.                                                  |

| Others |              | Reserved                                                          |

When PFREEZE bit is set while a transaction is in progress on the USB bus, this transaction will be properly completed. PFREEZE bit will be read as "1" only when the ongoing transaction will have been completed.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The Pipe operates in normal operation.                                                         |

| 1     | The Pipe is frozen and no additional requests will be sent to the device on this pipe address. |

# Bit 2 – CURBK: Current Bank

|   | Value Description |                                                                              |

|---|-------------------|------------------------------------------------------------------------------|

| C | )                 | The bank0 is the bank that will be used in the next single/multi USB packet. |

| 1 | 1                 | The bank1 is the bank that will be used in the next single/multi USB packet. |

# Bit 0 – DTGL: Data Toggle Sequence

Writing a one to the bit EPSTATUSCLR.DTGL will clear this bit.

Writing a one to the bit EPSTATUSSET.DTGL will set this bit.

This bit is toggled automatically by hardware after a data transaction.

This bit will reflect the data toggle in regards of the token type (IN/OUT/SETUP).

| Value Description |                                                                |

|-------------------|----------------------------------------------------------------|

| 0                 | The PID of the next expected transaction will be zero: data 0. |

| 1                 | The PID of the next expected transaction will be one: data 1.  |

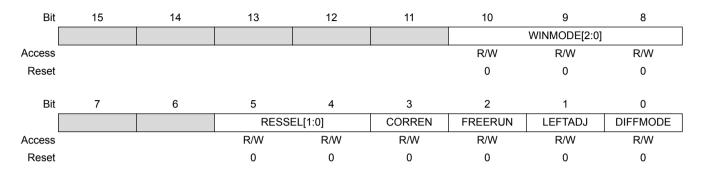

# 42.8.10. Control C

Name:CTRLCOffset:0x0AReset:0x0000Property:PAC Write-Protection, Write-Synchronized

# Bits 10:8 – WINMODE[2:0]: Window Monitor Mode

These bits enable and define the window monitor mode.

| Value     | Name    | Description              |

|-----------|---------|--------------------------|

| 0x0       | DISABLE | No window mode (default) |

| 0x1       | MODE1   | RESULT > WINLT           |

| 0x2       | MODE2   | RESULT < WINUT           |

| 0x3       | MODE3   | WINLT < RESULT < WINUT   |

| 0x4       | MODE4   | WINUT < RESULT < WINLT   |

| 0x5 - 0x7 |         | Reserved                 |

### Bits 5:4 – RESSEL[1:0]: Conversion Result Resolution

These bits define whether the ADC completes the conversion 12-, 10- or 8-bit result resolution.

| Value | Name  | Description               |

|-------|-------|---------------------------|

| 0x0   | 12BIT | 12-bit result             |

| 0x1   | 16BIT | For averaging mode output |

| 0x2   | 10BIT | 10-bit result             |

| 0x3   | 8BIT  | 8-bit result              |

### Bit 3 – CORREN: Digital Correction Logic Enabled

| Value | Description                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | Disable the digital result correction.                                                                                                                                                                                                                                                                                                       |  |  |  |

| 1     | Enable the digital result correction. The ADC conversion result in the RESULT register is then corrected for gain and offset based on the values in the GAINCORR and OFFSETCORR registers. Conversion time will be increased by 13 cycles according to the value in the Offset Correction Value bit group in the Offset Correction register. |  |  |  |

# Atmel

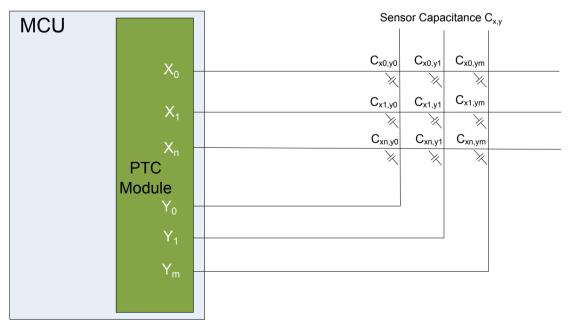

# 45.4. Signal Description

Table 45-1. Signal Description for PTC

| Name   | Туре    | Description           |

|--------|---------|-----------------------|

| Y[m:0] | Analog  | Y-line (Input/Output) |

| X[n:0] | Digital | X-line (Output)       |

Note: The number of X and Y lines are device dependent. Refer to Configuration Summary for details.

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

### **Related Links**

Configuration Summary on page 16 I/O Multiplexing and Considerations on page 30

# 45.5. Product Dependencies

In order to use this Peripheral, configure the other components of the system as described in the following sections.

# 45.5.1. I/O Lines

The I/O lines used for analog X-lines and Y-lines must be connected to external capacitive touch sensor electrodes. External components are not required for normal operation. However, to improve the EMC performance, a series resistor of  $1k\Omega$  or more can be used on X-lines and Y-lines.

### 45.5.1.1. Mutual-capacitance Sensor Arrangement

A mutual-capacitance sensor is formed between two I/O lines - an X electrode for transmitting and Y electrode for receiving. The mutual capacitance between the X and Y electrode is measured by the Peripheral Touch Controller.

### Figure 45-3. Mutual Capacitance Sensor Arrangement

# **Atmel**

| Symbol                                                                     | Description                                                                  | Conditions                      | Max.  | Max. |     |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------|-------|------|-----|

|                                                                            |                                                                              |                                 | PL0   | PL2  |     |

| fGCLK_EVSYS_CHANNEL_0                                                      | EVSYS channel 0 input clock frequency                                        | -                               | 12    | 48   | MHz |

| fGCLK_EVSYS_CHANNEL_1                                                      | EVSYS channel 1 input clock frequency -                                      |                                 |       |      |     |

| fgclk_evsys_channel_2                                                      | EVSYS channel 2 input clock frequency                                        | -                               |       |      |     |

| fgclk_evsys_channel_3                                                      | EVSYS channel 3 input clock frequency                                        | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_4                                                      | EVSYS channel 4 input clock frequency-EVSYS channel 5 input clock frequency- |                                 |       |      |     |

| fGCLK_EVSYS_CHANNEL_5                                                      |                                                                              |                                 |       |      |     |

| fGCLK_EVSYS_CHANNEL_6                                                      | EVSYS channel 6 input clock frequency                                        | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_7                                                      | EVSYS channel 7 input clock frequency                                        | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_8                                                      | EVSYS channel 8 input clock frequency                                        | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_9                                                      | EVSYS channel 9 input clock frequency                                        | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_10                                                     | EVSYS channel 10 input clock frequency                                       | -                               |       |      |     |

| fGCLK_EVSYS_CHANNEL_11                                                     | EVSYS channel 11 input clock frequency                                       | -                               |       |      |     |

| f <sub>GCLK_SERCOMx_SLOW</sub> Common SERCOM slow input clock<br>frequency |                                                                              | -                               | 1     | 5    | MHz |

| f <sub>GCLK_SERCOM0_CORE</sub>                                             | SERCOM0 input clock frequency                                                | SERCOM0 input clock frequency - |       | 48   | MHz |

| f <sub>GCLK_SERCOM1_CORE</sub>                                             | SERCOM1 input clock frequency                                                | -                               |       |      |     |

| f <sub>GCLK_SERCOM2_CORE</sub>                                             | SERCOM2 input clock frequency                                                | RCOM2 input clock frequency -   |       |      |     |

| f <sub>GCLK_SERCOM3_CORE</sub>                                             | SERCOM3 input clock frequency                                                | -                               |       |      |     |

| f <sub>GCLK_SERCOM4_CORE</sub>                                             | SERCOM4 input clock frequency -                                              |                                 |       |      |     |

| f <sub>GCLK_SERCOM5_CORE</sub>                                             | SERCOM5 input clock frequency                                                | -                               |       |      |     |

| fGCLK_TCC0, GCLK_TCC1                                                      | TCC0,TCC1 input clock frequency                                              | -                               | 24    | 96   | MHz |

| fGCLK_TCC2, GCLK_TC0                                                       | TCC2,TC0 input clock frequency                                               | -                               | 12    | 48   | MHz |

| fGCLK_TC1, GCLK_TC2                                                        | TC1,TC2 input clock frequency -                                              |                                 |       |      |     |

| fGCLK_TC3, GCLK_TC4                                                        | TC3,TC4 input clock frequency                                                | -                               |       |      |     |

| f <sub>GCLK_ADC</sub>                                                      | ADC input clock frequency                                                    | -                               | 12 48 |      | MHz |

| f <sub>GCLK_AC</sub>                                                       | AC digital input clock frequency                                             | -                               |       |      |     |

| f <sub>GCLK_DAC</sub>                                                      | DAC input clock frequency                                                    | -                               |       |      |     |

| f <sub>GCLK_PTC</sub>                                                      | PTC input clock frequency                                                    | -                               |       |      |     |

| f <sub>GCLK_CCL</sub>                                                      | CCL input clock frequency                                                    | -                               |       |      |     |

# Note:

1. These values are based on simulation. They are not covered by production test limits or characterization.

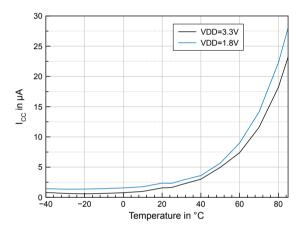

# 47. Typical Characteristics

# 47.1. Power Consumption over Temperature in Sleep Modes

### **Power Consumption in Standby Sleep Mode with RTC** Operating conditions:

• VDDIN = 3.3V or 1.8V

- ULPVERG LPEFF Enable

- RTC running on external 32KHz crystal

- PD0, PD1, PD2 in retention state

- BOD33 is disabled

### Figure 47-1. Power Consumption over Temperature in STANDBY Sleep Mode with RTC

# **Power Consumption in BACKUP Sleep Mode with RTC** Operating conditions:

VDDIN =0V

- VBAT = 3.3V or 1.8V

- RTC running on external 32KHz crystal

- BOD33 is disabled

# 49.6.4. Calculating the Correct Crystal Decoupling Capacitor

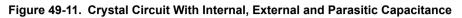

The model shown in Figure 49-11 can be used to calculate correct load capacitor for a given crystal. This model includes internal capacitors  $C_{Ln}$ , external parasitic capacitance  $C_{ELn}$  and external load capacitance  $C_{Pn}$ .

Using this model the total capacitive load for the crystal can be calculated as shown in the equation below:

$$\sum C_{\text{tot}} = \frac{(C_{L1} + C_{P1} + C_{\text{EL1}})(C_{L2} + C_{P2} + C_{\text{EL2}})}{C_{L1} + C_{P1} + C_{\text{EL1}} + C_{L2} + C_{P2} + C_{\text{EL2}}}$$

where C<sub>tot</sub> is the total load capacitance seen by the crystal. This value should be equal to the load capacitance value found in the crystal manufacturer datasheet.

The parasitic capacitance  $C_{ELn}$  can in most applications be disregarded as these are usually very small. If accounted for, these values are dependent on the PCB material and PCB layout.

For some crystal the internal capacitive load provided by the device itself can be enough. To calculate the total load capacitance in this case.  $C_{ELn}$  and  $C_{Pn}$  are both zero,  $C_{L1} = C_{L2} = C_L$ , and the equation reduces to the following:

$$\sum C_{\rm tot} = \frac{C_L}{2}$$

See the related links for equivalent internal pin capacitance values.

### **Related Links**

External 32KHz Crystal Oscillator (XOSC32K) Characteristics on page 1177

# 49.7. Programming and Debug Ports

For programming and/or debugging the SAM L21, the device should be connected using the Serial Wire Debug, SWD, interface. Currently the SWD interface is supported by several Atmel and third party programmers and debuggers, like the Atmel-ICE, SAM-ICE, JTAGICE3 or SAM L21 Xplained Pro (SAM L21 evaluation kit) Embedded Debugger.