#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 37                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21g17b-aut |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 12-7. Low-Power Bus Matrix Slaves

| Low-Power Bus Matrix Slaves                                       | Slave ID |

|-------------------------------------------------------------------|----------|

| AHB-APB Bridge A                                                  | 0        |

| AHB-APB Bridge C                                                  | 1        |

| AHB-APB Bridge D                                                  | 2        |

| AHB-APB Bridge E                                                  | 3        |

| LP SRAM Port 2- H2LBRIDGEM access                                 | 5        |

| LP SRAM Port 1- DMAC access                                       | 7        |

| L2HBRIDGES - Low-Power to High-Speed bus matrix AHB to AHB bridge | 8        |

| HS SRAM Port 2- HMATRIXLP access                                  | 9        |

#### 12.4.3. SRAM Quality of Service

To ensure that masters with latency requirements get sufficient priority when accessing RAM, priority levels can be assigned to the masters for different types of access.

The Quality of Service (QoS) level is independently selected for each master accessing the RAM. For any access to the RAM, the RAM also receives the QoS level. The QoS levels and their corresponding bit values for the QoS level configuration are shown in the following table.

| Value | Name    | Description                         |

|-------|---------|-------------------------------------|

| 0x0   | DISABLE | Background (no sensitive operation) |

| 0x1   | LOW     | Sensitive Bandwidth                 |

| 0x2   | MEDIUM  | Sensitive Latency                   |

| 0x3   | HIGH    | Critical Latency                    |

#### Table 12-8. Quality of Service

If a master is configured with QoS level DISABLE (0x0) or LOW (0x1) there will be a minimum latency of one cycle for the RAM access.

The priority order for concurrent accesses are decided by two factors. First, the QoS level for the master and second, a static priority given by the port ID. The lowest port ID has the highest static priority. See the tables below for details.

The MTB has a fixed QoS level HIGH (0x3).

The CPU QoS level can be written/read, using 32-bit access only, at address 0x41008114 bits [1:0]. Its reset value is 0x3.

Refer to different master QOSCTRL registers for configuring QoS for the other masters (USB, DMAC).

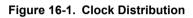

# 16. Clock System

This chapter summarizes the clock distribution and terminology in the SAM L21 device. It will not explain every detail of its configuration. For in-depth documentation, see the respective peripherals descriptions and the *Generic Clock* documentation.

#### **Related Links**

GCLK - Generic Clock Controller on page 133 MCLK – Main Clock on page 154

# 16.1. Clock Distribution

The SAM L21 clock system consists of:

- Clock sources, controlled by OSCCTRL and OSC32KCTRL

- A clock source provides a time base that is used by other components, such as Generic Clock Generators. Example clock sources are the internal 16MHz oscillator (OSC16M), external crystal oscillator (XOSC) and the Digital Frequency Locked Loop (DFLL48M).

- *Generic Clock Controller (GCLK),* which generates, controls and distributes the asynchronous clock consisting of:

- *Generic Clock Generators:* These are programmable prescalers that can use any of the system clock sources as a time base. The Generic Clock Generator 0 generates the clock

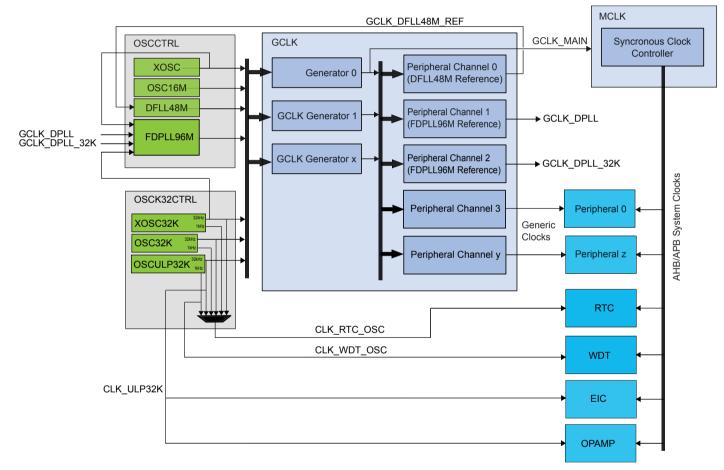

# 18. MCLK – Main Clock

# 18.1. Overview

The Main Clock (MCLK) controls the synchronous clock generation of the device.

Using a clock provided by the Generic Clock Module (GCLK\_MAIN), the Main Clock Controller provides synchronous system clocks to the CPU and the modules connected to the AHBx and the APBx bus. The synchronous system clocks are divided into a number of clock domains. Each clock domain can run at different frequencies, enabling the user to save power by running peripherals at a relatively low clock frequency, while maintaining high CPU performance or vice versa. In addition, the clock can be masked for individual modules, enabling the user to minimize power consumption.

# 18.2. Features

- Generates CPU, AHB, and APB system clocks

- Clock source and division factor from GCLK

- Clock prescaler with 1x to 128x division

- Safe run-time clock switching from GCLK

- Module-level clock gating through maskable peripheral clocks

# 18.3. Block Diagram

Figure 18-1. MCLK Block Diagram

# 18.4. Signal Description

Not applicable.

# 18.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 18.5.1. I/O Lines

Not applicable.

# 19.7. Register Summary

| Offset | Name     | Bit Pos. |        |      |     |       |          |             |       |         |

|--------|----------|----------|--------|------|-----|-------|----------|-------------|-------|---------|

| 0x00   | RCAUSE   | 7:0      | BACKUP | SYST | WDT | EXT   |          | BOD33       | BOD12 | POR     |

| 0x01   | Reserved |          |        |      |     |       |          |             |       |         |

| 0x02   | BKUPEXIT | 7:0      |        |      |     |       |          | BBPS        | RTC   | EXTWAKE |

| 0x03   | Reserved |          |        |      |     |       |          |             |       |         |

| 0x04   | WKDBCONF | 7:0      |        |      |     |       |          | WKDBCNT[4:0 | ]     |         |

| 0x05   |          |          |        |      |     |       |          |             |       |         |

|        | Reserved |          |        |      |     |       |          |             |       |         |

| 0x07   |          |          |        |      |     |       |          |             |       |         |

| 0x08   | WKPOL    | 7:0      |        |      |     | WKPC  | DL[7:0]  |             |       |         |

| 0x09   | VICFOL   | 15:8     |        |      |     |       |          |             |       |         |

| 0x0A   |          |          |        |      |     |       |          |             |       |         |

|        | Reserved |          |        |      |     |       |          |             |       |         |

| 0x0B   |          |          |        |      |     |       |          |             |       |         |

| 0x0C   | WKEN     | 7:0      |        |      |     | WKE   | N[7:0]   |             |       |         |

| 0x0D   | VICEN    | 15:8     |        |      |     |       |          |             |       |         |

| 0x0E   |          |          |        |      |     |       |          |             |       |         |

|        | Reserved |          |        |      |     |       |          |             |       |         |

| 0x0F   |          |          |        |      |     |       |          |             |       |         |

| 0x10   | WKCAUSE  | 7:0      |        |      |     | WKCAL | JSE[7:0] |             |       |         |

| 0x11   | WINCAUSE | 15:8     |        |      |     |       |          |             |       |         |

# 19.8. Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

#### 20.8.6. Interrupt Flag Status and Clear

|        | Name:<br>Offset:<br>Reset:<br>Property | 0x0<br>0x0 |   |   |   |   |   |   |       |

|--------|----------------------------------------|------------|---|---|---|---|---|---|-------|

| Bit    | 7                                      |            | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|        |                                        |            |   |   |   |   |   |   | PLRDY |

| Access |                                        |            |   |   |   |   |   |   | R/W   |

| Reset  |                                        |            |   |   |   |   |   |   | 0     |

#### Bit 0 – PLRDY: Performance Level Ready

This flag is set when the performance level is ready and will generate an interrupt if INTENCLR/ SET.PLRDY is '1'.

Writing a '1' to this bit has no effect.

Writing a '1' to this bit clears the Performance Ready interrupt flag.

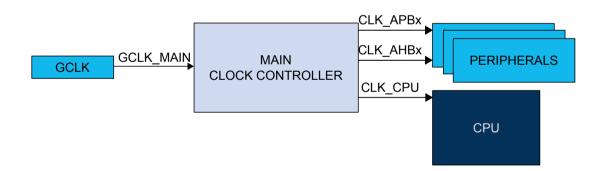

#### 21.8.12. DPLL Ratio Control

Name:DPLLRATIOOffset:0x2CReset:0x00Property:PAC Write-Protection, Write-Synchronized

#### Bits 19:16 – LDRFRAC[3:0]: Loop Divider Ratio Fractional Part

Writing these bits selects the fractional part of the frequency multiplier. Due to synchronization there is a delay between writing these bits and the effect on the DPLL output clock. The value written will read back immediately and the DPLLRATIO bit in the DPLL Synchronization Busy register (DPLLSYNCBUSY.DPLLRATIO) will be set. DPLLSYNCBUSY.DPLLRATIO will be cleared when the operation is completed.

#### Bits 11:0 – LDR[11:0]: Loop Divider Ratio

Writing these bits selects the integer part of the frequency multiplier. The value written to these bits will read back immediately, and the DPLLRATIO bit in the DPLL Synchronization busy register (DPLLSYNCBUSY.DPLLRATIO), will be set. DPLLSYNCBUSY.DPLLRATIO will be cleared when the operation is completed.

#### 25.5.3. Clocks

The RTC bus clock (CLK\_RTC\_APB) can be enabled and disabled in the Main Clock module MCLK, and the default state of CLK\_RTC\_APB can be found in Peripheral Clock Masking section.

A 32KHz or 1KHz oscillator clock (CLK\_RTC\_OSC) is required to clock the RTC. This clock must be configured and enabled in the 32KHz oscillator controller (OSC32KCTRL) before using the RTC.

This oscillator clock is asynchronous to the bus clock (CLK\_RTC\_APB). Due to this asynchronicity, writing to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

OSC32KCTRL – 32KHz Oscillators Controller on page 273 Peripheral Clock Masking on page 157

#### 25.5.4. DMA

Not applicable.

#### **Related Links**

DMAC - Direct Memory Access Controller on page 406

#### 25.5.5. Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the RTC interrupt requires the Interrupt Controller to be configured first.

#### **Related Links**

Nested Vector Interrupt Controller on page 52

#### 25.5.6. Events

The events are connected to the Event System.

#### **Related Links**

EVSYS - Event System on page 544

#### 25.5.7. Debug Operation

When the CPU is halted in debug mode the RTC will halt normal operation. The RTC can be forced to continue operation during debugging. Refer to DBGCTRL for details.

#### 25.5.8. Register Access Protection

All registers with write-access are optionally write-protected by the peripheral access controller (PAC), except the following registers:

- Interrupt Flag Status and Clear (INTFLAG) register

- General Purpose (GPx) registers

Write-protection is denoted by the "PAC Write-Protection" property in the register description.

Write-protection does not apply to accesses through an external debugger. Refer to the PAC - Peripheral Access Controller for details.

#### **Related Links**

PAC - Peripheral Access Controller on page 59

#### 25.8.3. Interrupt Enable Clear in COUNT32 mode (CTRLA.MODE=0)

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

Name: INTENCLR Offset: 0x08 Reset: 0x0000 Property: PAC Write-Protection

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|--------|------|------|------|------|------|------|------|------|

|        | OVF  |      |      |      |      |      |      | CMP0 |

| Access | R/W  |      |      |      |      |      |      | R/W  |

| Reset  | 0    |      |      |      |      |      |      | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | PER7 | PER6 | PER5 | PER4 | PER3 | PER2 | PER1 | PER0 |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Bit 15 – OVF: Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### Bit 8 – CMP0: Compare 0 Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Compare 0 Interrupt Enable bit, which disables the Compare interrupt.

| Value | Description                          |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|

| 0     | The Compare 0 interrupt is disabled. |  |  |  |  |

| 1     | The Compare 0 interrupt is enabled.  |  |  |  |  |

#### Bits 7:0 – PERn: Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Periodic Interval n Interrupt Enable bit, which disables the Periodic Interval n interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

# 26. DMAC – Direct Memory Access Controller

# 26.1. Overview

The Direct Memory Access Controller (DMAC) contains both a Direct Memory Access engine and a Cyclic Redundancy Check (CRC) engine. The DMAC can transfer data between memories and peripherals, and thus off-load these tasks from the CPU. It enables high data transfer rates with minimum CPU intervention, and frees up CPU time. With access to all peripherals, the DMAC can handle automatic transfer of data between communication modules.

The DMA part of the DMAC has several DMA channels which all can receive different types of transfer triggers to generate transfer requests from the DMA channels to the arbiter, see also the Block Diagram. The arbiter will grant one DMA channel at a time to act as the active channel. When an active channel has been granted, the fetch engine of the DMAC will fetch a transfer descriptor from the low-power (LP) SRAM and store it in the internal memory of the active channel, which will execute the data transmission.

An ongoing data transfer of an active channel can be interrupted by a higher prioritized DMA channel. The DMAC will write back the updated transfer descriptor from the internal memory of the active channel to LP SRAM, and grant the higher prioritized channel to start transfer as the new active channel. Once a DMA channel is done with its transfer, interrupts and events can be generated optionally.

The DMAC has four bus interfaces:

- The data transfer bus is used for performing the actual DMA transfer.

- The AHB/APB Bridge bus is used when writing and reading the I/O registers of the DMAC.

- The *descriptor fetch bus* is used by the fetch engine to fetch transfer descriptors before data transfer can be started or continued.

- The write-back bus is used to write the transfer descriptor back to LP SRAM.

All buses are AHB master interfaces but the AHB/APB Bridge bus, which is an APB slave interface.

The CRC engine can be used by software to detect an accidental error in the transferred data and to take corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

# 26.2. Features

- Data transfer from:

- Peripheral to peripheral

- Peripheral to memory

- Memory to peripheral

- Memory to memory

- Transfer trigger sources

- Software

- Events from Event System

- Dedicated requests from peripherals

- SRAM based transfer descriptors

- Single transfer using one descriptor

- Multi-buffer or circular buffer modes by linking multiple descriptors

- Up to 16channels

#### 26.8.21. Channel Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Channel Interrupt Enable Clear (CHINTENCLR) register. This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

Name:CHINTENSETOffset:0x4DReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0    |

|--------|---|---|---|---|---|------|-------|------|

|        |   |   |   |   |   | SUSP | TCMPL | TERR |

| Access |   |   |   |   |   | R/W  | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0    | 0     | 0    |

#### Bit 2 – SUSP: Channel Suspend Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Suspend Interrupt Enable bit, which enables the Channel Suspend interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Channel Suspend interrupt is disabled. |

| 1     | The Channel Suspend interrupt is enabled.  |

#### Bit 1 – TCMPL: Channel Transfer Complete Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Complete Interrupt Enable bit, which enables the Channel Transfer Complete interrupt.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The Channel Transfer Complete interrupt is disabled. |

| 1     | The Channel Transfer Complete interrupt is enabled.  |

#### Bit 0 – TERR: Channel Transfer Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Channel Transfer Error Interrupt Enable bit, which enables the Channel Transfer Error interrupt.

| Value | Description                                       |  |  |  |  |

|-------|---------------------------------------------------|--|--|--|--|

| 0     | The Channel Transfer Error interrupt is disabled. |  |  |  |  |

| 1     | The Channel Transfer Error interrupt is enabled.  |  |  |  |  |

#### 27.8.4. Synchronization Busy

Name: SYNCBUSY Offset: 0x04 **Reset:** 0x00000000 Property: -Bit 31 30 29 28 27 26 25 24 Access Reset 23 22 21 19 Bit 20 18 17 16 Access Reset Bit 15 14 13 12 11 10 9 8 Access Reset 2 Bit 7 6 5 3 1 0 4 SWRST ENABLE R Access R Reset 0 0

#### Bit 1 – ENABLE: Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

#### Bit 0 – SWRST: Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

| Value | Name          | Description                                                                                                                                                                                                                                        |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x2   | DETERMINISTIC | The cache system ensures that a cache hit or miss takes the same<br>amount of time, determined by the number of programmed Flash wait<br>states. This mode can be used for real-time applications that require<br>deterministic execution timings. |

| 0x3   | Reserved      |                                                                                                                                                                                                                                                    |

#### Bits 9:8 – SLEEPPRM[1:0]: Power Reduction Mode during Sleep

Indicates the Power Reduction Mode during sleep.

| Value | Name          | Description                                                                                                |

|-------|---------------|------------------------------------------------------------------------------------------------------------|

| 0x0   | WAKEUPACCESS  | NVM block enters low-power mode when entering sleep.<br>NVM block exits low-power mode upon first access.  |

| 0x1   | WAKEUPINSTANT | NVM block enters low-power mode when entering sleep.<br>NVM block exits low-power mode when exiting sleep. |

| 0x2   | Reserved      |                                                                                                            |

| 0x3   | DISABLED      | Auto power reduction disabled.                                                                             |

# Bit 7 – MANW: Manual Write

Note that reset value of this bit is '1'.

| Value | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Writing to the last word in the page buffer will initiate a write operation to the page addressed by the last write operation. This includes writes to memory and auxiliary rows. |

| 1     | Write commands must be issued through the CTRLA.CMD register.                                                                                                                     |

#### Bits 4:1 – RWS[3:0]: NVM Read Wait States

These bits control the number of wait states for a read operation. '0' indicates zero wait states, '1' indicates one wait state, etc., up to 15 wait states.

This register is initialized to 0 wait states. Software can change this value based on the NVM access time and system frequency.

# 28.8.8. Address

Name:ADDROffset:0x1CReset:0x00000000Property:PAC Write-Protection

| Bit    | 31        | 30  | 29  | 28   | 27     | 26      | 25  | 24  |

|--------|-----------|-----|-----|------|--------|---------|-----|-----|

|        |           |     |     |      |        |         |     |     |

| Access |           |     |     |      |        |         |     |     |

| Reset  |           |     |     |      |        |         |     |     |

|        |           |     |     |      |        |         |     |     |

| Bit    | 23        | 22  | 21  | 20   | 19     | 18      | 17  | 16  |

|        |           |     |     |      | ADDR   | [21:16] |     |     |

| Access | <b>L</b>  | •   | R/W | R/W  | R/W    | R/W     | R/W | R/W |

| Reset  |           |     | 0   | 0    | 0      | 0       | 0   | 0   |

|        |           |     |     |      |        |         |     |     |

| Bit    | 15        | 14  | 13  | 12   | 11     | 10      | 9   | 8   |

|        |           |     |     | ADDF | [15:8] |         |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W    | R/W     | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0      | 0       | 0   | 0   |

|        |           |     |     |      |        |         |     |     |

| Bit    | 7         | 6   | 5   | 4    | 3      | 2       | 1   | 0   |

|        | ADDR[7:0] |     |     |      |        |         |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W    | R/W     | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0      | 0       | 0   | 0   |

|        |           |     |     |      |        |         |     |     |

# Bits 21:0 - ADDR[21:0]: NVM Address

ADDR drives the hardware (16-bit) address to the NVM when a command is executed using CMDEX. This register is also automatically updated when writing to the page buffer.

| Value | Name  | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0x2   | DITH5 | Dithering is done every 32 PWM frames.                     |

|       |       | PER[4:0] and CCx[4:0] contain dithering pattern selection. |

| 0x3   | DITH6 | Dithering is done every 64 PWM frames.                     |

|       |       | PER[5:0] and CCx[5:0] contain dithering pattern selection. |

#### Bit 1 – ENABLE: Enable

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the ENABLE bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TCC (except DBGCTRL) to their initial state, and the TCC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# Bits 24, 25, 26, 27 – CPTEN0, CPTEN1, CPTEN2, CPTEN3: Capture Channel x Enable

These bits are used to select the capture or compare operation on channel x.

Writing a '1' to CPTENx enables capture on channel x.

Writing a '0' to CPTENx disables capture on channel x.

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 38.6.2.2. Enabling, Disabling, and Resetting

The AES module is enabled by writing a one to the Enable bit in the Control A register (CTRLA.ENABLE). The module is disabled by writing a zero to CTRLA.ENABLE. The module is reset by writing a one to the Software Reset bit in the Control A register (CTRLA.SWRST).

#### 38.6.2.3. Basic Programming

The CIPHER bit in the Control A Register (CTRLA.CIPHER) allows selection between the encryption and the decryption processes. The AES is capable of using cryptographic keys of 128/192/256 bits to encrypt and decrypt data in blocks of 128 bits. The Key Size (128/192/256) can be programmed in the KEYSIZE field in the Control A Register (CTRLA.KEYSIZE). This 128-bit/192-bit/256-bit key is defined in the Key Word Registers (KEYWORDx). By setting the XORKEY bit of CTRLA register, keyword can be updated with the resulting XOR value of user keyword and previous keyword content.

The input data for processing is written to a data buffer consisting of four 32-bit registers through the Data register address. The data buffer register (note that input and output data shares the same data buffer register) that is written to when the next write is performed is indicated by the Data Pointer in the Data Buffer Pointer (DATABUFPTR) register. This field is incremented by one or wrapped by hardware when a write to the DATA register address is performed. This field can also be programmed, allowing the user direct control over which input buffer register to write to. Note that when AES module is in the CFB operation mode with the data segment size less than 128 bits, the input data must be written to the first (DATABUFPTR = 0) and/or second (DATABUFPTR = 1) input buffer registers (see Table 38-1).

The input to the encryption processes of the CBC, CFB and OFB modes includes, in addition to the plaintext, a 128-bit data block called the Initialization Vector (IV), which must be set in the Initialization Vector Registers (INTVECTx). Additionally, the GCM mode 128-bit authentication data needs to be programmed. The Initialization Vector is used in the initial step in the encryption of a message and in the corresponding decryption of the message. The Initialization Vector Registers are also used by the Counter mode to set the counter value.

It is necessary to notify AES module whenever the next data block it is going to process is the beginning of a new message. This is done by writing a one to the New Message bit in the Control B register (CTRLB.NEWMSG).

The AES modes of operation are selected by setting the AESMODE field in the Control A Register (CTRLA.AESMODE). In Cipher Feedback Mode (CFB), five data sizes are possible (8, 16, 32, 64 or 128 bits), configurable by means of the CFBS field in the Control A Register (CTRLA.CFBS). In Counter mode, the size of the block counter embedded in the module is 16 bits. Therefore, there is a rollover after processing 1 megabyte of data. The data pre-processing, post-processing and data chaining for the concerned modes are automatically performed by the module.

When data processing has completed, the Encryption Complete bit in the Interrupt Flag register (INTFLAG.ENCCMP) is set by hardware (which triggers an interrupt request if the corresponding interrupt is enabled). The processed output data is read out through the Output Data register (DATA) address from the data buffer consisting of four 32-bit registers. The data buffer register that is read from when the next read is performed is indicated by the Data Pointer field in the Data Buffer Pointer register (DATABUFPTR). This field is incremented by one or wrapped by hardware when a read from the DATA register address is performed. This field can also be programmed, giving the user direct control over which output buffer register to read from. Note that when AES module is in the CFB operation mode with the data segment size less than 128 bits, the output data must be read from the first (DATABUFPTR = 0) and/or second (DATABUFPTR = 1) output buffer registers (see see Table 38-1). The Encryption Complete bit (INTFLAG.ENCCMP) is cleared by hardware after the processed data has been read from the relevant output buffer registers.

Name:DATAOffset:0X38Reset:0x00000000Property:PAC Write-Protection

| Bit    | 31          | 30  | 29  | 28    | 27     | 26  | 25  | 24  |

|--------|-------------|-----|-----|-------|--------|-----|-----|-----|

|        | DATA[31:24] |     |     |       |        |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |             |     |     |       |        |     |     |     |

| Bit    | 23          | 22  | 21  | 20    | 19     | 18  | 17  | 16  |

|        |             |     |     | DATA[ | 23:16] |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |             |     |     |       |        |     |     |     |

| Bit    | 15          | 14  | 13  | 12    | 11     | 10  | 9   | 8   |

|        | DATA[15:8]  |     |     |       |        |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |             |     |     |       |        |     |     |     |

| Bit    | 7           | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

|        | DATA[7:0]   |     |     |       |        |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |             |     |     |       |        |     |     |     |

#### Bits 31:0 - DATA[31:0]: Data Value

A write to or read from this register corresponds to a write to or read from one of the four data registers. The four 32-bit Data registers set the 128-bit data block used for encryption/decryption. The data register that is written to or read from is given by the DATABUFPTR.DATPTR field.

**Note:** Both input and output shares the same data buffer. Reading DATA register will return 0's when AES is performing encryption or decryption operation.

#### Bit 2 – SOF: Start-of-Frame Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Start-of-Frame interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Start-of-Frame interrupt is disabled.                                                                                         |

| 1     | The Start-of-Frame interrupt is enabled and an interrupt request will be generated when the Start-of-Frame interrupt Flag is set. |

#### Bit 0 – SUSPEND: Suspend Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Suspend Interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| 0     | The Suspend interrupt is disabled.                                                                                  |

| 1     | The Suspend interrupt is enabled and an interrupt request will be generated when the Suspend interrupt Flag is set. |

# Bits 3:2 – SPDCONF[1:0]: Speed Configuration for Host

These bits select the host speed configuration as shown below

| Value | Description                |

|-------|----------------------------|

| 0x0   | Low and Full Speed capable |

| 0x1   | Reserved                   |

| 0x2   | Reserved                   |

| 0x3   | Reserved                   |

# Bit 1 – RESUME: Send USB Resume

Writing 0 to this bit has no effect.

1: Generates a USB Resume on the USB bus.

This bit is cleared when the USB Resume has been sent or when a USB reset is requested.

#### 41.8.3. OPAMP Control x

Name:

OPAMPCTRLx

Offset:

0x04+4\*x, [x=0..2]

Reset:

0x0000080

Property:

PAC

Write-Protection

| Bit    | 31       | 30          | 29  | 28        | 27       | 26     | 25          | 24      |

|--------|----------|-------------|-----|-----------|----------|--------|-------------|---------|

|        |          |             |     |           |          |        |             |         |

| Access |          |             |     |           |          |        |             |         |

| Reset  |          |             |     |           |          |        |             |         |

|        |          |             |     |           |          |        |             |         |

| Bit    | 23       | 22          | 21  | 20        | 19       | 18     | 17          | 16      |

|        |          | MUXNEG[2:0] |     |           |          |        | MUXPOS[2:0] |         |

| Access |          | R/W         | R/W | R/W       |          | R/W    | R/W         | R/W     |

| Reset  |          | 0           | 0   | 0         |          | 0      | 0           | 0       |

|        |          |             |     |           |          |        |             |         |

| Bit    | 15       | 14          | 13  | 12        | 11       | 10     | 9           | 8       |

|        |          | POTMUX[2:0] |     | RES1M     | IUX[1:0] | RES1EN | RES2VCC     | RES2OUT |

| Access | R/W      | R/W         | R/W | R/W       | R/W      | R/W    | R/W         | R/W     |

| Reset  | 0        | 0           | 0   | 0         | 0        | 0      | 0           | 0       |

|        |          |             |     |           |          |        |             |         |

| Bit    | 7        | 6           | 5   | 4         | 3        | 2      | 1           | 0       |

|        | ONDEMAND | RUNSTDBY    |     | BIAS[1:0] |          | ANAOUT | ENABLE      |         |

| Access | R/W      | R/W         |     | R/W       | R/W      | R/W    | R/W         |         |

| Reset  | 0        | 0           |     | 0         | 0        | 0      | 0           |         |

# Bits 22:20 – MUXNEG[2:0]: Negative Input Mux Selection

Selection on negative input for operational amplifier x.

| Value | OPAMPx  | Name     | Description            |  |  |

|-------|---------|----------|------------------------|--|--|

| 0x0   | x=0,1,2 | OAxNEG   | Negative I/O pin       |  |  |

| 0x1   | x=0,1,2 | OAxTAP   | Resistor ladder x taps |  |  |

| 0x2   | x=0,1,2 | OAxOUT   | OPAMPx output          |  |  |

| 0x3   | x=0,1   | DAC      | DAC output             |  |  |

|       | x=2     | OA0NEG   | Negative I/O pin OPA0  |  |  |

| 0x4   | x=0,1   | Reserved |                        |  |  |

|       | x=2     | OA1NEG   | Negative I/O pin OPA1  |  |  |

| 0x5   | x=0,1   | Reserved |                        |  |  |

|       | x=2     | DAC      | DAC output             |  |  |

| 0x6   | x=0,1,2 | Reserved |                        |  |  |

| 0x7   | x=0,1,2 | Reserved |                        |  |  |

www.atmel.com

# Atmel Enabling Unlimited Possibilities

Atmel Corporation

1600 Technology Drive, San Jose, CA 95110 USA

**T:** (+1)(408) 441.0311

F: (+1)(408) 436.4200

f 🔰 in 8 🖸 W

© 2016 Atmel Corporation. / Rev.: Atmel-42385J-SAM L21 Datasheet Complete-06/2016

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM<sup>®</sup>, ARM Connected<sup>®</sup> logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as military-grade.