#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9×9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21j17b-mnt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 13.7.4. Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENCLR).

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------|---|---|---|---|---|---|---|-----|

|        |   |   |   |   |   |   |   | ERR |

| Access |   |   |   |   |   |   |   | R/W |

| Reset  |   |   |   |   |   |   |   | 0   |

#### Bit 0 – ERR: Peripheral Access Error Interrupt Enable

This bit indicates that the Peripheral Access Error Interrupt is enabled and an interrupt request will be generated when one of the interrupt flag registers bits (INTFLAGAHB, INTFLAGn) is set:

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Peripheral Access Error interrupt Enable bit and enables the corresponding interrupt request.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Peripheral Access Error interrupt is disabled. |

| 1     | Peripheral Access Error interrupt is enabled.  |

# 22. OSC32KCTRL – 32KHz Oscillators Controller

# 22.1. Overview

The 32KHz Oscillators Controller (OSC32KCTRL) provides a user interface to the 32.768kHz oscillators: XOSC32K, OSC32K, and OSCULP32K.

The OSC32KCTRL sub-peripherals can be enabled, disabled, calibrated, and monitored through interface registers.

All sub-peripheral statuses are collected in the Status register (STATUS). They can additionally trigger interrupts upon status changes via the INTENSET, INTENCLR, and INTFLAG registers.

# 22.2. Features

- 32.768kHz Crystal Oscillator (XOSC32K)

- Programmable start-up time

- Crystal or external input clock on XIN32 I/O

- 32.768kHz High Accuracy Internal Oscillator (OSC32K)

- Frequency fine tuning

- Programmable start-up time

- 32.768kHz Ultra Low Power Internal Oscillator (OSCULP32K)

- Ultra low power, always-on oscillator

- Frequency fine tuning

- Calibration value loaded from Flash factory calibration at reset

- 1.024kHz clock outputs available

# 23. SUPC – Supply Controller

# 23.1. Overview

The Supply Controller (SUPC) manages the voltage reference, power supply, and supply monitoring of the device. It is also able to control two output pins.

The SUPC controls the voltage regulators for the core (VDDCORE) and backup (VDDBU) domains. It sets the voltage regulators according to the sleep modes, or the user configuration. In active mode, the voltage regulators can be selected on the fly between LDO (low-dropout) type regulator or Buck converter.

The SUPC supports connection of a battery backup to the VBAT power pin. It includes functionality that enables automatic power switching between main power and battery backup power. This ensures power to the backup domain when the main battery or power source is unavailable.

The SUPC embeds two Brown-Out Detectors. BOD33 monitors the voltage applied to the device (VDD or VBAT) and BOD12 monitors the internal voltage to the core (VDDCORE). The BOD can monitor the supply voltage continuously (continuous mode) or periodically (sampling mode).

The SUPC generates also a selectable reference voltage and a voltage dependent on the temperature which can be used by analog modules like the ADC or DAC.

# 23.2. Features

- Voltage Regulator System

- Main voltage regulator: LDO or Buck Converter in active mode (MAINVREG)

- Low Power voltage regulator in standby mode (LPVREG)

- Backup voltage regulator for backup domains

- Controlled VDDCORE voltage slope when changing VDDCORE

- Battery Backup Power Switch

- Automatic switching from main power to battery backup power

- · Automatic entry to backup mode when switched to battery backup power

- Automatic switching from battery backup power to main power

- · Automatic exit from backup mode when switched back to main power

- Stay in backup mode when switched back to main power

- Main power request upon wake-up sources from backup mode

- Voltage Reference System

- Reference voltage for ADC and DAC

- Temperature sensor

- 3.3V Brown-Out Detector (BOD33)

- Programmable threshold

- Threshold value loaded from NVM User Row at startup

- Triggers resets, interrupts, or Battery Backup Power Switch. Action loaded from NVM User Row

- Operating modes:

- Continuous mode

#### Table 24-1. WDT Operating Modes

| CTRLA.ENABLE | CTRLA.WEN | Interrupt Enable | Mode                                     |

|--------------|-----------|------------------|------------------------------------------|

| 0            | x         | x                | Stopped                                  |

| 1            | 0         | 0                | Normal mode                              |

| 1            | 0         | 1                | Normal mode with Early Warning interrupt |

| 1            | 1         | 0                | Window mode                              |

| 1            | 1         | 1                | Window mode with Early Warning interrupt |

#### 24.6.2. Basic Operation

#### 24.6.2.1. Initialization

The following bits are enable-protected, meaning that they can only be written when the WDT is disabled (CTRLA.ENABLE=0):

- Control A register (CTRLA), except the Enable bit (CTRLA.ENABLE)

- Configuration register (CONFIG)

- Early Warning Interrupt Control register (EWCTRL)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'.

The WDT can be configured only while the WDT is disabled. The WDT is configured by defining the required Time-Out Period bits in the Configuration register (CONFIG.PER). If Window mode operation is desired, the Window Enable bit in the Control A register must be set (CTRLA.WEN=1) and the Window Period bits in the Configuration register (CONFIG.WINDOW) must be defined.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

#### 24.6.2.2. Configurable Reset Values

After a Power-on Reset, some registers will be loaded with initial values from the NVM User Row.

This includes the following bits and bit groups:

- Enable bit in the Control A register, CTRLA.ENABLE

- Always-On bit in the Control A register, CTRLA.ALWAYSON

- Watchdog Timer Windows Mode Enable bit in the Control A register, CTRLA.WEN

- Watchdog Timer Windows Mode Time-Out Period bits in the Configuration register, CONFIG.WINDOW

- Time-Out Period bits in the Configuration register, CONFIG.PER

- Early Warning Interrupt Time Offset bits in the Early Warning Interrupt Control register, EWCTRL.EWOFFSET

## **Related Links**

NVM User Row Mapping on page 47

## 24.6.2.3. Enabling, Disabling, and Resetting

The WDT is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The WDT is disabled by writing a '0' to CTRLA.ENABLE.

The WDT can be disabled only if the Always-On bit in the Control A register (CTRLA.ALWAYSON) is '0'.

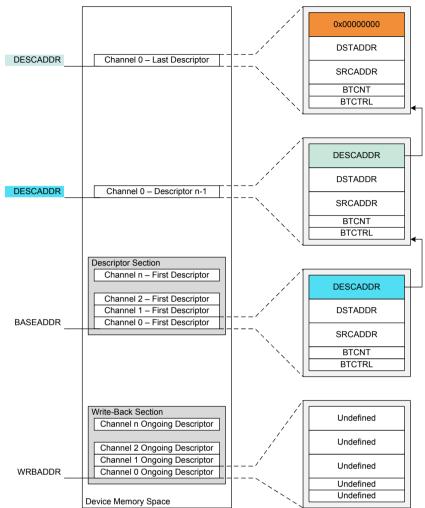

The size of the descriptor and write-back memory sections is dependent on the number of the most significant enabled DMA channel *m*, as shown below:

Size = 128bits  $\cdot (m + 1)$

For memory optimization, it is recommended to always use the less significant DMA channels if not all channels are required.

The descriptor and write-back memory sections can either be two separate memory sections, or they can share memory section (BASEADDR=WRBADDR). The benefit of having them in two separate sections, is that the same transaction for a channel can be repeated without having to modify the first transfer descriptor. The benefit of having descriptor memory and write-back memory in the same section is that it requires less LP SRAM.

# 26.6.2.4. Arbitration

If a DMA channel is enabled and not suspended when it receives a transfer trigger, it will send a transfer request to the arbiter. When the arbiter receives the transfer request it will include the DMA channel in the queue of channels having pending transfers, and the corresponding Pending Channel x bit in the Pending Channels registers (PENDCH.PENDCHx) will be set. Depending on the arbitration scheme, the arbiter will choose which DMA channel will be the next active channel. The active channel is the DMA channel being granted access to perform its next transfer. When the arbiter has granted a DMA channel access to the DMAC, the corresponding bit PENDCH.PENDCHx will be cleared. See also the following figure.

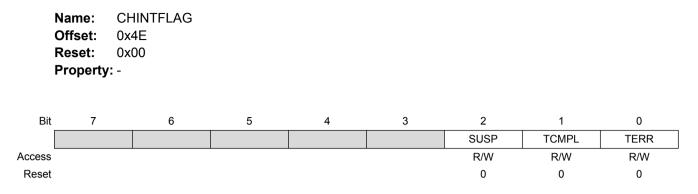

#### 26.8.22. Channel Interrupt Flag Status and Clear

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

## Bit 2 – SUSP: Channel Suspend

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer with suspend block action is completed, when a software suspend command is executed, when a suspend event is received or when an invalid descriptor is fetched by the DMA.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Channel Suspend interrupt flag for the corresponding channel.

For details on available software commands, refer to CHCTRLB.CMD.

For details on available event input actions, refer to CHCTRLB.EVACT.

For details on available block actions, refer to BTCTRL.BLOCKACT.

#### Bit 1 – TCMPL: Channel Transfer Complete

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer is completed and the corresponding interrupt block action is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Complete interrupt flag for the corresponding channel.

#### Bit 0 – TERR: Channel Transfer Error

This flag is cleared by writing a '1' to it.

This flag is set when a bus error is detected during a beat transfer or when the DMAC fetches an invalid descriptor.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Error interrupt flag for the corresponding channel.

#### 28.8.4. Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x0CReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0 |

|--------|---|---|---|---|---|---|-------|---|

|        |   |   |   |   |   |   | ERROR |   |

| Access |   |   |   |   |   |   | R/W   |   |

| Reset  |   |   |   |   |   |   | 0     |   |

#### Bit 1 – ERROR: Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the ERROR interrupt enable.

This bit will read as the current value of the ERROR interrupt enable.

| Value     | Channel Number |

|-----------|----------------|

| 0x0B      | 10             |

| 0x0C      | 11             |

| 0x0D-0xFF | Reserved       |

#### Table 30-2. User Multiplexer Number

| USERm  | User Multiplexer | Description | Path Type                                                 |

|--------|------------------|-------------|-----------------------------------------------------------|

| m = 0  | PORT EV0         | Event 0     | Asynchronous,<br>synchronous, and<br>resynchronized paths |

| m = 1  | PORT EV1         | Event 1     | Asynchronous,<br>synchronous, and<br>resynchronized paths |

| m = 2  | PORT EV2         | Event 2     | Asynchronous,<br>synchronous, and<br>resynchronized paths |

| m = 3  | PORT EV3         | Event 3     | Asynchronous,<br>synchronous, and<br>resynchronized paths |

| m = 4  | DMAC CH0         | Channel 0   | Synchronous, and resynchronized paths                     |

| m = 5  | DMAC CH1         | Channel 1   | Synchronous, and resynchronized paths                     |

| m = 6  | DMAC CH2         | Channel 2   | Synchronous, and resynchronized paths                     |

| m = 7  | DMAC CH3         | Channel 3   | Synchronous, and resynchronized paths                     |

| m = 8  | DMAC CH4         | Channel 4   | Synchronous, and resynchronized paths                     |

| m = 9  | DMAC CH5         | Channel 5   | Synchronous, and resynchronized paths                     |

| m = 10 | DMAC CH6         | Channel 6   | Synchronous, and resynchronized paths                     |

| m = 11 | DMAC CH7         | Channel 7   | Synchronous, and resynchronized paths                     |

| m = 12 | TCC0 EV0         | -           | Asynchronous,<br>synchronous, and<br>resynchronized paths |

| m = 13 | TCC0 EV1         | -           | Asynchronous,<br>synchronous, and<br>resynchronized paths |

- SPI:

- Hardware chip select

- Wake on  $\overline{SS}$  assertion

See the Related Links for full feature lists of the interface configurations.

#### **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter on page 577 SERCOM SPI – SERCOM Serial Peripheral Interface on page 615 SERCOM I2C – SERCOM Inter-Integrated Circuit on page 648

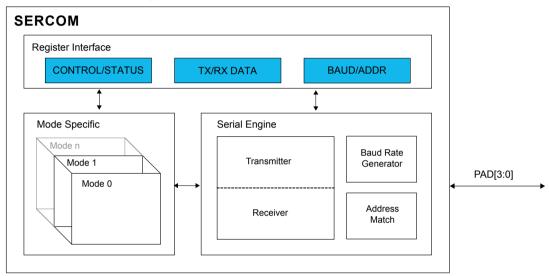

# 31.3. Block Diagram

#### Figure 31-1. SERCOM Block Diagram

# 31.4. Signal Description

See the respective SERCOM mode chapters for details.

## **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter on page 577 SERCOM SPI – SERCOM Serial Peripheral Interface on page 615 SERCOM I2C – SERCOM Inter-Integrated Circuit on page 648

# 31.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 31.5.1. I/O Lines

Using the SERCOM I/O lines requires the I/O pins to be configured using port configuration (PORT).

From USART Block Diagram one can see that the SERCOM has four internal pads, PAD[3:0]. The signals from I2C, SPI and USART are routed through these SERCOM pads via a multiplexer. The configuration of the multiplexer is available from the different SERCOM modes. Refer to the mode specific chapters for details.

# 32.6.4. DMA, Interrupts and Events

#### Table 32-4. Module Request for SERCOM USART

| Condition                          | Request                                       |           |       |  |  |  |

|------------------------------------|-----------------------------------------------|-----------|-------|--|--|--|

|                                    | DMA                                           | Interrupt | Event |  |  |  |

| Data Register Empty (DRE)          | Yes<br>(request cleared when data is written) | Yes       | NA    |  |  |  |

| Receive Complete (RXC)             | Yes<br>(request cleared when data is read)    | Yes       |       |  |  |  |

| Transmit Complete (TXC)            | NA                                            | Yes       |       |  |  |  |

| Receive Start (RXS)                | NA                                            | Yes       |       |  |  |  |

| Clear to Send Input Change (CTSIC) | NA                                            | Yes       |       |  |  |  |

| Receive Break (RXBRK)              | NA                                            | Yes       |       |  |  |  |

| Error (ERROR)                      | NA                                            | Yes       |       |  |  |  |

#### 32.6.4.1. DMA Operation

The USART generates the following DMA requests:

- Data received (RX): The request is set when data is available in the receive FIFO. The request is cleared when DATA is read.

- Data transmit (TX): The request is set when the transmit buffer (TX DATA) is empty. The request is cleared when DATA is written.

#### 32.6.4.2. Interrupts

The USART has the following interrupt sources. These are asynchronous interrupts, and can wake up the device from any sleep mode:

- Data Register Empty (DRE)

- Receive Complete (RXC)

- Transmit Complete (TXC)

- Receive Start (RXS)

- Clear to Send Input Change (CTSIC)

- Received Break (RXBRK)

- Error (ERROR)

Each interrupt source has its own interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the interrupt condition is met. Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and if the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the USART is reset. For details on clearing interrupt flags, refer to the INTFLAG register description.

The USART has one common interrupt request line for all the interrupt sources. The value of INTFLAG indicates which interrupt is executed. Note that interrupts must be globally enabled for interrupt requests. Refer to *Nested Vector Interrupt Controller* for details.

## Bit 1 – TXC: Transmit Complete

This flag is cleared by writing '1' to it or by writing new data to DATA.

This flag is set when the entire frame in the transmit shift register has been shifted out and there are no new data in DATA.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 0 – DRE: Data Register Empty

This flag is cleared by writing new data to DATA.

This flag is set when DATA is empty and ready to be written.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

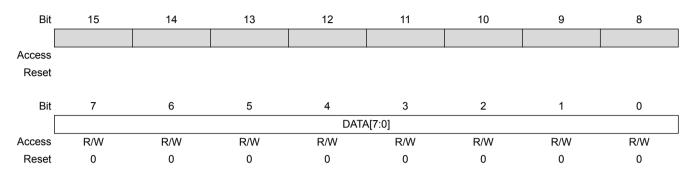

# Name:DATAOffset:0x28Reset:0x0000Property:Write-Synchronized, Read-Synchronized

# Bits 7:0 - DATA[7:0]: Data

The slave data register I/O location (DATA.DATA) provides access to the master transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is held low by the slave (STATUS.CLKHOLD is set). An exception occurs when reading the last data byte after the stop condition has been received.

Accessing DATA.DATA auto-triggers I<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

Writing or reading DATA.DATA when not in smart mode does not require synchronization.

# Atmel

## 34.8.9. Data

#### 34.10.5. Interrupt Enable Clear

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name:INTENSETOffset:0x16Reset:0x00Property:PAC Write-Protection

| Bit    | 7     | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|-------|---|---|---|---|---|-----|-----|

|        | ERROR |   |   |   |   |   | SB  | MB  |

| Access | R/W   |   |   |   |   |   | R/W | R/W |

| Reset  | 0     |   |   |   |   |   | 0   | 0   |

#### Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |  |

|-------|------------------------------|--|

| 0     | Error interrupt is disabled. |  |

| 1     | Error interrupt is enabled.  |  |

#### Bit 1 – SB: Slave on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Slave on Bus Interrupt Enable bit, which enables the Slave on Bus interrupt.

| Val | ue | Description                             |  |  |  |

|-----|----|-----------------------------------------|--|--|--|

| 0   |    | The Slave on Bus interrupt is disabled. |  |  |  |

| 1   |    | The Slave on Bus interrupt is enabled.  |  |  |  |

#### Bit 0 – MB: Master on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Master on Bus Interrupt Enable bit, which enables the Master on Bus interrupt.

|   | /alue | Description                              |  |  |  |

|---|-------|------------------------------------------|--|--|--|

| C | )     | The Master on Bus interrupt is disabled. |  |  |  |

| 1 |       | The Master on Bus interrupt is enabled.  |  |  |  |

#### 36.8.8. Debug control

Name:DBGCTRLOffset:0x1EReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0      |

|--------|---|---|---|---|---|-------|---|--------|

|        |   |   |   |   |   | FDDBD |   | DBGRUN |

| Access |   |   |   |   |   | R/W   |   | R/W    |

| Reset  |   |   |   |   |   | 0     |   | 0      |

#### Bit 2 – FDDBD: Fault Detection on Debug Break Detection

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

By default this bit is zero, and the on-chip debug (OCD) fault protection is enabled. OCD break request from the OCD system will trigger non-recoverable fault. When this bit is set, OCD fault protection is disabled and OCD break request will not trigger a fault.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | No faults are generated when TCC is halted in debug mode.                                     |

| 1     | A non recoverable fault is generated and FAULTD flag is set when TCC is halted in debug mode. |

#### Bit 0 – DBGRUN: Debug Running State

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

| Value | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| 0     | The TCC is halted when the device is halted in debug mode.                  |

| 1     | The TCC continues normal operation when the device is halted in debug mode. |

#### 38.8.10. Initialization Vector x Register

Name:

INTVECTx

Offset:

0x3C + n\*0x04 [n=0..3]

Reset:

0x0000000

Property:

PAC Write-Protection

| Bit    | 31 | 30 | 29 | 28     | 27       | 26 | 25 | 24 |

|--------|----|----|----|--------|----------|----|----|----|

|        |    |    |    | INTVEC | T[31:24] |    |    |    |

| Access | W  | W  | W  | W      | W        | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19       | 18 | 17 | 16 |

|        |    |    |    | INTVEC | T[23:16] |    |    |    |

| Access | W  | W  | W  | W      | W        | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11       | 10 | 9  | 8  |

|        |    |    |    | INTVE  | CT[15:8] |    |    |    |

| Access | W  | W  | W  | W      | W        | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3        | 2  | 1  | 0  |

|        |    |    |    | INTVE  | CT[7:0]  |    |    |    |

| Access | W  | W  | W  | W      | W        | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0  |

#### Bits 31:0 – INTVECT[31:0]: Initialization Vector Value

The four 32-bit Initialization Vector registers INTVECTX set the 128-bit Initialization Vector data block that is used by some modes of operation as an additional initial input. INTVECT0.INTVECT corresponds to the first word of the Initialization Vector, INTVECT3.INTVECT to the last one. These registers are write-only to prevent the Initialization Vector from being read by another application. For CBC, OFB, and CFB modes, the Initialization Vector corresponds to the initialization vector. For CTR mode, it corresponds to the counter value.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The Upstream Resume interrupt is disabled. |

| 1     | The Upstream Resume interrupt is enabled.  |

# Bit 5 – DNRSM: Down Resume Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Down Resume interrupt Enable bit and enable the DNRSM interrupt.

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The Down Resume interrupt is disabled. |

| 1     | The Down Resume interrupt is enabled.  |

# Bit 4 – WAKEUP: Wake Up Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Wake Up interrupt Enable bit and enable the WAKEUP interrupt request.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The WakeUp interrupt is disabled. |

| 1     | The WakeUp interrupt is enabled.  |

# Bit 3 – RST: Bus Reset Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Bus Reset interrupt Enable bit and enable the Bus RST interrupt.

| Value | Description                          |  |

|-------|--------------------------------------|--|

| 0     | The Bus Reset interrupt is disabled. |  |

| 1     | The Bus Reset interrupt is enabled.  |  |

## Bit 2 – HSOF: Host Start-of-Frame Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Host Start-of-Frame interrupt Enable bit and enable the HSOF interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Host Start-of-Frame interrupt is disabled. |

| 1     | The Host Start-of-Frame interrupt is enabled.  |

I/O pins are externally accessible so that the operational amplifier can be configured with external feedback.

All OPAMPs can be cascaded to support circuits such as differential amplifiers.

#### 41.6.2. Basic Operation

Each operational amplifier can be configured in different modes, selected by the OPAMP Control x register (OPAMPCTRLx):

- Standalone operational amplifier

- Operational amplifier with built-in feedback

After being enabled, a start-up delay is added before the output of the operational amplifier is available. This start-up time is measured internally to account for environmental changes such as temperature or voltage supply level.

When the OPAMP is ready, the respective Ready x bit in the Status register is set (STATUS.READYx=1).

If the supply voltage is below 2.5V, the start-up time is also dependent on the voltage doubler. If the supply voltage is always above 2.5V, the voltage doubler can be disabled by setting the Low-Power Mux bit in the Control A Register (CTRLA.LPMUX).

# 41.6.2.1. Initialization

The OPAMP must be configured with the desired properties and inputs before it is enabled.

The asynchronous clocks CLK\_OPAMP must be configured in the OSC32KCTRL module before enabling individual OPAMPs. See OSC32KCTRL – 32KHz Oscillators Controller for further details.

#### **Related Links**

OSC32KCTRL - 32KHz Oscillators Controller on page 273

#### 41.6.2.2. Enabling, Disabling, and Resetting

The OPAMP is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The OPAMP is disabled by writing a '0' to CTRLA.ENABLE.

Each OPAMP sub-module is enabled by writing a '1' to the Enable bit in the OPAMP Control x register (OPAMPCTRLx.ENABLE). Each OPAMP sub-module is disabled by writing a '0'to OPAMPCTRLx.ENABLE.

The OPAMP module is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the OPAMP will be reset to their initial state, and the OPAMP will be disabled. Refer to CTRLA for details.

#### 41.6.3. DMA Operation

Not applicable.

## 41.6.4. Interrupts

Not applicable.

#### 41.6.5. Events

Not applicable.

#### 41.6.6. Sleep Mode Operation

The OPAMPs can also be used during sleep modes. The 32KHz clock source used by the voltage doubler must remain active. See Voltage Doubler for more details.

## 42.8.10. Control C

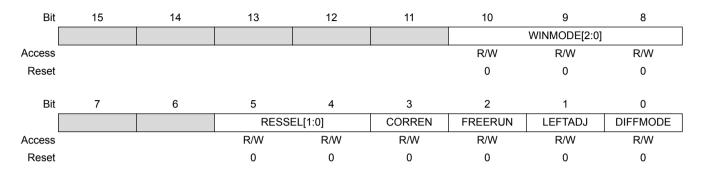

Name:CTRLCOffset:0x0AReset:0x0000Property:PAC Write-Protection, Write-Synchronized

# Bits 10:8 – WINMODE[2:0]: Window Monitor Mode

These bits enable and define the window monitor mode.

| Value     | Name    | Description              |

|-----------|---------|--------------------------|

| 0x0       | DISABLE | No window mode (default) |

| 0x1       | MODE1   | RESULT > WINLT           |

| 0x2       | MODE2   | RESULT < WINUT           |

| 0x3       | MODE3   | WINLT < RESULT < WINUT   |

| 0x4       | MODE4   | WINUT < RESULT < WINLT   |

| 0x5 - 0x7 |         | Reserved                 |

#### Bits 5:4 – RESSEL[1:0]: Conversion Result Resolution

These bits define whether the ADC completes the conversion 12-, 10- or 8-bit result resolution.

| Value | Name  | Description               |

|-------|-------|---------------------------|

| 0x0   | 12BIT | 12-bit result             |

| 0x1   | 16BIT | For averaging mode output |

| 0x2   | 10BIT | 10-bit result             |

| 0x3   | 8BIT  | 8-bit result              |

#### Bit 3 – CORREN: Digital Correction Logic Enabled

| Value | Description                                                                                                                                                                                                                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Disable the digital result correction.                                                                                                                                                                                                                                                                                                       |

| 1     | Enable the digital result correction. The ADC conversion result in the RESULT register is then corrected for gain and offset based on the values in the GAINCORR and OFFSETCORR registers. Conversion time will be increased by 13 cycles according to the value in the Offset Correction Value bit group in the Offset Correction register. |

# Atmel

Note: The pin VOUT0 will be dedicated as internal input and cannot be configured as alternate function.

#### 44.6.3.2. Output Buffer Current Control

Power consumption can be reduced by controlling the output buffer current, according to conversion rate. Writing to the Current Control bits in DAC Control x register (DACCTRLx.[1:0]) will select an output buffer current.

## 44.6.3.3. Conversion Refresh

The DAC can only maintain its output within one LSB of the desired value for approximately 100µs. When a DAC is used to generate a static voltage or at a rate less than 20kSPS, the conversion must be refreshed periodically. The OSCULP32K clock can start new conversions automatically after a specified period. Write a value to the Refresh bit field in the DAC Control x register (DACCTRLx.REFRESH[3:0]) to select the refresh period according to the formula:

$T_{\text{REFRESH}} = \text{REFRESH} \times T_{\text{OSCULP32K}}$

The actual period will depend on the tolerance of the OSCULP32K (see Electrical Characteristics).

If DACCTRLx.REFRESH=0, there is no conversion refresh. DACCTRLx.REFRESH=1 is Reserved.

If no new conversion is started before the refresh period is completed, DACx will convert the DATAx value again.

In standby sleep mode, the refresh mode remains enabled if DACCTRLx.RUNSTDBY=1.

If DATAx is written while a refresh conversion is ongoing, the conversion of the new content of DATAx is postponed until DACx is ready to start the next conversion.

#### **Related Links**

Electrical Characteristics on page 1144

#### 44.6.3.4. Differential Mode

DAC0 and DAC1 can be configured to operate in differential mode, i.e. the combined output is a voltage balanced around VREF/2, see also the figure below.

In differential mode, DAC0 and DAC1 are converting synchronously the DATA0 value. DATA0 must therefore be a signed value, represented in two's complement format with DATA0[11] as the signed bit. DATA0 has therefore the range [-2047:2047].

VOUT0 is the positive output and VOUT1 the negative output. The differential output voltage is therefore:

$$V_{\text{OUT}} = \frac{\text{DATA0}}{2047} \times \text{VREF} = (V_{\text{OUT0}} - V_{\text{OUT1}})$$

DACCTRL0 serves as the configuration register for both DAC0 and DAC1. Therefore DACCTRL1 does not need to be written.

The differential mode is enabled by writing a '1' to the Differential bit in the Control B register (CTRLB.DIFF).

| Symbol           | Parameter        | Conditions                          | Min.   | Тур.   | Max.   | Units |

|------------------|------------------|-------------------------------------|--------|--------|--------|-------|

| F <sub>OUT</sub> | Output frequency | at 25°C, at V <sub>DDIO</sub> =3.3V | 31.775 | 32.768 | 34.033 | kHz   |

|                  |                  | at 25°C, over [1.62, 3.63]V         | 31.848 | 32.768 | 34.202 | kHz   |

|                  |                  | over[-40,+85]°C, over [1.62, 3.63]V | 26.296 | 32.768 | 38.384 | kHz   |

| Duty             | Duty Cycle       |                                     | -      | 50     | -      | %     |

## 46.12.4. Internal Ultra Low Power 32KHz RC Oscillator (OSCULP32K) Characteristics Table 46-52. Ultra Low Power Internal 32KHz RC Oscillator Electrical Characteristics

# 46.12.5. Digital Frequency Locked Loop (DFLL48M) Characteristics

# Table 46-53. DFLL48M Characteristics - Open Loop Mode<sup>(1,2)</sup>

| Symbol       | Parameter        | Conditions                                                                              | Min. | Тур. | Max. | Units |

|--------------|------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| FOpenOUT     | Output frequency | DFLLVAL.COARSE=DFLL48M_COARSE_CAL<br>DFLLVAL.FINE=512                                   | 46.6 | 47.8 | 49   | MHz   |

| TOpenSTARTUP | Startup time     | DFLLVAL.COARSE=DFLL48M_COARSE_CAL<br>DFLLVAL.FINE=512<br>FOUT within 90% of final value | -    | 8.3  | 9.1  | μs    |

## Note:

- 1. DFLL48 in open loop can be used only with LDO regulator.

- 2. These values are based on characterization.

# Table 46-54. DFLL48M Characteristics - Closed Loop Mode

| Symbol                                  | Parameter                    | Conditions                                                                                                                                                                                                     | Min.   | Тур.   | Max.   | Units |

|-----------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|

| F <sub>CloseOUT</sub>                   | Average Output<br>frequency  | f <sub>REF</sub> = XTAL, 32.768kHz, 100ppm<br>DFLLMUL=1464                                                                                                                                                     | 47.963 | 47.972 | 47.981 | MHz   |

| F <sub>REF</sub> <sup>(2,3)</sup>       | Input reference<br>frequency |                                                                                                                                                                                                                | 732    | 32768  | 33000  | Hz    |

| F <sub>CloseJitter</sub> <sup>(1)</sup> | Period Jitter                | f <sub>REF</sub> = XTAL, 32.768kHz, 100ppm<br>DFLLMUL=1464                                                                                                                                                     | -      | -      | 0.51   | ns    |

| T <sub>Lock</sub> <sup>(1)</sup>        | Lock time                    | F <sub>REF</sub> = XTAL, 32.768kHz, 100ppm<br>DFLLMUL=1464<br>DFLLVAL.COARSE=DFLL48M_COARSE_CAL<br>DFLLVAL.FINE = 512<br>DFLLCTRL.BPLCKC = 1<br>DFLLCTRL.QLDIS = 0<br>DFLLCTRL.CCDIS = 1<br>DFLLMUL.FSTEP = 10 |        | 200    | 700    | μs    |

# Note:

1. These values are based on characterization.