Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21j18b-ant |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 9.4.1. Power-On Reset on VDDIN

VDDIN is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VDDIN goes below the threshold voltage, the entire chip is reset.

### 9.4.2. Power-On Reset on VSWOUT

VSWOUT is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VSWOUT goes below the threshold voltage, the entire chip is reset.

### 9.4.3. Power-On Reset on VDDIO

VDDIO is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VDDIO goes below the threshold voltage, all I/Os supplied by VSWOUT are reset.

## 9.4.4. Brown-Out Detector on VSWOUT/VBAT

BOD33 monitors VSWOUT or VBAT depending on configuration.

## **Related Links**

SUPC – Supply Controller on page 292 Battery Backup Power Switch on page 297

## 9.4.5. Brown-Out Detector on VDDCORE

Once the device has started up, BOD12 monitors the internal VDDCORE.

## **Related Links**

SUPC – Supply Controller on page 292 Battery Backup Power Switch on page 297

# 9.5. Performance Level Overview

By default, the device will start in Performance Level 0. This PL0 is aiming for the lowest power consumption by limiting logic speeds and the CPU frequency. As a consequence, all GCLK will have limited capabilities, and some peripherals and clock sources will not work or with limited capabilities:

List of peripherals/clock sources not available in PL0:

- USB (limited by logic frequency)

- DFLL48M

List of peripherals/clock sources with limited capabilities in PL0:

- All AHB/APB peripherals are limited by CPU frequency

- DPLL96M: may be able to generate 48MHz internally, but the output cannot be used by logic

- GCLK: the maximum frequency is by factor 4 compared to PL2

- SW interface: the maximum frequency is by factor 4 compared to PL2

- TC: the maximum frequency is by factor 4 compared to PL2

- TCC: the maximum frequency is by factor 4 compared to PL2

- SERCOM: the maximum frequency is by factor 4 compared to PL2

List of peripherals/clock sources with full capabilities in PL0:

- AC

- ADC

- DAC

- EIC

# 12. Processor and Architecture

# 12.1. Cortex M0+ Processor

The Atmel SAM L21 implements the ARM<sup>®</sup>Cortex<sup>™</sup>-M0+ processor, based on the ARMv6 Architecture and Thumb<sup>®</sup>-2 ISA. The Cortex M0+ is 100% instruction set compatible with its predecessor, the Cortex-M0 core, and upward compatible to Cortex-M3 and M4 cores. The implemented ARM Cortex-M0+ is revision r0p1. For more information refer to http://www.arm.com

## 12.1.1. Cortex M0+ Configuration

Table 12-1. Cortex M0+ Configuration in Atmel SAM L21

| Features                         | Cortex M0+ options           | Atmel SAM L21 configuration                          |

|----------------------------------|------------------------------|------------------------------------------------------|

| Interrupts                       | External interrupts 0-32     | 29                                                   |

| Data endianness                  | Little-endian or big-endian  | Little-endian                                        |

| SysTick timer                    | Present or absent            | Present                                              |

| Number of watchpoint comparators | 0, 1, 2                      | 2                                                    |

| Number of breakpoint comparators | 0, 1, 2, 3, 4                | 4                                                    |

| Halting debug support            | Present or absent            | Present                                              |

| Multiplier                       | Fast or small                | Fast (single cycle)                                  |

| Single-cycle I/O port            | Present or absent            | Present                                              |

| Wake-up interrupt controller     | Supported or not supported   | Not supported                                        |

| Vector Table Offset Register     | Present or absent            | Present                                              |

| Unprivileged/Privileged support  | Present or absent            | Absent - All software run in<br>privileged mode only |

| Memory Protection Unit           | Not present or 8-region      | Not present                                          |

| Reset all registers              | Present or absent            | Absent                                               |

| Instruction fetch width          | 16-bit only or mostly 32-bit | 32-bit                                               |

The ARM Cortex-M0+ core has two bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides connections to peripherals and all system memory including Flash memory and RAM

- Single 32-bit I/O port bus interfacing to the PORT with 1-cycle loads and stores

## 12.1.1.1. Cortex M0+ Peripherals

- System Control Space (SCS)

- The processor provides debug through registers in the SCS. Refer to the Cortex-M0+ Technical Reference Manual for details (http://www.arm.com)

- Nested Vectored Interrupt Controller (NVIC)

## 17.5.2. Power Management

The GCLK can operate in all sleep modes, if required.

#### **Related Links**

PM – Power Manager on page 192

# 17.5.3. Clocks

The GCLK bus clock (CLK\_GCLK\_APB) can be enabled and disabled in the Main Clock Controller.

### **Related Links**

Peripheral Clock Masking on page 157 OSC32KCTRL – 32KHz Oscillators Controller on page 273

# 17.5.4. DMA

Not applicable.

# 17.5.5. Interrupts

Not applicable.

# 17.5.6. Events

Not applicable.

## 17.5.7. Debug Operation

When the CPU is halted in debug mode the GCLK continues normal operation. If the GCLK is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

### 17.5.8. Register Access Protection

All registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC).

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

## **Related Links**

PAC - Peripheral Access Controller on page 59

### 17.5.9. Analog Connections

Not applicable.

## 17.6. Functional Description

### 17.6.1. Principle of Operation

The GCLK module is comprised of nine Generic Clock Generators (Generators) sourcing up to 64 Peripheral Channels and the Main Clock signal GCLK\_MAIN.

A clock source selected as input to a Generator can either be used directly, or it can be prescaled in the Generator. A generator output is used by one or more Peripheral Channels to provide a peripheral generic clock signal (GCLK\_PERIPH) to the peripherals.

interrupt sources, the user must read the INTFLAG register to determine which interrupt condition is present.

### **Related Links**

Overview on page 52 PM – Power Manager on page 192 Sleep Mode Controller on page 198

# 18.6.5. Events

Not applicable.

## 18.6.6. Sleep Mode Operation

In IDLE sleep mode, the MCLK is still running on the selected main clock.

In STANDBY sleep mode, the MCLK is frozen if no synchronous clock is required.

| Value | Description                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The voltage reference is always on, if enabled.                                                                                           |

| 1     | The voltage reference is enabled when a peripheral is requesting it. The voltage reference is disabled if no peripheral is requesting it. |

# Bit 6 – RUNSTDBY: Run In Standby

The bit controls how the voltage reference behaves during standby sleep mode.

| Value | Description                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The voltage reference is halted during standby sleep mode.                                                                                                                                                                                        |

| 1     | The voltage reference is not stopped in standby sleep mode. If VREF.ONDEMAND=1, the voltage reference will be running when a peripheral is requesting it. If VREF.ONDEMAND=0, the voltage reference will always be running in standby sleep mode. |

# Bit 2 – VREFOE: Voltage Reference Output Enable

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The Voltage Reference output is not available as an ADC input channel. |

| 1     | The Voltage Reference output is routed to an ADC input channel.        |

## Bit 1 – TSEN: Temperature Sensor Enable

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | Temperature Sensor is disabled.                                   |

| 1     | Temperature Sensor is enabled and routed to an ADC input channel. |

# 25.5.9. Analog Connections

A 32.768kHz crystal can be connected to the XIN32 and XOUT32 pins, along with any required load capacitors. See Electrical Characteristics for details on recommended crystal characteristics and load capacitors.

## **Related Links**

**Electrical Characteristics on page 1144**

# 25.6. Functional Description

## 25.6.1. Principle of Operation

The RTC keeps track of time in the system and enables periodic events, as well as interrupts and events at a specified time. The RTC consists of a 10-bit prescaler that feeds a 32-bit counter. The actual format of the 32-bit counter depends on the RTC operating mode.

The RTC can function in one of these modes:

- Mode 0 COUNT32: RTC serves as 32-bit counter

- Mode 1 COUNT16: RTC serves as 16-bit counter

- Mode 2 CLOCK: RTC serves as clock/calendar with alarm functionality

## 25.6.2. Basic Operation

## 25.6.2.1. Initialization

The following bits are enable-protected, meaning that they can only be written when the RTC is disabled (CTRLA.ENABLE=0):

- Operating Mode bits in the Control A register (CTRLA.MODE)

- Prescaler bits in the Control A register (CTRLA.PRESCALER)

- Clear on Match bit in the Control A register (CTRLA.MATCHCLR)

- Clock Representation bit in the Control A register (CTRLA.CLKREP)

The following register is enable-protected

• Event Control register (EVCTRL)

Enable-protected bits and registers can be changed only when the RTC is disabled (CTRLA.ENABLE=0). If the RTC is enabled (CTRLA.ENABLE=1), these operations are necessary: first write CTRLA.ENABLE=0 and check whether the write synchronization has finished, then change the desired bit field value. Enable-protected bits in can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

The RTC prescaler divides the source clock for the RTC counter.

**Note:** In Clock/Calendar mode, the prescaler must be configured to provide a 1Hz clock to the counter for correct operation.

The frequency of the RTC clock (CLK\_RTC\_CNT) is given by the following formula:

$$f_{\text{CLK\_RTC\_CNT}} = \frac{f_{\text{CLK\_RTC\_OSC}}}{2^{\text{PRESCALER}}}$$

The frequency of the oscillator clock, CLK\_RTC\_OSC, is given by  $f_{CLK_RTC_OSC}$ , and  $f_{CLK_RTC_CNT}$  is the frequency of the internal prescaled RTC clock, CLK\_RTC\_CNT.

## 25.12.8. Frequency Correlation

Name:FREQCORROffset:0x14Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7    | 6 | 5   | 4   | 3    | 2      | 1   | 0   |

|--------|------|---|-----|-----|------|--------|-----|-----|

|        | SIGN |   |     |     | VALU | E[5:0] |     |     |

| Access | R/W  |   | R/W | R/W | R/W  | R/W    | R/W | R/W |

| Reset  | 0    |   | 0   | 0   | 0    | 0      | 0   | 0   |

# Bit 7 – SIGN: Correction Sign

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The correction value is positive, i.e., frequency will be decreased. |

| 1     | The correction value is negative, i.e., frequency will be increased. |

# Bits 5:0 – VALUE[5:0]: Correction Value

These bits define the amount of correction applied to the RTC prescaler.

| Value   | Description                                                |

|---------|------------------------------------------------------------|

| 0       | Correction is disabled and the RTC frequency is unchanged. |

| 1 - 127 | The RTC frequency is adjusted according to the value.      |

| Action                         | CHCTRLB.EVACT | CHCTRLB.TRGSRC |

|--------------------------------|---------------|----------------|

| Conditional Transfer on Strobe | TRIG          | any peripheral |

| Conditional Transfer           | CTRIG         | -              |

| Conditional Block Transfer     | CBLOCK        |                |

| Channel Suspend                | SUSPEND       |                |

| Channel Resume                 | RESUME        |                |

| Skip Next Block Suspend        | SSKIP         |                |

## **Normal Transfer**

The event input is used to trigger a beat or burst transfer on peripherals.

The event is acknowledged as soon as the event is received. When received, both the Channel Pending status bit in the Channel Status register (CHSTATUS.PEND) and the corresponding Channel n bit in the Pending Channels register (PENDCH.PENDCHn) are set. If the event is received while the channel is pending, the event trigger is lost.

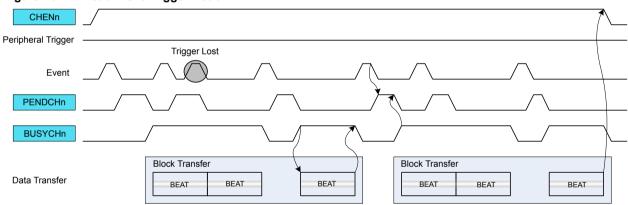

The figure below shows an example where beat transfers are enabled by internal events.

Figure 26-11. Beat Event Trigger Action

## **Conditional Transfer on Strobe**

The event input is used to trigger a transfer on peripherals with pending transfer requests. This event action is intended to be used with peripheral triggers, e.g. for timed communication protocols or periodic transfers between peripherals: only when the peripheral trigger coincides with the occurrence of a (possibly cyclic) event the transfer is issued.

The event is acknowledged as soon as the event is received. The peripheral trigger request is stored internally when the previous trigger action is completed (i.e. the channel is not pending) and when an active event is received. If the peripheral trigger is active, the DMA will wait for an event before the peripheral trigger is internally registered. When both event and peripheral transfer trigger are active, both CHSTATUS.PEND and PENDCH.PENDCHn are set. A software trigger will now trigger a transfer.

The figure below shows an example where the peripheral beat transfer is started by a conditional strobe event action.

## 27.6.4. Additional Features

### 27.6.4.1. Non-Maskable Interrupt (NMI)

The non-maskable interrupt pin can also generate an interrupt on edge or level detection, but it is configured with the dedicated NMI Control register (NMICTRL). To select the sense for NMI, write to the NMISENSE bit group in the NMI Control register (NMICTRL.NMISENSE). NMI filtering is enabled by writing a '1' to the NMI Filter Enable bit (NMICTRL.NMIFILTEN).

If edge detection or filtering is required, enable GCLK\_EIC or CLK\_ULP32K.

NMI detection is enabled only by the NMICTRL.NMISENSE value, and the EIC is not required to be enabled.

After reset, NMI is configured to no detection mode.

When an NMI is detected, the non-maskable interrupt flag in the NMI Flag Status and Clear register is set (NMIFLAG.NMI). NMI interrupt generation is always enabled, and NMIFLAG.NMI generates an interrupt request when set.

### 27.6.4.2. Asynchronous Edge Detection Mode

The EXTINT edge detection can be operated synchronously or asynchronously, selected by the Asynchronous Control Mode bit for external pin x in the External Interrupt Asynchronous Mode register (ASYNCH.ASYNCH[x]). The EIC edge detection is operated synchronously when the Asynchronous Control Mode bit (ASYNCH.ASYNCH[x]) is '0' (default value). It is operated asynchronously when ASYNCH.ASYNCH[x] is written to '1'.

In Synchronous Edge Detection Mode, the external interrupt (EXTINT) or the non-maskable interrupt (NMI) pins are sampled using the EIC clock as defined by the Clock Selection bit in the Control A register (CTRLA.CKSEL). The External Interrupt flag (INTFLAG.EXTINT[x]) or Non-Maskable Interrupt flag (NMIFLAG.NMI) is set when the last sampled state of the pin differs from the previously sampled state. In this mode, the EIC clock is required.

The Synchronous Edge Detection Mode can be used in Idle sleep mode.

In *Asynchronous Edge Detection Mode*, the external interrupt (EXTINT) pins or the non-maskable interrupt (NMI) pins set the External Interrupt flag or Non-Maskable Interrupt flag (INTFLAG.EXTINT[x] or NMIFLAG) directly. In this mode, the EIC clock is not requested.

The asynchronous edge detection mode can be used in all sleep modes.

### 27.6.5. DMA Operation

Not applicable.

### 27.6.6. Interrupts

The EIC has the following interrupt sources:

- External interrupt pins (EXTINTx). See Basic Operation.

- Non-maskable interrupt pin (NMI). See Additional Features.

Each interrupt source has an associated interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when an interrupt condition occurs (NMIFLAG for NMI). Each interrupt, except NMI, can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the EIC

## 28.8.7. Status

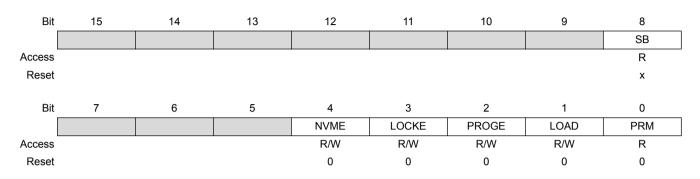

Name:STATUSOffset:0x18Reset:0x0X00Property:-

# Bit 8 – SB: Security Bit Status

| Value | Description                   |

|-------|-------------------------------|

| 0     | The Security bit is inactive. |

| 1     | The Security bit is active.   |

## Bit 4 – NVME: NVM Error

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------|

| 0     | No programming or erase errors have been received from the NVM controller since this bit was last cleared. |

| 1     | At least one error has been registered from the NVM Controller since this bit was last cleared.            |

### Bit 3 – LOCKE: Lock Error Status

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                  |  |  |

|-------|----------------------------------------------------------------------------------------------|--|--|

| 0     | No programming of any locked lock region has happened since this bit was last cleared.       |  |  |

| 1     | Programming of at least one locked lock region has happened since this bit was last cleared. |  |  |

# Bit 2 – PROGE: Programming Error Status

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | No invalid commands or bad keywords were written in the NVM Command register since this bit was last cleared.         |

| 1     | An invalid command and/or a bad keyword was/were written in the NVM Command register since this bit was last cleared. |

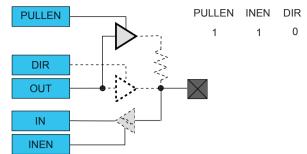

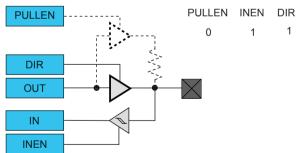

#### Figure 29-5. I/O Configuration - Input with Pull

**Note:** When pull is enabled, the pull value is defined by the OUT value.

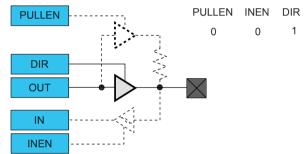

## 29.6.3.3. Totem-Pole Output

When configured for totem-pole (push-pull) output, the pin is driven low or high according to the corresponding bit setting in the OUT register. In this configuration there is no current limitation for sink or source other than what the pin is capable of. If the pin is configured for input, the pin will float if no external pull is connected.

Note: Enabling the output driver will automatically disable pull.

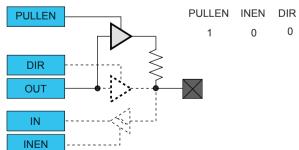

#### Figure 29-6. I/O Configuration - Totem-Pole Output with Disabled Input

#### Figure 29-7. I/O Configuration - Totem-Pole Output with Enabled Input

#### Figure 29-8. I/O Configuration - Output with Pull

| Value | Description               |

|-------|---------------------------|

| 0x0   | USART with external clock |

| 0x1   | USART with internal clock |

## Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable Synchronization Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |  |

|-------|-----------------------------------------------|--|

| 0     | The peripheral is disabled or being disabled. |  |

| 1     | The peripheral is enabled or being enabled.   |  |

## Bit 0 – SWRST: Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

Writing '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same writeoperation will be discarded. Any register write access during the ongoing reset will result in an APB error. Reading any register will return the reset value of the register.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

| Va | alue | Description                          |  |

|----|------|--------------------------------------|--|

| 0  |      | There is no reset operation ongoing. |  |

| 1  |      | The reset operation is ongoing.      |  |

# 34.10. Register Description - I<sup>2</sup>C Master

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

not reflect the registers of the 32-bit counter. Writing to any of the slave registers will not affect the 32-bit counter. Normal access to the slave COUNT and CCx registers is not allowed.

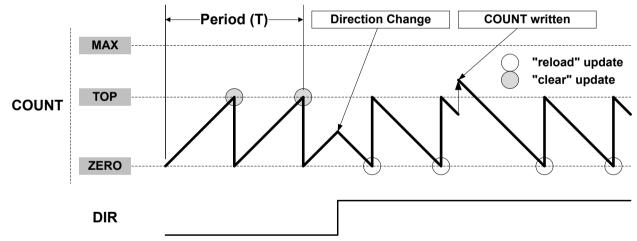

## 35.6.2.5. Counter Operations

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TC clock input (CLK\_TC\_CNT). A counter clear or reload marks the end of the current counter cycle and the start of a new one.

The counting direction is set by the Direction bit in the Control B register (CTRLB.DIR). If this bit is zero the counter is counting up, and counting down if CTRLB.DIR=1. The counter will count up or down for each tick (clock or event) until it reaches TOP or ZERO. When it is counting up and TOP is reached, the counter will be set to zero at the next tick (overflow) and the Overflow Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF) will be set. When it is counting down, the counter is reloaded with the TOP value when ZERO is reached (underflow), and INTFLAG.OVF is set.

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e. a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. When starting the TC, the COUNT value will be either ZERO or TOP (depending on the counting direction set by CTRLBSET.DIR or CTRLBCLR.DIR), unless a different value has been written to it, or the TC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed during normal operation. See also the figure below.

Due to asynchronous clock domains, the internal counter settings are written when the synchronization is complete. Normal operation must be used when using the counter as timer base for the capture channels.

### **Stop Command and Event Action**

A Stop command can be issued from software by using Command bits in the Control B Set register (CTRLBSET.CMD = 0x2, STOP). When a Stop is detected while the counter is running, the counter will be loaded with the starting value (ZERO or TOP, depending on direction set by CTRLBSET.DIR or CTRLBCLR.DIR). All waveforms are cleared and the Stop bit in the Status register is set (STATUS.STOP).

Writing a '1' to this bit clears the CNT interrupt flag.

## Bit 1 – TRG: Retrigger Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a counter retrigger occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the re-trigger interrupt flag.

## Bit 0 – OVF: Overflow Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after an overflow condition occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

## Bits 19,18,17,16 – MCx: Match or Capture Channel x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a match with the compare condition or once CCx register contain a valid capture value.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In Capture operation, this flag is automatically cleared when CCx register is read.

## Bits 15,14 – FAULTx: Non-Recoverable Fault x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Non-Recoverable Fault x occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Non-Recoverable Fault x interrupt flag.

| CTRLA.RESOLUTION | Bits [n:0]     |

|------------------|----------------|

| 0x0 - NONE       | -              |

| 0x1 - DITH4      | 3:0            |

| 0x2 - DITH5      | 4:0            |

| 0x3 - DITH6      | 5:0 (depicted) |

## 37.8.4. Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|--------|---|---|---|---|---|---|---|---------|

|        |   |   |   |   |   |   |   | DATARDY |

| Access |   |   |   |   |   |   |   | R/W     |

| Reset  |   |   |   |   |   |   |   | 0       |

# Bit 0 – DATARDY: Data Ready Interrupt Enable

Writing a '1' to this bit will set the Data Ready Interrupt Enable bit, which enables the corresponding interrupt request.

| Value | Description                        |  |

|-------|------------------------------------|--|

| 0     | The DATARDY interrupt is disabled. |  |

| 1     | The DATARDY interrupt is enabled.  |  |

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Transfer Fail 1 Interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Transfer Fail 1 interrupt is disabled.                                                                                          |

| 1     | The Transfer Fail 1 interrupt is enabled and an interrupt request will be generated when the Transfer Fail 1 Interrupt Flag is set. |

### Bit 2 – TRFAIL0: Transfer Fail 0 Interrupt Enable

The user should look into the descriptor table status located in ram to be informed about the error condition : ERRORFLOW, CRC.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Transfer Fail 0 Interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Transfer Fail bank 0 interrupt is disabled.                                                                                          |

| 1     | The Transfer Fail bank 0 interrupt is enabled and an interrupt request will be generated when the Transfer Fail 0 Interrupt Flag is set. |

## Bit 1 – TRCPT1: Transfer Complete 1 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Transfer Complete 1 Interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Transfer Complete 1 interrupt is disabled.                                                                                              |

| 1     | The Transfer Complete 1 interrupt is enabled and an interrupt request will be generated when the Transfer Complete 1 Interrupt Flag is set. |

### Bit 0 – TRCPT0: Transfer Complete 0 interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Transfer Complete 0 interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Transfer Complete bank 0 interrupt is disabled.                                                                                              |

| 1     | The Transfer Complete bank 0 interrupt is enabled and an interrupt request will be generated when the Transfer Complete 0 Interrupt Flag is set. |

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

## 44.8.14. Data Buffer DAC1

Name:DATABUF1Offset:0x16Reset:0x0000Property:Write-Synchronized

| Bit    | 15            | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|--------|---------------|----|----|----|----|----|---|---|

|        | DATABUF[15:8] |    |    |    |    |    |   |   |

| Access | W             | W  | W  | W  | W  | W  | W | W |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

|        |               |    |    |    |    |    |   |   |

| Bit    | 7             | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

|        | DATABUF[7:0]  |    |    |    |    |    |   |   |

| Access | W             | W  | W  | W  | W  | W  | W | W |

| Reset  | 0             | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

|        |               |    |    |    |    |    |   |   |

# Bits 15:0 – DATABUF[15:0]: DAC1 Data Buffer

DATABUF1 contains the value to be transferred into DATA1 when a START1 event occurs.