Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-11-                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART, USB                        |

| Peripherals                | DMA, POR, PWM, WDT                                                         |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml21j18b-mnt |

# 11.5. NVM Temperature Log Row

The NVM Temperature Log Row contains calibration data that are determined and written during production test. These calibration values are required for calculating the temperature from measuring the temperature sensor in the Supply Controller (SUPC) by the ADC.

The NVM Temperature Log Row can be read at address 0x00806030.

The NVM Temperature Log Row can not be written.

Table 11-6. Temperature Log Row Content

| Bit Position | Name              | Description                                                                                         |

|--------------|-------------------|-----------------------------------------------------------------------------------------------------|

| 7:0          | ROOM_TEMP_VAL_INT | Integer part of room temperature in °C                                                              |

| 11:8         | ROOM_TEMP_VAL_DEC | Decimal part of room temperature                                                                    |

| 19:12        | HOT_TEMP_VAL_INT  | Integer part of hot temperature in °C                                                               |

| 23:20        | HOT_TEMP_VAL_DEC  | Decimal part of hot temperature                                                                     |

| 31:24        | ROOM_INT1V_VAL    | 2's complement of the internal 1V reference drift at room temperature (versus a 1.0 centered value) |

| 39:32        | HOT_INT1V_VAL     | 2's complement of the internal 1V reference drift at hot temperature (versus a 1.0 centered value)  |

| 51:40        | ROOM_ADC_VAL      | Temperature sensor 12bit ADC conversion at room temperature                                         |

| 63:52        | HOT_ADC_VAL       | Temperature sensor 12bit ADC conversion at hot temperature                                          |

## **Related Links**

Device Temperature Measurement on page 1042

Temperature Sensor Characteristics on page 1170

# 11.6. Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following addresses:

Word 0: 0x0080A00C Word 1: 0x0080A040 Word 2: 0x0080A044 Word 3: 0x0080A048

The uniqueness of the serial number is guaranteed only when using all 128 bits.

# 16.3. Register Synchronization

## 16.3.1. Overview

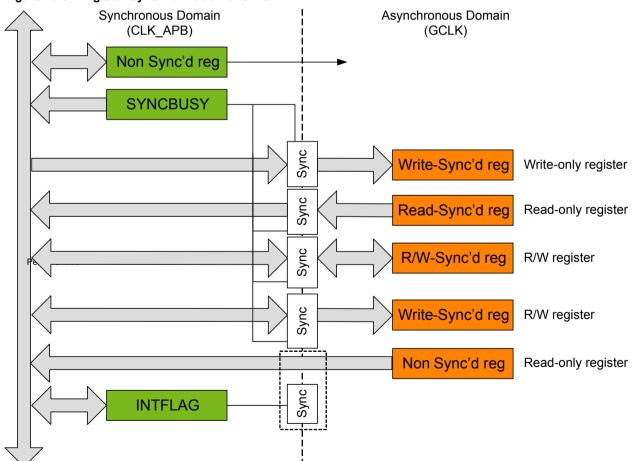

All peripherals are composed of one digital bus interface connected to the APB or AHB bus and running from a corresponding clock in the Main Clock domain, and one peripheral core running from the peripheral Generic Clock (GCLK).

Communication between these clock domains must be synchronized. This mechanism is implemented in hardware, so the synchronization process takes place even if the peripheral generic clock is running from the same clock source and on the same frequency as the bus interface.

All registers in the bus interface are accessible without synchronization.

All registers in the peripheral core are synchronized when written. Some registers in the peripheral core are synchronized when read.

Each individual register description will have the properties "Read-Synchronized" and/or "Write-Synchronized" if a register is synchronized.

As shown in the figure below, each register that requires synchronization has its individual synchronizer and its individual synchronization status bit in the Synchronization Busy register (SYNCBUSY).

**Note:** For registers requiring both read- and write-synchronization, the corresponding bit in SYNCBUSY is shared.

Figure 16-3. Register Synchronization Overview

There is one exception concerning the Generator 0. As it is used as GCLK\_MAIN, it cannot be locked. It is reset by any Reset and will start up in a known configuration. The software reset (CTRLA.SWRST) can not unlock the registers.

In case of an external Reset, the Generator source will be disabled. Even if the WRTLOCK bit is written to '1' the peripheral channels are disabled (PCHCTRLm.CHEN set to '0') until the Generator source is enabled again. Then, the PCHCTRLm.CHEN are set to '1' again.

## **Related Links**

CTRLA on page 146

PCHCTRLm on page 151

# 17.6.4. Additional Features

# 17.6.4.1. Peripheral Clock Enable after Reset

The Generic Clock Controller must be able to provide a generic clock to some specific peripherals after a Reset. That means that the configuration of the Generators and Peripheral Channels after Reset is device-dependent.

Refer to GENCTRLn.SRC for details on GENCTRLn reset.

Refer to PCHCTRLm.SRC for details on PCHCTRLm reset.

## 17.6.5. Sleep Mode Operation

#### 17.6.5.1. SleepWalking

The GCLK module supports the SleepWalking feature.

If the system is in a sleep mode where the Generic Clocks are stopped, a peripheral that needs its clock in order to execute a process must request it from the Generic Clock Controller.

The Generic Clock Controller receives this request, determines which Generic Clock Generator is involved and which clock source needs to be awakened. It then wakes up the respective clock source, enables the Generator and Peripheral Channel stages successively, and delivers the clock to the peripheral.

The RUNSTDBY bit in the Generator Control register controls clock output to pin during standby sleep mode. If the bit is cleared, the Generator output is not available on pin. When set, the GCLK can continuously output the generator output to GCLK\_IO. Refer to External Clock for details.

# Related Links

PM – Power Manager on page 192

#### 17.6.5.2. Minimize Power Consumption in Standby

The following table identifies when a Clock Generator is off in Standby Mode, minimizing the power consumption:

Table 17-2. Clock Generator n Activity in Standby Mode

| Request for Clock n present | GENCTRLn.RUNSTDB<br>Y | GENCTRLn.OE | Clock Generator n |

|-----------------------------|-----------------------|-------------|-------------------|

| yes                         | -                     | -           | active            |

| no                          | 1                     | 1           | active            |

| no                          | 1                     | 0           | OFF               |

Exiting STANDBY mode: Any peripheral able to generate an asynchronous interrupt can wake up the system. For example, a peripheral running on a GCLK clock can trigger an interrupt. When the enabled asynchronous wake-up event occurs and the system is woken up, the device will either execute the interrupt service routine or continue the normal program execution according to the Priority Mask Register (PRIMASK) configuration of the CPU.

Refer to Table 20-3 for the RAM state.

The regulator operates in low-power mode by default and switches automatically to the normal mode in case of a sleepwalking task requiring more power. It returns automatically to low power mode when the sleepwalking task is completed.

#### **BACKUP Mode**

The BACKUP mode allows achieving the lowest power consumption aside from OFF. The device is entirely powered off except for the backup domain. All peripherals in backup domain are allowed to run, e.g. the RTC can be clocked by a 32.768kHz oscillator. All PM registers are reset except the CTRLA.IORET bit.

- Entering Backup mode: This mode is entered by executing the WFI instruction after selecting the Backup mode by writing the Sleep Mode bits in the Sleep Configuration register (SLEEPCFG.SLEEPMODE=BACKUP).

- Exiting Backup mode: is triggered when a Backup Reset is detected by the Reset Controller (RSTC).

#### **OFF Mode**

In OFF mode, the device is entirely powered-off.

- Entering OFF mode: This mode is entered by selecting the OFF mode in the Sleep Configuration register by writing the Sleep Mode bits (SLEEPCFG.SLEEPMODE=OFF), and subsequent execution of the WFI instruction.

- Exiting OFF mode: This mode is left by pulling the RESET pin low, or when a power Reset is done.

# 20.6.3.4. I/O Lines Retention in BACKUP Mode

When entering BACKUP mode, the PORT is powered off but the pin configuration is retained. When the device exits the BACKUP mode, the I/O line configuration can either be released or stretched, based on the I/O Retention bit in the CTRLA register (CTRLA.IORET).

- If IORET=0 when exiting BACKUP mode, the I/O lines configuration is released and driven by the reset value of the PORT.

- If the IORET=1 when exiting BACKUP mode, the configuration of the I/O lines is retained until the IORET bit is written to 0. It allows the I/O lines to be retained until the application has programmed the PORT.

#### 20.6.3.5. Performance Level

The application can change the performance level on the fly writing to the by Performance Level Select bit in the Performance Level Configuration register (PLCFG.PLSEL).

When changing to a lower performance level, the bus frequency must be reduced before writing PLCFG.PLSEL in order to avoid exceeding the limit of the target performance level.

When changing to a higher performance level, the bus frequency can be increased only after the Performance Level Ready flag in the Interrupt Flag Status and Clear (INTFLAG.PLRDY) bit set to '1', indicating that the performance level transition is complete.

After a reset, the device starts in the lowest PL (lowest power consumption and lowest max frequency). The application can then switch to another PL at anytime without any stop in the code execution. As shown in Figure 20-3, performance level transition is possible only when the device is in active mode.

All modules located in PD0 are able to generate events. The EVSYS event generator must be configured to either synchronous or resynchronized path.

When PD0 and PD1 are in retention, dynamic SleepWalking based on event is not useful.

Refer also to Power Domains.

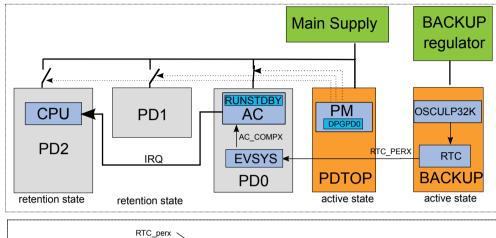

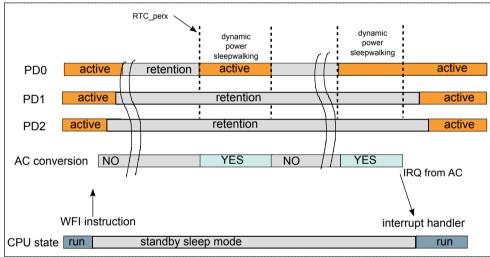

Dynamic SleepWalking based on event is illustrated in the following example:

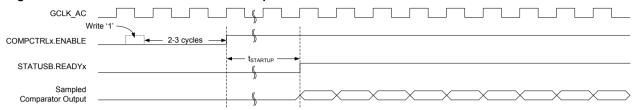

Figure 20-10. Dynamic SleepWalking based on Event: AC Periodic Comparison

The Analog Comparator (AC) peripheral is used in single shot mode to monitor voltage levels on input pins. A comparator interrupt, based on the AC peripheral configuration, is generated to wake up the device. In the GCLK module, the AC generic clock (GCLK\_AC) source is routed a 32.768kHz oscillator (for low power applications, OSC32KULP is recommended). RTC and EVSYS modules are configured to generate periodic events to the AC. To make the comparator continue to run in standby sleep mode, the RUNSTDBY bit is written to '1'. To enable the dynamic SleepWalking for PD0 power domain, STDBYCFG.DPGPD0 must be written to '1'.

Entering standby mode: The Power Manager sets the PD0 power domain (where the AC module is located) in retention state, as well as PD1 and PD2. The AC comparators, COMPx, are OFF. The GCLK AC clock is stopped. The VDDCORE is supplied by the low power regulator.

*Dynamic SleepWalking*: The RTC event (RTC\_PERX) is routed by the Event System to the Analog Comparator to trigger a single-shot measurement. This event is detected by the Power Manager, which sets the PD0 power domain to active state and starts the main voltage regulator.

#### **USB Clock Recovery Module**

USB Clock Recovery mode can be used to create the 48MHz USB clock from the USB Start Of Frame (SOF). This mode is enabled by writing a '1' to both the USB Clock Recovery Mode bit and the Mode bit in DFLL Control register (DFLLCTRL.USBCRM and DFLLCTRL.MODE).

The SOF signal from USB device will be used as reference clock (CLK\_DFLL\_REF), ignoring the selected generic clock reference. When the USB device is connected, a SOF will be sent every 1ms, thus DFLLVAL.MUX bits should be written to 0xBB80 to obtain a 48MHz clock.

In USB clock recovery mode, the DFLLCTRL.BPLCKC bit state is ignored, and the value stored in the DFLLVAL.COARSE will be used as final Coarse Value. The COARSE calibration value can be loaded from NVM OTP row by software. The locking procedure will also go instantaneously to the fine lock search.

The DFLLCTRL.QLDIS bit must be cleared and DFLLCTRL.CCDIS should be set to speed up the lock phase. The DFLLCTRL.STABLE bit state is ignored, an auto jitter reduction mechanism is used instead.

#### Wake from Sleep Modes

DFLL48M can optionally reset its lock bits when it is disabled. This is configured by the Lose Lock After Wake bit in the DFLL Control register (DFLLCTRL.LLAW).

If DFLLCTRL.LLAW is zero, the DFLL48M will be re-enabled and start running with the same configuration as before being disabled, even if the reference clock is not available. The locks will not be lost. After the reference clock has restarted, the fine lock tracking will quickly compensate for any frequency drift during sleep if DFLLCTRL.STABLE is zero.

If DFLLCTRL.LLAW is '1' when disabling the DFLL48M, the DFLL48M will lose all its locks, and needs to regain these through the full lock sequence.

# **Accuracy**

There are three main factors that determine the accuracy of  $F_{\text{clkdfll48m}}$ . These can be tuned to obtain maximum accuracy when fine lock is achieved.

- Fine resolution. The frequency step between two Fine values. This is relatively smaller for higher output frequencies.

- Resolution of the measurement: If the resolution of the measured F<sub>clkdfll48m</sub> is low, i.e., the ratio between the CLK\_DFLL48M frequency and the CLK\_DFLL48M\_REF frequency is small, the DFLL48M might lock at a frequency that is lower than the targeted frequency. It is recommended to use a reference clock frequency of 32KHz or lower to avoid this issue for low target frequencies.

- The accuracy of the reference clock.

## 21.6.5. Digital Phase Locked Loop (DPLL) Operation

The task of the DPLL is to maintain coherence between the input (reference) signal and the respective output frequency, CLK\_DPLL, via phase comparison. The DPLL controller supports three independent sources of reference clocks:

- XOSC32K: this clock is provided by the 32K External Crystal Oscillator (XOSC32K).

- XOSC: this clock is provided by the External Multipurpose Crystal Oscillator (XOSC).

- GCLK: this clock is provided by the Generic Clock Controller.

When the controller is enabled, the relationship between the reference clock frequency and the output clock frequency is:

$$f_{\text{CK}} = f_{\text{CKR}} \times \left( \text{LDR} + 1 + \frac{\text{LDRFRAC}}{16} \right) \times \frac{1}{2^{\text{PRESC}}}$$

## 23.6.2.2. Enabling, Disabling, and Resetting

The voltage reference output is enabled/disabled by setting/clearing the Voltage Reference Output Enable bit in the Voltage Reference register (VREF.VREFOE).

The temperature sensor is enabled/disabled by setting/clearing the Temperature Sensor Enable bit in the Voltage Reference register (VREF.TSEN).

**Note:** When VREF.ONDEMAND=0, it is not recommended to enable both voltage reference output and temperature sensor at the same time - only the voltage reference output will be present at both ADC inputs.

# 23.6.2.3. Selecting a Voltage Reference

The Voltage Reference Selection bit field in the VREF register (VREF.SEL) selects the voltage of INTREF to be applied to analog modules, e.g. the ADC.

## 23.6.2.4. Sleep Mode Operation

The Voltage Reference output and the Temperature Sensor output behavior during sleep mode can be configured using the Run in Standby bit and the On Demand bit in the Voltage Reference register (VREF.RUNSTDBY, VREF.ONDEMAND), see the following table:

Table 23-2. VREF Sleep Mode Operation

| VREF.ONDEMAND | VREF.RUNSTDBY | Voltage Reference Sleep behavior                                                         |

|---------------|---------------|------------------------------------------------------------------------------------------|

| -             | -             | Disable                                                                                  |

| 0             | 0             | Always run in all sleep modes except standby sleep mode                                  |

| 0             | 1             | Always run in all sleep modes including standby sleep mode                               |

| 1             | 0             | Only run if requested by the ADC, in all sleep modes <i>except</i> standby sleep mode    |

| 1             | 1             | Only run if requested by the ADC, in all sleep modes <i>including</i> standby sleep mode |

# 23.6.3. Battery Backup Power Switch

#### 23.6.3.1. Initialization

The Battery Backup Power Switch (BBPS) is disabled at power-up, and the backup domain is supplied by main power.

## 23.6.3.2. Forced Battery Backup Power Switch

The Backup domain is always supplied by the VBAT supply pin when the Configuration bit field in the Battery Backup Power Switch Control register (BBPS.CONF) is written to 0x2 (FORCED).

## 23.6.3.3. Automatic Battery Backup Power Switch

The supply of the backup domain can be switched automatically to VBAT supply pin by the Automatic Power Switch or by using the BOD33.

The supply of the backup domain can be switched automatically to VDD supply pin either by the Automatic Power Switch or the Main Power Pin when VDD and VDDCORE are restored.

## **Automatic Power Switch (APWS)**

When the Configuration bit field in the Battery Backup Power Switch register (BBPS.CONF) is selecting the APWS, the Automatic Power Switch will function as Battery Backup Power Switch.

The Automatic Power switch allows to switch the supply of the backup domain from VDD to VBAT power and vice-versa.

#### 25.5.3. Clocks

The RTC bus clock (CLK\_RTC\_APB) can be enabled and disabled in the Main Clock module MCLK, and the default state of CLK\_RTC\_APB can be found in Peripheral Clock Masking section.

A 32KHz or 1KHz oscillator clock (CLK\_RTC\_OSC) is required to clock the RTC. This clock must be configured and enabled in the 32KHz oscillator controller (OSC32KCTRL) before using the RTC.

This oscillator clock is asynchronous to the bus clock (CLK\_RTC\_APB). Due to this asynchronicity, writing to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### Related Links

OSC32KCTRL – 32KHz Oscillators Controller on page 273 Peripheral Clock Masking on page 157

#### 25.5.4. DMA

Not applicable.

#### Related Links

DMAC - Direct Memory Access Controller on page 406

# 25.5.5. Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the RTC interrupt requires the Interrupt Controller to be configured first.

## Related Links

Nested Vector Interrupt Controller on page 52

#### 25.5.6. Events

The events are connected to the Event System.

#### **Related Links**

EVSYS – Event System on page 544

## 25.5.7. Debug Operation

When the CPU is halted in debug mode the RTC will halt normal operation. The RTC can be forced to continue operation during debugging. Refer to DBGCTRL for details.

#### 25.5.8. Register Access Protection

All registers with write-access are optionally write-protected by the peripheral access controller (PAC), except the following registers:

- Interrupt Flag Status and Clear (INTFLAG) register

- General Purpose (GPx) registers

Write-protection is denoted by the "PAC Write-Protection" property in the register description.

Write-protection does not apply to accesses through an external debugger. Refer to the PAC - Peripheral Access Controller for details.

#### **Related Links**

PAC - Peripheral Access Controller on page 59

# 30. EVSYS – Event System

# 30.1. Overview

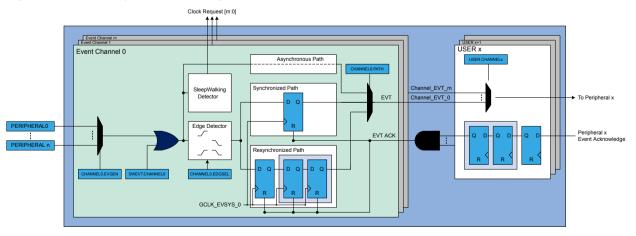

The Event System (EVSYS) allows autonomous, low-latency and configurable communication between peripherals.

Several peripherals can be configured to generate and/or respond to signals known as events. The exact condition to generate an event, or the action taken upon receiving an event, is specific to each peripheral. Peripherals that respond to events are called event users. Peripherals that generate events are called event generators. A peripheral can have one or more event generators and can have one or more event users.

Communication is made without CPU intervention and without consuming system resources such as bus or RAM bandwidth. This reduces the load on the CPU and other system resources, compared to a traditional interrupt-based system.

# 30.2. Features

- 12 configurable event channels, where each channel can:

- Be connected to any event generator.

- Provide a pure asynchronous, resynchronized or synchronous path

- 82 event generators.

- 42 event users.

- Configurable edge detector.

- Peripherals can be event generators, event users, or both.

- SleepWalking and interrupt for operation in sleep modes.

- Software event generation.

- Each event user can choose which channel to respond to.

# 30.3. Block Diagram

Figure 30-1. Event System Block Diagram

Table 30-1. Event Channel Sleep Behavior

| CHANNELn.ONDEMAN<br>D | CHANNELn.RUNSTDB<br>Y | Sleep Behavior                                                                                                                                                                       |

|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                     | 0                     | Only run in IDLE sleep mode if an event must be propagated. Disabled in STANDBY sleep mode.                                                                                          |

| 0                     | 1                     | Always run in IDLE and STANDBY sleep modes.                                                                                                                                          |

| 1                     | 0                     | Only run in IDLE sleep mode if an event must be propagated. Disabled in STANDBY sleep mode. Two GCLK_EVSYS_n latency added in RESYNC path before the event is propagated internally. |

| 1                     | 1                     | Always run in IDLE and STANDBY sleep modes. Two GCLK_EVSYS_n latency added in RESYNC path before the event is propagated internally.                                                 |

#### 30.7. **Register Summary**

# 30.7.1. Common Registers

| Offset   | Name      | Bit Pos. |         |         |         |         |          |          |          |         |

|----------|-----------|----------|---------|---------|---------|---------|----------|----------|----------|---------|

| 0x00     | CTRLA     | 7:0      |         |         |         |         |          |          |          | SWRST   |

| 0x010x0B | Reserved  |          |         |         |         |         |          |          |          |         |

| 0x0C     |           | 7:0      | USRRDY7 | USRRDY6 | USRRDY5 | USRRDY4 | USRRDY3  | USRRDY2  | USRRDY1  | USRRDY0 |

| 0x0D     | CLICTATUS | 15:8     |         |         |         |         | USRRDY11 | USRRDY10 | USRRDY9  | USRRDY8 |

| 0x0E     | CHSTATUS  | 23:16    | CHBUSY7 | CHBUSY6 | CHBUSY5 | CHBUSY4 | CHBUSY3  | CHBUSY2  | CHBUSY1  | CHBUSY0 |

| 0x0F     |           | 31:24    |         |         |         |         | CHBUSY11 | CHBUSY10 | CHBUSY9  | CHBUSY8 |

| 0x10     |           | 7:0      | OVR7    | OVR6    | OVR5    | OVR4    | OVR3     | OVR2     | OVR1     | OVR0    |

| 0x11     | INTENOLD  | 15:8     |         |         |         |         | OVR11    | OVR10    | OVR9     | OVR8    |

| 0x12     | INTENCLR  | 23:16    | EVD7    | EVD6    | EVD5    | EVD4    | EVD3     | EVD2     | EVD1     | EVD0    |

| 0x13     |           | 31:24    |         |         |         |         | EVD11    | EVD10    | EVD9     | EVD8    |

| 0x14     |           | 7:0      | OVR7    | OVR6    | OVR5    | OVR4    | OVR3     | OVR2     | OVR1     | OVR0    |

| 0x15     | INTENSET  | 15:8     |         |         |         |         | OVR11    | OVR10    | OVR9     | OVR8    |

| 0x16     | INTENSET  | 23:16    | EVD7    | EVD6    | EVD5    | EVD4    | EVD3     | EVD2     | EVD1     | EVD0    |

| 0x17     |           | 31:24    |         |         |         |         | EVD11    | EVD10    | EVD9     | EVD9    |

| 0x18     |           | 7:0      | OVR7    | OVR6    | OVR5    | OVR4    | OVR3     | OVR2     | OVR1     | OVR0    |

| 0x19     | INTELAC   | 15:8     |         |         |         |         | OVR11    | OVR10    | OVR9     | OVR8    |

| 0x1A     | INTFLAG   | 23:16    | EVD7    | EVD6    | EVD5    | EVD4    | EVD3     | EVD2     | EVD1     | EVD0    |

| 0x1B     |           | 31:24    |         |         |         |         | EVD11    | EVD10    | EVD9     | EVD9    |

| 0x1C     |           | 7:0      |         |         |         | CHANI   | NEL[7:0] |          |          |         |

| 0x1D     | OMEVT     | 15:8     |         |         |         |         |          | CHANN    | EL[11:8] |         |

| 0x1E     | SWEVT     | 23:16    |         |         |         |         |          |          |          |         |

| 0x1F     |           | 31:24    |         |         |         |         |          |          |          |         |

# 30.8.5. Interrupt Flag Status and Clear

Name: INTFLAG Offset: 0x18

**Reset:** 0x00000000

Property: -

| Bit    | 31   | 30   | 29   | 28   | 27    | 26    | 25   | 24   |

|--------|------|------|------|------|-------|-------|------|------|

|        |      |      |      |      | EVD11 | EVD10 | EVD9 | EVD8 |

| Access |      |      |      |      | R/W   | R/W   | R/W  | R/W  |

| Reset  |      |      |      |      | 0     | 0     | 0    | 0    |

|        |      |      |      |      |       |       |      |      |

| Bit    | 23   | 22   | 21   | 20   | 19    | 18    | 17   | 16   |

|        | EVD7 | EVD6 | EVD5 | EVD4 | EVD3  | EVD2  | EVD1 | EVD0 |

| Access | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0     | 0     | 0    | 0    |

|        |      |      |      |      |       |       |      |      |

| Bit    | 15   | 14   | 13   | 12   | 11    | 10    | 9    | 8    |

|        |      |      |      |      | OVR11 | OVR10 | OVR9 | OVR8 |

| Access |      |      |      |      | R/W   | R/W   | R/W  | R/W  |

| Reset  |      |      |      |      | 0     | 0     | 0    | 0    |

|        |      |      |      |      |       |       |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3     | 2     | 1    | 0    |

|        | OVR7 | OVR6 | OVR5 | OVR4 | OVR3  | OVR2  | OVR1 | OVR0 |

| Access | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0     | 0     | 0    | 0    |

## Bits 27:16 - EVDn: Event Detected Channel n [n=11..0]

This flag is set on the next CLK\_EVSYS\_APB cycle when an event is being propagated through the channel, and an interrupt request will be generated if INTENCLR/SET.EVDn is '1'.

When the event channel path is asynchronous, the EVDn interrupt flag will not be set.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Event Detected Channel n interrupt flag.

# Bits 11:0 - OVRn: Overrun Channel n [n=11..0]

This flag is set on the next CLK\_EVSYS\_APB cycle when an event is being propagated through the channel, and an interrupt request will be generated if INTENCLR/SET.OVRn is '1'.

When the event channel path is asynchronous, the OVRn interrupt flag will not be set.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Overrun Detected Channel n interrupt flag.

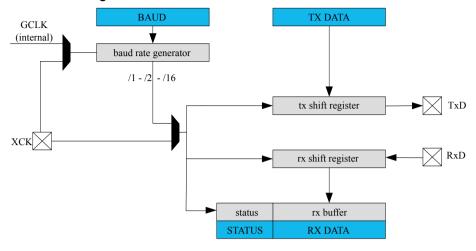

# 32.3. Block Diagram

Figure 32-1. USART Block Diagram

# 32.4. Signal Description

Table 32-1. SERCOM USART Signals

| Signal Name | Туре        | Description         |

|-------------|-------------|---------------------|

| PAD[3:0]    | Digital I/O | General SERCOM pins |

One signal can be mapped to one of several pins.

#### **Related Links**

I/O Multiplexing and Considerations on page 30

# 32.5. Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 32.5.1. I/O Lines

Using the USART's I/O lines requires the I/O pins to be configured using the I/O Pin Controller (PORT).

When the SERCOM is used in USART mode, the SERCOM controls the direction and value of the I/O pins according to the table below. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver or transmitter is disabled, these pins can be used for other purposes.

Table 32-2. USART Pin Configuration

| Pin | Pin Configuration |

|-----|-------------------|

| TxD | Output            |

| RxD | Input             |

| XCK | Output or input   |

The combined configuration of PORT and the Transmit Data Pinout and Receive Data Pinout bit fields in the Control A register (CTRLA.TXPO and CTRLA.RXPO, respectively) will define the physical position of the USART signals in Table 32-2.

#### 32.8.2. Control B

Name: CTRLB Offset: 0x04

**Reset**: 0x00000000

Property: PAC Write-Protection, Enable-Protected, Write-Synchronized

| Bit    | 31 | 30     | 29    | 28 | 27 | 26  | 25          | 24     |

|--------|----|--------|-------|----|----|-----|-------------|--------|

|        |    |        |       |    |    |     |             |        |

| Access |    |        |       |    |    |     |             | _      |

| Reset  |    |        |       |    |    |     |             |        |

|        |    |        |       |    |    |     |             |        |

| Bit    | 23 | 22     | 21    | 20 | 19 | 18  | 17          | 16     |

|        |    |        |       |    |    |     | RXEN        | TXEN   |

| Access |    |        |       |    |    |     | R/W         | R/W    |

| Reset  |    |        |       |    |    |     | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 15 | 14     | 13    | 12 | 11 | 10  | 9           | 8      |

|        |    |        | PMODE |    |    | ENC | SFDE        | COLDEN |

| Access |    |        | R/W   |    |    | R/W | R/W         | R/W    |

| Reset  |    |        | 0     |    |    | 0   | 0           | 0      |

|        |    |        |       |    |    |     |             |        |

| Bit    | 7  | 6      | 5     | 4  | 3  | 2   | 1           | 0      |

|        |    | SBMODE |       |    |    |     | CHSIZE[2:0] |        |

| Access |    | R/W    |       |    |    | R/W | R/W         | R/W    |

| Reset  |    | 0      |       |    |    | 0   | 0           | 0      |

## Bit 17 - RXEN: Receiver Enable

Writing '0' to this bit will disable the USART receiver. Disabling the receiver will flush the receive buffer and clear the FERR, PERR and BUFOVF bits in the STATUS register.

Writing '1' to CTRLB.RXEN when the USART is disabled will set CTRLB.RXEN immediately. When the USART is enabled, CTRLB.RXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled, CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the USART is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                            |

| 1     | The receiver is enabled or will be enabled when the USART is enabled. |

## Bit 16 - TXEN: Transmitter Enable

Writing '0' to this bit will disable the USART transmitter. Disabling the transmitter will not become effective until ongoing and pending transmissions are completed.

Writing '1' to CTRLB.TXEN when the USART is disabled will set CTRLB.TXEN immediately. When the USART is enabled, CTRLB.TXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the transmitter is enabled. When the transmitter is enabled, CTRLB.TXEN will read back as '1'.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 - ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 - SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# Bits 20, 21 – COPEN0, COPEN1: Capture On Pin x Enable [x = 1..0]

This bit selects the trigger source for capture operation, either events or I/O pin input.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

# Bits 16, 17 – CAPTEN0, CAPTEN1: Capture Channel x Enable [x = 1..0]

These bits are used to select whether channel x is a capture or a compare channel.

These bits are not synchronized.

| 1 | /alue | Description                            |

|---|-------|----------------------------------------|

| C | )     | CAPTENx disables capture on channel x. |

| 1 |       | CAPTENx enables capture on channel x.  |

# 39.8.4.2. Address of Data Buffer

Name: **ADDR**

**Offset:** 0x00 & 0x10 Reset: 0xxxxxxx

Property: NA

| Bit    | 31          | 30  | 29  | 28   | 27      | 26  | 25  | 24  |  |  |  |

|--------|-------------|-----|-----|------|---------|-----|-----|-----|--|--|--|

|        | ADDR[31:24] |     |     |      |         |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | Х           | x   | x   | Х    | x       | X   | x   | x   |  |  |  |

|        |             |     |     |      |         |     |     |     |  |  |  |

| Bit    | 23          | 22  | 21  | 20   | 19      | 18  | 17  | 16  |  |  |  |

|        |             |     |     | ADDR | [23:16] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | x           | x   | x   | x    | x       | x   | x   | x   |  |  |  |

|        |             |     |     |      |         |     |     |     |  |  |  |

| Bit    | 15          | 14  | 13  | 12   | 11      | 10  | 9   | 8   |  |  |  |

|        |             |     |     | ADDF | R[15:8] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | x           | x   | x   | x    | x       | x   | x   | x   |  |  |  |

|        |             |     |     |      |         |     |     |     |  |  |  |

| Bit    | 7           | 6   | 5   | 4    | 3       | 2   | 1   | 0   |  |  |  |

|        |             |     |     | ADDI | R[7:0]  |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | x           | x   | x   | x    | x       | x   | x   | X   |  |  |  |

# Bits 31:0 - ADDR[31:0]: Data Pointer Address Value

These bits define the data pointer address as an absolute word address in RAM. The two least significant bits must be zero to ensure the start address is 32-bit aligned.

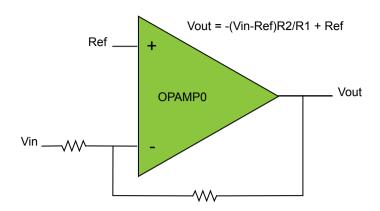

I/O pins are externally accessible so that the operational amplifier can be configured with external feedback.

All OPAMPs can be cascaded to support circuits such as differential amplifiers.

## 41.6.2. Basic Operation

Each operational amplifier can be configured in different modes, selected by the OPAMP Control x register (OPAMPCTRLx):

- Standalone operational amplifier

- Operational amplifier with built-in feedback

After being enabled, a start-up delay is added before the output of the operational amplifier is available. This start-up time is measured internally to account for environmental changes such as temperature or voltage supply level.

When the OPAMP is ready, the respective Ready x bit in the Status register is set (STATUS.READYx=1).

If the supply voltage is below 2.5V, the start-up time is also dependent on the voltage doubler. If the supply voltage is always above 2.5V, the voltage doubler can be disabled by setting the Low-Power Mux bit in the Control A Register (CTRLA.LPMUX).

# 41.6.2.1. Initialization

The OPAMP must be configured with the desired properties and inputs before it is enabled.

The asynchronous clocks CLK\_OPAMP must be configured in the OSC32KCTRL module before enabling individual OPAMPs. See OSC32KCTRL – 32KHz Oscillators Controller for further details.

#### Related Links

OSC32KCTRL – 32KHz Oscillators Controller on page 273

## 41.6.2.2. Enabling, Disabling, and Resetting

The OPAMP is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The OPAMP is disabled by writing a '0' to CTRLA.ENABLE.

Each OPAMP sub-module is enabled by writing a '1' to the Enable bit in the OPAMP Control x register (OPAMPCTRLx.ENABLE). Each OPAMP sub-module is disabled by writing a '0'to OPAMPCTRLx.ENABLE.

The OPAMP module is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the OPAMP will be reset to their initial state, and the OPAMP will be disabled. Refer to CTRLA for details.

## 41.6.3. DMA Operation

Not applicable.

# 41.6.4. Interrupts

Not applicable.

# 41.6.5. Events

Not applicable.

## 41.6.6. Sleep Mode Operation

The OPAMPs can also be used during sleep modes. The 32KHz clock source used by the voltage doubler must remain active. See Voltage Doubler for more details.

Figure 41-3. Inverting PGA

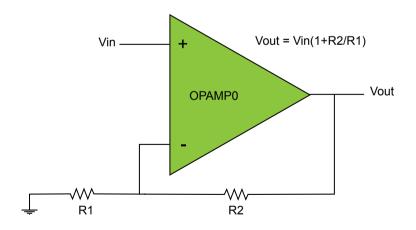

# 41.6.10.3. Non-Inverting PGA

For non-inverting programmable gain amplifier operation, the OPAMPCTRLx registers can be configured as follows:

Table 41-4. Configuration - Three Independent Non-Inverting PGAs (Example: Vout=4.Vin, R1=4R, R2=12R)

|        | MUXPOS | MUXNEG | RES1MUX | POTMUX | RES2VCC | RES2OUT | RES1EN | ANAOUT |

|--------|--------|--------|---------|--------|---------|---------|--------|--------|

| OPAMP0 | 000    | 001    | 11      | 100    | 0       | 1       | 1      | 0      |

| OPAMP1 | 000    | 001    | 11      | 100    | 0       | 1       | 1      | 0      |

| OPAMP2 | 000    | 001    | 11      | 100    | 0       | 1       | 1      | 0      |

Figure 41-4. Non-Inverting PGA

# 41.6.10.4. Cascaded Inverting PGA

The OPAMPs can be configured as three cascaded, inverting PGAs using these settings in OPAMPCTRLx:

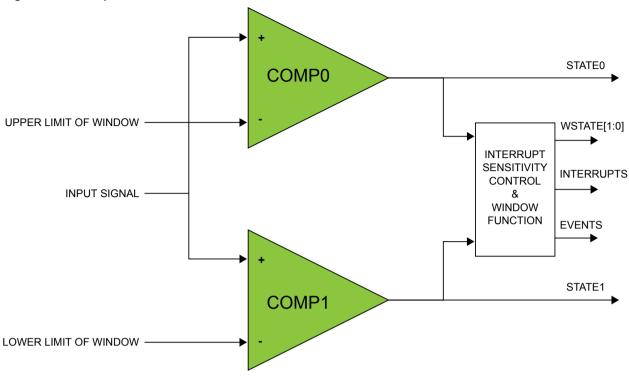

interrupts are also generated. New comparisons are performed continuously until the COMPCTRLx.ENABLE bit is written to zero. The start-up time applies only to the first comparison.

In continuous operation, edge detection of the comparator output for interrupts is done by comparing the current and previous sample. The sampling rate is the GCLK\_AC frequency. An example of continuous measurement is shown in the Figure 43-2.

Figure 43-2. Continuous Measurement Example

For low-power operation, comparisons can be performed during sleep modes without a clock. The comparator is enabled continuously, and changes of the comparator state are detected asynchronously. When a toggle occurs, the Power Manager will start GCLK\_AC to register the appropriate peripheral events and interrupts. The GCLK\_AC clock is then disabled again automatically, unless configured to wake up the system from sleep.

#### Related Links

Electrical Characteristics on page 1144

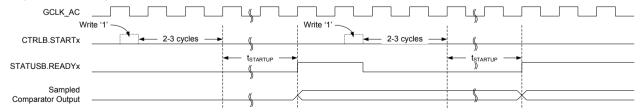

#### Single-Shot

Single-shot operation is selected by writing COMPCTRLx.SINGLE to '1'. During single-shot operation, the comparator is normally idle. The user starts a single comparison by writing '1' to the respective Start Comparison bit in the write-only Control B register (CTRLB.STARTx). The comparator is enabled, and after the start-up time has passed, a single comparison is done and STATUSA is updated. Appropriate peripheral events and interrupts are also generated. No new comparisons will be performed.

Writing '1' to CTRLB.STARTx also clears the Comparator x Ready bit in the Status B register (STATUSB.READYx). STATUSB.READYx is set automatically by hardware when the single comparison has completed.

A single-shot measurement can also be triggered by the Event System. Setting the Comparator x Event Input bit in the Event Control Register (EVCTRL.COMPEIx) enables triggering on incoming peripheral events. Each comparator can be triggered independently by separate events. Event-triggered operation is similar to user-triggered operation; the difference is that a peripheral event from another hardware module causes the hardware to automatically start the comparison and clear STATUSB.READYx.

To detect an edge of the comparator output in single-shot operation for the purpose of interrupts, the result of the current measurement is compared with the result of the previous measurement (one sampling period earlier). An example of single-shot operation is shown in Figure 43-3.

Figure 43-3. Single-Shot Example

For low-power operation, event-triggered measurements can be performed during sleep modes. When the event occurs, the Power Manager will start GCLK\_AC. The comparator is enabled, and after the startup time has passed, a comparison is done and appropriate peripheral events and interrupts are also

Figure 43-4. Comparators in Window Mode

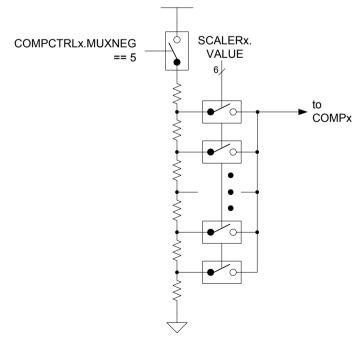

# 43.6.5. VDD Scaler

The VDD scaler generates a reference voltage that is a fraction of the device's supply voltage, with 64 levels. One independent voltage channel is dedicated for each comparator. The scaler of a comparator is enabled when the Negative Input Mux bit field in the respective Comparator Control register (COMPCTRLx.MUXNEG) is set to 0x5 and the comparator is enabled. The voltage of each channel is selected by the Value bit field in the Scaler x registers (SCALERx.VALUE).

Figure 43-5. VDD Scaler

**VDDIN Voltage** Time -Internal State Update BOD33 Level with User Row content Under POR reset Under BOD reset Jodate BOD33 Level Under BOD reset Under BOD reset Under POR reset Running Running Running Time Time -Internal Reset (active low) Time -Internal Reset (active high)

Figure 46-1. BOD Reset Behavior at Startup and Default Levels

46.10.4. Brown-Out Detectors (BOD) Characteristics

Table 46-20. BOD33 Characteristics(1)

| Symbol               | Parameters                       | Conditions             | Min.  | Тур.  | Max. | Unit |

|----------------------|----------------------------------|------------------------|-------|-------|------|------|

| V <sub>BOD+</sub>    | BOD33 high<br>threshold<br>Level | V <sub>BAT</sub> , 15  | 1.67  | 1.74  | 1.81 | V    |

|                      |                                  | V <sub>DDIN</sub> , 7  | 1.75  | 1.75  | 1.80 |      |

|                      |                                  | V <sub>DDIN</sub> , 6  | 1.66  | 1.72  | 1.75 |      |

|                      |                                  | V <sub>BAT</sub> , 55  | 2.80  | 2.90  | 3.01 |      |

|                      |                                  | V <sub>DDIN</sub> , 39 | 2.65  | 2.87  | 2.95 |      |

|                      |                                  | V <sub>BAT</sub> , 63  | 3.02  | 3.14  | 3.26 |      |

|                      |                                  | V <sub>DDIN</sub> , 48 | 03.12 | 3.20  | 3.29 |      |

| $V_{BOD-} / V_{BOD}$ | BOD33 low<br>threshold<br>Level  | V <sub>BAT</sub> , 15  | 1.60  | 1.66  | 1.72 | V    |

|                      |                                  | V <sub>DDIN</sub> , 7  | 1.63  | 1.673 | 1.71 |      |

|                      |                                  | V <sub>DDIN</sub> , 6  | 1.60  | 1.65  | 1.68 |      |

|                      |                                  | V <sub>BAT</sub> , 55  | 2.70  | 2.81  | 2.92 |      |

|                      |                                  | V <sub>DDIN</sub> , 39 | 2.70  | 2.77  | 2.84 |      |

|                      |                                  | V <sub>BAT</sub> , 63  | 2.92  | 3.04  | 3.16 |      |

|                      |                                  | V <sub>DDIN</sub> , 48 | 3.00  | 3.08  | 3.16 |      |

|                      | Step size                        | -                      |       | 34    |      | mV   |