Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b; D/A 3x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 24-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 24-VQFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny3217-mfr |

**Memories**

### 6.10.2.6 OSC20 Error at 3V

Name: OSC20ERR3V

Offset: 0x24

**Reset:** [Oscillator frequency error value]

Property: -

| Bit    | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|-----------------|---|---|---|---|---|---|---|--|--|

|        | OSC20ERR3V[7:0] |   |   |   |   |   |   |   |  |  |

| Access | R               | R | R | R | R | R | R | R |  |  |

| Reset  | X               | x | X | X | X | X | x | X |  |  |

## Bits 7:0 - OSC20ERR3V[7:0] OSC20 Error at 3V

These registers contain the signed oscillator frequency error value when running at internal 20 MHz at 3V, as measured during production.

**Memories**

### 6.10.2.7 OSC20 Error at 5V

Name: OSC20ERR5V

Offset: 0x25

**Reset:** [Oscillator frequency error value]

Property: -

| Bit    | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------|-----------------|---|---|---|---|---|---|---|--|--|--|

|        | OSC20ERR5V[7:0] |   |   |   |   |   |   |   |  |  |  |

| Access | R               | R | R | R | R | R | R | R |  |  |  |

| Reset  | X               | x | X | X | x | X | X | X |  |  |  |

## Bits 7:0 - OSC20ERR5V[7:0] OSC20 Error at 5V

These registers contain the signed oscillator frequency error value when running at internal 20 MHz at 5V, as measured during production.

## **Peripherals and Architecture**

30. ADC - Analog-to-Digital Converter

## 7.3 System Configuration (SYSCFG)

The system configuration contains the revision ID of the part. The revision ID is readable from the CPU, making it useful for implementing application changes between part revisions.

**CPUINT - CPU Interrupt Controller**

## Table 13-3. INTCTRL - Registers under Configuration Change Protection

| Register              | Key   |

|-----------------------|-------|

| IVSEL in CPUINT.CTRLA | IOREG |

| CVT in CPUINT.CTRLA   | IOREG |

### **Related Links**

8.5.7.1 Sequence for Write Operation to Configuration Change Protected I/O Registers

### 13.5.1 Control A

Name:

CTRLA

Offset:

0x00

Reset:

0x00

**Property:** Configuration Change Protection

| Bit    | 7 | 6     | 5   | 4 | 3 | 2 | 1 | 0      |  |

|--------|---|-------|-----|---|---|---|---|--------|--|

|        |   | IVSEL | CVT |   |   |   |   | LVL0RR |  |

| Access |   | R/W   | R/W |   |   |   |   | R/W    |  |

| Reset  |   | 0     | 0   |   |   |   |   | 0      |  |

### Bit 6 - IVSEL Interrupt Vector Select

If the boot section is defined, it will be placed before the application section. The actual start address of the application section is determined by the BOOTEND fuse.

This bit is protected by the Configuration Change Protection mechanism.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | Interrupt vectors are placed at the start of the application section of the Flash |

| 1     | Interrupt vectors are placed at the start of the boot section of the Flash        |

### Bit 5 - CVT Compact Vector Table

This bit is protected by the Configuration Change Protection mechanism.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | Compact Vector Table function is disabled |

| 1     | Compact Vector Table function is enabled  |

### Bit 0 - LVL0RR Round Robin Priority Enable

This bit is not protected by the Configuration Change Protection mechanism.

| Value | Description                                                                                        |

|-------|----------------------------------------------------------------------------------------------------|

| 0     | Priority is fixed for priority level 0 interrupt requests: The lowest interrupt vector address has |

|       | the highest priority.                                                                              |

| 1     | Round Robin priority scheme is enabled for priority level 0 interrupt requests                     |

## **PORTMUX - Port Multiplexer**

### 15.3.1 Control A

Name: CTRLA

Offset: 0x00

Reset: 0x00

Property: -

| Bit    | 7 | 6 | 5    | 4    | 3 | 2      | 1      | 0      |

|--------|---|---|------|------|---|--------|--------|--------|

|        |   |   | LUT1 | LUT0 |   | EVOUT2 | EVOUT1 | EVOUT0 |

| Access |   |   | R/W  | R/W  |   | R/W    | R/W    | R/W    |

| Reset  |   |   | 0    | 0    |   | 0      | 0      | 0      |

### Bit 5 – LUT1 CCL LUT 1 output

Write this bit to '1' to select alternative pin location for CCL LUT 1.

### Bit 4 - LUT0 CCL LUT 0 output

Write this bit to '1' to select alternative pin location for CCL LUT 0.

### Bit 2 - EVOUT2 Event Output 2

Write this bit to '1' to enable event output 2.

### Bit 1 - EVOUT1 Event Output 1

Write this bit to '1' to enable event output 1.

### Bit 0 - EVOUT0 Event Output 0

Write this bit to '1' to enable event output 0.

## TCA - 16-bit Timer/Counter Type A

### 20.7.4 Control D

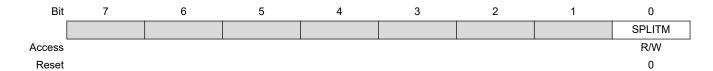

Name: CTRLD Offset: 0x03 Reset: 0x00 Property: -

### Bit 0 - SPLITM Enable Split Mode

This bit sets the timer/counter in Split mode operation. It will then work as two 8-bit timer/counters. The register map will change compared to normal 16-bit mode.

# 21.4 Register Summary - TCB

| Offset           | Name     | Bit Pos. |          |          |         |         |      |             |        |

|------------------|----------|----------|----------|----------|---------|---------|------|-------------|--------|

| 0x00             | CTRLA    | 7:0      | RUNSTDBY |          | SYNCUPD |         | CLKS | EL[1:0]     | ENABLE |

| 0x01             | CTRLB    | 7:0      | ASYNC    | CCMPINIT | CCMPEN  |         |      | CNTMODE[2:0 | ]      |

| 0x02<br><br>0x03 | Reserved |          |          |          |         |         |      |             |        |

| 0x04             | EVCTRL   | 7:0      | FILTER   |          | EDGE    |         |      |             | CAPTEI |

| 0x05             | INTCTRL  | 7:0      |          |          |         |         |      |             | CAPT   |

| 0x06             | INTFLAGS | 7:0      |          |          |         |         |      |             | CAPT   |

| 0x07             | STATUS   | 7:0      |          |          |         |         |      |             | RUN    |

| 0x08             | DBGCTRL  | 7:0      |          |          |         |         |      |             | DBGRUN |

| 0x09             | TEMP     | 7:0      |          |          | TEM     | P[7:0]  |      |             |        |

| 004              | ONIT     | 7:0      |          |          | CNT     | [7:0]   |      |             |        |

| 0x0A             | CNT      | 15:8     |          |          | CNT     | [15:8]  |      |             |        |

| 0x0C             | CCMD     | 7:0      |          |          | CCM     | P[7:0]  |      |             |        |

| UXUC             | CCMP     | 15:8     |          |          | CCMF    | P[15:8] |      |             |        |

# 21.5 Register Description

### 22.3.3 **Events**

The TCD can generate the following output events:

- TCD counter matches CMPBCLR

- TCD counter matches CMPASET

- TCD counter matches CMPBSET

- Programmable TCD output event. The user can select the trigger and all the different compare matches. In addition, it is possible to delay the output event from 0 to 256 TCD delay cycles.

The three events based on the counter match directly generate event strobes that last one clock cycle on the TCD counter clock. The programmable output event generates an event strobe that last one clock cycle on the TCD synchronizer clock.

The TCD has the possibility to receive these input events:

- Input A

- Input B

#### **Related Links**

22.3.2.4 TCD Inputs

14. EVSYS - Event System

### 22.3.3.1 Programmable Output Events

Programmable output event uses the same logic as the input blanking for trigger selection and delay. It is therefore not possible to configure the functionalities independently. If the input blanking functionality is used, the output event cannot be delayed and the trigger used for input blanking will also be used for the output event.

The programmable output events are controlled by the TCDn.DLYCTRL and TCDn.DLYVAL registers. It is possible to delay the output event by 0 to 256 TCD delay clock cycles if the DLYTRIG bits in TCDn.DLYCTRL is set to 0x2. The delayed output event functionality uses the TCD delay clock and counts until the DLYVAL value is reached before the trigger is sent out as an event. The TCD delay clock is a prescaled version of the TCD synchronization clock and the division factor is set by the DLYPRESC bits in the TCDn.DLYCTRL register. The output event will be delayed by TCD clock period x DLYPRESC division factor x DLYVAL.

#### 22.3.4 Interrupts

Table 22-8. Available Interrupt Vectors and Sources

| Offset | Name | Vector Description | Conditions                                                                                             |

|--------|------|--------------------|--------------------------------------------------------------------------------------------------------|

| 0x00   | OVF  | Overflow interrupt | The TCD is done with one TCD cycle.                                                                    |

| 0x04   | TRIG | Trigger interrupt  | <ul> <li>TRIGA: Counter is entering On-Time A</li> <li>TRIGB: Counter is entering On-Time B</li> </ul> |

When an interrupt condition occurs, the corresponding interrupt flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

## **USART - Universal Synchronous and Asynchrono...**

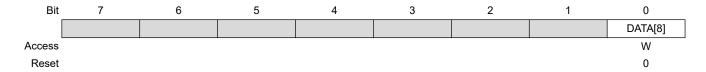

## Bit 0 - DATA[8] Receiver Data Register

When USART receiver is set to LINAUTO mode, this bit indicates if the received data is within the response space of a LIN frame. If the received data is the protected identifier field, this bit will be read as '0'. Otherwise, the bit will be read as '1'. For Receiver mode other than LINAUTO mode, DATA[8] holds the ninth data bit in the received character when operating with serial frames with nine data bits.

## **USART - Universal Synchronous and Asynchrono...**

## 24.5.4 Transmit Data Register High Byte

Name: TXDATAH

Offset: 0x03

Reset: 0x00

Property: -

USARTn.TXDATAH holds the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. When used this bit must be written before writing to USARTn.TXDATAL except if CHSIZE in USARTn.CTRLC is set to 9BIT Low byte first where USARTn.TXDATAL should be written first

This bit is unused in Master SPI mode of operation.

Bit 0 - DATA[8] Transmit Data Register

This bit is used when CHSIZE=9BIT in USARTn.CTRLC.

### 24.5.8 Control C - Async Mode

Name:

CTRLC

Offset:

0x07

Reset:

0x03

Property:

This register description is valid for all modes except Master SPI mode. When the USART Communication mode bits (CMODE) in this register are written to 'MSPI', see Control C - Master SPI Mode for the correct description.

| Bit    | 7   | 6       | 5          | 4   | 3      | 2           | 1   | 0   |

|--------|-----|---------|------------|-----|--------|-------------|-----|-----|

|        | CMO | DE[1:0] | PMODE[1:0] |     | SBMODE | CHSIZE[2:0] |     |     |

| Access | R/W | R/W     | R/W        | R/W | R/W    | R/W         | R/W | R/W |

| Reset  | 0   | 0       | 0          | 0   | 0      | 0           | 1   | 1   |

### Bits 7:6 - CMODE[1:0] USART Communication Mode

Writing these bits select the Communication mode of the USART.

Writing a 0x3 to these bits alters the available bit fields in this register, see Control C - Master SPI Mode.

| Value | Name         | Description            |

|-------|--------------|------------------------|

| 0x0   | ASYNCHRONOUS | Asynchronous USART     |

| 0x1   | SYNCHRONOUS  | Synchronous USART      |

| 0x2   | IRCOM        | Infrared Communication |

| 0x3   | MSPI         | Master SPI             |

### Bits 5:4 - PMODE[1:0] Parity Mode

Writing these bits enable and select the type of parity generation.

When enabled, the transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The receiver will generate a parity value for the incoming data, compare it to the PMODE setting, and set the Parity Error flag (PERR) in the STATUS register (USARTn.STATUS) if a mismatch is detected.

| Value | Name     | Description          |

|-------|----------|----------------------|

| 0x0   | DISABLED | Disabled             |

| 0x1   | -        | Reserved             |

| 0x2   | EVEN     | Enabled, Even Parity |

| 0x3   | ODD      | Enabled, Odd Parity  |

### Bit 3 - SBMODE Stop Bit Mode

Writing this bit selects the number of Stop bits to be inserted by the transmitter.

The receiver ignores this setting.

| Value | Description |

|-------|-------------|

| 0     | 1 Stop bit  |

| 1     | 2 Stop bits |

## **USART - Universal Synchronous and Asynchrono...**

### Bits 2:0 - CHSIZE[2:0] Character Size

Writing these bits select the number of data bits in a frame. The receiver and transmitter use the same setting. For 9BIT character size, the order of which byte to read or write first, low or high byte of RXDATA or TXDATA is selectable.

| Value | Name  | Description             |

|-------|-------|-------------------------|

| 0x0   | 5BIT  | 5-bit                   |

| 0x1   | 6BIT  | 6-bit                   |

| 0x2   | 7BIT  | 7-bit                   |

| 0x3   | 8BIT  | 8-bit                   |

| 0x4   | -     | Reserved                |

| 0x5   | -     | Reserved                |

| 0x6   | 9BITL | 9-bit (Low byte first)  |

| 0x7   | 9BITH | 9-bit (High byte first) |

## **USART - Universal Synchronous and Asynchrono...**

### 24.5.13 IRCOM Transmitter Pulse Length Control Register

Name: TXPLCTRL

Offset:

0x0D

Reset:

0x00

Property:

| Bit    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|

|        | TXPL[7:0] |     |     |     |     |     |     |     |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### Bits 7:0 – TXPL[7:0] Transmitter Pulse Length

The 8-bit value sets the pulse modulation scheme for the transmitter. Setting this register will have effect only if IRCOM mode is selected by a USART. By leaving this register value to '0', 3/16 of the baud rate period pulse modulation is used. Setting this value from 1 to 254 will give a fixed pulse length coding. The 8-bit value sets the number of system clock periods for the pulse. The start of the pulse will be synchronized with the rising edge of the baud rate clock. Setting the value to 255 (0xFF) will disable pulse coding, letting the RX and TX signals pass through the IRCOM module unaltered. This enables other features through the IRCOM module, such as half-duplex USART, Loop-back testing, and USART RX input from an event channel.

TXPL must be configured before the USART transmitter is enabled (TXEN).

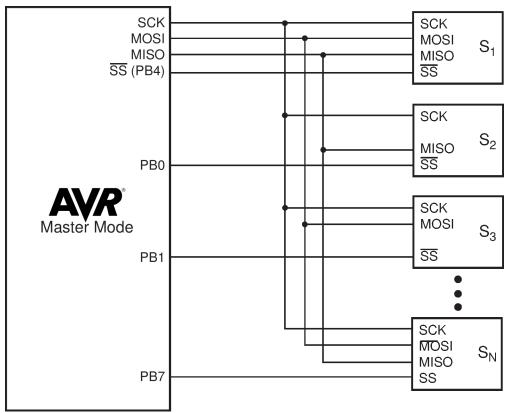

The ability to connect several devices to the same SPI bus is based on the fact that only one master and only one slave is active at the same time. The MISO, MOSI, and SCK lines of all the other slaves are tristated (configured as input pins of a high impedance with no pullup resistors enabled). A false implementation (for example, if two slaves are activated at the same time) can cause a driver contention which can lead to a CMOS latch-up state and must be avoided. Resistances of 1 to  $10\Omega$  in series with the pins of the SPI can be used to prevent the system from latching up. However this affects the maximum usable data rate, depending on the loading capacitance on the SPI pins.

Unidirectional SPI devices require just the clock line and one of the data lines. The device can use MISO line or the MOSI line depending on its purpose.

#### 25.3.2.2.4 Buffer Mode

To avoid data collisions, the SPI peripheral can be configured in buffered mode by writing a '1' to the Buffer Mode Enable bit in the Control B register (BUFEN in SPIn.CTRLB). In this mode, the SPI has additional interrupt flags and extra buffers. The extra buffers are shown in Figure 25-1. There are two different modes for the Buffer mode, selected with the Buffer mode Wait for Receive bit (BUFWR). The two different modes are described below with timing diagrams.

### 25.5.1 Control A

Name:

CTRLA

Offset:

0x00

Reset:

0x00

Property:

| Bit    | Bit 7 |      | 5      | 4     | 3 | 2          | 2 1 |        |

|--------|-------|------|--------|-------|---|------------|-----|--------|

|        |       | DORD | MASTER | CLK2X |   | PRESC[1:0] |     | ENABLE |

| Access |       | R/W  | R/W    | R/W   |   | R/W        | R/W | R/W    |

| Reset  |       | 0    | 0      | 0     |   | 0          | 0   | 0      |

#### Bit 6 - DORD Data Order

| V | 'alue | Description                                   |

|---|-------|-----------------------------------------------|

| 0 |       | The MSB of the data word is transmitted first |

| 1 |       | The LSB of the data word is transmitted first |

### Bit 5 - MASTER Master/Slave Select

This bit selects the desired SPI mode.

If  $\overline{SS}$  is configured as input and driven low while this bit is '1', this bit is cleared, and the IF flag in SPIn.INTFLAGS is set. The user has to write MASTER=1 again to re-enable SPI Master mode.

This behavior is controlled by the Slave Select Disable bit (SSD) in SPIn.CTRLB.

| Value | Description              |

|-------|--------------------------|

| 0     | SPI Slave mode selected  |

| 1     | SPI Master mode selected |

### Bit 4 - CLK2X Clock Double

When this bit is written to '1' the SPI speed (SCK frequency, after internal prescaler) is doubled in Master mode.

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | SPI speed (SCK frequency) is not doubled            |

| 1     | SPI speed (SCK frequency) is doubled in Master mode |

### Bits 2:1 - PRESC[1:0] Prescaler

This bit field controls the SPI clock rate configured in Master mode. These bits have no effect in Slave mode. The relationship between SCK and the peripheral clock frequency ( $f_{CLK\_PER}$ ) is shown below.

The output of the SPI prescaler can be doubled by writing the CLK2X bit to '1'.

| Value | Name   | Description |

|-------|--------|-------------|

| 0x0   | DIV4   | CLK_PER/4   |

| 0x1   | DIV16  | CLK_PER/16  |

| 0x2   | DIV64  | CLK_PER/64  |

| 0x3   | DIV128 | CLK_PER/128 |

### Bit 0 - ENABLE SPI Enable

**SPI - Serial Peripheral Interface**

### **Related Links**

25.3.2.3 Data Modes

# 30.4 Register Summary - ADCn

| Offset | Name     | Bit Pos. |         |              |       |         |         |              |              |         |

|--------|----------|----------|---------|--------------|-------|---------|---------|--------------|--------------|---------|

| 0x00   | CTRLA    | 7:0      | RUNSTBY |              |       |         |         | RESSEL       | FREERUN      | ENABLE  |

| 0x01   | CTRLB    | 7:0      |         |              |       |         |         |              | SAMPNUM[2:0] | l       |

| 0x02   | CTRLC    | 7:0      |         | SAMPCAP      | REFSE | EL[1:0] |         |              | PRESC[2:0]   |         |

| 0x03   | CTRLD    | 7:0      |         | INITDLY[2:0] |       | ASDV    |         | SAMP         | DLY[3:0]     |         |

| 0x04   | CTRLE    | 7:0      |         |              |       |         |         |              | WINCM[2:0]   |         |

| 0x05   | SAMPCTRL | 7:0      |         |              |       |         |         | SAMPLEN[4:0] |              |         |

| 0x06   | MUXPOS   | 7:0      |         | MUXPOS[4:0]  |       |         |         |              |              |         |

| 0x07   | Reserved |          |         |              |       |         |         |              |              |         |

| 0x08   | COMMAND  | 7:0      |         |              |       |         |         |              |              | STCONV  |

| 0x09   | EVCTRL   | 7:0      |         |              |       |         |         |              |              | STARTEI |

| 0x0A   | INTCTRL  | 7:0      |         |              |       |         |         |              | WCOMP        | RESRDY  |

| 0x0B   | INTFLAGS | 7:0      |         |              |       |         |         |              | WCOMP        | RESRDY  |

| 0x0C   | DBGCTRL  | 7:0      |         |              |       |         |         |              |              | DBGRUN  |

| 0x0D   | TEMP     | 7:0      |         |              |       | TEMI    | P[7:0]  |              |              |         |

| 0x0E   |          |          |         |              |       |         |         |              |              |         |

|        | Reserved |          |         |              |       |         |         |              |              |         |

| 0x0F   |          |          |         |              |       |         |         |              |              |         |

| 0x10   | RES      | 7:0      |         |              |       | RES     | [7:0]   |              |              |         |

| 0.00   | ILEO     | 15:8     |         |              |       | RES     | [15:8]  |              |              |         |

| 0x12   | WINLT    | 7:0      |         | WINLT[7:0]   |       |         |         |              |              |         |

| UXIZ   | WINE     | 15:8     |         | WINLT[15:8]  |       |         |         |              |              |         |

| 0x14   | WINHT    | 7:0      |         |              |       | WINH    | T[7:0]  |              |              |         |

| UX 14  | VVIINITI | 15:8     |         |              |       | WINH    | T[15:8] |              |              |         |

| 0x16   | CALIB    | 7:0      |         |              |       |         |         |              |              | DUTYCYC |

## 30.5 Register Description

### 33.2.2.1 Clocks

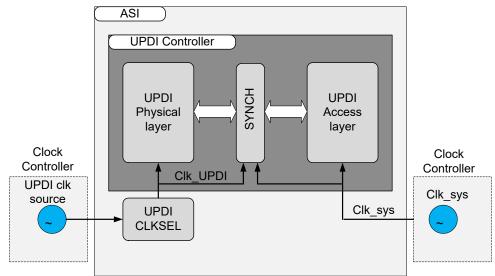

The UPDI Physical (UPDI PHY) layer and UPDI Access (UPDI ACC) layer can operate on different clock domains. The UPDI PHY layer clock is derived from an internal oscillator, and the UPDI ACC layer clock is the same as the system clock. There is a synchronization boundary between the UPDI PHY layer and the UPDI ACC layer, which ensures correct operation between the clock domains. The UPDI clock output frequency is selected through the ASI, and the default UPDI clock start-up frequency is 4 MHz after enabling the UPDI. The UPDI clock frequency is changed by writing the UPDICLKSEL bits in the ASI\_CTRLA register.

Figure 33-2. UPDI Clock Domains

#### **Related Links**

10. CLKCTRL - Clock Controller

### 33.2.2.2 I/O Lines and Connections

To operate the UPDI, the RESET pin must be set to UPDI mode. This is not done through the port I/O pin configuration as regular I/O pins, but through setting the RESET Pin Configuration (RSTPINCFG) bits in FUSE.SYSCFG0, as described in 33.3.2.1 UPDI Enable with Fuse Override of RESET Pin, or by following the UPDI 12V enable sequence from 33.3.2.2 UPDI Enable with 12V Override of RESET Pin. Pull enable, input enable, and output enable settings are automatically controlled by the UPDI when active.

#### 33.2.2.3 Events

The events of this peripheral are connected to the Event System.

#### **Related Links**

14. EVSYS - Event System

#### 33.2.2.4 Power Management

The UPDI physical layer continues to operate in any Sleep mode and is always accessible for a connected debugger, but read/write access to the system bus is restricted in Sleep modes where the CPU clock is switched OFF. The UPDI can be enabled at any time, independent of the system Sleep state. See 33.3.9 Sleep Mode Operation for details on UPDI operation during Sleep modes.

Table 37-16. 32.768 kHz External Crystal Oscillator (XOSC32K) Characteristics

| Symbol             | Description                                    | Condition               | Min. | Тур.   | Max. | Unit |

|--------------------|------------------------------------------------|-------------------------|------|--------|------|------|

| Fout               | Frequency                                      |                         | -    | 32.768 | -    | kHz  |

| T <sub>start</sub> | Start-up time                                  | C <sub>L</sub> =7.5 pF  | -    | 300    | _    | ms   |

| CL                 | Crystal load capacitance                       |                         | 7.5  | -      | 12.5 | pF   |

| CTOSC1             | Parasitic capacitor load                       |                         | -    | 5.5    | _    | pF   |

| CTOSC2             |                                                |                         | -    | 5.5    | _    | pF   |

| ESR                | Equivalent Series Resistance - Safety Factor=3 | C <sub>L</sub> =7.5 pF  | -    | -      | 80   | kΩ   |

|                    |                                                | C <sub>L</sub> =12.5 pF | _    | -      | 40   |      |

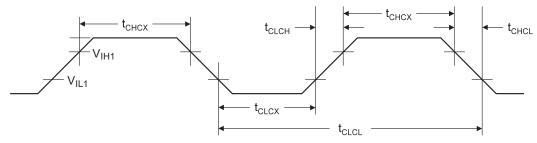

Figure 37-2. External Clock Waveform Characteristics

**Table 37-17. External Clock Characteristics**

| Symbol | Descriptio<br>n | Condition | V <sub>DD</sub> =[1.8, 5.5]V |      | V <sub>DD</sub> =[2.7, 5.5]V |      | V <sub>DD</sub> =[4.5, 5.5]V |      | Unit |

|--------|-----------------|-----------|------------------------------|------|------------------------------|------|------------------------------|------|------|

|        |                 |           | Min.                         | Max. | Min.                         | Max. | Min.                         | Max. |      |

| fCLCL  | Frequency       |           | 0                            | 5.0  | 0.0                          | 10.0 | 0.0                          | 20.0 | MHz  |

| tCLCL  | Clock<br>Period |           | 200                          | -    | 100                          | -    | 50                           | -    | ns   |

| tCHCX  | High Time       |           | 80                           | -    | 40                           | -    | 20                           | -    | ns   |

| tCLCX  | Low Time        |           | 80                           | -    | 40                           | -    | 20                           | -    | ns   |

## 37.11 I/O Pin Characteristics

Table 37-18. I/O Pin Characteristics (T<sub>A</sub>=[-40, 105]°C, V<sub>DD</sub>=[1.8, 5.5]V Unless Otherwise Noted)

| Symbol                            | Description                                            | Condition                                      | Min.                | Тур.   | Max.                  | Unit |  |

|-----------------------------------|--------------------------------------------------------|------------------------------------------------|---------------------|--------|-----------------------|------|--|

| VIL                               | Input low-voltage, except RESET pin as I/O             |                                                | -0.2                | -      | 0.3×V <sub>DD</sub>   | V    |  |

| VIH                               | Input high-voltage, except RESET pin as I/O            |                                                | 0.7×V <sub>DD</sub> | -      | V <sub>DD</sub> +0.2V | V    |  |

| I <sub>IH</sub> / I <sub>IL</sub> | I/O pin Input leakage current, except RESET pin as I/O | V <sub>DD</sub> =5.5V, Pin high                | -                   | < 0.05 | -                     | μΑ   |  |

|                                   |                                                        | V <sub>DD</sub> =5.5V, Pin low                 | -                   | < 0.05 | -                     |      |  |

| V <sub>OL</sub>                   | I/O pin drive strength                                 | V <sub>DD</sub> =1.8V, I <sub>OL</sub> =1.5 mA | -                   | -      | 0.36                  | V    |  |

|                                   |                                                        | V <sub>DD</sub> =3.0V, I <sub>OL</sub> =7.5 mA | -                   | -      | 0.6                   |      |  |

|                                   |                                                        | V <sub>DD</sub> =5.0V, I <sub>OL</sub> =15 mA  | -                   | -      | 1                     |      |  |

| Vон                               | I/O pin drive strength                                 | V <sub>DD</sub> =1.8V, I <sub>OH</sub> =1.5 mA | 1.44                | -      | -                     | V    |  |