Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | e200z4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 190                                                                     |

| Program Memory Size        | 3MB (3M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 160K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 1.32V                                                           |

| Data Converters            | A/D 40x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 324-BGA                                                                 |

| Supplier Device Package    | 324-PBGA (23x23)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564a74b4cfay |

# 1.5 Feature details

#### 1.5.1 e200z4 core

SPC564A80 devices have a high performance e200z448n3 core processor:

- Dual issue, 32-bit Power Architecture embedded category CPU

- Variable Length Encoding Enhancements

- 8 KB instruction cache: 2- or 4- way set associative instruction cache

- Thirty-two 64-bit general purpose registers (GPRs)

- Memory management unit (MMU) with 24-entry fully-associative translation look-aside buffer (TLB)

- Harvard Architecture: Separate instruction bus and load/store bus

- Vectored interrupt support

- Non-maskable interrupt input

- Critical Interrupt input

- New 'Wait for Interrupt' instruction, to be used with new low power modes

- Reservation instructions for implementing read-modify-write accesses

- Signal processing extension (SPE) APU

- Single Precision Floating point (scalar and vector)

- Nexus Class 3+ debug

- Process ID manipulation for the MMU using an external tool

# 1.5.2 Crossbar Switch (XBAR)

The XBAR multiport crossbar switch supports simultaneous connections between five master ports and four slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.

The crossbar allows three concurrent transactions to occur from the master ports to any slave port but each master must access a different slave. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions. Requesting masters are treated with equal priority and are granted access to a slave port in round-robin fashion, based upon the ID of the last master to be granted access. The crossbar provides the following features:

- 5 master ports

- CPU instruction bus

- CPU data bus

- eDMA

- FlexRay

- External Bus Interface

- 4 slave ports

- Flash

- Calibration and EBI bus

- SRAM

- Peripheral bridge

- 32-bit internal address, 64-bit internal data paths

#### 1.5.3 eDMA

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 64 programmable channels, with minimal intervention from the host processor. The hardware micro-architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size. The eDMA module provides the following features:

- All data movement via dual-address transfers: read from source, write to destination

- Programmable source and destination addresses, transfer size, plus support for enhanced addressing modes

- Transfer control descriptor organized to support two-deep, nested transfer operations

- An inner data transfer loop defined by a "minor" byte transfer count

- An outer data transfer loop defined by a "major" iteration count

- Channel activation via one of three methods:

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers

- Peripheral-paced hardware requests (one per channel)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- One interrupt per channel, optionally asserted at completion of major iteration count

- Error termination interrupts optionally enabled

- Support for scatter/gather DMA processing

- Ability to suspend channel transfers by a higher priority channel

# 1.5.4 Interrupt controller

The INTC (interrupt controller) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By

GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU. The reset controller performs reset monitoring of internal and external reset sources, and drives the RSTOUT pin. Communication between the SIU and the e200z4 CPU core is via the crossbar switch. The SIU provides the following features:

- System configuration

- MCU reset configuration via external pins

- Pad configuration control for each pad

- Pad configuration control for virtual I/O via DSPI serialization

- System reset monitoring and generation

- Power-on reset support

- Reset status register provides last reset source to software

- Glitch detection on reset input

- Software controlled reset assertion

- External interrupt

- Rising or falling edge event detection

- Programmable digital filter for glitch rejection

- Critical Interrupt request

- Non-Maskable Interrupt request

- GPIO

- Centralized control of I/O and bus pins

- Virtual GPIO via DSPI serialization (requires external deserialization device)

- Dedicated input and output registers for setting each GPIO and Virtual GPIO pin

- Internal multiplexing

- Allows serial and parallel chaining of DSPIs

- Allows flexible selection of eQADC trigger inputs

- Allows selection of interrupt requests between external pins and DSPI

# 1.5.8 Flash memory

The SPC564A80 provides up to 4 MB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used to store instructions or data, or both. The flash module includes a Fetch Accelerator that optimizes the performance of the flash array to match the CPU architecture. The flash module interfaces the system bus to a dedicated flash memory array controller. For CPU 'loads', DMA transfers and CPU instruction fetch, it supports a 64-bit data bus width at the system bus port, and 128- and 256-bit read data interfaces to flash memory. The module contains a prefetch controller which prefetches sequential lines of data from the flash array into the buffers. Prefetch buffer hits allow no-wait responses.

The flash memory provides the following features:

- Supports a 64-bit data bus for instruction fetch, CPU loads and DMA access. Byte, halfword, word and doubleword reads are supported. Only aligned word and doubleword writes are supported.

- Fetch Accelerator

- Architected to optimize the performance of the flash

- Configurable read buffering and line prefetch support

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of four semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to two parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test (MISC multiple input signature calculator), runs concurrently with eTPU2 normal operation

# 1.5.12 Reaction module

The reaction module provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The reaction module has the following features:

- Six reaction channels

- Each channel output is a bus of three signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions

### 1.5.13 eQADC

The enhanced queued analog to digital converter (eQADC) block provides accurate and fast conversions for a wide range of applications. The eQADC provides a parallel interface to two on-chip analog to digital converters (ADC), and a single master to single slave serial interface to an off-chip external device. Both on-chip ADCs have access to all the analog channels.

The eQADC prioritizes and transfers commands from six command conversion command 'queues' to the on-chip ADCs or to the external device. The block can also receive data from the on-chip ADCs or from an off-chip external device into the six result queues, in parallel, independently of the command queues. The six command queues are prioritized with Queue\_0 having the highest priority and Queue\_5 the lowest. Queue\_0 also has the added ability to bypass all buffering and queuing and abort a currently running conversion on either ADC and start a Queue\_0 conversion. This means that Queue\_0 will always have a deterministic time from trigger to start of conversion, irrespective of what tasks the ADCs were performing when the trigger occurred. The eQADC supports software and external hardware triggers from other blocks to initiate transfers of commands from the queues to the on-chip ADCs or to the external device. It also monitors the fullness of command queues and result queues, and accordingly generates DMA or interrupt requests to control data movement between the queues and the system memory, which is external to the eQADC.

The ADCs also support features designed to allow the direct connection of high impedance acoustic sensors that might be used in a system for detecting engine knock. These features

# 1.5.24 Power management controller (PMC)

The power management controller contains circuitry to generate the internal 3.3 V supply and to control the regulation of 1.2 V supply with an external NPN ballast transistor. It also contains low voltage inhibit (LVI) and power-on reset (POR) circuits for the 1.2 V supply, the 3.3 V supply, the 3.3 V/5 V supply of the closest I/O segment (VDDEH1) and the 5 V supply of the regulators (VDDREG).

# 1.5.25 Nexus port controller

The NPC (Nexus Port Controller) block provides real-time Nexus Class3+ development support capabilities for the SPC564A80 Power Architecture-based MCU in compliance with the IEEE-ISTO 5001-2003 and 2010 standards. MDO port widths of 4 pins and 12 pins are available in all packages.

#### 1.5.26 JTAG

The JTAGC (JTAG Controller) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001 standard. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE 1149.1-2001 standard and supports the following features:

- IEEE 1149.1-2001 Test Access Port (TAP) interface 4 pins (TDI, TMS, TCK, and TDO)

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD, HIGHZ, CLAMP

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS AUX TAP NPC

- ACCESS AUX TAP ONCE

- ACCESS\_AUX\_TAP\_eTPU

- ACCESS CENSOR

- 3 test data registers to support JTAG Boundary Scan mode

- Bypass register

- Boundary scan register

- Device identification register

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

- Censorship Inhibit Register

- 64-bit Censorship password register

- If the external tool writes a 64-bit password that matches the Serial Boot password stored in the internal flash shadow row, Censorship is disabled until the next system reset.

# 1.5.27 Development Trigger Semaphore (DTS)

SPC564A80 devices include a system development feature, the Development Trigger Semaphore (DTS) module, that enables software to signal an external tool by driving a persistent (affected only by reset or an external tool) signal on an external device pin. There

43/157

| Table 4. SPC564A80 signal properties (c | continued) |

|-----------------------------------------|------------|

|-----------------------------------------|------------|

|                                            |                                                                              | P                                                                                                        | PCR                      |                   | 1/0                    | (E) .                                               | Sta          | tus <sup>(7)</sup> | Package pin # |     |     |

|--------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|-------------------|------------------------|-----------------------------------------------------|--------------|--------------------|---------------|-----|-----|

| Name                                       | Function <sup>(1)</sup>                                                      | A<br>G <sup>(2)</sup>                                                                                    | PA<br>Field<br>(3)       | PCR<br>(4)        | I/O<br>Type            | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset     | 176           | 208 | 324 |

| ADDR12<br>GPIO[8]                          | External address bus<br>GPIO                                                 | P<br>G                                                                                                   | 01<br>00                 | 8                 | I/O<br>I/O             | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | Т3  |

| ADDR13<br>WE[2]<br>GPIO[9]                 | External address bus Write/byte enable GPIO                                  | P<br>A2<br>G                                                                                             | 001<br>100<br>000        | 9                 | I/O<br>O<br>I/O        | VDDE3<br>Fast                                       | — / Up       | — / Up             |               | _   | U3  |

| ADDR14<br>WE[3]<br>GPIO[10]                | External address bus Write/byte enables GPIO                                 | P<br>A2<br>G                                                                                             | 001<br>100<br>000        | 10                | I/O<br>O<br>I/O        | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | U4  |

| ADDR15<br>GPIO[11]                         | External address bus<br>GPIO                                                 |                                                                                                          | 01<br>00                 | 11                | I/O<br>I/O             | VDDE3<br>Fast                                       | — / Up       | — / Up             | _             | _   | V3  |

| ADDR16<br>FR_A_TX<br>DATA16<br>GPIO[12]    | External address bus Flexray TX data channel A External data bus GPIO        | P<br>A1<br>A2<br>G                                                                                       | 001<br>010<br>100<br>000 | 12                | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | P1  |

| ADDR17 FR_A_TX_EN DATA17 GPIO[13]          | External address bus FlexRay ch. A TX data enable External data bus GPIO     | External address bus P 001 FlexRay ch. A TX data enable External data bus P 001 A1 010 A2 100 I/O Medium |                          | VDDE-EH<br>Medium | — / Up                 | — / Up                                              | _            | _                  | P2            |     |     |

| ADDR18<br>FR_A_RX<br>DATA18<br>GPIO[14]    | External address bus Flexray RX data ch. A External data bus GPIO            | P<br>A1<br>A2<br>G                                                                                       | 001<br>010<br>100<br>000 | 14                | I/O<br>I<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | R1  |

| ADDR19<br>FR_B_TX<br>DATA19<br>GPIO[15]    | External address bus<br>Flexray TX data ch. B<br>External data bus<br>GPIO   | P<br>A1<br>A2<br>G                                                                                       | 001<br>010<br>100<br>000 | 15                | I/O<br>O<br>I/O<br>I/O | VDDE-EH<br>Medium                                   | — / Up       | — / Up             | _             | _   | R2  |

| ADDR20<br>FR_B_TX_EN<br>DATA20<br>GPIO[16] | External address bus Flexray TX data enable for ch. B External data bus GPIO | Flexray TX data enable for ch. B A1 010 A2 100 16 O VDDE-EH Medium                                       |                          | — / Up            | — / Up                 | _                                                   | _            | T1                 |               |     |     |

Table 4. SPC564A80 signal properties (continued)

|                   |                                                    | Р                     | PCR                |            | I/O  | (5)                                                 | Sta          | itus <sup>(7)</sup> |     | Packag | e pin # |

|-------------------|----------------------------------------------------|-----------------------|--------------------|------------|------|-----------------------------------------------------|--------------|---------------------|-----|--------|---------|

| Name              | Function <sup>(1)</sup>                            | A<br>G <sup>(2)</sup> | PA<br>Field<br>(3) | PCR<br>(4) | Туре | Voltage <sup>(5)</sup> /<br>Pad Type <sup>(6)</sup> | During Reset | After<br>Reset      | 176 | 208    | 324     |

| CAL_DATA[11]      | Calibration data bus                               | Р                     | 01                 | 341        | I/O  | VDDE12<br>Fast                                      | — / Up       | — / Up              |     | _      | _       |

| CAL_DATA[12]      | Calibration data bus                               | Р                     | 01                 | 341        | I/O  | VDDE12<br>Fast                                      | — / Up       | — / Up              |     | _      | _       |

| CAL_DATA[13]      | Calibration data bus                               | Р                     | 01                 | 341        | I/O  | VDDE12<br>Fast                                      | — / Up       | — / Up              | -   | _      | _       |

| CAL_DATA[14]      | Calibration data bus                               | Р                     | 01                 | 341        | I/O  | VDDE12<br>Fast                                      | — / Up       | — / Up              | _   | _      | _       |

| CAL_DATA[15]      | Calibration data bus                               | Р                     | 01                 | 341        | I/O  | VDDE12<br>Fast                                      | — / Up       | — / Up              |     | _      | _       |

| CAL_RD_WR         | Calibration read/write enable                      | Р                     | 01                 | 342        | 0    | VDDE12<br>Fast                                      |              | -/-                 |     | _      | _       |

| CAL_WE[0]/BE[0]   | Calibration write/byte enable                      | Р                     | 01                 | 342        | 0    | VDDE12<br>Fast                                      |              | -/-                 | ı   | _      | _       |

| CAL_WE[1]/BE[1]   | Calibration write/byte enable                      | Р                     | 01                 | 342        | 0    | VDDE12<br>Fast                                      |              | -/-                 | _   | _      | _       |

| CAL_OE            | Calibration output enable                          | Р                     | 01                 | 342        | 0    | VDDE12<br>Fast                                      |              | -/-                 | _   | _      | _       |

| CAL_TS<br>CAL_ALE | Calibration transfer start<br>Address Latch Enable | P<br>A                | 01<br>10           | 343        | 0    | VDDE12<br>Fast                                      |              | -/-                 | _   | _      | _       |

| CAL_MDO[4]        | Calibration Nexus Message Data<br>Out              | Р                     | 01                 | _          | 0    | VDDE12<br>Fast                                      | _            | CAL_MDO[4] / —      | _   | _      | _       |

| CAL_MDO[5]        | Calibration Nexus Message Data<br>Out              | Р                     | 01                 | _          | 0    | VDDE12<br>Fast                                      | _            | CAL_MDO[5] / —      |     | _      | _       |

| CAL_MDO[6]        | Calibration Nexus Message Data<br>Out              | Р                     | 01                 | _          | 0    | VDDE12<br>Fast                                      | _            | CAL_MDO[6] / —      | _   | _      | _       |

| CAL_MDO[7]        | Calibration Nexus Message Data<br>Out              | Р                     | 01                 | _          | 0    | VDDE12<br>Fast                                      | _            | CAL_MDO[7] / —      |     | _      | _       |

Doc ID 15399 Rev 9

51/157

MDO[2] / —

MDO[3] / —

\_/\_

A13

B13

P10

19

20

126

C18

D18

B19

|                      |                                                                                                  | Р | PCR          |                    | 1/0 | (5)                                            | Sta    | atus <sup>(7)</sup> |     | Packag | e pin # |

|----------------------|--------------------------------------------------------------------------------------------------|---|--------------|--------------------|-----|------------------------------------------------|--------|---------------------|-----|--------|---------|

| Name                 | Name Function <sup>(1)</sup> A A G <sup>(2)</sup> Field (3) PCR (4) Type Pad Type <sup>(6)</sup> |   | During Reset | After<br>Reset     | 176 | 208                                            | 324    |                     |     |        |         |

| CAL_MDO[8]           | Calibration Nexus Message Data<br>Out                                                            | Р | 01           | _                  | 0   | VDDE12<br>Fast                                 | _      | CAL_MDO[8] / —      | _   | _      | _       |

| CAL_MDO[9]           | Calibration Nexus Message Data<br>Out                                                            | Р | 01           | _                  | 0   | VDDE12<br>Fast                                 | _      | CAL_MDO[9] / —      | _   | _      | _       |

| CAL_MDO[10]          | Calibration Nexus Message Data<br>Out                                                            | Р | 01           | _                  | 0   | VDDE12<br>Fast                                 | _      | CAL_MDO[10] / —     | _   | _      | _       |

| CAL_MDO[11]          | Calibration Nexus Message Data<br>Out                                                            | Р | 01           | _                  | 0   | VDDE12<br>Fast                                 | _      | CAL_MDO[11] / —     | _   | _      | _       |

|                      |                                                                                                  |   |              |                    | NE  | xus                                            |        |                     |     |        |         |

| EVTI                 | Nexus event in                                                                                   | Р | 01           | 231                | I   | VDDEH7<br>MultiV <sup>(12),(14)</sup>          | — / Up | EVTI / Up           | 116 | E15    | F21     |

| EVTO                 | Nexus event out                                                                                  | Р | 01           | 227                | 0   | VDDEH7<br>MultiV <sup>(12),(14),</sup><br>(15) | _      | EVTO / —            | 120 | D15    | F22     |

| мско                 | Nexus message clock out                                                                          | Р | _            | 219 <sup>(11</sup> | 0   | VRC33<br>Fast                                  | _      | мско / —            | 14  | F15    | G20     |

| MDO0 <sup>(16)</sup> | Nexus message data out                                                                           | Р | 01           | 220                | 0   | VRC33<br>Fast                                  | _      | MDO[0] / —          | 17  | A14    | B20     |

| MDO1 <sup>(16)</sup> | Nexus message data out                                                                           | Р | 01           | 221                | 0   | VRC33<br>Fast                                  | _      | MDO[1] / —          | 18  | B14    | C19     |

| MDO2 <sup>(16)</sup> | Nexus message data out                                                                           | Р | 01           | 222                | 0   | VRC33                                          | _      | MDO[2] / —          | 19  | Δ13    | C18     |

01

01

01

10

00

Р

Р

Α1

G

222

223

75

0

0

0

0

I/O

Fast VRC33

Fast

VDDEH7

MultiV<sup>(12),(14)</sup>

MDO2<sup>(16)</sup>

MDO3<sup>(16)</sup>

MDO4<sup>(16)</sup>

GPIO[75]

ETPUA2\_O<sup>(8)</sup>

Nexus message data out

Nexus message data out

Nexus message data out

**GPIO**

eTPU A channel (output only)

Table 9. Absolute maximum ratings<sup>(1)</sup> (continued)

| Cymbal           |    | Parameter                                                      | Conditions | Va    | Heit  |      |

|------------------|----|----------------------------------------------------------------|------------|-------|-------|------|

| Symbol           |    | Parameter                                                      | Conditions | min   | max   | Unit |

| ТЈ               | SR | Maximum operating temperature range - die junction temperature |            | -40.0 | 150.0 | °C   |

| T <sub>STG</sub> | SR | Storage temperature range                                      |            | -55.0 | 150.0 | °C   |

| T <sub>SDR</sub> | SR | Maximum solder temperature <sup>(13)</sup>                     |            | _     | 260.0 | °C   |

| MSL              | SR | Moisture sensitivity level <sup>(14)</sup>                     |            | _     | 3     |      |

Functional operating conditions are given in the DC electrical specifications. Absolute maximum ratings are stress ratings

only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device

reliability or cause permanent damage to the device.

- 2. Allowed 2 V for 10 hours cumulative time, remaining time at 1.2 V +10%.

- The V<sub>FLASH</sub> supply is connected to V<sub>RC33</sub> in the package substrate. This specification applies to calibration package devices only.

- 4. Allowed 5.3 V for 10 hours cumulative time, remaining time at 3.3 V +10%.

- 5. Allowed 5.9 V for 10 hours cumulative time, remaining time at 5 V +10%.

- 6. All functional non-supply I/O pins are clamped to  $V_{\mbox{SS}}$  and  $V_{\mbox{DDE}}$ , or  $V_{\mbox{DDEH}}$ .

- AC signal overshoot and undershoot of up to 2.0 V of the input voltages is permitted for an accumulative duration of 60 hours over the complete lifetime of the device (injection current not limited for this duration).

- 8. Internal structures hold the voltage greater than -1.0 V if the injection current limit of 2 mA is met.

- Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- 10. Internal structures hold the input voltage less than the maximum voltage on all pads powered by  $V_{DDE}$  supplies, if the maximum injection current specification is met (2 mA for all pins) and  $V_{DDE}$  is within the operating voltage specifications.

- 11. Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- 12. Total injection current for all analog input pins must not exceed 15 mA.

- 13. Solder profile per IPC/JEDEC J-STD-020D.

- 14. Moisture sensitivity per JEDEC test method A112.

### 3.3 Thermal characteristics

Table 10. Thermal characteristics for 176-pin QFP<sup>(1)</sup>

| Symb            | ymbol C Parameter |   | Parameter                                              | Conditions                                  | Value | Unit |

|-----------------|-------------------|---|--------------------------------------------------------|---------------------------------------------|-------|------|

| $R_{\thetaJA}$  | CC                | D | Junction-to-Ambient, Natural Convection <sup>(2)</sup> | Single layer board - 1s                     | 38    | °C/W |

| $R_{\theta JA}$ | СС                | D | Junction-to-Ambient, Natural Convection <sup>(2)</sup> | Four layer board - 2s2p                     | 31    | °C/W |

| $R_{	heta JMA}$ | СС                | D | Junction-to-Moving-Air, Ambient <sup>(2)</sup>         | 200 ft./min., single layer<br>board - 1s    | 30    | °C/W |

| $R_{	heta JMA}$ | СС                | D | Junction-to-Moving-Air, Ambient <sup>(2)</sup>         | at 200 ft./min., four layer<br>board - 2s2p | 25    | °C/W |

| $R_{\theta JB}$ | CC                | D | Junction-to-Board <sup>(3)</sup>                       |                                             | 20    | °C/W |

Table 10. Thermal characteristics for 176-pin QFP<sup>(1)</sup> (continued)

|   | Symbo              | ol | С | Parameter                                                  | Conditions | Value | Unit |

|---|--------------------|----|---|------------------------------------------------------------|------------|-------|------|

| Ī | $R_{\theta JCtop}$ | CC | D | Junction-to-Case <sup>(4)</sup>                            |            | 5     | °C/W |

|   | $\Psi_{JT}$        | СС | D | Junction-to-Package Top, Natural Convection <sup>(5)</sup> |            | 2     | °C/W |

- 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

- Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 4. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 11. Thermal characteristics for 208-pin LBGA<sup>(1)</sup>

| Symbo            | ol | C | Parameter                                                  | Conditions                                | Value | Unit |

|------------------|----|---|------------------------------------------------------------|-------------------------------------------|-------|------|

| $R_{	hetaJA}$    | СС | D | Junction-to-Ambient, Natural Convection <sup>(2),(3)</sup> | One layer board - 1s                      | 39    | °C/W |

| $R_{	hetaJA}$    | СС | D | Junction-to-Ambient, Natural Convection <sup>(2),(4)</sup> | Four layer board - 2s2p                   | 24    | °C/W |

| $R_{\theta JMA}$ | СС | D | Junction-to-Moving-Air, Ambient <sup>(2),(4)</sup>         | at 200 ft./min., one layer board          | 31    | °C/W |

| $R_{\theta JMA}$ | СС | D | Junction-to-Moving-Air, Ambient <sup>(2),(4)</sup>         | at 200 ft./min., four layer<br>board 2s2p | 20    | °C/W |

| $R_{\theta JB}$  | CC | D | Junction-to-board <sup>(5)</sup>                           | Four layer board - 2s2p                   | 13    | °C/W |

| $R_{\theta JC}$  | СС | D | Junction-to-case <sup>(6)</sup>                            |                                           | 6     | °C/W |

| $\Psi_{JT}$      | СС | D | Junction-to-package top natural convection <sup>(7)</sup>  |                                           | 2     | °C/W |

- 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# 3.6.2 Recommended power transistors

The following NPN transistors are recommended for use with the on-chip voltage regulator controller: ON Semiconductor<sup>TM</sup> BCP68T1 or NJD2873 as well as Philips Semiconductor<sup>TM</sup> BCP68. The collector of the external transistor is preferably connected to the same voltage supply source as the output stage of the regulator.

| Symbol              | Parameter                               | Value                    | Unit |

|---------------------|-----------------------------------------|--------------------------|------|

| h <sub>FE</sub> (β) | DC current gain (Beta)                  | 60 – 550                 | _    |

| P <sub>D</sub>      | Absolute minimum power dissipation      | >1.0<br>(1.5 preferred)  | W    |

| I <sub>CMaxDC</sub> | Minimum peak collector current          | 1.0                      | Α    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage | 200 – 600 <sup>(1)</sup> | mV   |

| $V_{BE}$            | Base-to-emitter voltage                 | 0.4 – 1.0                | V    |

<sup>1.</sup> Adjust resistor at bipolar transistor collector for 3.3 V/5.0 V to avoid VCE < VCE<sub>SAT</sub>.

# 3.7 Power up/down sequencing

There is no power sequencing required among power sources during power up and power down, in order to operate within specification.

Although there are no power up/down sequencing requirements to prevent issues such as latch-up or excessive current spikes the state of the I/O pins during power up/down varies according to *Table 19* for all pins with fast pads, and *Table 20* for all pins with medium, slow, and multi-voltage pads.

Table 19. Power sequence pin states (fast pads)

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | Pad State      |

|------------------|-------------------|-----------------|----------------|

| LOW              | X                 | Х               | LOW            |

| $V_{DDE}$        | LOW               | Х               | HIGH           |

| V <sub>DDE</sub> | V <sub>RC33</sub> | LOW             | HIGH IMPEDANCE |

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | FUNCTIONAL     |

Table 20. Power sequence pin states (medium, slow, and multi-voltage pads)

| V <sub>DDEH</sub> | V <sub>DD</sub> | Pad State      |  |  |  |

|-------------------|-----------------|----------------|--|--|--|

| LOW               | Х               | LOW            |  |  |  |

| V <sub>DDEH</sub> | LOW             | HIGH IMPEDANCE |  |  |  |

| V <sub>DDEH</sub> | V <sub>DD</sub> | FUNCTIONAL     |  |  |  |

Table 29. eQADC single ended conversion specifications (operating)

| Symbol C         |    | ( | Parameter                                                     | V    | Unit             |        |

|------------------|----|---|---------------------------------------------------------------|------|------------------|--------|

| Symbol           |    | C | raiametei                                                     | min  | max              |        |

| OFFNC            | CC | С | Offset error without calibration                              | 0    | 160              | Counts |

| OFFWC            | СС | С | Offset error with calibration                                 | -4   | 4                | Counts |

| GAINNC           | СС | С | Full scale gain error without calibration                     | -160 | 0                | Counts |

| GAINWC           | СС | С | Full scale gain error with calibration                        | -4   | 4                | Counts |

| I <sub>INJ</sub> | СС | Т | Disruptive input injection current (1), (2), (3), (4)         | -3   | 3                | mA     |

| E <sub>INJ</sub> | СС | Т | Incremental error due to injection current <sup>(5),(6)</sup> | -4   | 4                | Counts |

| TUE8             | СС | С | Total unadjusted error (TUE) at 8 MHz                         | -4   | 4 <sup>(6)</sup> | Counts |

| TUE16            | CC | С | Total unadjusted error at 16 MHz                              | -8   | 8                | Counts |

Below disruptive current conditions, the channel being stressed has conversion values of 0x3FF for analog inputs greater then V<sub>RH</sub> and 0x0 for values less then V<sub>RL</sub>. Other channels are not affected by non-disruptive conditions.

- 4. Condition applies to two adjacent pins at injection limits.

- 5. Performance expected with production silicon.

- 6. All channels have same 10 k $\Omega$  < Rs < 100 k $\Omega$ ; Channel under test has Rs=10 k $\Omega$ ;  $I_{INJ}=I_{INJMAX},I_{INJMIN}$

Table 30. eQADC differential ended conversion specifications (operating)

| Symbol   |    | С | Parameter          |               | Va                         | - Unit           |                       |

|----------|----|---|--------------------|---------------|----------------------------|------------------|-----------------------|

|          |    | C |                    |               | min                        | max              | Oilit                 |

|          | CC | - | Variable gain ampl | ifier accurad | cy (gain=1) <sup>(2)</sup> |                  |                       |

|          | СС | С | INL                | 8 MHz<br>ADC  | -4                         | 4                | Counts <sup>(3)</sup> |

| GAINVGA1 | СС | С | IINL               | 16 MHz<br>ADC | -8                         | 8                | Counts                |

|          | CC | С | DNL                | 8 MHz<br>ADC  | -3 <sup>(4)</sup>          | 3 <sup>(4)</sup> | Counts                |

|          | CC | С | DINE               | 16 MHz<br>ADC | -3 <sup>(4)</sup>          | 3 <sup>(4)</sup> | Counts                |

<sup>2.</sup> Exceeding limit may cause conversion error on stressed channels and on unstressed channels. Transitions within the limit do not affect device reliability or cause permanent damage.

<sup>3.</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values using V<sub>POSCLAMP</sub> = V<sub>DDA</sub> + 0.5 V and V<sub>NEGCLAMP</sub> = -0.3 V, then use the larger of the calculated values.

# 3.16 AC specifications

# 3.16.1 Pad AC specifications

Table 35. Pad AC specifications (5.0 V)<sup>(1)</sup>

| Name                          |     | С | Output Delay<br>(ns) <sup>(2),(3)</sup><br>Low-to-High / High-<br>to-Low |           | Rise/Fall Ed | lge (ns) <sup>(3),(4)</sup> | Drive Load<br>(pF) | SRC/DSC           |

|-------------------------------|-----|---|--------------------------------------------------------------------------|-----------|--------------|-----------------------------|--------------------|-------------------|

|                               |     |   | Min                                                                      | Max       | Min          | Max                         |                    | MSB,LSB           |

|                               | СС  | D | 4.6/3.7                                                                  | 12/12     | 2.2/2.2      | 7/7                         | 50                 | 11 <sup>(8)</sup> |

| Medium <sup>(5),(6),(7)</sup> |     | • |                                                                          |           | N/A          |                             |                    | 10 <sup>(9)</sup> |

| Wedium                        | СС  | D | 12/13                                                                    | 28/34     | 5.6/6        | 15/15                       | 50                 | 01                |

|                               | СС  | D | 69/71                                                                    | 152/165   | 34/35        | 74/74                       | 50                 | 00                |

|                               | СС  | D | 7.3/5.7                                                                  | 19/18     | 4.4/4.3      | 14/14                       | 50                 | 11 <sup>(8)</sup> |

| Slow <sup>(7),(10)</sup>      | N/A |   |                                                                          |           |              |                             |                    |                   |

| Slow(*),(**)                  | СС  | D | 26/27                                                                    | 61/69     | 13/13        | 34/34                       | 50                 | 01                |

|                               | СС  | D | 137/142                                                                  | 320/330   | 72/74        | 164/164                     | 50                 | 00                |

|                               | СС  | D | 4.1/3.6                                                                  | 10.3/8.9  | 3.28/2.98    | 8/8                         | 50                 | 11 <sup>(8)</sup> |

| MultiV <sup>(11)</sup>        | N/A |   |                                                                          |           |              |                             | 10 <sup>(9)</sup>  |                   |

| (High Swing Mode)             | СС  | D | 8.38/6.11                                                                | 16/12.9   | 5.48/4.81    | 11/11                       | 50                 | 01                |

|                               | СС  | D | 61.7/10.4                                                                | 92.2/24.3 | 42.0/12.2    | 63/63                       | 50                 | 00                |

| MultiV<br>(Low Swing Mode)    | СС  | D | 2.31/2.34                                                                | 7.62/6.33 | 1.26/1.67    | 6.5/4.4                     | 30                 | 11 <sup>(8)</sup> |

| Fast <sup>(12)</sup>          | N/A |   |                                                                          |           |              |                             |                    |                   |

| pad_i_hv <sup>(13)</sup>      | СС  | D | 0.5/0.5                                                                  | 1.9/1.9   | 0.3/0.3      | ±1.5/1.5                    | 0.5                | N/A               |

| pull_hv                       | СС  | D | NA                                                                       | 6000      |              | 5000/5000                   | 50                 | N/A               |

<sup>1.</sup> These are worst case values that are estimated from simulation and not tested. The values in the table are simulated at  $V_{DD} = 1.14 \text{ V}$  to 1.32 V,  $V_{DDEH} = 4.5 \text{ V}$  to 5.5 V,  $T_A = T_L$  to  $T_H$

- 3. Delay and rise/fall are measured to 20% or 80% of the respective signal.

- 4. This parameter is guaranteed by characterization before qualification rather than 100% tested.

- 5. In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- 6. Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 7. Output delay is shown in Figure 9: Pad output delay. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- 8. Can be used on the tester.

- 9. This drive select value is not supported. If selected, it will be approximately equal to 11.

- 10. Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- 11. Selectable high/low swing IO pad with selectable slew in high swing mode only.

- 12. Fast pads are 3.3 V pads.

- 13. Stand alone input buffer. Also has weak pull-up/pull-down.

<sup>2.</sup> This parameter is supplied for reference and is not guaranteed by design and not tested.

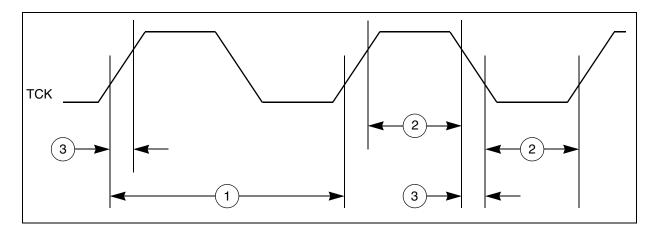

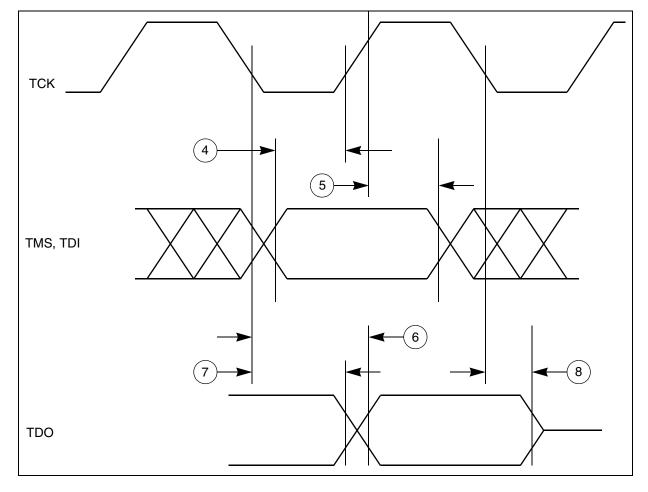

next Nexus/JTAG command. Expect the affect of EVTI and RDY to be delayed by edges of TCK. Note: RDY is not available in all packages of all devices.

Figure 11. JTAG test clock input timing

Figure 12. JTAG test access port timing

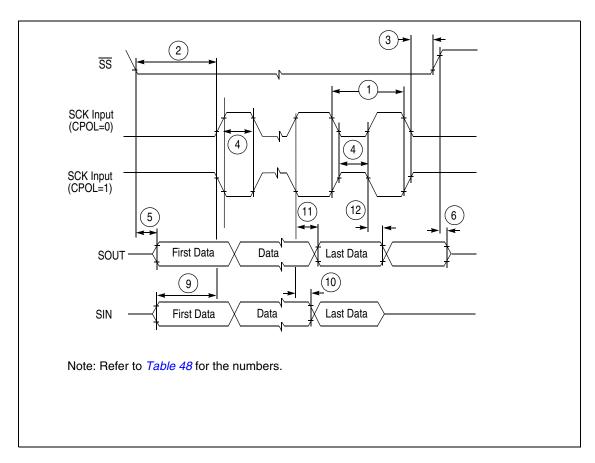

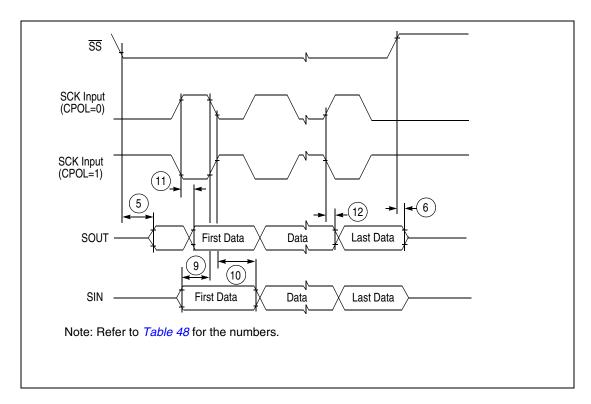

Figure 29. DSPI modified transfer format timing — slave, CPHA =0

Figure 30. DSPI modified transfer format timing — slave, CPHA =1

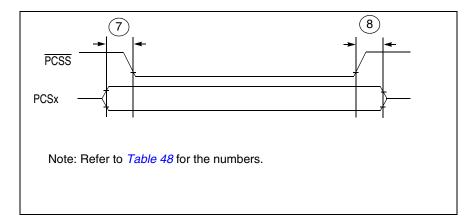

Figure 31. DSPI PCS strobe (PCSS) timing

# 4 Packages

# 4.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

Table 52. LQFP176 package mechanical data

| DEE              | DATABOOK |     |     | MII   | LIMETER | S <sup>(1)</sup> | INCHES |       |       |

|------------------|----------|-----|-----|-------|---------|------------------|--------|-------|-------|

| REF.             | TYP      | MIN | MAX | TYP   | MIN     | MAX              | TYP    | MIN   | MAX   |

| Α                |          |     |     |       |         | 1.600            |        |       | 0.063 |

| A1               |          |     |     |       | 0.050   | 0.150            |        | 0.002 |       |

| A2               |          |     |     |       | 1.350   | 1.450            |        | 0.053 | 0.057 |

| b                |          |     |     |       | 0.170   | 0.270            |        | 0.007 | 0.011 |

| С                |          |     |     |       | 0.090   | 0.200            |        | 0.004 | 0.008 |

| D                |          |     |     |       | 23.900  | 24.100           |        | 0.941 | 0.949 |

| Е                |          |     |     |       | 23.900  | 24.100           |        | 0.941 | 0.949 |

| е                |          |     |     | 0.500 |         |                  | 0.020  |       |       |

| HD               |          |     |     |       | 25.900  | 26.100           |        | 1.020 | 1.028 |

| HE               |          |     |     |       | 25.900  | 26.100           |        | 1.020 | 1.028 |

| L <sup>(2)</sup> |          |     |     |       | 0.450   | 0.750            |        | 0.018 | 0.030 |

| L1               |          |     |     | 1.000 |         |                  | 0.039  |       |       |

| ZD               |          |     |     | 1.250 |         |                  | 0.049  |       |       |

| ZE               |          |     |     | 1.250 |         |                  | 0.049  |       |       |

| ccc              |          |     |     |       |         | 0.080            |        |       | 0.003 |

| ANGLE            |          |     |     |       | 0°      | 7°               |        | 0     | 7º    |

<sup>1.</sup> Controlling Dimension: MILLIMETER

<sup>2.</sup> L dimension is measured at gauge plane at 0.25 above the seating plane.

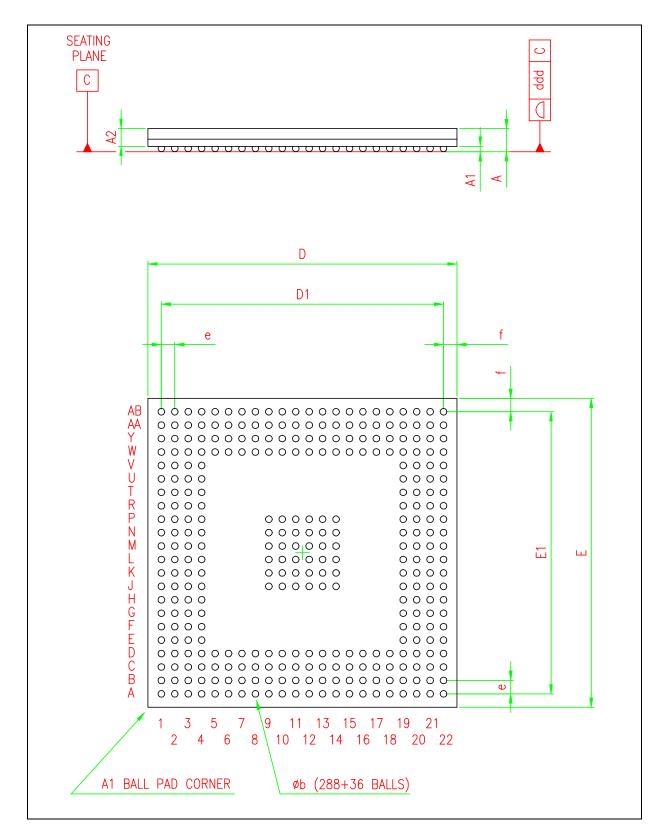

| Symbol             |       | mm    |       | inches <sup>(1)</sup> |        |        |  |  |

|--------------------|-------|-------|-------|-----------------------|--------|--------|--|--|

|                    | Min   | Тур   | Max   | Min                   | Тур    | Max    |  |  |

| D                  | 16.80 | 17.00 | 17.20 | 0.6614                | 0.6693 | 0.6772 |  |  |

| D1                 |       | 15.00 |       |                       | 0.5906 |        |  |  |

| E                  | 16.80 | 17.00 | 17.20 | 0.6614                | 0.6693 | 0.6772 |  |  |

| E1                 |       | 15.00 |       |                       | 0.5906 |        |  |  |

| е                  |       | 1.00  |       |                       | 0.0394 |        |  |  |

| F                  |       | 1.00  |       |                       | 0.0394 |        |  |  |

| ddd                |       |       | 0.20  |                       |        | 0.0079 |  |  |

| eee <sup>(4)</sup> |       |       | 0.25  |                       |        | 0.0098 |  |  |

| fff <sup>(5)</sup> |       |       | 0.10  |                       |        | 0.0039 |  |  |

Table 53. LBGA208 mechanical data (continued)

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- LBGA stands for Low profile Ball Grid Array.

—Low profile: The total profile height (Dim A) is measured from the seating plane to the top of the

- —The maximum total package height is calculated by the following methodology: A2 Typ+A1 Typ + $\sqrt{(A1^2+A3^2+A4^2)}$  tolerance values) Low profile: 1.20mm < A  $\leq$  1.70mm

- 3. The typical ball diameter before mounting is 0.60mm.

- The tolerance of position that controls the location of the pattern of balls with respect to datums A and B. For each ball there is a cylindrical tolerance zone eee perpendicular to datum C and located on true position with respect to datums A and B as defined by e. The axis perpendicular to datum C of each ball must lie within this tolerance zone.

- The tolerance of position that controls the location of the balls within the matrix with respect to each other. For each ball there is a cylindrical tolerance zone fff perpendicular to datum C and located on true position as defined by e. The axis perpendicular to datum C of each ball must lie within this tolerance zone. Each tolerance zone fff in the array is contained entirely in the respective zone eee above. The axis of each ball must lie simultaneously in both tolerance zones.

#### 4.2.3 **PBGA324**

Doc ID 15399 Rev 9 142/157

Figure 34. PBGA324 package mechanical drawing

**577**